Академический Документы

Профессиональный Документы

Культура Документы

Improving Noise Immunity For Serial Interface

Загружено:

shubhamformeОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Improving Noise Immunity For Serial Interface

Загружено:

shubhamformeАвторское право:

Доступные форматы

IMPROVING NOISE IMMUNITY

FOR SERIAL INTERFACE

A Lattice Semiconductor White Paper

July 2014

Lattice Semiconductor

5555 Northeast Moore Ct.

Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000

www.latticesemi.com

1 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Introduction

Serial interfaces like SPI or I2C are common methods of communication between ICs or

devices. The I2C interface has two wires (lines), one is clock and the other is data. The

data is transferred serially from one device to another at the frequency determined by

the clock. The protocol of communication between the two devices should meet all the

required specifications of the serial interfaces, in order to send and receive correct data.

FPGAs and CPLDs are programmable devices which often implement serial interface

controller using HDL (Hardware Description Language) so that the user can define any

general purpose I/O (GPIO) as serial interface ports. The serial interface specification

for high speed data transfer (400 kHz and faster) recommends a 50 ns noise filter on

the inputs to prevent double-clocking and miss-communication. However,

programmable devices generally do not have built-in noise filters on their GPIO pins.

In a complex system there can be noise from a variety of sources such as: switching

noise from power supplies, other devices, or the environment itself. Any or all of these

may cause an intermittent error in serial communication. This paper discusses some

techniques to improve noise immunity for the serial interfaces implemented in devices

which do not have built-in noise filter for the serial interface.

Techniques to improve noise immunity

External RC Filter

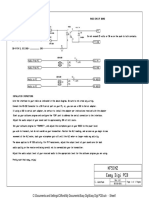

Adding an external RC low-pass filter on the serial interface pins is one way of

implementing a noise filter. However, a simple RC filter with time constant of 50 ns also

slows the rising edges and presents a considerable load to the driving pins. A slow

edge is more susceptible to noise and the large capacitive load can cause ground-

bounce within the device. The circuit shown in Figure 1 is a good compromise; providing

noise reduction without slowing the edge too much or loading down the driver pins.

This circuit can be used on both the Master and Slave devices on any given bus. The

exact component values for Cf, RS1, RS2, and Rpull-up depend upon supply voltage and

level of noise reduction desired.

2 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Figure 1: External Low Pass Noise Filter Circuit

The value of the series resistor(s) (RS1 and RS2) will effectively raise the logic low output

level on to the bus from the device being filtered. If the value of the series resistor(s) is

too large, then the voltage swing on the serial bus will be too small for reliable

communication. Thus, the value of the series resistor(s) has to balance between

enough filtering without reducing the low voltage margin. The tables below show

suggested values of components that balance these issues and consider the other

serial interface specifications for either a 3.3 V or 2.5 V system. The 3.3 V system has

about 100 mV better noise margin over the 2.5 V system, based on the values in the

tables.

Time constant = RS1 *Cf in seconds.

Margin to VIL = VIL (max) – VOL (calculated) = 0.3 VDD – [VOL (max) + VRs (voltage drop

on both RS1 and RS2)]

3 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Table 1: Component Values for: VDD =3.3 V VIL (max)=0.99 V VOL (max) =0.4 V

Table 2: Component Values for: VDD =2.5 V VIL (max)=0.75 V VOL (max) =0.4 V

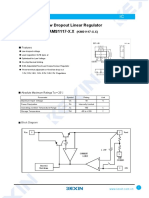

Decoupling Supply

There are instances where noise on supplies associated with serial interfaces may

cause error in communication. Reducing such noise can be accomplished with simple

LC filtering circuit. An inductor or Ferrite Bead of about 4-10 uH, with good current

carrying characteristics and low resistance should be placed in series with the voltage

source to choke off the high frequency noise. Ferrite Bead Inductors such as Murata

BLM31B601S, BLM11B601SPB, or equivalent offer good inductive supply isolation.

After the inductor multiple capacitors of different values are typically used. The smaller

valued capacitor is better at filtering out the highest frequency component of the noise

4 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

while the larger valued capacitor is more effective at filtering out the lower frequency

component of the noise. Figure 2 shows a typical circuit configuration.

Figure 2: Typical Supply Decoupling Circuit

Digital Filter

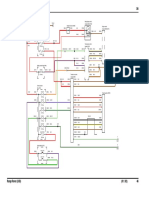

In FPGA designs that implement a soft core serial interface, a pair of digital filters can

be added; one for the data and one for the clock. Figure 3 is a generic circuit of a

scalable single filter that can be realized in VHDL or Verilog. The size of the filter, or

number of taps, is based on the oscillator (OSC) frequency and the desired filter time.

The filter should have a minimum of three taps. Table 3 lists some recommended

frequencies and number of filter taps to provide effective filtering. Generally speaking,

both of the serial signals (data and clock) should have identically sized filters. The

exception would be if the data and clock have a known relationship that does not meet

the specification. Then one of the filters could be extended to properly align the signals

at the outputs.

5 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Figure 2: Digital Filter Circuit

Table 3: Digital Filter Taps and Filter Time Based on OSC Frequencies

6 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Summary

For reliable Serial communication, it is essential to minimize the effect of external noise

from the data and clock lines. The techniques discussed in this white paper can be used

to improve the reliability of serial communication in noisy environments. One or more of

the techniques described above may be helpful for designers working with serial

interfaces on devices such as the ones mentioned below:

• Any FPGA or CPLD using GPIOs for serial interface ports

• Any device without built-in noise filter on the serial ports

• MachXO2-EFB, POWR1220AT8, POWR1014A, POWR6AT6

Additionally, it is advised that the designer follows the serial interface specifications,

when implementing the above techniques.

7 Improving Noise Immunity for Serial Interface

A Lattice Semiconductor White Paper

Вам также может понравиться

- Diseño Algoritmos RFДокумент67 страницDiseño Algoritmos RFRodrigo LopezОценок пока нет

- 4.1 Network Filters and Transmission LinesДокумент11 страниц4.1 Network Filters and Transmission LinesRockyОценок пока нет

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsДокумент5 страницLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantОценок пока нет

- Implementation Using Power Line Communications in Telephone SystemДокумент5 страницImplementation Using Power Line Communications in Telephone SystemGopinath KudaravalliОценок пока нет

- Adf PLL Adf 4351 Adl5801 CN0239Документ6 страницAdf PLL Adf 4351 Adl5801 CN0239ibanitescuОценок пока нет

- Delta Modulation For Voice Transmission: Application Note January 1997 AN607.1Документ6 страницDelta Modulation For Voice Transmission: Application Note January 1997 AN607.1Mac AnciadoОценок пока нет

- AN491 - Power Supply Rejection For Low-Jitter ClocksДокумент8 страницAN491 - Power Supply Rejection For Low-Jitter ClocksJohanes SetiawanОценок пока нет

- Semiconductor Application Note: Archived by Freescale Semiconductor, Inc. 2005Документ8 страницSemiconductor Application Note: Archived by Freescale Semiconductor, Inc. 2005Shuvo RashidОценок пока нет

- RS-232 and RS-485 Serial InterfacesДокумент10 страницRS-232 and RS-485 Serial InterfacesSPAPUKYAN100% (3)

- "Guidelines To Low Cost Wireless System Design": Frank Karlsen - RF Designer, Wireless Communications, Nordic VLSI ASAДокумент15 страниц"Guidelines To Low Cost Wireless System Design": Frank Karlsen - RF Designer, Wireless Communications, Nordic VLSI ASAdeyavik2013Оценок пока нет

- High-Speed-Board Design Techniques: Application NoteДокумент28 страницHigh-Speed-Board Design Techniques: Application NoteMicle MarianОценок пока нет

- Embedded Ultra Low-Power Digital Signal Processing: Electronics / ÉlectroniqueДокумент4 страницыEmbedded Ultra Low-Power Digital Signal Processing: Electronics / ÉlectroniquemeasbolasОценок пока нет

- Microsemi Proasicplus Designing Clean Analog PLL Mixed Signal Environment Application Note Ac204 v2Документ8 страницMicrosemi Proasicplus Designing Clean Analog PLL Mixed Signal Environment Application Note Ac204 v2Denis GrigorenkoОценок пока нет

- Tidu 160Документ47 страницTidu 160engamin_sОценок пока нет

- AFBR 776BxxxZ and AFBR 786BxxxZ Twelve Channel Transmitter and Receiver Pluggable Parallel Fiber Optics ModulesДокумент48 страницAFBR 776BxxxZ and AFBR 786BxxxZ Twelve Channel Transmitter and Receiver Pluggable Parallel Fiber Optics ModulesTene Emil GabrielОценок пока нет

- AN 01eДокумент3 страницыAN 01eluisОценок пока нет

- Fundamentals of Wireless LANs Answer - 100%Документ8 страницFundamentals of Wireless LANs Answer - 100%John van der VaartОценок пока нет

- Quickchip Design Example 1 - A Silicon Bipolar Broadband PLL Building Block Integrated CircuitДокумент7 страницQuickchip Design Example 1 - A Silicon Bipolar Broadband PLL Building Block Integrated Circuitflo724Оценок пока нет

- Input EMI Filters For SMPS PDFДокумент8 страницInput EMI Filters For SMPS PDFsenkum812002Оценок пока нет

- (MWRF0204) Balanced LNA Suits Cellular Base StationsДокумент9 страниц(MWRF0204) Balanced LNA Suits Cellular Base StationsdvdiyenОценок пока нет

- Extending The SPI Bus For Long Distnce CommДокумент7 страницExtending The SPI Bus For Long Distnce CommFelipe Ademir Aleman Hdez100% (2)

- A 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)Документ8 страницA 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)XollloXОценок пока нет

- Design and Analysis of A Low Power Passive UHF RFID Transponder ICДокумент6 страницDesign and Analysis of A Low Power Passive UHF RFID Transponder ICAli ErenОценок пока нет

- AND9114/D Maintaining Signal Integrity When Selecting ESD Protection For USB 3.0 InterfaceДокумент8 страницAND9114/D Maintaining Signal Integrity When Selecting ESD Protection For USB 3.0 Interfacev2304451Оценок пока нет

- Design 2Документ25 страницDesign 2Fatih Mehmet FerahОценок пока нет

- Eetop - CN PLL TutorialДокумент23 страницыEetop - CN PLL TutorialMustafaMuhammadОценок пока нет

- A Versatile Low-Power Power Line FSK TransceiverДокумент4 страницыA Versatile Low-Power Power Line FSK TransceiverLuciana JovinianoОценок пока нет

- D-Band Frequency Tripler For Passive Imaging - Final 13th JulyДокумент4 страницыD-Band Frequency Tripler For Passive Imaging - Final 13th JulyTapas SarkarОценок пока нет

- Follow PC-Board Design Guidelines For Lowest CMOS EMI RadiationДокумент6 страницFollow PC-Board Design Guidelines For Lowest CMOS EMI RadiationPraveen KumarОценок пока нет

- "Power Line Communication": 1.dhiraj S. Bhojane 2.saurabh R. Chaudhari 3. Prakash D. More 4.eshant G. RajgureДокумент7 страниц"Power Line Communication": 1.dhiraj S. Bhojane 2.saurabh R. Chaudhari 3. Prakash D. More 4.eshant G. RajgureChanna SenavirathnaОценок пока нет

- V-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower FrequenciesДокумент4 страницыV-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower Frequencieskarthik srivatsa mbОценок пока нет

- High-Performance D/A-Converters: Application to Digital TransceiversОт EverandHigh-Performance D/A-Converters: Application to Digital TransceiversОценок пока нет

- The Effects and Reduction of Common-Mode Noise and Electromagnetic Interference in High - Resolution Digital Audio Transmission SystemsДокумент33 страницыThe Effects and Reduction of Common-Mode Noise and Electromagnetic Interference in High - Resolution Digital Audio Transmission Systemss3tupОценок пока нет

- Tutorial On Basic Link Budget Analysis PDFДокумент8 страницTutorial On Basic Link Budget Analysis PDFMeklit Wolde MariamОценок пока нет

- Figure 3.2. RS-485 BusДокумент42 страницыFigure 3.2. RS-485 BusMichal Cousins100% (1)

- Design of A Baw Quadplexer ModuleДокумент12 страницDesign of A Baw Quadplexer ModuleHa TranОценок пока нет

- Full TextДокумент19 страницFull TextAbdullah Sulaiman AlorainiОценок пока нет

- EMC Testing of Copper Cables For High Speed Data TransmissionДокумент30 страницEMC Testing of Copper Cables For High Speed Data TransmissionMarcus DragoОценок пока нет

- The RS-485 Design GuideДокумент9 страницThe RS-485 Design GuideZoran FabekovicОценок пока нет

- Link Budget Calculation - Tranzeo Link Budget WhitepaperДокумент4 страницыLink Budget Calculation - Tranzeo Link Budget Whitepapernassr_ismail100% (1)

- High Order Programmable and Tunable Analog Filter ICДокумент16 страницHigh Order Programmable and Tunable Analog Filter ICRahil JainОценок пока нет

- The RC Link and ASK Environment: RF Based Wireless Remote Control SystemДокумент9 страницThe RC Link and ASK Environment: RF Based Wireless Remote Control SystemKhang VanОценок пока нет

- Easy Radio 433Документ15 страницEasy Radio 433John TwomeyОценок пока нет

- What's The Difference Between The RS-232 and RS-485 Serial Interfaces?Документ8 страницWhat's The Difference Between The RS-232 and RS-485 Serial Interfaces?vairam81100% (2)

- 16Документ6 страниц16Isnaldi NasrulОценок пока нет

- Experiment-1: Fig 1.1: Network DesignedДокумент46 страницExperiment-1: Fig 1.1: Network DesignedRadhika RaghavОценок пока нет

- Serial Communication ProtocolsДокумент32 страницыSerial Communication ProtocolsVissu Sweet100% (1)

- Industrial Data Communications - RS-232/RS-485: Tutorial 2Документ5 страницIndustrial Data Communications - RS-232/RS-485: Tutorial 2Pedro Ferreira100% (4)

- WS3000 (G SHDSL) - EngДокумент132 страницыWS3000 (G SHDSL) - Engjohnsonjoseph50% (1)

- RXM XXX ES Data GuideДокумент11 страницRXM XXX ES Data GuideAstrid PorticaОценок пока нет

- Research PaperДокумент8 страницResearch PaperinfydiptiОценок пока нет

- Agilent 34970A Data Acquistion / Switch Unit: User's GuideДокумент18 страницAgilent 34970A Data Acquistion / Switch Unit: User's GuideUttam MishraОценок пока нет

- An Overview of Pow Er Amplifier Research at Ucsd: Lots of Watts and Plenty of MHZДокумент33 страницыAn Overview of Pow Er Amplifier Research at Ucsd: Lots of Watts and Plenty of MHZMerlyCalvaОценок пока нет

- Serial Communication 2Документ31 страницаSerial Communication 2jaigodara100% (1)

- What's The Difference Between The RS-232 and RS-485 Serial Interfaces?Документ7 страницWhat's The Difference Between The RS-232 and RS-485 Serial Interfaces?Pranjali patil100% (1)

- For ProjectДокумент7 страницFor ProjectPranjal Jalan100% (1)

- Design Notes: Lowćvoltage Differential Signaling (LVDS)Документ7 страницDesign Notes: Lowćvoltage Differential Signaling (LVDS)Abhishek SinghОценок пока нет

- Chip IO Circuit Design - Input Ouput CircuitryДокумент9 страницChip IO Circuit Design - Input Ouput CircuitryVăn CôngОценок пока нет

- ADAS ASSIGNMENT FinalДокумент14 страницADAS ASSIGNMENT FinalshubhamformeОценок пока нет

- Model Based Development of Future Small Electric Vehicle by ModelicaДокумент8 страницModel Based Development of Future Small Electric Vehicle by ModelicashubhamformeОценок пока нет

- ADAS Assignment ReportДокумент11 страницADAS Assignment ReportshubhamformeОценок пока нет

- Msa 0386 Lns For ArmyДокумент4 страницыMsa 0386 Lns For ArmyshubhamformeОценок пока нет

- Quick Start Guide: Mplab Pickit 4 In-Circuit DebuggerДокумент2 страницыQuick Start Guide: Mplab Pickit 4 In-Circuit DebuggershubhamformeОценок пока нет

- Jio Apn SettingsДокумент1 страницаJio Apn SettingsshubhamformeОценок пока нет

- National Train Enquiry System: 12612 Nzm-Mas Garib Rath Exp Garib Rath 12434 Nzm-Mas Rajdhani Exp RajdhaniДокумент1 страницаNational Train Enquiry System: 12612 Nzm-Mas Garib Rath Exp Garib Rath 12434 Nzm-Mas Rajdhani Exp RajdhanishubhamformeОценок пока нет

- Micro908 Schematic B1 0427Документ2 страницыMicro908 Schematic B1 0427shubhamformeОценок пока нет

- Mplab Snap In-Circuit Debugger Mplab Snap In-Circuit Debugger Information SheetДокумент12 страницMplab Snap In-Circuit Debugger Mplab Snap In-Circuit Debugger Information SheetshubhamformeОценок пока нет

- ARDUINO RF Power & SWR Meter: How To Calibrate The Power Indication ?Документ11 страницARDUINO RF Power & SWR Meter: How To Calibrate The Power Indication ?shubhamformeОценок пока нет

- Homebrewing HFI 2016 SWR Meter: SP BhatnagarДокумент22 страницыHomebrewing HFI 2016 SWR Meter: SP BhatnagarshubhamformeОценок пока нет

- PickitДокумент1 страницаPickitshubhamformeОценок пока нет

- Dr. Reckeweg Reference Guide - United RemediesДокумент4 страницыDr. Reckeweg Reference Guide - United RemediesshubhamformeОценок пока нет

- Ibm Thinkpad R51/R40 Notebooks: Mainstream Performance and FeaturesДокумент4 страницыIbm Thinkpad R51/R40 Notebooks: Mainstream Performance and FeaturesshubhamformeОценок пока нет

- EasyDigi Schematic PDFДокумент1 страницаEasyDigi Schematic PDFshubhamformeОценок пока нет

- 2m BP Filter-Yu1lmДокумент5 страниц2m BP Filter-Yu1lmshubhamformeОценок пока нет

- Smallest Petrol Generator in The WorldДокумент24 страницыSmallest Petrol Generator in The WorldshubhamformeОценок пока нет

- Excellent SWR MeterДокумент3 страницыExcellent SWR Metershubhamforme100% (1)

- Log Farm Bifoundation Domain Oracle Ias FarmДокумент19 страницLog Farm Bifoundation Domain Oracle Ias Farmahmed_sftОценок пока нет

- ECE467: To Vlsi Design: Lecture-1Документ27 страницECE467: To Vlsi Design: Lecture-1Rohan JainОценок пока нет

- School Management System: Submitted By: Muhammad Kaleem Ullah Hamza UmarДокумент32 страницыSchool Management System: Submitted By: Muhammad Kaleem Ullah Hamza UmarwalterОценок пока нет

- Ccna Sec 1.1Документ231 страницаCcna Sec 1.1loffy hackerОценок пока нет

- Optimization of Delay IIN Pipeline Mac Unit Using Wallace Tree MultiplierДокумент9 страницOptimization of Delay IIN Pipeline Mac Unit Using Wallace Tree MultiplierIJRASETPublicationsОценок пока нет

- Instruction of The Software MPE-822R - 825RДокумент2 страницыInstruction of The Software MPE-822R - 825RRoberto TorresОценок пока нет

- Design of CNC Machine Based Laser Engraver With Arduino UNOДокумент7 страницDesign of CNC Machine Based Laser Engraver With Arduino UNOIJRASETPublicationsОценок пока нет

- Artemis TrainingДокумент5 страницArtemis TrainingAgellos KoursarisОценок пока нет

- APC 10 Instruction Manual PDFДокумент64 страницыAPC 10 Instruction Manual PDFELSAKHWAYОценок пока нет

- File DelДокумент9 страницFile DelGabrielОценок пока нет

- Process ListДокумент3 страницыProcess ListAnonymous BJdOLuABОценок пока нет

- Professional Summary:: Ramana : +919677095107Документ4 страницыProfessional Summary:: Ramana : +919677095107raamanОценок пока нет

- HPE Version Control Repository Manager - HPE SupportДокумент2 страницыHPE Version Control Repository Manager - HPE SupportSandip AjaniОценок пока нет

- 15.2 Logic Circuits, Boolean Algebra, FlipFlopДокумент11 страниц15.2 Logic Circuits, Boolean Algebra, FlipFlopkimОценок пока нет

- Eventide H910-HK941 Harmonizer ManualДокумент11 страницEventide H910-HK941 Harmonizer ManualAlex HAIKINEОценок пока нет

- WP 001 SCADApolletДокумент13 страницWP 001 SCADApolletabdel taibОценок пока нет

- Features: Subordinate New BrandДокумент6 страницFeatures: Subordinate New BrandIleanaОценок пока нет

- Automatic TransmissionДокумент5 страницAutomatic Transmissionolyga mgolОценок пока нет

- Acm 2010Документ16 страницAcm 2010Mxplatform Mx PlatformОценок пока нет

- 7.sap - Abap 2Документ15 страниц7.sap - Abap 2mlp mlpОценок пока нет

- SMD Type IC: Low Dropout Linear Regulator AMS1117-X.XДокумент3 страницыSMD Type IC: Low Dropout Linear Regulator AMS1117-X.XcarlosmarciosfreitasОценок пока нет

- MSDN Mag 0710Документ102 страницыMSDN Mag 0710AlexandreОценок пока нет

- Adc 128 S 022Документ29 страницAdc 128 S 022Subhrajit MitraОценок пока нет

- Lvlog2019 08 28 23 04 39Документ4 страницыLvlog2019 08 28 23 04 39Brain Magdaleno DazaОценок пока нет

- Microcontroller 8051, Instruction SetДокумент140 страницMicrocontroller 8051, Instruction Setgopir28Оценок пока нет

- Bus Reservation System Using C++Документ4 страницыBus Reservation System Using C++Omar OubahaОценок пока нет

- 1U 17" LCD Monitor USB KVM Keyboard Drawer W/ 8-Port Switches, Optional Touch Pad (Model: NVP117-S801e) & Trackball (Model: NVP117-S801b)Документ5 страниц1U 17" LCD Monitor USB KVM Keyboard Drawer W/ 8-Port Switches, Optional Touch Pad (Model: NVP117-S801e) & Trackball (Model: NVP117-S801b)Franklin SolanoОценок пока нет

- Regin Regio Midi EngДокумент2 страницыRegin Regio Midi EngMc EswaranОценок пока нет

- Global Cache: Installation and Operations GuideДокумент27 страницGlobal Cache: Installation and Operations GuideNakendra DhamiОценок пока нет

- Tableau VM Tuning and Best PracticesДокумент6 страницTableau VM Tuning and Best Practicessrikanth_4allОценок пока нет