Академический Документы

Профессиональный Документы

Культура Документы

Amplificador Irs2092 PDF

Загружено:

Tiago MizaelОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Amplificador Irs2092 PDF

Загружено:

Tiago MizaelАвторское право:

Доступные форматы

IRAUDAMP7S

25W-500W Scalable Output Power

Class D Audio Power Amplifier Reference Design

Using the IRS2092S Protected Digital Audio Driver

By

Jun Honda, Manuel Rodríguez, Liwei Zheng

CAUTION:

International Rectifier suggests the following guidelines for safe operation and handling of

IRAUDAMP7S Demo Board:

• Always wear safety glasses whenever operating Demo Board

• Avoid personal contact with exposed metal surfaces when operating Demo Board

• Turn off Demo Board when placing or removing measurement probes

www.irf.com IRAUDAMP7S REV 1.3 Page 1 of 42

Item Table of Contents Page

1 Introduction of scalable design ………………………………………………….. 3

2 Power table values for each power model……………………………………… 4

3 Specifications……………………………………………………………………… 4-5

4 Connection setup…………………………………………………………………. 6

5 Test procedure…………………………………………………………………..… 7

6 Performance and test graphs………………………………………………….… 8-13

7 Clipping characteristics…………………………………………………………… 14

8 Efficiency…………………………………………………………………………… 14-16

9 Thermal considerations……………………………………………...…………… 16

10 PSRR, half bridge, full bridge……………………………………………………. 16-17

11 Short circuit response…………………………………………………………….. 17-18

12 IRAUDAMP7S Overview……………………………………………………….… 18-19

13 Functions Descriptions…………………………………………………………… 20-22

14 Selectable dead Time…………………………………..………………………… 22

15 Protection Features……………………………………………..………………… 23-25

16 Click and pop noise control………………………………………….…………… 25

17 Bus pumping…………………………………………………….………………… 26-27

18 Bridged configuration……………………………………….……..……………… 27

19 Input signal and Gain……………………………………….……………………. 29

20 Gain settings………………………………………………………………………. 29

21 Schematics………………………………………………………………………… 30-32

22 Bill of Materials………………………………………………………………..…… 33-36

23 IRAUDAMP7S models differential table………………………………………... 37

24 Hardware…………………………………………………………………………… 38-39

25 PCB specifications………………………………………………………………… 40

26 Assembly Drawings………………………………………………………….…… 41

27 Revision changes descriptions………………………………………………….. 42

www.irf.com IRAUDAMP7S REV 1.3 Page 2 of 42

Introduction

The IRAUDAMP7S reference design is a two-channel Class D audio power amplifier that features output

power scalability. The IRAUDAMP7S offers selectable half-bridge (stereo) and full-bridge (bridged) modes.

This reference design demonstrates how to use the IRS2092 Class D audio driver IC, along with IR’s digital

audio dual MOSFETs, such as IRFI4024H-117P, IRFI4019H-117P, IRFI4212H-117P and IRFI4020H-117P,

on a single layer PCB. The design shows how to implement peripheral circuits on an optimum PCB layout

using a single sided board.

The resulting design requires a small heatsink for normal operation (one-eighth of continuous rated power).

The reference design provides all the required housekeeping power supplies and protections.

Unless otherwise noted, this user’s manual is based on 150V model, IRAUDAMP7S-150.

Other output power versions can be configured by replacing components given in the component selection

of Table 5 on page 36

Applications

• AV receivers

• Home theater systems

• Mini component stereos

• Powered speakers

• Sub-woofers

• Musical Instrument amplifiers

• Automotive after market amplifiers

Features

Output Power: Scalable output power from 25W- 500W (see Table 1)

Residual Noise: 200 μV, IHF-A weighted, AES-17 filter

Distortion: 0.007 % THD+N @ 60W, 4 Ω

Efficiency: 90 % @ 500W, 8 Ω, Class D stage

Multiple Protection Features: Over-current protection (OCP), high side and low side MOSFET

Over-voltage protection (OVP),

Under-voltage protection (UVP), high side and low side MOSFET

DC-protection (DCP),

Over-temperature protection (OTP)

PWM topology: Self-oscillating PWM, half-bridge or full-bridge topologies selectable

www.irf.com IRAUDAMP7S REV 1.3 Page 3 of 42

Table 1 IRAUDAMP7S Specification Table Series

Model Name

Item AMP7S-55 AMP7S-100 AMP7S-150 AMP7S-200

IR Power FET1A,

IRFI4024H-117P IRFI4212H-117P IRFI4019H-117P IRFI4020H-117P

MOSFET FET1B

8Ω 25W x 2 60W x 2 125W x 2 250W x 2

Half Bridge

4Ω 50W x 2 120W x 2 250W x 2 Not Supported

Full Bridge 8Ω 100W x 1 240W x 1 500W x 1 Not Supported

Nominal

Supply +B, -B ±25V ±35V ±50V ±70V

Voltage

Min/Max

Supply +B, -B ±20V ~ ±28V ±28V ~ ±45V ±45V ~ ±60V ±60V ~ ±80V

Voltage

Voltage

Gv 20 30 36 40

Gain

Notes:

• All the power ratings are at clipping power (THD+N = 1 %). To estimate power ratings at

THD+N=10%, multiply them by 1.33

• See Table 5 on page 36 for the complete listing of components table.

Specifications

General Test Conditions for IRAUDAMP7S-150 (unless otherwise noted) Notes / Conditions

Power Supply Voltages ± 50V

Load Impedance 4Ω

Self-Oscillating Frequency 400kHz

Voltage Gain 36

Electrical Data Typical Notes / Conditions

IR Devices Used IRS2092, Protected digital audio driver

IRFI4024H-117P, IRFI4019H-117P, IRFI4212H-117P, IRFI4020H-

117P Digital audio MOSFETs

PWM Modulator Self-oscillating, second order sigma-delta modulation, analog input

Power Supply Range ± 45V to ± 60V Or see table 1 above

Output Power CH1-2: (1 % THD+N) 300W 1kHz

Output Power CH1-2: (10 % THD+N) 400W 1kHz

Rated Load Impedance 8-4Ω Resistive load

Standby Supply Current +50 mA/-80 mA No input signal

Total Idle Power Consumption 7W No input signal

Channel Efficiency 90 % Single-channel driven, 250W

.

www.irf.com IRAUDAMP7S REV 1.3 Page 4 of 42

Audio Performance

Before Class D Notes / Conditions

Demodulator Output

THD+N, 1W 0.01 % 0.02 %

THD+N, 10W 0.005 % 0.007 % 1kHz, Single-channel driven

THD+N, 60W 0.005 % 0.007 %

THD+N, 100W 0.007 % 0.008 %

A-weighted, AES-17 filter,

Dynamic Range 101 dB 101 dB

Single-channel operation

22 Hz – 20kHz, AES17 filter

Residual Noise 200 μV 200 μV Self-oscillating frequency

400kHz

Damping Factor 2000 120 1kHz, relative to 4 Ω load

95 dB 90 dB 100Hz

Channel Separation 85 dB 80 dB 1kHz

75 dB 65 dB 10kHz

Frequency Response : 20 Hz- ±3 dB

20 Hz-35kHz 1W, 4 Ω – 8 Ω Load

20kHz

Thermal Performance (TA=25 °C)

Condition Typical Notes / Conditions

TC =30 °C

Idling No signal input

TPCB=37 °C

TC =54 °C

2 ch x 31W (1/8 rated power)

TPCB=67 °C

TC =80 °C

2 ch x 250W (Rated power) OTP shutdown after 150 s

TPCB=106 °C

Physical Specifications

Dimensions 5.7”(L) x 4”(W) x 1.25”(H)

145 mm (L) x 100 mm (W) x 35 mm(H)

Weight 0.330kgm

www.irf.com IRAUDAMP7S REV 1.3 Page 5 of 42

Test Setup

+B, 5A DC supply -B, 5A DC supply

4 Ohm 4 Ohm

G

SPK1A CNN1 SPK1B

LED1 LED1

A B

S1

LED2 LED2

A BS300

RCA1A RCA1B

Audio Signal

Fig 1 Typical Test Setup

Connector Description

CH1 IN RCA1A Analog input for CH1

CH2 IN RCA1B Analog input for CH2

SUPPLY CNN1 Positive and negative supply (+B / -B)

CH1 OUT SPK1A Output for CH1

CH2 OUT SPK1B Output for CH2

Switches Descriptions

S1 Shutdown PWM

S300 Half bridge / Full bridge select

Indicator Description

LED1A, B PWM (presence of low side gate signal)

LED2A,B Protection

www.irf.com IRAUDAMP7S REV 1.3 Page 6 of 42

Test Procedures

Test Setup:

1. On the unit under test (UUT), set switch S1 to OFF and S300 to Stereo positions.

2. Connect 4 Ω-200 W dummy loads to output connectors, SPKR1A and SPKR1B, as shown

on Fig 1.

3. Set up a dual power supply ±50V with 5A current limit

4. Turn OFF the dual power supply before connecting to UUT.

5. Connect the dual power supply to CNN1, as shown in Fig 1.

Power up:

6. Turn ON the dual power supply. The ±B supplies must be applied and removed at the

same time.

7. The red LEDs (Protections) turn ON immediately and stay on as long as S1 is in OFF

position. Blue LEDs stay OFF.

8. Quiescent current for the positive and negative supplies must be less than 50mA, while S1

is in OFF position. Under this condition, IRS2092 is in shutdown mode.

9. Slide S1 to ON position; after one second delay, the two blue LEDs turn ON and the red

LEDs turns off. The two blue LEDs indicate that PWM oscillation is present. This transition

delay time is controlled by CSD pin of IRS2092, capacitor CP3

10. Under the normal operating condition with no input signal applied, quiescent current for the

positive supply must be less than 50 mA; the negative supply current must be less than

100 mA.

Switching Frequency Test:

11. With an oscilloscope, monitor switching waveform at test points VS1 & VS2 Adjust P1A &

P1B to change self oscillating frequency to 400kHz ± 25kHz.

Note: To change self-oscillating switching frequency, Adjust the potentiometer

resistances of P11A and P11B for CH1 and CH2 respectively.

Audio Functionality Tests:

12. Set the signal generator to 1kHz, 20 mVRMS output.

13. Connect audio signal generators to RCA1A and RCA1B.

14. Sweep the audio signal voltage from 15 mVRMS to 1 VRMS.

15. Monitor the output signals at SPK1A/B with an oscilloscope. Waveform must be a non

distorted sinusoidal signal.

16. Observe 1 VRMS input generates output voltage of 36 VRMS. The ratio, R8/(R7+R2),

determines the voltage gain of IRAUDAMP7S.

17. Set switch S300 to Bridged position.

18. Observe that voltage gain doubles.

www.irf.com IRAUDAMP7S REV 1.3 Page 7 of 42

Test Setup using Audio Precision (Ap):

19. Use unbalance-floating signal generator outputs.

20. Use balanced inputs taken across output terminals, SPKR1A and SPKR1B.

21. Connect Ap frame ground to GND in terminal CNN1.

22. Place AES-17 filter for all the testing except frequency response.

23. Use signal voltage sweep range from 15 mVRMS to 1 VRMS.

24. Run Ap test programs for all subsequent tests as shown in Fig 2- Fig 13 below.

Test Results

10

5

2

1

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

100m 200m 500m 1 2 5 10 20 50 100

W

Red = CH1, Blue = CH2

±B Supply = ±25V, 4 Ω Resistive Load

Fig 2 IRAUDAMP7S-55, THD+N versus Power, Stereo, 4 Ω

www.irf.com IRAUDAMP7S REV 1.3 Page 8 of 42

10

5

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

100m 200m 500m 1 2 5 10 20 50 100 200

W

Red = CH1, Blue = CH2

±B Supply = ±35V, 4 Ω Resistive Load

Fig 3 IRAUDAMP7S-100, THD+N versus Power, Stereo, 4 Ω

.

10

5

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

100m 200m 500m 1 2 5 10 20 50 100 200 500

W

±B Supply = ±35V, 8 Ω Resistive Load, Bridged

Fig 4 IRAUDAMP7S-100, THD+N versus Power, Bridged, 8 Ω

www.irf.com IRAUDAMP7S REV 1.3 Page 9 of 42

.

10

5

2

1

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

100m 200m 500m 1 2 5 10 20 50 100 200 500

W

Red = CH1, Blue = CH2

±B Supply = ±50V, 4 Ω Resistive Load

Fig 5 IRAUDAMP7S-150, THD+N versus Power, Stereo, 4 Ω

.

10

5

2

1

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

100m 200m 500m 1 2 5 10 20 50 100 200 700

W

±B Supply = ±50V, 8 Ω Resistive Load

Fig 6 IRAUDAMP7S-150, THD+N versus Power, Bridged 8 Ω

www.irf.com IRAUDAMP7S REV 1.3 Page 10 of 42

.

+4

+2

+0

d

-2

B

r

-4

A

-6

-8

-10

20 50 100 200 500 1k 2k 5k 10k 20k 50k 100k 200k

Hz

Red CH1 - 4 Ω, 2 V Output referenced

Blue CH1 - 8 Ω, 2 V Output referenced

Fig 8 Frequency Response (All Models)

www.irf.com IRAUDAMP7S REV 1.3 Page 11 of 42

10

T

5

0.5

0.2

% 0.1

0.05

0.02

0.01

0.005

0.002

0.001

20 50 100 200 500 1k 2k 5k 10k 20k

Hz

Red CH1, 10W Output

Blue CH1, 50W Output

Fig 9 IRAUDAMP7S-150, THD+N versus Frequency, 4Ω

+0

-10

-20

-30

-40

d -50

B

V -60

-70

-80

-90

-100

-110

20 50 100 200 500 1k 2k 5k 10k 20k

Hz

Red = CH1, Blue = CH2

1V Output

Fig 10 IRAUDAMP7S-150, 1 kHz – 1 V Output Spectrum, Stereo

.

www.irf.com IRAUDAMP7S REV 1.3 Page 12 of 42

+0

-10

-20

-30

-40

d -50

B

V -60

-70

-80

-90

-100

-110

20 50 100 200 500 1k 2k 5k 10k 20k

Hz

1V Output

Fig 11 IRAUDAMP7S-150, 1 kHz - 1V Output Spectrum, Bridged

.

+20

+0

-20

-40

d -60

B

V

-80

-100

-120

-140

10 20 50 100 200 500 1k 2k 5k 10k 20k

Hz

Red CH1 - ACD, No signal, Self Oscillator @ 400kHz

Blue CH2 - ACD, No signal, Self Oscillator @ 400kHz

Fig 12 IRAUDAMP7S-150 Noise Floor

.

www.irf.com IRAUDAMP7S REV 1.3 Page 13 of 42

Clipping characteristics

Red Trace: Total Distortion + Noise Voltage

Gold Trace: Output Voltage

210 W / 4 Ω, 1 kHz, THD+N = 0.02 % 310 W / 4 Ω, 1 kHz, THD+N = 10 %

Measured Output and Distortion Waveforms

Fig 13 Clipping Characteristics

.

Efficiency

Figs 14-19 show efficiency characteristics of the IRAUDAMP7S. The high efficiency is achieved by

following major factors:

1) Low conduction loss due to the dual FETs offering low RDS(ON)

2) Low switching loss due to the dual FETs offering low input capacitance for fast rise and fall

times

3) Secure dead-time provided by the IRS2092, avoiding cross-conduction

100%

90%

80%

70%

Efficiency (%)

60%

25V-4ohms

50%

40%

30%

20%

10%

0%

0 10 20 30 40 50 60

Output power (W)

±B Supply = ±25 V

Fig 14 Efficiency versus Output Power, IRAUDAMP7S-55, 4 Ω, Stereo

www.irf.com IRAUDAMP7S REV 1.3 Page 14 of 42

100%

90%

80%

Efficiency (%)

70%

60%

35V-4ohms

50%

40%

30%

20%

10%

0%

0 20 40 60 80 100 120 140 160

Output power (W)

±B Supply = ±35 V

Fig 15 Efficiency versus Output Power, IRAUDAMP7S-100, 4 Ω, Stereo

100%

90%

80%

70%

Efficiency (%)

60%

50%

35V-8ohms-Full bridge

40%

30%

20%

10%

0%

0 50 100 150 200 250 300

Output power (W)

±B Supply = ±35V

Fig 16 Efficiency versus Output Power, IRAUDAMP7S-100, 8 Ω, Bridged

90%

80%

70%

Efficiency (%)

60%

50% 50V-4ohms

40%

30%

20%

10%

0%

0 50 100 150 200 250 300

Output power (W)

±B Supply = ±50V

Fig 17 Efficiency versus Output Power, IRAUDAMP7S-150, 4 Ω, Stereo

www.irf.com IRAUDAMP7S REV 1.3 Page 15 of 42

.

100%

90%

80%

70%

Efficiency (%)

60%

50%

50V-8ohms-Full bridge

40%

30%

20%

10%

0%

0 50 100 150 200 250 300 350 400 450 500 550

Output power (W)

±B Supply = ±50V

Fig 18 Efficiency versus Output Power, IRAUDAMP7S-150, 8 Ω, Bridged

100%

90%

80%

70%

Efficiency (%)

60%

70V-8ohms

50%

40%

30%

20%

10%

0%

0 50 100 150 200 250 300

Output power (W)

±B supply = ±70V

Fig 19 Efficiency versus Output Power, IRAUDAMP7S-200, 8 Ω, Stereo

Thermal Considerations

With this high efficiency, the IRAUDAMP7S design can handle one-eighth of the continuous rated

power, which is generally considered to be a normal operating condition for safety standards,

without additional heatsink or forced air-cooling.

Power Supply Rejection Ratio (PSRR)

The IRAUDAMP7S obtains good power supply rejection ratio of -65 dB at 1kHz shown in Fig 20.

With this high PSRR, IRAUDAMP7S accepts any power supply topology as far as the supply

voltages fit in the min and max range.

www.irf.com IRAUDAMP7S REV 1.3 Page 16 of 42

Red: VAA & VSS are fed by +/-B bus

Green: VAA & VSS are fed by external +/-5 V regulated power supplies.

Fig 20 IRAUDAMP7S Power Supply Rejection Ratio

Short Circuit Protection Response

Figs 21-23 show over current protection reaction time of the IRAUDAMP7S in a short circuit event.

As soon as the IRS2092 detects over current condition, it shuts down PWM. After one second, the

IRS2092 tries to resume the PWM. If the short circuit persists, the IRS2092 repeats try and fail

sequences until the short circuit is removed.

Short Circuit in Positive and Negative Load Current

CSD pin CSD pin

VS pin Positive OCP VS pin Load current

Load current Negative OCP

Fig 21 Positive and Negative OCP Waveforms

.

www.irf.com IRAUDAMP7S REV 1.3 Page 17 of 42

OCP Waveforms Showing CSD Trip and Hiccup

CSD pin CSD pin

VS pin VS pin

Load current

Load current

Fig 22 OCP Response with Continuous Short Circuit

Actual Reaction Time

OCP Waveforms Showing actual reaction time

Fig. 23 High and Low Side OCP current waveform reaction time

IRAUDAMP7S Overview

The IRAUDAMP7S features a self-oscillating type PWM modulator for the lowest component

count, highest performance and robust design. This topology represents an analog version of a

second-order sigma-delta modulation having a Class D switching stage inside the loop. The

www.irf.com IRAUDAMP7S REV 1.3 Page 18 of 42

benefit of the sigma-delta modulation, in comparison to the carrier-signal based modulation, is that

all the error in the audible frequency range is shifted to the inaudible upper-frequency range by

nature of its operation. Also, sigma-delta modulation allows a designer to apply a sufficient

amount of error correction.

The IRAUDAMP7S self-oscillating topology consists of following essential functional blocks.

• Front-end integrator

• PWM comparator

• Level shifters

• Gate drivers and MOSFETs

• Output LPF

Integrator

Referring to Fig 24 below, the input operational amplifier of the IRS2092 forms a front-end second-

order integrator with R7, C4, C6, P1, and R11. The integrator that receives a rectangular feedback

signal from the PWM output via R8 and audio input signal via R7 generates quadratic carrier

signal in COMP pin. The analog input signal shifts the average value of the quadratic waveform

such that the duty cycle varies according to the instantaneous voltage of the analog input signal.

PWM Comparator

The carrier signal in COMP pin is converted to PWM signal by an internal comparator that has

threshold at middle point between VAA and VSS. The comparator has no hysteresis in its input

threshold.

Level Shifters

The internal input level-shifter transfers the PWM signal down to the low-side gate driver section.

The gate driver section has another level-shifter that level shifts up the high-side gate signal to the

high-side gate driver section.

Gate Drivers and MOSFETs

The received PWM signal is sent to the dead-time generation block where a programmable

amount of dead time is added into the PWM signal between the two gate output signals of LO and

HO to prevent potential cross conduction across the output power MOSFETs. The high-side level-

shifter shifts up the high-side gate drive signal out of the dead-time block.

The IRS2092 drives two MOSFETs, high- and low-sides, in the power stage providing the

amplified PWM waveform.

www.irf.com IRAUDAMP7S REV 1.3 Page 19 of 42

Output LPF

The amplified PWM output is reconstructed back to analog signal by the output LC LPF.

Demodulation LC low-pass filter (LPF) formed by L1 and C12, filters out the Class D switching

carrier signal leaving the audio output at the speaker load. A single stage output filter can be used

with switching frequencies of 400 kHz and greater; a design with a lower switching frequency may

require an additional stage of LPF.

.

R8

R117

+B

CP4

0V

+VAA +B

0V

C4 C6 VB

COMP

IRS2092 -B

HO R24

0V

R11

C7

LP Filter 0V

R7

IN- CP6

INPUT - Modulator

VS

and

. + FET1 L1

D3

Shift level

GND VCC IRFI4024H-117P C12

IRFI4212H-117P .

Integrator LO R25 IRFI4019H-117P

IRFI4020H-117P

+VCC

-VSS COM

CP5

CP2

-B

R118

.

Fig 24 Simplified Block Diagram of IRAUDAMP7S Class D Amplifier

Functional Descriptions

IRS2092 Gate Driver IC

The IRAUDAMP7S uses IRS2092, a high-voltage (up to 200 V), high-speed power MOSFET

driver with internal dead-time and protection functions specifically designed for Class D audio

amplifier applications. These functions include OCP and UVP. The IRS2092 integrates bi-

directional over current protection for both high-side and low-side MOSFETs. The dead-time can

be selected for optimized performance according to the size of the MOSFET, minimizing dead-

time while preventing shoot-through. As a result, there is no gate-timing adjustment required

externally. Selectable dead-time through the DT pin voltage is an easy and reliable function which

requires only two external resistors, R26 and R27 as shown on Fig 25 below.

www.irf.com IRAUDAMP7S REV 1.3 Page 20 of 42

The IRS2092 offers the following functions.

• PWM modulator

• Dead-time insertion

• Over current protection

• Under voltage protection

• Level shifters

Refer to IRS2092 datasheet and AN-1138 for more details.

VS1

Feedback +B

R8 R117

*120k 1%

*3.3k 1w

RCA1 RCA1 CP1

R2 R7 R17

330 *3.01K 1% R22 *47k

22uF +B

C2 10k R18

1nF

U1 C11

150pF,250V

*9.1k D4 CP8

R1 100k +VAA

CP4 R19 0.1uF,100V

C9

1 16 *470uF,100V

VAA CSH C10

Z103 10k FET1

2K POT

CP6 *IRFI4019H-117P

P1 R11

22uF 2 15

5.6V GND VB

5

HS1

0.1uF,400V

R14 100R 22uF +B

R29

4.7k R24

3 14 4

CSD1

IN- HO

20R

L1

22uH

CH1 OUT

*MUR120RLG

3 FET2

10R

RED 1 1nF 1nF CH_OUT SPKR1

C7 1nF D5

PROT BS250F

4

COMP VS

13 3

1

+

2

CH1

R3 C4 C6

C12 R30 R31

-

2

10R

R28

5 12 D3 D6

SD CSD VCC R20 0.47uF, 400V 10, 1W 2.2k

D1 100R

*470uF,100V

CP3 10uF -B

150pF,250V

4.7R R25

0.1uF,100V

6 11 2 *MUR120RLG

CP7

C14

VSS LO

C8

C13

Z104 R118 CP2 20R 0.1uF, 400V

5.6V *3.3k 1W 22uF R13 7 10

VREF COM

1

10k R21 R23 LED1

-B

8 9 R26

OCSET DT 10R 10k Blue

10k

R12 IRS2092S 3 2 R114

*7.5k R27 VCC

CP5 *1k 1W

10k 22uF TIP31C

Q105

Z102 R115

1

15V *15k

-B

CP101 22uF

Fig 25 System-level View of IRAUDAMP7S

Self-Oscillating Frequency

Self-oscillating frequency is determined by the total delay time along the control loop of the

system; the propagation delay of the IRS2092, the MOSFETs switching speed, the time-constant

of front-end integrator (P1, R7, R11 R8, C4, C6, C7). Variations in +B and –B supply voltages

also affect the self-oscillating frequency.

The self-oscillating frequency changes with the duty ratio. The frequency is highest at idling. It

drops as duty cycle varies away from 50%.

www.irf.com IRAUDAMP7S REV 1.3 Page 21 of 42

Adjustments of Self-Oscillating Frequency

Use P1 & R11 to set different self-oscillating frequencies. The PWM switching frequency in this

type of self-oscillating switching scheme greatly impacts the audio performance, both in absolute

frequency and frequency relative to the other channels. In the absolute terms, at higher

frequencies distortion due to switching-time becomes significant, while at lower frequencies, the

bandwidth of the amplifier suffers. In relative terms, interference between channels is most

significant if the relative frequency difference is within the audible range.

Normally, when adjusting the self-oscillating frequency of the different channels, it is suggested to

either match the frequencies accurately, or have them separated by at least 25kHz. Under the

normal operating condition with no audio input signal, the switching-frequency is set around

400kHz in the IRAUDAMP7S.

Selectable Dead-time

The dead-time of the IRS2092 is set based on the voltage applied to the DT pin. Fig 26 lists the

suggested component value for each programmable dead-time between 25 and 105 ns.

All the IRAUDAMP7S models use DT2 (45ns) dead-time.

Dead-time Mode R1 R2 DT/SD Voltage

DT1 <10k Open Vcc

DT2 5.6kΩ 4.7kΩ 0.46 x Vcc

DT3 8.2kΩ 3.3kΩ 0.29 x Vcc

DT4 Open <10k COM

Recommended Resistor Values for Dead Time Selection

Dead- time

IRS2092(S)

25nS

>0.5mA

Vcc

45nS

R1

75nS

DT

105nS

R2

0.23xVcc 0.36xVcc 0.57xVcc Vcc

VDT COM

Fig 26 Dead-time Settings vs. VDT Voltage

Protection System Overview

www.irf.com IRAUDAMP7S REV 1.3 Page 22 of 42

The IRS2092 integrates over current protection (OCP) inside the IC. The rest of the protections,

such as over-voltage protection (OVP), under-voltage protection (UVP), speaker DC offset

protection (DCP) and over temperature protection (OTP), are realized externally to the IRS2092

(Fig 27).

In the event that any of these external fault conditions are detected, the external shutdown circuit

will disable the output by pulling down CSD pins, turning on red LEDs, and turning off blue LEDs

(Fig 28). If the fault condition persists, the protection circuit stays in shutdown until the fault is

removed. Once the fault is cleared, the blue LEDs turn on and red LEDs turn off.

TH100 is thermally connected with Heat sink

DCP

R108

CH1_OUT

100k

2N3906

TH100

OTP R109

Q102

2.2k

CH2_OUT

100k

R103

715R R110

R101

100k

2N3906

4.7k CP100

Q103

R104 2N3906

4.7k Q101 330uF, 10V

-VSS1

S1 2 +B +B

1

OVP

UVP

-VSS1 3

Z100 R111 Z101

4 *68V 10k *39V

5

6

SD SW DPDT

R102 R105 R106 R107 R112

10k 10k 10k 10k JW3 47K

2N3904

Q100

2N3904

C100

Q104

0.1uF

R113

10k

-VSS1

-VSS1

Fig 27 DCP, OTP, UVP and OVP Protection Circuits

.

.

R17

D4

CSH +B

R18 BAV19

+ VB

R19

1.2V HO

FET1

+VAA LP Filter

VS

. CSD .

FET2 CSD

VCC

CP3

PROT

RED

OCSET

LO

-VSS

OCREF BLUE

5.1V R13 R12 LED1

-B

OCREF OCSET COM

Fig 28 Simplified Functional Diagram of OCP and Associated LED Indicators

www.irf.com IRAUDAMP7S REV 1.3 Page 23 of 42

Over-Current Protection (OCP)

Low-Side Current Sensing

The low-side current sensing feature protects the low side MOSFET from an overload condition in negative

load current by measuring drain-to-source voltage across RDS(ON) during its on state. OCP shuts down the

switching operation if the drain-to-source voltage exceeds a preset trip level.

The voltage setting on the OCSET pin programs the threshold for low-side over-current sensing. When the

VS voltage during low-side conduction gets higher than the OCSET voltage, the IRS2092 turns off outputs

and pulls CSD down to -VSS.

High-Side Current Sensing

The high-side current sensing protects the high side MOSFET from an overload condition in

positive load current by measuring drain-to-source voltage across RDS(ON) during its on state. OCP

shuts down the switching operation if the drain-to-source voltage exceeds a preset trip level.

High-side over-current sensing monitors drain-to-source voltage of the high-side MOSFET while it

is in the on state through the CSH and VS pins. The CSH pin detects the drain voltage with

reference to the VS pin, which is the source of the high-side MOSFET. In contrast to the low-side

current sensing, the threshold of CSH pin to trigger OC protection is internally fixed at 1.2V. An

external resistive divider R19, R18 and R17 are used to program a threshold as shown in Fig 26.

An external reverse blocking diode D4 is required to block high voltage feeding into the CSH pin

during low-side conduction. By subtracting a forward voltage drop of 0.6V at D4, the minimum

threshold which can be set for the high-side is 0.6V across the drain-to-source.

Table 2 Actual OCP table setting thresholds

Function Device Amp7-55 Amp7-100 Amp7-150 Amp7-200

OCSET R12A

1.3K 3.9K 7.5K 5.1K

R12B

Tested OCP current 25oC 23A 30A 23A

CSH R18A

0.0 4.7K 9.1K 8.2K

R18B

Tested OCP current 25oC 23A 29A 23A

Peak load current

6.0A 8.7A 12.2A 8.9A

at rated power

Over-Voltage Protection (OVP)

OVP is provided externally to the IRS2092. OVP shuts down the amplifier if the bus voltage

between GND and +B exceeds 75V. The threshold is determined by a Zener diode Z100. OVP

www.irf.com IRAUDAMP7S REV 1.3 Page 24 of 42

protects the board from harmful excessive supply voltages, such as due to bus pumping at very

low frequency continuous output in stereo mode.

Under-Voltage Protection (UVP)

UVP is provided externally to the IRS2092. UVP prevents unwanted audible noise output from

unstable PWM operation during power up and down. UVP shuts down the amplifier if the bus

voltage between GND and +B falls below a voltage set by Zener diode Z101.

Speaker DC-Voltage Protection (DCP)

DCP protects speakers against DC output current feeding to its voice coil. DC offset detection

detects abnormal DC offset and shuts down PWM. If this abnormal condition is caused by a

MOSFET failure because one of the high-side or low-side MOSFETs short circuited and remained

in the on state, the power supply needs to be cut off in order to protect the speakers. Output DC

offset greater than ±4V triggers DCP.

Offset Null (DC Offset) Adjustment

The IRAUDAMP7S requires no output-offset adjustment. DC offsets are tested to be less than ±20

mV.

Over-Temperature Protection (OTP)

A NTC resistor, TH100 in Fig 25, is placed in close proximity to two dual MOSFETs on a heatsink

to monitor heatsink temperature. If the heatsink temperature rises above 100 °C, the OTP shuts

down both channels by pulling down CSD pins of the IRS2092. OTP recovers once the

temperature has cooled down.

ON-OFF Switch

OFF position of S1 forces the IRAUDAMP7S to stay in shutdown mode by pulling down the CSD

pin. During the shutdown mode the output MOSFETs are kept off.

Click and POP Noise Reduction

Thanks to the click and pop elimination function built into the IRS2092, IRAUDAMP7S does not

use any additional components for this function.

www.irf.com IRAUDAMP7S REV 1.3 Page 25 of 42

Power Supply Requirements

For convenience, the IRAUDAMP7S has all the necessary housekeeping power supplies onboard

and only requires a pair of symmetric power supplies. Power supply voltage depends on the model

and is shown in the power selection in Table 1.

House Keeping Power Supply

The internally-generated housekeeping power supplies include ±5.6V for analog signal processing,

and +12V supply (VCC) referred to negative supply rail -B for MOSFET gate drive. The VAA and

VSS supplying floating input section are fed from +B and -B power stage bus supplies via R117

and R118, respectively. Gate driver section of IRS2092 uses VCC to drive gates of MOSFETs.

The VCC is referenced to –B (negative power supply). D3 and CP6 form a bootstrap floating supply

for the HO gate driver.

Bus Pumping

When the IRAUDAMP7S is running in the stereo mode, bus pumping effect takes place with low

frequency high output. Since the energy flowing in the Class D switching stage is bi-directional,

there is a period where the Class D amplifier feeds energy back to the power supply. The majority

of the energy flowing back to the supply is from the energy stored in the inductor in the output LPF.

Usually, the power supply has no way to absorb the energy coming back from the load.

Consequently the bus voltage is pumped up, creating bus voltage fluctuations.

Following conditions make bus pumping worse:

1. Lower output frequencies (bus-pumping duration is longer per half cycle)

2. Higher power output voltage and/or lower load impedance (more energy transfers between

supplies)

3. Smaller bus capacitance (the same energy will cause a larger voltage increase)

The OVP protects IRAUDAMP7S from failure in case of excessive bus pumping. One of the

easiest counter measures of bus pumping is to drive both of the channels in a stereo configuration

out-of-phase so that one channel consumes the energy flow from the other and does not return it

to the power supply. Bus voltage detection monitors only +B supply, assuming the bus pumping

on the supplies is symmetric in +B and -B supplies.

There is no bus pumping effect in full bridge mode.

www.irf.com IRAUDAMP7S REV 1.3 Page 26 of 42

Cyan: Positive Rail voltage (+B), Green: Speaker Output, Pink: Negative Rail voltage (-B)

Fig 29 Bus Pumping in Half Bridge Mode

Bridged Configuration

By selecting S300 to Bridged position, the IRAUDAMP7S realizes full bridge mode, also known as

bridge-tied-load, or BTL configuration. Full bridge operation is achieved by feeding out-of-phase

audio input signals to the two input channels as shown in the Fig 30 below.

In bridged mode, IRAUDAMP7S receives audio input signal from channel A only. The on-board

inverter feed out-of-phase signal to Channel B. The speaker output must be connected between

(+) of Channel A and (+) of Channel B in bridged mode.

In bridged mode, nominal load impedance is 8 Ω. (See power table in Table 1)

.

C300 Bridged

R302

+VAA From Ch B

R301

100 CP1B+ S300 2

22k RCA2

0.1uF 1

1 U300 3

7

From Ch A 8 TL072CP

JW8 R300

2 4

RCA1

6 5

22k

3 6

5 SW DPDT

4

Steereo

C301

R303

-VSS

100

0.1uF

Fig 30 Bridged Configuration (BTL)

www.irf.com IRAUDAMP7S REV 1.3 Page 27 of 42

Load Impedance

Each channel is optimized for a 4 Ω speaker load in half bridge and 8 Ω load in full bridge.

Output Filter Selection

Since the output filter is not included in the control loop of the IRAUDAMP7S, the control loop has

no ability to compensate performance deterioration caused by the output filter. Therefore, it is

necessary to understand what characteristics are preferable when designing the output filter.

1) The DC resistance of the inductor should be minimized to 20 mΩ or less.

2) The linearity of the output inductor and capacitor should be high with output current and

voltage.

Fig 31 demonstrates THD performance difference with various inductors.

100

T T

10

% 0.1

0.01

0.001

0.0001

100m 200m 500m 1 2 5 10 20 50 100 200

W

Fig 31 THD+N vs. Output Power with Different kind of Output Inductors

www.irf.com IRAUDAMP7S REV 1.3 Page 28 of 42

Input Signal and Gain Setting

A proper input signal is an analog signal ranging from 20Hz to 20kHz with up to 3 VRMS amplitude

with a source impedance of no more than 600 Ω. Input signal with frequencies from 30kHz to

60kHz may cause LC resonance in the output LPF, causing a large reactive current flowing

through the switching stage, especially with greater than 8 Ω load impedances, and the LC

resonance can activate OCP.

The IRAUDAMP7S has an RC network called Zobel network (R30 and C13) to damp the

resonance and prevent peaking frequency response with light loading impedance. (Fig 32) The

Zobel network is not thermally rated to handle continuous supersonic frequencies above 20kHz.

These supersonic input frequencies can be filtered out by adding R2 and C2 as shown on main

schematic Fig 33 and Fig 34. This RC filter works also as an input RF filter to prevent potential

radio frequency interferences.

LP Filter 0V

.

0V L1 .

R30

C12

C13

.

Fig 32 Output Low Pass Filter and Zobel Network

Gain Setting

The ratio of resistors R8/R2 in Fig 33 sets voltage gain. The IRAUDAMP7S has no on board volume control.

To change the voltage gain, change the input resistor term R2. Changing R8 affects PWM control loop

design and may result poor audio performance.

www.irf.com IRAUDAMP7S REV 1.3 Page 29 of 42

VS1

Feedback +B

Note: R8 R117

R2 & C2 are RF filters, optional *120k 1%

*3.3k 1w

RCA1 RCA1 CP1

R2 R7 R17

330 *3.01K 1% R22 *47k

22uF +B

C2 10k R18

1nF

U1 CH1 C11

150pF,250V

*9.1k D4 CP8

R1 100k +VAA

CP4 R19 0.1uF,100V

C9

1 16 *470uF,100V

VAA CSH C10

Z103 10k FET1

2K POT

CP6 *IRFI4019H-117P

P1 R11

22uF 2 15

5.6V GND VB

0.1uF,400V

HS1

R14 100R 22uF +B

R29

4.7k R24

3 14 4

CSD1

IN- HO

20R

L1

22uH

CH1 OUT

*MUR120RLG

3 FET2

10R

RED 1 1nF 1nF CH_OUT SPKR1

C7 1nF D5

PROT BS250F

4

COMP VS

13 3

1 +

2 CH1

R3 C4 C6

C12 R30 R31

-

2

10R

R28

5 12 D3 D6

SD CSD VCC R20 0.47uF, 400V 10, 1W 2.2k

D1 100R

*470uF,100V

-VSS CP3 10uF -B

150pF,250V

4.7R

0.1uF,100V

R25

6 11 2 *MUR120RLG

CP7

C14

VSS LO

C8

C13

Z104 R118 CP2 20R 0.1uF, 400V

5.6V *3.3k 1W 22uF R13 7 10

VREF COM

1

10k R21 R23 LED1

-B

8 9 R26

OCSET DT 10R 10k Blue

10k

R12 IRS2092S 3 2 R114

*7.5k R27 VCC

CP5 *1k 1W

10k 22uF TIP31C

Q105

Z102 R115

1

15V *15k

-B

Note: Components values marked on red or * are according to power table

IRAUDAMP7-55, +B,-B are +/-25V with FET1 as IRFI4024H-117P CP101 22uF IRAUDAMP7S Rev 1.0

IRAUDAMP7-100, +B,-B are +/-35Vwith FET1 as IRFI4212H-117P

IRAUDAMP7-150, +B,-B are +/-50Vwith FET1 as IRFI4019H-117P

IRAUDAMP7-200, +B,-B are +/-70Vwith FET1 as IRFI4020H-117P

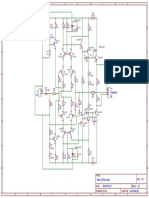

Fig 33 Amplifier Schematic, Channel 1 & Channel 2

.

www.irf.com IRAUDAMP7S REV 1.3 Page 30 of 42

JW2 TH1 is thermally connected with FET1

SD

JW3

SD

DCP R108

CH2_OUT

JW4

MMBT5401

100k

TH100

JW5 OTP TH2.2k R109 JW12

CH1_OUT

Q102

100k

JW7 R103

VCC VCC R110

715R

MMBT5401

JW8 R101 100k

-B -B

CP100

JW9 4.7k Q103

VCC VCC

R104 MMBT5401

JW10 4.7k Q101 330uF,10V

+B +B

-VSS

JW11 S1 2 +B +B

-B -B

1

-VSS 3

Z100 R111 Z101

4 *68V 10k *39V

5

6

SW DPDT

R102 R105 R106 R107 R112

OVP

UVP

SD 10k 10k 10k 10k 47k

MMBT5551

Q100

MMBT5551

C100

Q104

0.1uF

R113

10k

-VSS

-VSS

Note: Components values marked on red or * are according to power table

Fig 34 Protection Schematic

.

www.irf.com IRAUDAMP7S REV 1.3 Page 31 of 42

Bridged

S300 2

FromCh B

RCA2

1

CP1B+

3

4

5

JW1 6

C300

R302 SW DPDT Steereo

JW6

R301 +VAA

100

22k 0.1uF

1 U300

7

FromCh A R300

8 TLC081IDR

2

RCA1

6

22k

3

5

4

C301

R303

-VSS

100

0.1uF

Fig 35 Bridge Preamp Schematic

www.irf.com IRAUDAMP7S REV 1.3 Page 32 of 42

IRAUDAMP7S-150 Fabrication Materials

Table 3 IRAUDAMP7S-150 Electrical Bill of Materials

Quantity Value Description Designator Digikey P/N Vendor

8 1nF,250V CAP CER 1000PF 250V C0G C2A, C2B, C4A, C4B, 445-2325-1-ND TDK Corporation

5% C6A, C6B, C7A, C7B

4 150pF,250V CAP CER 150PF 250V U2J C8A, C8B, C9A, C9B 490-5025-1-ND Murata Electronics

4 0.1uF,400V CAP .10UF 400V METAL C10A, C10B, C13A, 495-1311-ND EPCOS Inc

POLYPRO C13B

4 0.1uF,100V CAP .10UF 100V CERAMIC C11A, C11B, C14A, PCC2239CT-ND Panasonic - ECG

X7R C14B

2 0.47uF, 400V CAP .47UF 400V METAL C12A, C12B 495-1315-ND EPCOS Inc

POLYPRO

3 0.1uF, 10V CAP CER 0.1UF 10V SL 5% C100, C300, C301 445-2686-1-ND TDK Corporation

1 ED365/3 TERMINAL BLOCK 7.50MM CONN1 ED2355-ND On Shore

3POS PCB Technology Inc

12 22uF CAP 22UF 25V ELECT VR CP1A, CP1B, CP2A, 493-1058-ND Nichicon

RADIAL CP2B, CP4A, CP4B,

CP5A, CP5B, CP6A,

CP6B, CP101A,

CP101B

2 10uF, 16V CAP ELECT 10UF 16V KS CP3A, CP3B P966-ND Panasonic - ECG

RADIAL

4 470uF,100V CAP 470UF 100V ELECT PW CP7A, CP7B, CP8A, 493-1985-ND Nichicon

RADIAL CP8B

1 330uF, 10V CAP 330UF 10V ALUM LYTIC CP100 P5125-ND Panasonic - ECG

RADIAL

2 Red LED LED 3MM HI-EFF RED CSD1A, CSD1B 160-1140-ND Lite-On Inc

TRANSPARENT

2 1N4148WS DIODE SWITCH 75V 200MW D1A, D1B 1N4148WS-FDICT-ND Diodes Inc

2 MURA120T3G DIODE ULTRA FAST 1A 200V D3A, D3B MURA120T3GOSCT- ON Semiconductor

ND

2 BAV19WS DIODE SWITCH 100V 200MW D4A, D4B BAV19WS-FDICT-ND Diodes Inc

4 MURA120T3G DIODE ULTRA FAST 1A 200V D5A, D5B, D6A, D6B MURA120T3GOSCT- ON Semiconductor

ND

2 IRFI4019H- IRFI4019H-117P, Dual FET1A, FET1B IR's Part No. International

117P MOSFET Rectifier

TO-220-5

2 BS250P MOSFET P-CH 45V 90MA FET2A, FET2B BS250FTC-ND Zetex Inc

1 Heat Sink Aluminum heat spreader HS1A Drawing IRHS_Amp1 Custom made

1 JW-300 Wire Jumper #20 AWG JW1 Custom Custom

insulated

3 JW-300 Wire Jumper #20 AWG JW2, JW4, JW10 Custom Custom

insulated

1 JW-1500 Wire Jumper #20 AWG JW3 Custom Custom

insulated

1 JW-1500 Wire Jumper #20 AWG JW5 Custom Custom

insulated

2 JW-1800 Wire Jumper #20 AWG JW6, JW7 Custom Custom

insulated

2 JW-2000 Wire Jumper #20 AWG JW8, JW9 Custom Custom

insulated

2 22uH, 13A Class D Inductor, 22UH L1A, L1B Sagami 7G17A-220M- Inductors, Inc.

R or

or ICE Components,

IN09063 Inc.

2 Blue LED LED 3MM DUAL FLANGE LED1A, LED1B 160-1600-ND LITE-ON INC

BLUE CLEAR

2 2K POT POTENTIOMETER P1A, P1B 3362H-202LF-ND Bourns Inc.

2 MMBT5551 TRANSISTOR NPN 160V Q100, Q104 MMBT5551FSCT-ND Fairchild

Semiconductor

www.irf.com IRAUDAMP7S REV 1.3 Page 33 of 42

3 MMBT5401 TRANS PNP 150V 350MW Q101, Q102, Q103 MMBT5401-FDICT-ND Diodes Inc

SMD

2 TIP31C TRANSISTOR NPN 100V 3A Q105A, Q105B 497-2615-5-ND STMicroelectronics

3 100k RES 100K OHM 1/8W 5% R1A, R1B, R110 RHM100KARCT-ND Rohm

1 330 RES 330 OHM 1/8W 1% R2A RHM330CRCT-ND Rohm

1 330 RES 330 OHM CARBON FILM R2B P330BACT-ND Panasonic - ECG

2 100R RES 100 OHM 1/8W 5% R3A, R3B P100ACT-ND Panasonic - ECG

2 3.01K RES 3.01K OHM 1/8W 1% R7A, R7B RHM3.01KCCT-ND Rohm

2 120k 1% RES METAL FILM 120K OHM R8A, R8B P120KCACT-ND Panasonic - ECG

1/4W

2 100R RES 100 OHM 1/8W 5% R11A, R11B RHM100ARCT-ND Rohm

2 7.5k RES 7.5K OHM 1/8W 5% R12A, R12B RHM7.5KARCT-ND Rohm

18 10k RES 10K OHM 1/8W 5% R13A, R13B, R19A, RHM10KARCT-ND Rohm

R19B, R22A, R22B,

R23A, R23B, R26A,

R26B, R27A, R27B,

R102, R105, R106,

R107, R111, R113

4 4.7k RES 4.7K OHM 1/8W 5% R14A, R14B, R101, RHM4.7KARCT-ND Rohm

R104

2 47k RES 47K OHM 1/8W 5% R17A, R17B RHM47KARCT-ND Rohm

2 9.1k RES 9.1K OHM 1/8W 5% R18A, R18B RHM9.1KARCT-ND Rohm

2 4.7R RES 4.7 OHM 1/4W 1% R20A, R20B P4.7RCT-ND Panasonic - ECG

2 10R RES 10.0 OHM 1/4W 1% R21A, R21B RHM10.0FRCT-ND Rohm

4 20R RES 20.0 OHM 1/8W 1% R24A, R24B, R25A, RHM20.0CRCT-ND Rohm

R25B

4 10R RES 10.0 OHM 1/8W 1% R28A, R28B, R29A, RHM10.0CRCT-ND Rohm

R29B

2 10, 1W RES 10 OHM 1W 5% R30A, R30B PT10XCT-ND Panasonic - ECG

2 2.2k RES 2.2K OHM 1/4W 5% R31A, R31B RHM2.2KERCT-ND Rohm

1 715R RES 715 OHM 1/8W 1% R103 RHM715CCT-ND Rohm

1 100k RES 100K OHM 1/8W 5% R108 RHM100KARCT-ND Rohm

1 100k RES 100K OHM CARBON R109 P100KBATB-ND Panasonic - ECG

FILM 1/4W 5%

1 47k RES 47K OHM 1/8W 5% R112 RHM47KARCT-ND Rohm

2 1k 1W RES 1.0K OHM 1W 5% R114A, R114B 1.0KW-1-ND Yageo

METAL OXIDE

2 15k RES 15K OHM CARBON FILM R115A, R115B P15KBACT-ND Panasonic - ECG

1/4W 5%

4 3.3k 1w RES 3.3K OHM 1W 5% R117A, R117B, R118A, 3.3KW-1-ND Yageo

METAL OXIDE R118B

2 22k RES 22K OHM 1/8W 5% R300, R301 RHM22KARCT-ND Rohm

2 100 RES 100 OHM 1/8W 5% R302, R303 RHM100ARCT-ND Rohm

2 RCJ-012 CONN RCA JACK METAL R/A RCA1A CP-1401-ND (Red) CUI Inc

RED PCB

2 RCJ-013 CONN RCA JACK METAL R/A RCA1B CP-1402-ND (White) CUI Inc

WHT PCB

2 EG2209A SWITCH SLIDE DPDT 12V S1, S300 EG1908-ND E-Switch

.1A L=4

2 ED365/2 TERMINAL BLOCK 7.50MM SPKR1A, SPKR1B ED2354-ND On Shore

2POS PCB Technology

1 2.2k at 25C THERMISTOR NTC 2.2K TH100 BC2304-ND Vishay/BC

OHM Components

LEADED

2 IRS2092SPBF Class D Controller, U1A, U1B IR's P/N International

IRS2092SPbF 16-Lead SOIC Rectifier

1 TLC071CD IC SINGLE SUPPLY OPAMP U300 296-2414-5-ND Texas Instruments

8-SOIC IRS2092SPBF

2 15V DIODE ZENER 500MW 15V Z102A, Z102B MMSZ4702T1GOSCT- ON Semiconductor

ND

www.irf.com IRAUDAMP7S REV 1.3 Page 34 of 42

1 68V DIODE ZENER 375MW 68V Z100 568-3782-1-ND NXP

Semiconductors

1 39V DIODE ZENER 500MW 39V Z101 BZT52C39-TPMSCT- Micro Commercial

ND Co

4 5.6V DIODE ZENER 500MW 5.6V Z103A, Z103B, Z104A, BZT52C5V6- Micro Commercial

Z104B TPMSCT-ND Co

Note all ½ W and 1W resistors are flame proof part numbers

www.irf.com IRAUDAMP7S REV 1.3 Page 35 of 42

Table 4 IRAUDAMP7S Mechanical Bill of Materials

Quantit Digikey

Value Description Designator Vendor

y P/N

Lock washer 1, Lock washer 2, Building

WASHER LOCK H729-

5 Washer #4 SS Lock washer 3, Lock washer 4, Fastener

INTERNAL #4 SS ND

Lock washer 5 s

Print Circuit Board

1 PCB IRAUDAMP7S_Rev PCB 1 Custom

2.2 .PCB

Screw 1, Screw 2, Screw 3,

Building

Screw 4- SCREW MACHINE Screw 4, Screw 5, Screw 6, H343-

12 Fastener

40X5/16 PHILLIPS 4-40X5/16 Screw 7, Screw 8, Screw 9, ND

s

Screw 10, Screw 11, Screw 12

Keystone

STANDOFF HEX 4- Stand Off 1, Stand Off 2, Stand 1893K-

4 Stand off 0.5" Electro-

40THR .500"L ALUM Off 3, Stand Off 4 ND

nics

STANDOFF HEX M/F 4- Keystone

8401K-

1 Stand off 0.5" 40 .500" ALUM, Chassis Stand Off 5 Electro-

ND

GND nics

Newuark

Thermalloy TO-220 Therm-

1 AAVID 4880G TO-220 mounting kit 1 82K609

mounting kit with screw alloy

6

www.irf.com IRAUDAMP7S REV 1.3 Page 36 of 42

Table 5 IRAUDAMP7S Models Differential Table

Model Name

Item AMP7S-55 AMP7S-100 AMP7S-150 AMP7S-200 Notes

IR

Power

FET1 IRFI4024H-117P IRFI4212H-117P IRFI4019H-117P IRFI4020H-117P

MOSFE

TS

Half 8Ω 25 W x 2 60 W x 2 125 W x 2 250 W x 2 Stereo

Bridge

Output 4Ω 50 W x 2 120 W x 2 250 W x 2 N/A Stereo

Full

Bridge 8Ω 100 W x 1 240 W x 1 500 W x 1 N/A Bridged

Output

+B, -B ±25 V ±35 V ±50 V ±70 V

Power ±B

Supply Voltage

±3 V ±5 V ±8 V ±10 V

Range

Audio

Gain 20 30 36 40

Gain

Feedbac R8A,R8

68k 100k 120k 130 k

k B

R117A*

+VAA 1 k, 1 W 2.2 k, 1 W 3.3 k, 1 W 5.1 k, 1 W

R117B*

R118A*

-VSS 1 k, 1 W 2.2 k, 1 W 3.3 k, 1 W 5.1 k, 1 W

R118B*

R114A*

100,1 W 220, 1 W 1 k, 1 W 2.2 k 1 W

R114B*

VCC R115A

4.7 k 10 k 15 k 20 k

R115B

R12A 1.3 k 3.9 k 7.5 k 5.1 k (Trip

OCSET

R12B (20 A) (23 A) (30 A) (23 A) level)

R18A 0.0 4.7 k 9.1 k 8.2 k (Trip

CSH

R18B (20A) (23A) (29A) (23 A) level)

R17A

VB 20 k 33 k 47 k 75 k

R17B

24 V 47 V 91 V Zener

68 V

OVP Z100 BZT52C24- MMSZ5261BT1GO MMSZ5270BT1G Digikey

568-3782-1-ND

TPMSCT-ND SCT-ND OSCT-ND P/N

12 V 30 V 39 V 51 V Zener

UVP Z101 MMSZ5242BT1GO MMSZ5256BT1GO BZT52C39- MMSZ5262BT1G Digikey

SCT-ND SCT-ND TPMSCT-ND OSCT-ND P/N

D5A

Clampin D5B MURA120T3OSCT- MURA120T3OSCT- IMURA120T3OS

N/A

g Diode D6A ND ND CT-ND

D6B

* Marked components are axial, ±5 %, ¼ w, and flame proof type.

www.irf.com IRAUDAMP7S REV 1.3 Page 37 of 42

IRAUDAMP7S Hardware

Put silicone grease between

Heat sink the heat spreader and TO-220-5

Heatsink threaded Screw

Lock washer

Flat Washer #4

Dual FET

TO-220-5

Heatsink threaded

PCB

Lock washer

Screws

H343-ND Screw

Lock washers

H729-ND

Fig 36 Dual MOSFET Mounting

TO-220 Pad insulator

Heat Sink

Shoulder Washer

Heatsink threaded Screw

Lock washer

Flat Washer #4

TO-220

Heatsink threaded

PCB

Lock washer

Screws

Lock washers H343-ND

H729-ND Screw

Fig 37 +VCC Regulator TO-220 Mounting

www.irf.com IRAUDAMP7S REV 1.3 Page 38 of 42

Fig 38 Heat Spreader

Screw Screw

H343-ND H343-ND

Lock washer Lock washer

incert thermistor

into this hole and

put silicone grease

Screw Screw

H343-ND Stand Off 3 H343-ND Stand Off 2

1893K-ND 1893K-ND

Lock washer Lock washer

Lock washer

Lock washer

GND Standoff

Screw

Screw

Stand Off 4 Lock washers Stand Off 5 Stand Off 1

1893K-ND H729-ND 8401K-ND 1893K-ND

Screws

H343-ND

Fig 39 Hardware Assemblies

www.irf.com IRAUDAMP7S REV 1.3 Page 39 of 42

IRAUDAMP7S PCB Specifications

PCB:

1. Single Layers SMT PCB with through holes

2. 1/16 thickness

3. 2/0 OZ Cu

4. FR4 material

5. 10 mil lines and spaces

6. Solder Mask to be Green enamel EMP110 DBG (CARAPACE) or Enthone

Endplate DSR-3241or equivalent.

7. Top Silk Screen to be white epoxy non conductive per IPC–RB 276 Standard.

8. All exposed copper must finished with TIN-LEAD Sn 60 or 63 for 100u inches

thick.

9. Tolerance of PCB size shall be 0.010 –0.000 inches

10. Tolerance of all Holes is -.000 + 0.003”

11. PCB acceptance criteria as defined for class II PCB’S standards.

Gerber Files Apertures Description:

All Gerber files stored in the attached CD-ROM were generated from Protel Altium

Designer Altium Designer 6. Each file name extension means the following:

1. .gbl Bottom copper, bottom side

2. .gto Top silk screen

3. .gbo Bottom silk screen

4. .gbs Bottom Solder Mask

5. .gko Keep Out,

6. .gm1 Mechanical

7. .gd1 Drill Drawing

8. .gg1 Drill locations

9. .txt CNC data

10. .apr Apertures data

Additional files for assembly that may not be related with Gerber files:

11. .pcb PCB file

12. .bom Bill of materials

13. .cpl Components locations

14. .sch Schematic

15. .csv Pick and Place Components

16. .net Net List

17. .bak Back up files

18. .lib PCB libraries

www.irf.com IRAUDAMP7S REV 1.3 Page 40 of 42

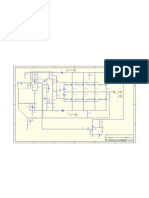

Fig 40 IRAUDAMP7S PCB Top Overlay (Top View)

Fig 41 IRAUDAMP7S PCB Bottom Layer (Top View)

www.irf.com IRAUDAMP7S REV 1.3 Page 41 of 42

Revision changes descriptions

Revision Changes description Date

Rev 1.1 Released Sep, 03 2008

Rev 1.2 ROHS Compliant(BOM updated) May, 29 2009

Rev 1.3 BOM updated :Ice Components as a October 28, 2009

second vender of the inductor

WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 08/29/2008

www.irf.com IRAUDAMP7S REV 1.3 Page 42 of 42

Вам также может понравиться

- 25W-500W Scalable Class D Audio AmplifierДокумент42 страницы25W-500W Scalable Class D Audio AmplifierPablo IgorОценок пока нет

- Carvin Schematic - DCM2000 Rev MДокумент1 страницаCarvin Schematic - DCM2000 Rev MdodОценок пока нет

- TI Class D AmplifierДокумент74 страницыTI Class D AmplifierAnonymous DjWqKpZ1Оценок пока нет

- Iraudamp6: 250W/8 X 2 Channel Class D Audio Power Amplifier Using The IRS20957S and IRF6785Документ46 страницIraudamp6: 250W/8 X 2 Channel Class D Audio Power Amplifier Using The IRS20957S and IRF6785jean grangeonОценок пока нет

- QSC Rmx850 SchematicДокумент7 страницQSC Rmx850 SchematicSergioMastríacoОценок пока нет

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WДокумент13 страницClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428100% (1)

- ICE250A Datasheet Full Rev 8Документ15 страницICE250A Datasheet Full Rev 8Johs316Оценок пока нет

- QSC RMX 850 RMX 1450 RMX 2450Документ42 страницыQSC RMX 850 RMX 1450 RMX 2450Wilmer RamirezОценок пока нет

- Allen Heath Zed-10fx SMДокумент63 страницыAllen Heath Zed-10fx SMIojan AndreiОценок пока нет

- Hfe Sony Str-Da30es Da50es V55es ServiceДокумент16 страницHfe Sony Str-Da30es Da50es V55es ServiceFeisal Ali100% (1)

- Funcionamento T CONДокумент49 страницFuncionamento T CONHilfeTech Informatica100% (1)

- LA48Документ2 страницыLA48henrycervantes4Оценок пока нет

- Check List For Acdb: Document NoДокумент2 страницыCheck List For Acdb: Document NoJaswant SutharОценок пока нет

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WДокумент13 страницClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428Оценок пока нет

- BOM Report SummaryДокумент28 страницBOM Report SummaryJosé Rodríguez VázquezОценок пока нет

- PlxmanДокумент83 страницыPlxmantedmich100% (1)

- IoioinglesДокумент6 страницIoioinglesSailin GudhkaОценок пока нет

- Lecture-5 Supervisory Control and Data Acquisition (SCADA)Документ6 страницLecture-5 Supervisory Control and Data Acquisition (SCADA)SanayaОценок пока нет

- Wharfedale Titan 15 Active Service ManualДокумент18 страницWharfedale Titan 15 Active Service ManualIrena TanaseОценок пока нет

- 1985 D11 Hitachi Power MOSFET Data BookДокумент362 страницы1985 D11 Hitachi Power MOSFET Data BookTodorosss Jj100% (1)

- MA5002VZ SM 130446-1amplificator ManualДокумент140 страницMA5002VZ SM 130446-1amplificator Manualtiganiada100% (1)

- Class D AmplifierДокумент5 страницClass D AmplifierkothuraОценок пока нет

- 6n1 SPK Prot Rev 1.2B - With Basic Function How It WorksДокумент34 страницы6n1 SPK Prot Rev 1.2B - With Basic Function How It Worksអំភ្លី សំលេងОценок пока нет

- Yamaha psr550 Sevicemanual PDFДокумент50 страницYamaha psr550 Sevicemanual PDFAnand s100% (1)

- Icepower 1000 AMK2Документ16 страницIcepower 1000 AMK2henrycervantes4Оценок пока нет

- Ram AudioДокумент1 страницаRam Audioto_netiks100% (1)

- Laney AH50Документ2 страницыLaney AH50Zoeloe_2Оценок пока нет

- Service Manual DP750 - DP760 - ENG - Rev1 PDFДокумент96 страницService Manual DP750 - DP760 - ENG - Rev1 PDFДмитрий РазуваевОценок пока нет

- Si 824 XДокумент30 страницSi 824 Xttnaing100% (2)

- 500w Pro Audio-SchemaДокумент1 страница500w Pro Audio-SchemausernamescuОценок пока нет

- Uppen FP 2200 PWR SMДокумент49 страницUppen FP 2200 PWR SMcoolruler40Оценок пока нет

- UCD-MINIONINA v.1 Class D AmpДокумент1 страницаUCD-MINIONINA v.1 Class D AmpMuhamad KharisОценок пока нет

- Hfe Kef Psw3500 Service enДокумент30 страницHfe Kef Psw3500 Service enTiromancino Tiromancino100% (1)

- Circuit Adjustable Bass Filter From 50 HZ To 150 HZ NE5532Документ4 страницыCircuit Adjustable Bass Filter From 50 HZ To 150 HZ NE5532Javier Castellanos BarrazaОценок пока нет

- Roland TD-8 ManualДокумент224 страницыRoland TD-8 ManualAnonymous cdQSIU03AQОценок пока нет

- Goldmund Audio Amplifier SchematicДокумент1 страницаGoldmund Audio Amplifier SchematicCường MchwОценок пока нет

- Ca 20Документ5 страницCa 20jhon130296Оценок пока нет

- Yamaha pc4800n pc9500n PDFДокумент86 страницYamaha pc4800n pc9500n PDFMhooMOoChaappHteenОценок пока нет

- SCS150SI SCS160SI SCS180.6S: Service ManualДокумент27 страницSCS150SI SCS160SI SCS180.6S: Service ManualShiro Nekorben Dallas NekoОценок пока нет

- 600mA Low Dropout Linear Regulator Data SheetДокумент24 страницы600mA Low Dropout Linear Regulator Data SheetJosé Manuel BelaОценок пока нет

- Sa Akx710Документ107 страницSa Akx710William SerranoОценок пока нет

- 4d4fe32593743 - SiA 208RДокумент8 страниц4d4fe32593743 - SiA 208RManoj VattavilaОценок пока нет

- GTO Series: Service ManualДокумент32 страницыGTO Series: Service ManualHardikОценок пока нет

- JVC AV-21B117BДокумент10 страницJVC AV-21B117Bdoraemon007100% (1)

- DX 1227Документ11 страницDX 1227Marcos Daniel Muñoz ToledoОценок пока нет

- Schematic 1200W-AMP Sheet-1 20180711223415Документ1 страницаSchematic 1200W-AMP Sheet-1 20180711223415Sachin SinghОценок пока нет

- 2x20W Stereo Class-D Audio Amplifier With Power Limit: FeaturesДокумент22 страницы2x20W Stereo Class-D Audio Amplifier With Power Limit: FeaturesFranz KardelОценок пока нет

- 400W-Protel Schematic-Anthony E Holton Audio Amplifier 17-02-2004Документ1 страница400W-Protel Schematic-Anthony E Holton Audio Amplifier 17-02-2004vdăduicăОценок пока нет

- Onkyo TX-NR646 PDFДокумент132 страницыOnkyo TX-NR646 PDFboroda2410100% (3)

- Specification: Approved by DaxiangДокумент17 страницSpecification: Approved by DaxiangRiatОценок пока нет

- Crest Audio ProДокумент6 страницCrest Audio ProrudiОценок пока нет

- STK 415Документ12 страницSTK 415bbchacinОценок пока нет

- LED TV CONTROL BOARD SPECIFICATIONДокумент15 страницLED TV CONTROL BOARD SPECIFICATIONSamuel Ulises Leon GonzalezОценок пока нет

- M-PRO2 DatasheetДокумент17 страницM-PRO2 DatasheetcdpangoОценок пока нет

- Ad52060 PDFДокумент1 страницаAd52060 PDFReyniel VazquezОценок пока нет

- LCR-0202 Analog Linear CouplingДокумент3 страницыLCR-0202 Analog Linear CouplingJaPan Life100% (1)

- Kenwood-KGC4042A Car EqualДокумент8 страницKenwood-KGC4042A Car EqualatukbarazaОценок пока нет

- Iraudamp 5Документ51 страницаIraudamp 5Carlos AlvarezОценок пока нет

- Irs2092 25W 500WДокумент42 страницыIrs2092 25W 500WKien TrungОценок пока нет

- IRAUDAMP70Документ42 страницыIRAUDAMP70Edmond HaidauОценок пока нет

- Iraudamp9 - 1x1700w PDFДокумент39 страницIraudamp9 - 1x1700w PDFHarun ARIKОценок пока нет

- Amplificador 25w A 500wДокумент41 страницаAmplificador 25w A 500wVictor ReyesОценок пока нет

- 300W X 2 Channel Class D Audio Power Amplifier-1Документ34 страницы300W X 2 Channel Class D Audio Power Amplifier-1Sahab RathoreОценок пока нет

- Iraudamp 5Документ51 страницаIraudamp 5Shaun Dwyer Van HeerdenОценок пока нет

- Iraudamp 11Документ35 страницIraudamp 11Bin LowenОценок пока нет

- Atmel 2486 8 Bit Avr Microcontroller Atmega8 L DatasheetДокумент331 страницаAtmel 2486 8 Bit Avr Microcontroller Atmega8 L DatasheetRolando IrrazabalОценок пока нет

- Irfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120AДокумент12 страницIrfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADirson Volmir WilligОценок пока нет

- NN 6956Документ5 страницNN 6956Tiago MizaelОценок пока нет

- Philips 70fr210 70fr212 70fr315 SMДокумент17 страницPhilips 70fr210 70fr212 70fr315 SMTiago MizaelОценок пока нет

- PWM Qricice1qso1gДокумент21 страницаPWM Qricice1qso1gCintya CardozoОценок пока нет

- L293DДокумент7 страницL293Dapi-370080950% (2)

- HCF 4070Документ7 страницHCF 4070Tiago MizaelОценок пока нет

- Lab 2 Universal Logic GatesДокумент4 страницыLab 2 Universal Logic GatesIfthakharul Alam ShuvoОценок пока нет

- Edc Lab Manual Final PDFДокумент81 страницаEdc Lab Manual Final PDFAchyuth NaiduОценок пока нет

- Forbidden LatenciesДокумент7 страницForbidden LatenciesAr VindОценок пока нет

- 9mm!ূຌዡገ๕ۉ࿋ഗ Rotary Potentiometers With Metal Shaft Series: WH9011A-1-18TДокумент26 страниц9mm!ূຌዡገ๕ۉ࿋ഗ Rotary Potentiometers With Metal Shaft Series: WH9011A-1-18TpeterfunОценок пока нет

- CM-MSS.22 and CM-MSS.23: Thermistor Motor Protection RelaysДокумент13 страницCM-MSS.22 and CM-MSS.23: Thermistor Motor Protection RelaysBinh Thai HYОценок пока нет

- Swyd NewДокумент39 страницSwyd NewMrityunjayChauhanОценок пока нет

- TGS 6 - Backpropagation-18.01.53.0065Документ2 страницыTGS 6 - Backpropagation-18.01.53.0065Ki JahsehОценок пока нет

- S17A - Kel.5 - Laporan Ujian Akhir SemesterДокумент320 страницS17A - Kel.5 - Laporan Ujian Akhir SemesterWahyu Anantyo AkbarОценок пока нет

- CARA PEMASANGAN RADIO KERETA DALAM 40 HURUFДокумент6 страницCARA PEMASANGAN RADIO KERETA DALAM 40 HURUFamir akmalОценок пока нет

- TC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchДокумент11 страницTC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchCandelaria CortesОценок пока нет

- Manual 802Документ38 страницManual 802Ludovic OuedraogoОценок пока нет

- Generador El PoyДокумент4 страницыGenerador El PoyPortillo Calix Jorge LuisОценок пока нет

- File - 1CB30C A2c3fe F1a5aa 3804e1 5ecd44 024FD7Документ4 страницыFile - 1CB30C A2c3fe F1a5aa 3804e1 5ecd44 024FD7Khaled KamelОценок пока нет

- HP-AN346 - A Guideline For Designing External DC Bias CircuitsДокумент10 страницHP-AN346 - A Guideline For Designing External DC Bias Circuitssirjole7584Оценок пока нет

- UlagarajaДокумент3 страницыUlagarajaulaga rajaОценок пока нет

- LCD Interfacing With Microcontroller 8051Документ50 страницLCD Interfacing With Microcontroller 8051Darshan Vala100% (2)

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringДокумент40 страницInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano HarОценок пока нет

- Circuit Construction Kit Ac Virtual Lab HTML Guide - enДокумент4 страницыCircuit Construction Kit Ac Virtual Lab HTML Guide - enkavithaОценок пока нет

- ZVA Service ManualДокумент226 страницZVA Service Manualrf2011Оценок пока нет

- Tarot x6 User Manual 1Документ35 страницTarot x6 User Manual 1El CuriosoОценок пока нет

- 1 HPPДокумент36 страниц1 HPPAutomation WorksОценок пока нет

- Differential AmplifierДокумент5 страницDifferential Amplifiermahesh babuОценок пока нет

- Areva MBCHДокумент16 страницAreva MBCHronald_chan_2100% (3)

- Sifang Csc-100eb v1.09 Line Protection Ied Manual 2022-12Документ514 страницSifang Csc-100eb v1.09 Line Protection Ied Manual 2022-12MarkusKunОценок пока нет

- ETIMAT 1N 1p+N B6 6kA Miniature Circuit Breaker DatasheetДокумент4 страницыETIMAT 1N 1p+N B6 6kA Miniature Circuit Breaker DatasheetCuc Gabriel PaulОценок пока нет

- Sony Hcd-gnz77d Gnz88d Ver-1.3 SCHДокумент6 страницSony Hcd-gnz77d Gnz88d Ver-1.3 SCHShailesh SanayeОценок пока нет