Академический Документы

Профессиональный Документы

Культура Документы

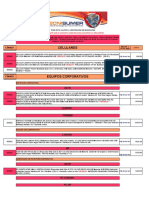

Caratula

Загружено:

Dil ContrerasАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Caratula

Загружено:

Dil ContrerasАвторское право:

Доступные форматы

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

COMPUERTAS LOGICAS

PRESENTADO POR:

DILSON CONTRERAS MARTINEZ

JAVIER DUMAR HOYOS

LEIDER BRUNO MERCADO

YERSON CONTRERAS ROMERO

PRESENTADO A

ALVARO ALARCON ALARCON

SAHAGUN

2018

PROGRAMA DE INGENIERIA DE SISTEMAS

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

INTRODUCCION

En el presente informe se detallan las actividades realizadas en circuitos electrónicos digitales,

estos circuitos digitales se montaron en una protoboard para la comprobación física del os circuitos,

siguiendo una guía de laboratorio digital, en la cual se daban los diagramas para el montaje en el

software Arduino y posteriormente se monta en la placa deprueba, dando como resultado la

comprobación de su funcionamiento. Además se realizaron los análisis de los diagramas o

esquemas de circuitos lógicos con compuertas AND, OR, NOT, NOR y NAND par determinar la

función resultante de cada uno de ellos utilizando la tabla de laverdad,

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

OBJETIVO GENERAL

El principal objetivo del laboratorio de electrónica digital I, es complementar los conocimientos

adquiridos teóricamente en el curso y llevarlos a la implementación mediante el lenguaje arduino

utilizando la protoboard y las distintas compuertas

OBJETIVOS ESPECIFICOS

-Tener un primer acercamiento al funcionamiento de las compuertas lógicas, tomando en

cuenta como se polarizan correctamente.

- Elaborar los diseños de las compuertas XOR, XNOR a base de compuertas lógicas básicas

(AND, OR, NOT).

- Diseñar las compuertas lógicas básicas a partir de una compuerta.

- Comprobar la tabla de verdad de las compuertas implementándolas en un circuito.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

CUESTIONARIO

1. ¿Por qué la señal que llega a cualquiera de las entradas toma un tiempo en ser procesada?

¿De cuánto tiempo es dicho retardo en cada circuito integrado?

2. Existen unos valores necesarios de voltaje y corriente que las señales de entrada en los

circuitos integrados usados en la práctica deben tener ¿Cuáles son dichos valores para

cada CI?

3. Si en la práctica, en vez de usar integrados de la familia TTL, se hubieran usado integrados

de la familia CMOS ¿Cuáles serian las principales diferencias y ventajas?

4. ¿Qué significan las letras LS que están contenidas en el serial de los circuitos usados en la

práctica? Existen otras letras, qué significado tienen?

SOLUCION

1.

El 7404 IC el voltaje de operación es de 5V, el voltaje de entrada de alto nivel es de 2V, y la

entrada de bajo nivel es de 0.8V

El 7408 IC la alimentación del circuito está comprendida entre 4.75 y 5.25 Voltios.

El 7432 IC el voltaje de alimentación: 4.75V a 5.25V.

El 7400 IC el voltaje de alimentación: 5 V, con una tolerancia (de 4.5 V a 5.5 V).

2.

Características de la lógica CMOS:

• Disipación de baja potencia: La disipación de potencia depende de la potencia de la fuente de

poder, su frecuencia, carga en la salida y el tiempo de arranque. A 1 MHz y a 50pF de carga, la

disipación de potencia es típicamente 10nW por compuerta.

• Retrasos de propagación corta: Depende de la fuente de poder, los retrasos de propagación son

usualmente de 25 ns a 50 ns.

• Tiempos de subida y bajada controlados: Los flancos de subida y de bajada son usualmente

denominados como rampas en lugar de funciones de escalón, y tardan entre 20% – 40% más que

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

los retrasos de propagación.

• La inmunidad al ruido ronda el 50% o 45% de la oscilación lógica.

• Niveles lógicos serán esencialmente iguales a la fuente de poder, esto debido a la alta

impedancia de entrada.

• Nivel de tensión desde 0 a VDD donde VDD es la fuente de tensión. Un nivel bajo es cualquier

valor entre 0 y 1/3 de VDD mientras que un nivel alto se representa como cualquier valor entre 2/3

VDD y VDD.

Características de la lógica TTL:

• 10 mW de disipación de potencia por compuerta.

• Retrasos de propagación son de 10ns al tratar con 15 pF/400 Ω de carga.

• El rango de tensión está entre 0 y Vcc donde Vcc es usualmente 4.75V – 5.25V. Un nivel bajo es

representado por niveles de tensión entre 0V– 0.8V, mientras que un nivel alto se representa por

niveles de tensión entre 2V – Vcc.

CMOS comparado con TTL:

• Los componentes CMOS son usualmente más caros que los equivalentes en TTL. Sin embargo,

la tecnología CMOS es más barata a nivel de sistema, esto debido a los chips que poseen un

menor tamaño además que requieren menos regulación.

• Los circuitos CMOS no drenan tanta potencia como los TTL en los períodos de inactividad. Sin

embargo, el consumo de potencia de los CMOS se incrementa más rápidamente que los TTL al

aumentar la velocidad del reloj. Un menor consumo de corriente requiere menor distribución de la

fuente de alimentación, teniendo como producto un diseño más sencillo y barato.

• Debido a que los tiempos de subida y bajada son mayores, la transmisión de las señales digitales

resulta más sencilla y barata con los chips CMOS.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

• Los componentes CMOS son más susceptibles a daños por descargas electrostáticas con

respecto a los componentes TTL.

3. Las letras significan:

-LS, S, etc. son TTL normales y corrientes. Son compatibles 99%.

-HC es del tipo CMOS. Ósea, bajo consumo, más delicados y de muy

poca corriente. También son más lentos. Es 10%

compatible con el LS.

-HCT es un hibrido entre los otros dos. Es CMOS pero un poco más rápido

que el HC y casi soporta la misma corriente que el LS. Es 70% compatible

con cualquiera.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

PROCEDIMIENTO

1. Usando el ProtoBoard, ensamble el circuito de la figura 1, Tenga en cuenta la

polaridad de los LED y la identificación correcta de los pines del circuito

integrado. Recuerde que es preferible antes de ensamblar el circuito en la

ProtoBoard, se realice una simulación del circuito en cualquier programa de

simulación de circuitos

Figura 1. Figura 2.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

Figura 3.

Figura 4. Figura 5.

2. Aplique el voltaje al circuito conectando una fuente de voltaje de 5V.

3. A partir de las entradas, observar el comportamiento de la salida afín de construir la

tabla de verdad.

4. Para los circuitos de las figuras 2, 3, 4, 5 Repetir los pasos 1-3.

5. Para Construir las compuertas XOR y XNOR, se usaran las compuertas antes usadas

(AND, OR, NOT) Investigar e implementar en la ProtoBoard.

6. Construir compuertas lógicas básicas usando solamente compuertas NAND.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

DATOS Y RESULTADOS

TABLAS DE VERDAD

MinT = S= A.B

MinT = S= 𝐴̅. 𝐵 + 𝐴. 𝐵̅ + A.B

MinT = S= 𝐴̅

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

NAND

MinT = S= A.𝐵̅ + 𝐴̅. 𝐵 + 𝐴𝐵̅

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

TEORIA RELACIONADA

Compuertas Lógicas

La construcción de las compuertas lógicas, está basada en componentes discretos (Transistores,

Diodos, y Resistencias), pero con la enorme ventaja de que en un solo el meterelo se puede

encontrar 1, 2, 3 o 4 compuertas (dependiendo de la cantidad de entradas y propiedades).Todos

los circuitos internos de las compuertas están conectados de manera que las entradas y los

caminos pueden manejar estados lógicos (1 o 0).

Tablas de verdad

Una tabla de verdad es una tabla que nos muestra la manera en que reacciona la salida de una

compuerta o circuito lógico, en función de sus entradas. En la tabla se vieron todas las posibles

variables de entrada y las variables de salida.

Operaciones Lógicas

Las operaciones lógicas básicas 3 OR (suma), Y (multiplicación) y NO (negación), Tomando como base la

operación que ejecutan, se le da a cada compuerta su nombre y símbolo en un diagrama,

veamos con más detalle cada una de ellas:

Operación O (+)

Tomemos una compuerta con dos entradas (Variables A y B), y una salida (Variable Z), al realizar

la operación O sobre las entradas A, B, el valor de la salida, Z sería:

Z = A + B (o de manera gráfica) Z = A o B

La siguiente tabla representa la tabla de verdad para una compuerta tipo O, y su símbolo gráfico.

La tabla de verdad nos lleva a la conclusión de que si cualquiera de las entradas de una

compuerta O es ALTA, la salida también es ALTA; cualquier otra combinación nos dará una salida

BAJA. Por lo que podríamos resumir la operación O como: Si A o B hijo1, Z será 1.Z = A + B se

"traducirá" como Z es igual a A más B. La operación O es básicamente una suma, pero como solo

podemos tener 0o 1, la suma de 1 +1 siempre es igual a 1.Si nuestra compuerta fue más

entradas, la operación sería la misma, por ejemplo: Z = A + B+ C + D se "traducirá" como Z es

igual a A más B más C más D.Z = 1 + 1 +1 + 1 = 1

Operación AND

Tomemos una compuerta con dos entradas (Variables A y B), y una salida (Variable Z), al realizar

la operación Y sobre las entradas A, B, el valor de la salida, Z sería:

Z = A * B (o de manera gráfica) Z = A y B

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

La siguiente tabla representa la tabla de verdad para una compuerta tipo Y, y su símbolo gráfico.

La tabla de verdad nos lleva a la conclusión de que si todas las entradas de una compuerta Y son

ALTAS, la salida también es ALTA, o bien, la salida BAJA. Por lo que podríamos resumir la

operación AND como: Si A y B hijo 1, Z ser 1Z = A * B se "traduciría " como Z es igual a A por B

La operación Y es básicamente una multiplicación, pero como yo solo puedo tener 0 o 1, la suma

de 1 *1 siempre es igual a 1.Si nuestra compuerta tiene más entradas, la operación sería la

misma, por ejemplo: Z = A * B *C * D se "translada" como: Z es igual a A por B por C por D.Z = 1 *

1*1*1=1

Operación NO

Tomemos una compuerta NO, este tipo de compuerta s solo tienen una entrada, nuestra salida

siempre es el opuesto a la entrada, al realizar la operación NO a la entrada, el valor de X sería:

Z = A Negada (o de manera gráfica) Z = A

La siguiente tabla representa la tabla de verdad para una compuerta tipo Y, y su símbolo gráfico.

La tabla de verdad nos lleva a la conclusión de que la salida de una compuerta NO (Inversora)

siempre es el nivel contrario a la entrada.

Combinaciones entre compuertas

Una vez comprendido los resultados que obtenemos con las operaciones de las compuertas

lógicas básicas, podemos analizar las teclas básicas entre las compuertas. Cada una de las

uniones de lastres compuertas básicas como, nos dan como resultado las compuertas más, O no,

y Y no con (De hecho, tres, faltando la unión NO y NO, pero esta unión directa no es útil si se

tiene solo una salida, ya que el resultado de la misma i o igual a la entrada).Otro tipo de

compuertas combinadas incluyen más dedos compuertas) que pueden usar las compuertas OR y

NOR EXCLUSIVAS, veamos cómo están conformadas.

Compuerta NOR

La siguiente imagen nos muestra el proceso de unión de las compuertas O y NO para darnos

como resultado la compuerta NOR.

ALVARO ANTONIO ALARCÓN ALARCÓN

UNIVERSIDAD DE CÓRDOBA

FACULTAD DE INGENIERÍAS

PROGRAMA DE INGENIERÍA DE SISTEMAS Y TELECOMUNICACIONES

LABORATORIO DE ELECTRÓNICA DIGITAL

ALVARO ANTONIO ALARCÓN ALARCÓN

Вам также может понравиться

- CUENTOДокумент1 страницаCUENTODil ContrerasОценок пока нет

- CUENTOДокумент1 страницаCUENTODil ContrerasОценок пока нет

- Acompañamiento en BlancoДокумент5 страницAcompañamiento en BlancoDil ContrerasОценок пока нет

- Seguimiento Al Desarrollo Del Niño O NiñaДокумент2 страницыSeguimiento Al Desarrollo Del Niño O NiñaDil ContrerasОценок пока нет

- Formato CORREGIDOДокумент1 страницаFormato CORREGIDODil ContrerasОценок пока нет

- Acompañamiento en BlancoДокумент5 страницAcompañamiento en BlancoDil ContrerasОценок пока нет

- Formato CORREGIDOДокумент1 страницаFormato CORREGIDODil ContrerasОценок пока нет

- Acompañamiento Telefonico - 4Документ3 страницыAcompañamiento Telefonico - 4Dil ContrerasОценок пока нет

- Biologia Molecular Maria VerbelДокумент2 страницыBiologia Molecular Maria VerbelDil ContrerasОценок пока нет

- Microprocesadores y Microcomputadoras PDFДокумент27 страницMicroprocesadores y Microcomputadoras PDFLuis NaulaОценок пока нет

- Taller Electronica DigitalДокумент6 страницTaller Electronica DigitalcamiloОценок пока нет

- Tema 3, Problemas Con Solución (IC, TSI)Документ69 страницTema 3, Problemas Con Solución (IC, TSI)PabloОценок пока нет

- Trabajo Practico 7 y 8.Документ38 страницTrabajo Practico 7 y 8.antitohОценок пока нет

- Procesadores VelocidadesДокумент16 страницProcesadores VelocidadesJeshu LimaОценок пока нет

- Clase CpuДокумент64 страницыClase CpuMarcosОценок пока нет

- Lista de Precios TecnisumerДокумент20 страницLista de Precios TecnisumerAlejandro Echeverri CiroОценок пока нет

- Practica 01Документ18 страницPractica 01Jesus Roca FernandezОценок пока нет

- Control de Luminosidad LCDДокумент28 страницControl de Luminosidad LCDRodrigo Leiva DiazОценок пока нет

- Arquitectura Del Computador - Tercera EntregaДокумент9 страницArquitectura Del Computador - Tercera EntregaDIEGO ALEJANDRO LOPEZ GARZONОценок пока нет

- Como Usar Un PIC y Un Display en ProteusДокумент12 страницComo Usar Un PIC y Un Display en ProteusAbraham GallardoОценок пока нет

- 1 - PDFsam - MANUAL DE INSTRUCCIONES AVR ENSAMBLADOR Esp PDFДокумент50 страниц1 - PDFsam - MANUAL DE INSTRUCCIONES AVR ENSAMBLADOR Esp PDFluisОценок пока нет

- ICEE1012 Capitulo 5 La MemoriaДокумент101 страницаICEE1012 Capitulo 5 La MemoriaZapatoCuadradoОценок пока нет

- Informe N°3Документ14 страницInforme N°3Andre AliagaОценок пока нет

- Historia Del ProcesadorДокумент20 страницHistoria Del ProcesadorMax Luviano89% (18)

- Practi Arqui AvДокумент129 страницPracti Arqui AvJErdradexОценок пока нет

- Introduccion A Las Arquitecturas ParalelasДокумент92 страницыIntroduccion A Las Arquitecturas ParalelasJack SesentayTresОценок пока нет

- Caracteristicas de La Series CMOSДокумент11 страницCaracteristicas de La Series CMOSFelipe Rodriguez100% (1)

- Clasificación de Computadores y Generación de Computadores - Natalia PerezДокумент4 страницыClasificación de Computadores y Generación de Computadores - Natalia PerezJuan David Londoño LaraОценок пока нет

- Arquitectura Del Microprocesador z80Документ9 страницArquitectura Del Microprocesador z80Nilyan BertiОценок пока нет

- Registros de SegmentacionДокумент6 страницRegistros de SegmentacionMichael BorjasОценок пока нет

- Practica 1 Xilinix Ise Design2019bДокумент11 страницPractica 1 Xilinix Ise Design2019bJaime GarciaОценок пока нет

- Previo 2 AДокумент16 страницPrevio 2 Adiego condeОценок пока нет

- Trabajo de Electiva IIIДокумент7 страницTrabajo de Electiva IIIRost RattОценок пока нет

- Instrucciones Soportadas en Simuproc 1Документ13 страницInstrucciones Soportadas en Simuproc 1MarcelaPereiraОценок пока нет

- 2018-2 Guia - Lab - 2 PDFДокумент3 страницы2018-2 Guia - Lab - 2 PDFsonirichnaviОценок пока нет

- Programar microcontroladores con software MiniProДокумент2 страницыProgramar microcontroladores con software MiniProFerney RojasОценок пока нет

- Arquitectura de Un MicroprocesadorДокумент4 страницыArquitectura de Un MicroprocesadorRolando NinaОценок пока нет

- Lab7 Comunicacion Serial Con Pic 16F877A y MikroBasicДокумент5 страницLab7 Comunicacion Serial Con Pic 16F877A y MikroBasicVictor Azaña PomaОценок пока нет

- Generador de Señal de Reloj con 74LS14 y 74HC132Документ17 страницGenerador de Señal de Reloj con 74LS14 y 74HC132Eduardo OrtizОценок пока нет