Академический Документы

Профессиональный Документы

Культура Документы

Pic Microcontroller

Загружено:

Me himpОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Pic Microcontroller

Загружено:

Me himpАвторское право:

Доступные форматы

International Journal of Engineering Trends and Technology (IJETT) – Volume 33 Number 1- March 2016

Analysis and Design of Positive Feedback

Adiabatic Logic (PFAL) Based Universal

Gates

Sowmiya.M1, Darwin.S2, Sindhuja.D3, Sheela Merlin.M4

1,3,4

PG Student, 2 Asst.Prof, Electronics Department,

Dr.Sivanthi Aditanar College of Engineering, Tiruchendur, Tamilnadu, India.

Abstract their results were compared with the conventional

This paper presents positive feedback CMOS design. As universal gates plays vital role in

adiabatic logic that employs the principle of most of the digital circuits, the present paper

adiabatic charge recovery. The low power PFAL mainly concern on its design. The performance of

apply a sinusoidal power supply with magnitude this device was evaluated using Positive Feedback

Vdd. Dynamic power contributes large power in Adiabatic Logic (PFAL). This paper analyzed the

hardware design. So the design of a circuit with universal logic gates with the help of PFAL styles

less power consumption for low power application and their results were compared.

has become critical concern. More energy is

dissipated during the switching events. PFAL 1.1. ADIABATIC LOGIC

circuit dramatically reduces power dissipation by

reducing switching activity. This paper also Adiabatic” is a term of Greek origin that

analysis the design of NAND, NOR, NOT logic gate has spent most of its history associated with

based on PFAL topology. The simulation result is classical thermodynamics. It refers to a system in

obtained using Tanner EDA Tools. Positive which a transition occurs without energy (usually

Feedback Adiabatic Logic contributes the best way in the form of heat) being either lost to or gained

to reuse the energy stored at the output node from the system. In the context of electronic

capacitor instead of discharging it to the ground systems, rather than heat, electronic charge is

node. preserved. Thus, an ideal adiabatic circuit would

operate without the loss or gain of electronic

Keywords charge.

Because of the Second Law of

Adiabatic logic, dynamic power, PFAL, low Thermodynamics, it is not possible to completely

power, switching activity. convert energy into useful work. However, the term

“Adiabatic Logic” is used to describe logic families

1. INTRODUCTION that could theoretically operate without losses. The

term “Quasi-Adiabatic Logic” is used to describe

Now a day‟s Power dissipation is more logic that operates with a lower power than static

important problem in compact electronic devices. CMOS logic, but which still has some theoretical

This power dissipation causes the low battery non-adiabatic losses [1], [5], [6]. In both cases, the

backup. So energy efficiency has become main nomenclature is used to indicate that these systems

concern in the portable equipments to get better are capable of operating with substantially less

performance with less power dissipation. As the power dissipation than traditional static CMOS

power dissipation in a device increases then extra circuits.

circuitry is necessary to cool the device and to Adiabatic circuits are low power circuits

protect the device from thermal breakdown which which use "reversible logic" to conserve energy.

also results in increase of total area of the device. Adiabatic circuits are those circuits which work on

In order to overcome these problems the power the principle of adiabatic charging and discharging

dissipation of the circuit is to be reduced by and which recycle the energy from output nodes

adopting different low power techniques [8], [9]. instead of discharging it to ground. Conventional

The present paper focuses on a novel energy CMOS circuits achieve a logic „1‟ or logic „0‟ by

efficient technique called adiabatic logic which is charging the load capacitor to supply voltage Vdd

based on energy recovery principle. In this and discharging it to ground respectively. As such

technique instead of discharging the consumed every time a charge-discharge cycle occurs, an

energy is recycled back to the power supply amount of energy equal to V2dd C is dissipated.

thereby reducing overall power consumption. In Unlike the conventional CMOS circuits, in

this paper the performance of universal gates is adiabatic circuits energy is recycled [3]. Instead of

evaluated in different adiabatic logic styles and

ISSN: 2231-5381 http://www.ijettjournal.org Page 4

International Journal of Engineering Trends and Technology (IJETT) – Volume 33 Number 1- March 2016

discharging the capacitor to ground, the charge is 2.2 PFAL BASED NOT GATE

discharged to the power supply. Since the charge The inverter (NOT circuit) performs the

has to be discharged to supply, the supply in operation called inversion or complementation. The

adiabatic circuits is a time varying one called the NOT operation changes one logic level to the

power clock. It has been observed that among the opposite logical level. When the input is Low, the

different waveforms for charging or discharging the output is high. When the input is high, the output is

load capacitor, a ramp is more efficient and as such low. The inverter changes one logic level to the

trapezoidal power clocks have been used in many opposite level. In terms of bits, it changes a 1 to a 0

adiabatic circuit styles [2]. Many adiabatic logic and 0 to 1. When a High level is applied to an

circuits which dissipate less power than static inverter input, a low level will appear on its output.

CMOS logic circuits have been introduced as a When a low level is applied to its input, a High will

promising approach in low power circuit design. appear on its output. PFAL based NOT gate is

shown in Figure 2.

2. MATERIALS AND METHODOLOGY

2.1 POSITIVE FEEDBACK ADIABATIC

LOGIC

The partial energy recovery circuit

structure named Positive Feedback Adiabatic Logic

(PFAL) has been used, since it shows the lowest

energy consumption if compared to other similar

families, and a good robustness against

technological parameter variations. It is a dual-rail

circuit with partial energy recovery [4], [10]. The

general schematic of the PFAL gate is shown in

Figure 1.

The core of all the PFAL gates is an

adiabatic amplifier, a latch made by the two PMOS Figure 2 Structure of PFAL based NOT gate

M1-M2 and two NMOS M3-M4, that avoids a

logic level degradation on the output nodes out and 2.3 PFAL BASED NAND GATE

/out. The two n-trees realize the logic functions. NAND gate is an electronic circuit which

This logic family also generates both positive and has two or more inputs but only one output. The

negative outputs. NAND gate is the natural implementation for the

simplest and fastest electronic circuits [7]. The

output is HIGH if at least one of its inputs is LOW.

The output is LOW only when all the inputs are

HIGH. The term NAND is a contraction of NOT-

AND. The NAND gate is a combination of an

AND gate followed by NOT gate. For 2 input

NAND gate, two NMOS transistors connected in

series is taken as pull down network and two

PMOS transistors connected in series is taken as

pull up network.

PFAL based NAND gate structure is

shown in Figure 3. This circuit works similar to

CMOS technology based circuit and also reduces

power by recycling the energy instead of

discharging it to ground.

Figure 1 Basic structure of Positive Feedback

Adiabatic Logic (PFAL).

The functional blocks are in parallel with

the PMOSFETs of the adiabatic amplifier and form

a transmission gate. The two n-trees realize the

logic functions. This logic family also generates

both positive and negative outputs.

Figure 3 Structure of PFAL based NAND gate

ISSN: 2231-5381 http://www.ijettjournal.org Page 5

International Journal of Engineering Trends and Technology (IJETT) – Volume 33 Number 1- March 2016

2.4 PFAL BASED NOR GATE

The NOR gate, like the NAND gate, NOR

gate is also useful logical element because it can

also be used as a universal gate. NOR gate can be

used in combination to perform the AND, OR and

Inverter operations.

NOR Gate is the combination of NOT gate

at the output of OR gate, hence NOR gate is type of

NOT-OR gate. NOR gate has two or more input

and only one output. The Output of NOR gate is

high when all inputs are low otherwise the output is

low.

PFAL based NOT gate is shown in Figure

4 which has similar operation to CMOS technology

The schematic diagram for PFAL based NOR

with less power consumption.

gate is shown in Figure 7.

Figure 4 Structure of PFAL based NOR gate

3. RESULTS AND DISCUSSION

The Positive Feedback Adiabatic Logic

based NAND, NOR, NOT gates are designed and The transient analysis of PFAL based NAND

simulated using TANNER EDA Tools. gate is shown in the Figure 8.

The schematic diagram for PFAL based

NAND gate is shown in Figure 5.

The schematic diagram for PFAL based NOT

gate is shown in Figure 9.

The transient analysis of PFAL based NAND

gate is shown in the Figure 6.

ISSN: 2231-5381 http://www.ijettjournal.org Page 6

International Journal of Engineering Trends and Technology (IJETT) – Volume 33 Number 1- March 2016

The transient analysis of PFAL based NOT 7) www.slideshare.net/satyaJoshi1/logic-gates-and-or-not-

nor-nand-xor-xnor-gates-35078548?qid=8f8afd9a-7415-

gate is shown in the Figure 10.

4e83-b2b6-dcabda54efc8&v=&b=&from_search=1

8) W.C. Athas, L.J. Svensson, J.G. Koller, N.Tzartzains, and

E. Y-C. Chou, “Low-power digital systems based on

adiabatic-switching principles,”Very Large Scale

Integration. (VLSI) Syst., IEEE Transaction on, Vol.2,

Issue4, Dec., 1994, pp.398-407.

9) Sonal Jain, Prof. Monika Kapoor,” Design and Analysis of

CMOS and Adiabatic 4-Bit Binary Multiplier”

International Journal of Engineering Trends and

Technology (IJETT) – Volume 7 Number 2 - Jan 2014

10) B. Dilli Kumar, M. Bharathi “Design of Energy Efficient

Arithmetic Circuits Using Charge Recovery Adiabatic

Logic” International Journal of Engineering Trends and

Technology- Volume4Issue1- 2013

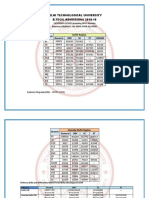

Table 1: Performance Analysis

GATES POWER(mW)

BASIC PFAL

NOT 87.694 83.79

NAND 87.5 50.05

NOR 92.31 64.3

4. CONCLUSION

We conclude that the proposed adiabatic

logic circuit is advantageous to ultra low power

applications. This paper shows the simulation result

of universal gates and also compares the power

values using Tanner EDA. The NOT gate, NOR

gate and NAND gate achieves power reduction of

23%, 36.1% and 42.8% respectively. Among three

gates, NAND gate consume less power. Hence it

proves that positive feedback adiabatic logic based

NAND gate can be used for ultra low power

circuits.

REFERENCES

1) Prasad D Khandekar, Shaila Subbaraman, and Abhijit V.

Chitre Implementation and Analysis of Quasi-Adiabatic

Inverters International conference of engineers and

computer Scientist 2010 Vol II IMECS 17-19-201 Hong

Kong

2) Arsalan, Shams, “Charge-recovery power clock generators

for adiabatic logic circuits”, 18th International Conference

on VLSI Design, pp. 171- 174, 3-7 January 2005.

3) Indermauer.T and Horowitz.M, “Evaluation of Charge

Recovery Circuits and Adiabatic Switching for Low Power

Design, “Technical Digest IEEE Sym.Low Power

Electronics, San Diego, pp. 102-103, Oct. 2002.

4) Mukesh Tiwari, Jai karan Singh, Yashasvi Vaidhya

“Adiabatic Positive Feedback Charge Recovery Logic for

low power CMOS Design” IJCTEE, Volume 2, Issue 5,

October 2012.

5) Prof Mukesh Tiwari, Prof Jaikaran Singh, Mr Yashasvi

Vaidhya “Adiabatic Improved Efficient Charge Recovery

Logic for low power CMOS logic ” International journal

of Electronic Communication and Computer Engineering

pp 350-354 Vol 1 issue 5.

6) Samik Samanta Power Efficient VLSI Inverter Design

using Adiabatic Logic and Estimation of Power dissipation

using VLSI-EDA Tool Special Issue of IJCCT Vol. 2 Issue

2, 3, 4; 2010 for International Conference [ICCT-2010],

3rd-5th December 2010

ISSN: 2231-5381 http://www.ijettjournal.org Page 7

Вам также может понравиться

- Adiabatic Positive Feedback Charge Recovery Logic For Low Power CMOS DesignДокумент6 страницAdiabatic Positive Feedback Charge Recovery Logic For Low Power CMOS DesignvaseemalikhanОценок пока нет

- 24.IJAEST Vol No 5 Issue No 2 Two Phase Clocked Adiabatix Logic For Low Power Multiplier 255 260Документ6 страниц24.IJAEST Vol No 5 Issue No 2 Two Phase Clocked Adiabatix Logic For Low Power Multiplier 255 260iserpОценок пока нет

- Parameter Analysis of ECRL & 2N2N-2P Energy Recovery ComparatorsДокумент5 страницParameter Analysis of ECRL & 2N2N-2P Energy Recovery ComparatorsInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- A New Design Technique For Low Power Dynamic Feedthrough Logic With Delay ElementДокумент5 страницA New Design Technique For Low Power Dynamic Feedthrough Logic With Delay ElementET181018 Md Maharaj KabirОценок пока нет

- Adiabatic Implementation On Full Adder Circuits: R.Swapna, Shoban MudeДокумент5 страницAdiabatic Implementation On Full Adder Circuits: R.Swapna, Shoban MudeshrivathsavsОценок пока нет

- Low Power Adiabatic Logic Design: G.P.S. Prashanti, N. Navya Sirisha, N. Akhila ReddyДокумент7 страницLow Power Adiabatic Logic Design: G.P.S. Prashanti, N. Navya Sirisha, N. Akhila ReddyprasanthiОценок пока нет

- Performance of FinFET Based Adiabatic Logic CircuitsДокумент6 страницPerformance of FinFET Based Adiabatic Logic CircuitsJaspreet SalujaОценок пока нет

- Performance Analysis of Positive Feedback Adiabatic Logic For Low PowerДокумент7 страницPerformance Analysis of Positive Feedback Adiabatic Logic For Low PowerKiran KumarОценок пока нет

- A Novel Design of Adder For Ultra Low Power Application: M A, M M K, I BДокумент6 страницA Novel Design of Adder For Ultra Low Power Application: M A, M M K, I BAmeem Ahmed KhanОценок пока нет

- Adiabatic Logic Circuits: A Retrospect: Deepti Shinghal Amit Saxena Arti NoorДокумент7 страницAdiabatic Logic Circuits: A Retrospect: Deepti Shinghal Amit Saxena Arti NoorshrivathsavsОценок пока нет

- Efficient Design of 1Документ7 страницEfficient Design of 1sumathiОценок пока нет

- Low Power Dissipation in Johnson Counter Using DFAL TechniqueДокумент4 страницыLow Power Dissipation in Johnson Counter Using DFAL TechniqueEditor IJRITCCОценок пока нет

- 0.5 V Supply Resistorless Voltage Reference For Low Voltage ApplicationsДокумент6 страниц0.5 V Supply Resistorless Voltage Reference For Low Voltage ApplicationsSteven Curly ComalingОценок пока нет

- An Adiabatic Approach For Low Power Full Adder DesДокумент15 страницAn Adiabatic Approach For Low Power Full Adder Dessai tejuswiniОценок пока нет

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Документ16 страниц1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraОценок пока нет

- Pre-Settable Sequential Circuits Design Using Single-Clocked Energy Efficient Adiabatic LogicДокумент6 страницPre-Settable Sequential Circuits Design Using Single-Clocked Energy Efficient Adiabatic LogicSiam HasanОценок пока нет

- Final ProjectДокумент5 страницFinal Projectnksharma.naveen1855Оценок пока нет

- Analyzing Energy-Delay Behavior in Room Temperature Single Electron TransistorsДокумент6 страницAnalyzing Energy-Delay Behavior in Room Temperature Single Electron Transistorsveeresh_bitОценок пока нет

- Design and Analysis of CMOS and Adiabatic 4-Bit Binary MultiplierДокумент4 страницыDesign and Analysis of CMOS and Adiabatic 4-Bit Binary MultipliervaseemalikhanОценок пока нет

- Tahmasbi Fard2018 PDFДокумент8 страницTahmasbi Fard2018 PDFMahum JamilОценок пока нет

- Reliability Prediction For Low Power Adiabatic Logic FamiliesДокумент6 страницReliability Prediction For Low Power Adiabatic Logic FamilieshakikОценок пока нет

- INTEGRATION, The VLSI Journal: Keivan Navi, Mehrdad Maeen, Vahid Foroutan, Somayeh Timarchi, Omid KaveheiДокумент11 страницINTEGRATION, The VLSI Journal: Keivan Navi, Mehrdad Maeen, Vahid Foroutan, Somayeh Timarchi, Omid KaveheiDeepak RajeshОценок пока нет

- Research Paper IjvesДокумент5 страницResearch Paper Ijveshemendra07Оценок пока нет

- Architectural-Level Low-Power Design: Naehyuck Chang Dept. of EECS/CSE Seoul National University Naehyuck@snu - Ac.krДокумент53 страницыArchitectural-Level Low-Power Design: Naehyuck Chang Dept. of EECS/CSE Seoul National University Naehyuck@snu - Ac.krRMD Academic CoordinatorОценок пока нет

- Energy-Efficient Low Dropout Regulator With Switching Mechanism and Course Regulator For Internet of Things (Iot) DevicesДокумент11 страницEnergy-Efficient Low Dropout Regulator With Switching Mechanism and Course Regulator For Internet of Things (Iot) DevicesijesajournalОценок пока нет

- Proceedings 2005Документ21 страницаProceedings 2005api-3805241Оценок пока нет

- Design of A Low Power Dynamic Comparator in 180nm CMOS TechnologyДокумент6 страницDesign of A Low Power Dynamic Comparator in 180nm CMOS TechnologyVishnu VardhanОценок пока нет

- High PSRR Voltage Reference Circuit With Dual-Output For Low Power ApplicationsДокумент4 страницыHigh PSRR Voltage Reference Circuit With Dual-Output For Low Power Applicationsmd istiyakОценок пока нет

- Unit 2 QB With AnswersДокумент13 страницUnit 2 QB With AnswersECE SakthivelОценок пока нет

- A Comparative Study Between Different Types of Adders and MultipliersДокумент5 страницA Comparative Study Between Different Types of Adders and MultipliersVivek SinghОценок пока нет

- Low-Voltage Low-Overhead Asynchronous LogicДокумент6 страницLow-Voltage Low-Overhead Asynchronous LogicJon DCОценок пока нет

- ANALYSIS OF PWM TECHNIQUES APPLIED TO HALF BRIDGE ANPC INVERTER CONNECTED TO GRID Ijariie3291Документ11 страницANALYSIS OF PWM TECHNIQUES APPLIED TO HALF BRIDGE ANPC INVERTER CONNECTED TO GRID Ijariie3291fgokcegozОценок пока нет

- Distributed Active Transformer-A New Power-Combining and Impedance-Transformation TechniqueДокумент16 страницDistributed Active Transformer-A New Power-Combining and Impedance-Transformation Techniquereddy balajiОценок пока нет

- Low-Power Digital Systems Based On Adiabatic3 Witching PrinciplesДокумент10 страницLow-Power Digital Systems Based On Adiabatic3 Witching PrinciplesVishwas GosainОценок пока нет

- Nanometer MOSFETДокумент12 страницNanometer MOSFETSibi ManojОценок пока нет

- Design of ALU Circuits Using Pass Transistor LogicДокумент71 страницаDesign of ALU Circuits Using Pass Transistor LogicVivek GuntumuduguОценок пока нет

- 2102-Ritu Sharma 2Документ4 страницы2102-Ritu Sharma 2Dr-Irfan Ahmad PindooОценок пока нет

- Lasc As 2010Документ4 страницыLasc As 2010Rahul ShandilyaОценок пока нет

- Lallart 2008Документ9 страницLallart 2008Minh Le VanОценок пока нет

- Analysis of Full Adder Using Adiabatic Charge Recovery LogicДокумент6 страницAnalysis of Full Adder Using Adiabatic Charge Recovery LogicBibartan DasОценок пока нет

- Designing of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyДокумент7 страницDesigning of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyAMIT VERMAОценок пока нет

- Cmos Transistor AdderДокумент9 страницCmos Transistor AdderRahul KannojiaОценок пока нет

- A Cold-Startup SSHI Rectifier For Piezoelectric Energy Harvesters With Increased Open-Circuit VoltageДокумент12 страницA Cold-Startup SSHI Rectifier For Piezoelectric Energy Harvesters With Increased Open-Circuit VoltageHafeez KtОценок пока нет

- A Flip-Flop For The DPA Resistant Three-Phase Dual-RailДокумент5 страницA Flip-Flop For The DPA Resistant Three-Phase Dual-RailSethu GeorgeОценок пока нет

- Capless Ldo ThesisДокумент7 страницCapless Ldo Thesisgjaj8vvw100% (1)

- FORTRAN Based ApproachДокумент22 страницыFORTRAN Based ApproachGS EKTAОценок пока нет

- INTEGRATION, The VLSI Journal: Fang Tang, Amine Bermak, Zhouye GuДокумент10 страницINTEGRATION, The VLSI Journal: Fang Tang, Amine Bermak, Zhouye GuET181018 Md Maharaj KabirОценок пока нет

- Design of Small Printed Multiband Loop Antennas For Short Range Wireless (SRW) ApplicationsДокумент9 страницDesign of Small Printed Multiband Loop Antennas For Short Range Wireless (SRW) Applicationsabdou lamkaОценок пока нет

- A Low-Power 1-V Supply Dynamic ComparatorДокумент4 страницыA Low-Power 1-V Supply Dynamic Comparator22pimt01Оценок пока нет

- Sub-Threshold Adiabatic Logic For Low Power ApplicationsДокумент7 страницSub-Threshold Adiabatic Logic For Low Power ApplicationsarcherselevatorsОценок пока нет

- Power ElectronicsДокумент27 страницPower ElectronicsAnand Pon KumarОценок пока нет

- Adiabatic Technique FOR Low Power VlsiДокумент16 страницAdiabatic Technique FOR Low Power VlsiAnamika PancholiОценок пока нет

- Design and Implementation of Combinational Circuits Using Reversible Logic On FPGA SPARTAN 3EДокумент6 страницDesign and Implementation of Combinational Circuits Using Reversible Logic On FPGA SPARTAN 3Evarsha muthyalaОценок пока нет

- Wair Ya 2010Документ6 страницWair Ya 2010abhishek shuklaОценок пока нет

- 2007 Nonis TCAS CML Divider DesignДокумент10 страниц2007 Nonis TCAS CML Divider DesignDavidОценок пока нет

- Implementation of Low Power Test Pattern Generator Using LFSRДокумент6 страницImplementation of Low Power Test Pattern Generator Using LFSRIjsrnet EditorialОценок пока нет

- Review On Low Power Energy Efficient VLSI Circuits Using Adiabatic LogicДокумент3 страницыReview On Low Power Energy Efficient VLSI Circuits Using Adiabatic LogicerpublicationОценок пока нет

- A 32-Bit ALU With Sleep Mode For Leakage Power Reduction: AbstractДокумент7 страницA 32-Bit ALU With Sleep Mode For Leakage Power Reduction: Abstractig77Оценок пока нет

- Novel Architectures For High-Speed and Low-Power 3-2, 4-2 and 5-2 CompressorsДокумент6 страницNovel Architectures For High-Speed and Low-Power 3-2, 4-2 and 5-2 CompressorsMe himpОценок пока нет

- Comp ProjДокумент12 страницComp ProjMe himpОценок пока нет

- Delhi Technological University B.TECH. ADMISSIONS 2018-19: BT CE COE ECE EE ENE EP IT MAM MCE ME PCT PIE SEДокумент2 страницыDelhi Technological University B.TECH. ADMISSIONS 2018-19: BT CE COE ECE EE ENE EP IT MAM MCE ME PCT PIE SEShailendra KumarОценок пока нет

- Chemistry Class 12 Project CbseДокумент1 страницаChemistry Class 12 Project CbseMe himpОценок пока нет

- English Set 1Документ8 страницEnglish Set 1Me himpОценок пока нет

- English Set IДокумент15 страницEnglish Set IafОценок пока нет

- Arm Inst PDFДокумент100 страницArm Inst PDFAshley Jovian CorreaОценок пока нет

- Chapter 7 Start PDFДокумент25 страницChapter 7 Start PDFMe himpОценок пока нет

- Marriage Families Separation Information PackДокумент6 страницMarriage Families Separation Information PackFatima JabeenОценок пока нет

- Q3 Lesson 5 MolalityДокумент16 страницQ3 Lesson 5 MolalityAly SaОценок пока нет

- Rebecca Young Vs CAДокумент3 страницыRebecca Young Vs CAJay RibsОценок пока нет

- IndianJPsychiatry632179-396519 110051Документ5 страницIndianJPsychiatry632179-396519 110051gion.nandОценок пока нет

- PEG Catalog Siemens PDFДокумент419 страницPEG Catalog Siemens PDFrukmagoudОценок пока нет

- Chapin Columbus DayДокумент15 страницChapin Columbus Dayaspj13Оценок пока нет

- Debarchana TrainingДокумент45 страницDebarchana TrainingNitin TibrewalОценок пока нет

- Monastery in Buddhist ArchitectureДокумент8 страницMonastery in Buddhist ArchitectureabdulОценок пока нет

- Pediatric ECG Survival Guide - 2nd - May 2019Документ27 страницPediatric ECG Survival Guide - 2nd - May 2019Marcos Chusin MontesdeocaОценок пока нет

- Gamboa Vs Chan 2012 Case DigestДокумент2 страницыGamboa Vs Chan 2012 Case DigestKrissa Jennesca Tullo100% (2)

- What Is SCOPIC Clause - A Simple Overview - SailorinsightДокумент8 страницWhat Is SCOPIC Clause - A Simple Overview - SailorinsightJivan Jyoti RoutОценок пока нет

- Mooting ExampleДокумент35 страницMooting Exampleluziro tenОценок пока нет

- Caregiving Learning Activity Sheet 3Документ6 страницCaregiving Learning Activity Sheet 3Juvy Lyn CondaОценок пока нет

- Pa Print Isang Beses LangДокумент11 страницPa Print Isang Beses LangGilbert JohnОценок пока нет

- Field Assignment On Feacal Sludge ManagementДокумент10 страницField Assignment On Feacal Sludge ManagementSarah NamyaloОценок пока нет

- Tour Guiding and Escort Services - 301Документ95 страницTour Guiding and Escort Services - 301Zane 19531Оценок пока нет

- Theo Hermans (Cáp. 3)Документ3 страницыTheo Hermans (Cáp. 3)cookinglike100% (1)

- Contoh RPH Ts 25 Engish (Ppki)Документ1 страницаContoh RPH Ts 25 Engish (Ppki)muhariz78Оценок пока нет

- APICS-Houston Newsletter Sept 2012Документ16 страницAPICS-Houston Newsletter Sept 2012Christopher SeifertОценок пока нет

- Project TitleДокумент15 страницProject TitleadvikaОценок пока нет

- Magnetism 1Документ4 страницыMagnetism 1krichenkyandex.ruОценок пока нет

- First Aid General PathologyДокумент8 страницFirst Aid General PathologyHamza AshrafОценок пока нет

- APA CitationsДокумент9 страницAPA CitationsIslamОценок пока нет

- Grave MattersДокумент19 страницGrave MattersKeith Armstrong100% (2)

- S Jozsef Viata in DiosigДокумент52 страницыS Jozsef Viata in Diosigunoradean2Оценок пока нет

- Chapter 15 (Partnerships Formation, Operation and Ownership Changes) PDFДокумент58 страницChapter 15 (Partnerships Formation, Operation and Ownership Changes) PDFAbdul Rahman SholehОценок пока нет

- Buddhism & Tantra YogaДокумент2 страницыBuddhism & Tantra Yoganelubogatu9364Оценок пока нет

- Imogen Powerpoint DesignДокумент29 страницImogen Powerpoint DesignArthur100% (1)

- Lesson 73 Creating Problems Involving The Volume of A Rectangular PrismДокумент17 страницLesson 73 Creating Problems Involving The Volume of A Rectangular PrismJessy James CardinalОценок пока нет

- Berrinba East State School OSHC Final ITO For Schools Final 2016Документ24 страницыBerrinba East State School OSHC Final ITO For Schools Final 2016hieuntx93Оценок пока нет