Академический Документы

Профессиональный Документы

Культура Документы

Analisis Comparativo y Conclusiones

Загружено:

Laura CaicedoОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Analisis Comparativo y Conclusiones

Загружено:

Laura CaicedoАвторское право:

Доступные форматы

Análisis comparativo y conclusiones

8.- Análisis comparativo y conclusiones.

En esta sección vamos a comparar las distintas arquitecturas comentadas en

los apartados anteriores y también vamos a analizar los resultados obtenidos con

Matlab.

8.1.- Arquitecturas.

En el presente proyecto hemos divido las arquitecturas posibles para

implementar la FFT en cuatro grandes grupos: arquitectura con un microprocesador,

arquitectura basada en un DSP, arquitectura con un multiprocesador o un DSP

especializado y arquitecturas totalmente especializadas.

De estos cuatro grandes grupos, los tres primeros quedan totalmente

descartados. Aunque estos grupos son los más flexibles (aspecto deseado a la hora

de diseñar un circuito), el hecho del elevado consumo de potencia así como el tiempo

invertido en obtener el resultado hacen que esas opciones se vean descartadas.

Por lo anteriormente expuesto, sólo nos queda una opción válida: una

arquitectura totalmente especializada. Como inconvenientes de este tipo de

arquitecturas podemos decir que no es muy flexible, pero se gana tanto en área,

rapidez y consumo.

Una vez decidido que necesitamos una arquitectura especializada se nos

plantea una nueva elección: una arquitectura “in place” o una arquitectura del tipo

pipeline.

Las arquitecturas “in place” presentan una clara ventaja en área respecto a las

arquitecturas pipeline. Esto es así, ya que las arquitecturas “in place” solo requieren

una memoria en la que se almacenan todos los datos (los datos de entrada, los datos

intermedios y los datos de salida). Además solamente se implementa un módulo

butterfly, lo que implica un ahorro importante de memoria.

Hay que aclarar que un módulo butterfly, si estamos en un caso radix-2, implica

una multiplicación compleja y un sumador. Esa multiplicación compleja, lleva implícitas

cuatro multiplicaciones reales. Con esto quiero poner de manifiesto, que de

implementar un solo módulo a implementar varios hay una diferencia apreciable en

cuanto a área.

Escuela Superior de Ingenieros 102

Análisis comparativo y conclusiones

Pero estas arquitecturas no solo presentan ventajas, el principal y gran

inconveniente es el excesivo tiempo de cálculo, respecto a las arquitecturas pipeline.

Las arquitecturas pipeline, se emplean para casos de tiempo real, y presenta

características como un simplicidad, modularidad y un alto rendimiento. Este

rendimiento elevado viene dado porque las arquitecturas “in place” realizan una

butterfly por ciclo, mientras que las arquitecturas pipeline realizan una butterfly por

etapa por ciclo.

Para poder elegir entre un grupo u otro, tenemos que acudir a la aplicación

para la que se va a emplear. Si vamos a usar dicho módulo en una aplicación en

tiempo real, tenemos que acudir inevitablemente a la arquitectura pipeline; sino

podemos elegir entre cualquiera de las dos opciones. En este último caso acudiríamos

a magnitudes como el área o el consumo de potencia para discernir entre una u otra.

Obviamente, si tenemos una alta restricción en área es mejor usar una arquitectura in

place, ya que el consumo de área es menor. Mientras que si tenemos una restricción

en potencia, tendríamos que analizar cada arquitectura de forma específica dentro de

cada grupo para poder realizar una comparación.

Si nos decantamos por una arquitectura “in place”, tenemos varias opciones en

las que elegir. Básicamente todas las opciones presentadas y comentadas en el

presente proyecto, se basan en el trabajo desarrollado por Cohen en [7]. Cohen fue el

realmente pionero, ya que basándose en el trabajo previo de Pease [31], propuso un

control lógico simplificado para un procesador FFT radix-2. Basándose en dicho

trabajo, el resto de las arquitecturas buscan mejorar el esquema de Cohen.

Si tuviéramos que elegir alguno nos decantaríamos por el esquema de Ma y

Wanhammar [8] [9], el esquema de Hasan y Arslan [10] [11] o un esquema radix-mixto

[15]. Hemos desechado las otras arquitecturas porque incluyen o una memoria extra, o

muchos módulos butterfly lo que implica un aumento de área considerable. Las dos

primeras opciones seleccionadas proponen mejoras al esquema de Cohen y obtienen

resultados mejores en el tiempo de retraso, en el consumo de área y en el consumo de

potencia. El esquema radix-mixto busca una mayor rapidez en la ejecución sin tener

que aumentar el área. Es muy útil en los casos que la longitud de la secuencia no es

múltiplo de cuatro.

Si nos decantamos por una arquitectura de tipo pipeline, no cabe duda que la

mejor opción es la arquitectura R22SDF (Radix-22 Single-path Delay Feedback), ya

que consigue unir las mejores características de los distintos algoritmos (tiene la

misma complejidad en las multiplicaciones que el caso radix-4, pero conserva la

misma estructura de butterflies que el algoritmo radix-2). Los requerimientos hardware

de esta arquitectura son mínimos en dos componentes dominantes: log4 N -1

multiplicadores complejos y N-1 datos de tamaño de la memoria. Además la

complejidad del algoritmo de control es muy simple.

Escuela Superior de Ingenieros 103

Análisis comparativo y conclusiones

8.2.- Estudio de la cuantización.

Con los resultados que nos ha proporcionado Matlab, vamos a realizar tres

análisis diferentes. Primero vamos a analizar el caso radix-2 en su totalidad, para

luego hacer lo mismo con el caso radix-4. Por último vamos a comparar los dos casos

(radix-2 y radix-4).

8.2.1.- Radix-2.

De las gráficas y tablas de la sección anterior podemos sacar una serie de

conclusiones:

• A medida que la longitud de la secuencia de entrada aumenta, la SNR

disminuye. El valor de la SNR cae aproximadamente unos 6dB cada

vez que la longitud de la secuencia de entrada se cuadruplica. La causa

de esta disminución se debe a que al aumentar la longitud, aumenta el

número de operaciones a realizar por lo que el error cometido aumenta,

de ahí que disminuya la SNR.

• Variando el número de cuantización de los twiddle se vuelve a poner de

manifiesto lo comentado en el punto anterior. También se pone de

manifiesto cómo al aumentar el número de bits utilizados para cuantizar

los twiddle, la SNR aumenta de valor. Esto es lógico ya que

aumentamos la precisión con la que se representa el número.

Como se ha mantenido una cuantización en el resto de los puntos (en

los datos de entrada, en la multiplicación, en la memoria interna y en los

datos de salida), la SNR llega a un valor máximo, es decir, no podemos

aumentarla todo lo que queramos sólo variando la cuantización en los

twiddle. Llega un momento en que por mucho que variemos el número

de bits la SNR permanece constante. El número de bits para el cual la

SNR permanece prácticamente constante vale lo mismo sea cual sea la

longitud a analizar.

Si queremos dimensionar correctamente este valor tomaremos

NB_TWE=10, ya que para un valor mayor la SNR no sufre una variación

significativa.

• Variando el número de bits empleados en la multiplicación llegamos a

las mismas conclusiones que en el punto anterior: la SNR aumenta a

medida que el número de bits aumenta, hasta que se estabiliza en un

valor.

El número de bits para el cual se alcanza el máximo valor de la SNR es

igual para todas las longitudes, y en este caso (con los valores que se

tomaron para obtener el resultado numérico) vale 11.

Escuela Superior de Ingenieros 104

Análisis comparativo y conclusiones

En este caso si hay que comentar, que no nos vale un número muy

pequeño en el número de bits empleados, ya que sino no se obtendría

un valor fiable de la FFT (sobre todo para una longitud elevada de la

señal de entrada).

• Cuando variamos el número de bits empleados en la memoria interna,

se vuelve a poner de manifiesto lo comentado en el punto anterior. Para

este caso, el valor óptimo del número de bits de cuantización sería

NB_MEM=11, ya que si aumentamos más dicho valor la SNR no varía

significativamente. Al igual que ocurría para los otros casos, dicho valor

es independiente de la longitud de la secuencia de entrada.

Analizando los cambios que sufre el valor de la SNR cuando variamos el

número de bits de cuantización, podemos llegar a obtener la mejor combinación de los

mismos para maximizar la SNR. Hay que tener presente el valor deseado de SNR

para buscar la mejor combinación de dichos valores.

8.2.2.- Radix-4.

Viendo los resultados obtenidos en la sección anterior para el caso radix-4,

podemos sacar las mismas conclusiones que las sacadas para el caso radix-2.

• La SNR disminuye a medida que la longitud de la secuencia de entrada

aumenta a una razón aproximada de unos 6dB cada vez que se

cuadruplica la longitud de la secuencia de entrada.

• A mayor número de bits empleados en cuantizar los twiddle, mayor

SNR. Se alcanza un máximo en el número de bits que vale lo mismo

para todas las longitudes, ya que a partir de él la SNR no sufre una

variación significativa. En este caso dicho máximo se encuentra para

NB_TWE=10.

• Si el número de bits empleados en cuantizar la multiplicación aumenta,

la SNR también aumenta. Al igual que en los casos anteriores, la SNR

satura para un determinado número de bits que es igual pata todas las

longitudes (dicho máximo se alcanza para NB_MUL=11).

• La SNR aumenta al aumentar el número de bits empleados en cuantizar

la memoria interna. También se alcanza un valor máximo que en este

caso vale NB_MEM=12.

Si queremos obtener una SNR determinada, al igual que ocurría para el caso

radix-2, analizando la variación que sufre la SNR respecto al numero de bits de

cuantización, obtenemos la mejor relación entre los mismos para alcanzar dicho valor.

Escuela Superior de Ingenieros 105

Análisis comparativo y conclusiones

8.2.3.- Radix-2 y Radix-4.

Vamos a comparar los valores de la SNR que obtenemos para los dos casos.

Reescribiremos dichos valores de forma conjunta para que se vez más claro la

relación entre los mismos.

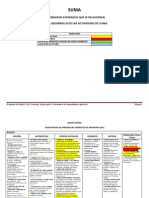

SNR (dB)

Longitud

Radix-2 Radix-4

16 40.993 43.739

64 34.496 38.438

256 28.647 31.973

1024 22.713 25.738

4096 16.804 19.929

Tabla 8. 1.- Comparación entre la SNR del caso radix-2 y radix-4.

La tabla anterior se ha obtenido de la sección 6 y se corresponde con la Tabla

6.7 y la Tabla 6.18. Estos valores se obtienen (para los dos casos) al realizar una

cuantización en todos los puntos usando los valores por defecto y tomando como

entrada la matriz de entradas.

Comparando los datos de la tabla anterior podemos observar que obtenemos

un mejor valor de la SNR utilizando el radix-4 que usando el radix-2. La razón de esta

mejora radica en que el radix-4 tiene un menor número de multiplicadores y

sumadores. Esto se debe a que el módulo butterfly que emplea el radix-4 es de mayor

tamaño y por lo tanto realiza menos operaciones. Como realiza un menor número de

operaciones implica que el error cometido es menor.

La desventaja que presenta el radix-4 respecto al radix-2 es el aumento de

área. No solo aumenta el área utilizada por aumentar el tamaño del módulo butterfly,

sino también por que la lógica necesaria para conseguir las direcciones adecuadas de

los datos aumenta en complejidad y por lo tanto en área.

Escuela Superior de Ingenieros 106

Análisis comparativo y conclusiones

8.3.- Estudio del número de ciclos.

En la sección anterior hemos puesto de manifiesto la importancia del número

de ciclos a la hora de seleccionar una arquitectura u otra.

Hemos comprobado como la arquitectura más rápida es la R22SDF, ya que

obtiene el valor de la FFT en el menor número de ciclos. Sin embargo tiene el

inconveniente de que ocupa mucha área y consume mucha potencia si la comparamos

con el resto de arquitecturas.

Las arquitecturas “in place” obtienen la solución en un mayor número de ciclos,

sin embargo ocupan menos área y consumen menos potencia que las arquitecturas

pipeline. Dentro de las mismas, la que obtiene la solución en un menor número de

ciclos es la arquitectura de Cohen, siempre que la longitud sea un múltiplo de 4. Si la

longitud no es factor de 4 la mejor opción sería emplear una arquitectura radix-mixto.

También hay que resaltar las ventajas de emplear un radix-4 a un radix-2 ya

que nos permite obtener la solución en menos tiempo, consiguiendo además un valor

más elevado de la SNR. Como inconveniente tiene que el área ocupada es mayor al

igual que el consumo de potencia

En resumen, si tenemos una fuerte restricción en el número de ciclos que debe

tardar nuestra arquitectura, sabemos que la elección debe ser una de tipo pipeline. Por

el contrario si no tenemos ese tipo de restricción, siempre será mejor decantarse por

una arquitectura “in place”, debido a lo anteriormente expuesto.

Escuela Superior de Ingenieros 107

Вам также может понравиться

- P 003 - Procedimiento de Investigación de Accidentes e Incidentes de TrabajoДокумент20 страницP 003 - Procedimiento de Investigación de Accidentes e Incidentes de TrabajoPerla Villegas100% (1)

- Proyecto Pozo A Tierra CorregidoДокумент28 страницProyecto Pozo A Tierra CorregidoDlc MiguelОценок пока нет

- ExP Uni2022-I EE418 MNO VBДокумент2 страницыExP Uni2022-I EE418 MNO VBRoy Vega100% (1)

- Manual - Centrifuga LW Scientific Model E8Документ2 страницыManual - Centrifuga LW Scientific Model E8Soporte Técnico Electronitech100% (1)

- 26 - El Ladron de TiempoДокумент196 страниц26 - El Ladron de TiempoKristell Bonilla Ramírez100% (1)

- Folle ToДокумент1 страницаFolle ToLaura CaicedoОценок пока нет

- Mi Yo Del FuturoДокумент1 страницаMi Yo Del FuturoLaura CaicedoОценок пока нет

- Artistic AДокумент1 страницаArtistic ALaura CaicedoОценок пока нет

- Artistic AДокумент1 страницаArtistic ALaura CaicedoОценок пока нет

- Mi Libro DoradoДокумент24 страницыMi Libro DoradoLaura CaicedoОценок пока нет

- Filosodia LauarДокумент6 страницFilosodia LauarLaura CaicedoОценок пока нет

- Analisis Comparativo y ConclusionesДокумент6 страницAnalisis Comparativo y ConclusionesLaura CaicedoОценок пока нет

- Filosodia LauarДокумент6 страницFilosodia LauarLaura CaicedoОценок пока нет

- Documento 5Документ3 страницыDocumento 5Laura CaicedoОценок пока нет

- Agenda 2 1075 Taller de AdnДокумент4 страницыAgenda 2 1075 Taller de AdnLaura CaicedoОценок пока нет

- Estadistica 7-ProbabilidadДокумент64 страницыEstadistica 7-ProbabilidadJosé Luis AlvarezОценок пока нет

- Propiedades de La LuzДокумент5 страницPropiedades de La LuzRené ZavalaОценок пока нет

- Autoevaluacion CinematicaДокумент1 страницаAutoevaluacion CinematicaYisus 264Оценок пока нет

- Ecuacion de Balance de Materia para Yacimientos de GasДокумент3 страницыEcuacion de Balance de Materia para Yacimientos de GasJuan LuixОценок пока нет

- INFOGRAFIAДокумент1 страницаINFOGRAFIAPablo MoraОценок пока нет

- AMATISTAДокумент9 страницAMATISTAJose Carlos Amado RamirezОценок пока нет

- Manual Del Producto 16Документ2 страницыManual Del Producto 16Oscar VillamizarОценок пока нет

- ALCOHOLESДокумент14 страницALCOHOLESEFRAINОценок пока нет

- Cfe P33Документ3 страницыCfe P33Alberto GonzalezОценок пока нет

- BDPH1200 ManualДокумент36 страницBDPH1200 ManualAngel SuárezОценок пока нет

- Concentrado - Aprendizajes Esperados - Grado 5° - V2.0Документ7 страницConcentrado - Aprendizajes Esperados - Grado 5° - V2.0Yessi LopezОценок пока нет

- Proyecto de FundicionДокумент25 страницProyecto de FundicionMichael Maque0% (1)

- Pin FisicaДокумент8 страницPin FisicaA. Cesar Grimaldez MamaniОценок пока нет

- Catálogo de Conceptos CDMXДокумент372 страницыCatálogo de Conceptos CDMXBlanca Oliver100% (2)

- Esfuerzos de La EstructuraДокумент8 страницEsfuerzos de La EstructuraadadadadОценок пока нет

- Tarea Semana 5 - Energias AlternativasДокумент3 страницыTarea Semana 5 - Energias AlternativasIgnacio SaunierОценок пока нет

- Taller de Tecnologia Grado 7 3p Tipos de EnergiaДокумент9 страницTaller de Tecnologia Grado 7 3p Tipos de EnergiaDana PatiñoОценок пока нет

- Cálculos y Tablas de Intensidades Admisibles en Cuadros Eléctricos PDFДокумент5 страницCálculos y Tablas de Intensidades Admisibles en Cuadros Eléctricos PDFvicente manuel castello bioscaОценок пока нет

- LABORATORIO #3 CapilaridadДокумент9 страницLABORATORIO #3 CapilaridadEdder Andrés Potosí VillacísОценок пока нет

- Utensilios de La CocteleriaДокумент3 страницыUtensilios de La CocteleriaSam TobíoОценок пока нет

- Taichi 2Документ6 страницTaichi 2Claudio Nelson Estela100% (1)

- Actividad 4Документ7 страницActividad 4Diana Paola Salazar SurezОценок пока нет

- Capitulo 05 QuimicosДокумент10 страницCapitulo 05 QuimicosalexisОценок пока нет

- 4 Saludos Protocolares y PresentacionesДокумент39 страниц4 Saludos Protocolares y PresentacioneslorenaОценок пока нет

- Bayes EjerciciosДокумент9 страницBayes Ejerciciosismael8888Оценок пока нет