Академический Документы

Профессиональный Документы

Культура Документы

ALU-Quichimbo Pablo

Загружено:

Pablo Andrés QuichimboОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

ALU-Quichimbo Pablo

Загружено:

Pablo Andrés QuichimboАвторское право:

Доступные форматы

UNIDAD ARITMÉTICA LÓGICA “A.L.U.

”

QUICHIMBO PLAZA PABLO ANDRES

Universidad Politécnica Salesiana

E-mail: pquichimbo@est.ups.edu.ec

I. RESUMEN

En el siguiente informe se detallara el funcionamiento de los circuitos que forman la

unidad aritmética lógica “ALU” de 4 bits en binario, el cual esta conformado de

operaciones aritméticas: suma, resta y multiplicación. La visualización de los números

ingresados y la respuesta obtenida se presentaran mediante displays. El mismo es

comandado mediante un sistema de control, para la elección de las operaciones que se

desea obtener como respuesta.

Palabras claves: A.L.U, Bits, Displays.

II. INTRODUCCIÓN

El desarrollo de un ALU, se fundamenta en un conjunto de operaciones aritmeticas, es

decir suma, resta, multiplicación, etc. Para el desarrollo del mismo se basa en la

utilización de componentes digitales, como sumadores, comparadores, displays, entre

otros.

III. DESARROLLO

1.- DATOS DE INGRESO

Fig.1. Datos de ingreso en forma de binário.

En la Fig.1, se observa la configuracion para los datos de ingreso, los mismo son activos

a 1=5V, el ingreso de los valores es mediante la configuración de números binários, las

señales emitidas por los diferentes switch ingresan a los decodificadores 7447 que son

activo a 1, los decodificadores estan conenctado a un display 7 segmentos para la

visualización de numeros en decimal.

2.- CIRCUITO DE LA OPERACIÓN SUMA

Fig.2. Circuito para realizar la operación de la suma en la Unidad Aritmética Lógica.

En la Fig.2, se observa la circuiteria y la lógica digital utilizada para el desarrollo de la

suma de dos números con 4 bits respectivamente. Los valores o señales enviadas desde

los diferentes switch ingresan al sumador 74LS283, este permite la comparación de los

dos valores binarios que previamente se ingreso, a la misma vez, a la salida de la

compuerta se encuentra la lógica digital desarrollada para la activación del siguiente

sumador; mediante el uso de las compuertas 74HC244, que es una compuerta lógica de

un conjunto 3 estados internos, este sirve para la visualización del resultado de la suma

en el display en un instante del tiempo cuando se active en el control del sistema la

configuración de suma.

3.- CIRCUITO DE LA OPERACIÓN RESTA

Fig.3. Circuito para realizar la operación de la resta en la Unidad Aritmética Lógica.

En la Fig.3, se puede analizar el circuito desarrollado para la obtención de la resta que

esta integrada en la unidad aritmética lógica, el mismo esta conformado por sumador

74HC283, permitiendo asi la comparación de 2 numeros de ingreso en binario, a

continuación se encuentra la lógica digital utilizada para el acoplamiento de la salida del

sumador con el ingreso del siguiente sumador, la lógica intermedia sirve para la

activación del segundo sumador 74HC283, de esta forma da paso a la visualización de

los resultados obtenidos de la resta en un display en general.

4.- CIRCUITO DE LA OPERACIÓN MULTIPLICACIÓN

Fig.4. Circuito para realizar la operación de la multiplicación en la Unidad Aritmética Lógica.

En la Fig.4, se observa la configuración analizada para la visualización de la

multiplicación de 2 números de 4 bits en el ALU, el mismo esta conformado por

compuertas AND al ingreso, estas sirven para seguir un orden ya establecido para la

obtención de la multiplicación, las salidas respectivamente de las compuertas lógicas

ingresan a los sumadores, encargados de comparar los valores de ingreso, para el caso de

la multiplicación se utilizo 3 sumadores 74HC283 divididos en entre las salidas de las

compuertas, a su vez la salidas se dirigen a la circuiteria de control para la intervención

en un cierto tiempo, cuando se active la opción de producto, la visualización será en el

display general.

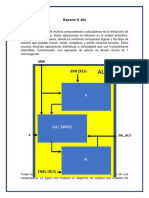

5.- CONTROL DEL SISTEMA Y VISUALIZACIÓN DE LA RESPUESTA

Fig.5. Circuito para el control del sistema en general y la visualización del resultado.

En la Fig.5. se observa el control de la unidad aritmética lógica, a traves de un Dip-switch,

el mismo esta configurado para diferentes tipos de respuesta es decir, cuando el dip esta

un estado de 1, el circuito reponderia con la suma de los valores, cuando el pin 2 del dip

esta en un estado de 1 y el otro de 0, este responderia a una resta, y mientras cuando el

dip este en 3 es decir todos sus estados estan activos realizara la operación de la

multiplicación.

IV. CONCLUSIONES:

Al momento de realizar los diferentes circuitos surgio un problema, en la parte de

la multiplicación ya que no coincidian con los parametros preestablecidos por el

docente, la manera de solucionarlo fue a traves del internet, visualizando un

circuito ya establecido en el mismo.

Para la visualización de todos los resultados un 2 displays comunes se necesito de

compuertas lógicas 74HC244, siendo asi un problema al momento de relacionar

cada operación con el centro de control del sistema.

Вам также может понравиться

- Proyecto ALU. 2Документ20 страницProyecto ALU. 2Abraham HeyerОценок пока нет

- Trabajo Sumador Restador 3 BitsДокумент7 страницTrabajo Sumador Restador 3 BitsPandaОценок пока нет

- Laboratorio Circuitos CombinatoriosДокумент11 страницLaboratorio Circuitos CombinatoriosHeyner Marmol VerbelОценок пока нет

- Practica ALU - CLRДокумент8 страницPractica ALU - CLRRaúl Olmos EstradaОценок пока нет

- Sumador y Restador 4 BitsДокумент17 страницSumador y Restador 4 BitsulisoaОценок пока нет

- COntador BinarioДокумент40 страницCOntador BinarioKasey Turner0% (1)

- Tarea1 - FF y TEMPORIZADORESJДокумент9 страницTarea1 - FF y TEMPORIZADORESJRaúl PalominoОценок пока нет

- Lab - 05 Aritmética BinariaДокумент13 страницLab - 05 Aritmética BinariaPedro Luis Contreras EgusquizaОценок пока нет

- Electronica Decodificador, SumadorДокумент9 страницElectronica Decodificador, SumadorLuis IzaОценок пока нет

- CalculadoraДокумент15 страницCalculadoraValeria Gutierrez RuizОценок пока нет

- SDP6Документ3 страницыSDP6Angelo EspinozaОценок пока нет

- VacaKevin PazmiñoNayro Informe8Документ9 страницVacaKevin PazmiñoNayro Informe8Kevin BlackstarОценок пока нет

- Lenguajes de ProgramacionДокумент20 страницLenguajes de ProgramacioncaxchosОценок пока нет

- Alu 74181Документ9 страницAlu 74181Franck JonhsonОценок пока нет

- Reporte Practica ALU - Equipo 6Документ12 страницReporte Practica ALU - Equipo 6Jerson Cadena M0% (1)

- Circuitos Digitales Medio SumadorДокумент7 страницCircuitos Digitales Medio SumadorMiwel Angel GVОценок пока нет

- Practica 1 Diseño Digital.Документ11 страницPractica 1 Diseño Digital.Angel OrochimaruОценок пока нет

- Decodificador Binario A HexadecimalДокумент5 страницDecodificador Binario A HexadecimalEmmanuel E. AguïlarОценок пока нет

- U2.2 - Circuitos LogicosДокумент15 страницU2.2 - Circuitos LogicosAndres SanchezОценок пока нет

- Sumador y RestadorДокумент14 страницSumador y RestadorHaver Arley Pena ManriqueОценок пока нет

- Upo1 Sistemas DigitalesДокумент16 страницUpo1 Sistemas DigitalesJoseph AndinoОценок пока нет

- Informe CalculadoraДокумент24 страницыInforme CalculadoraZule VallejoОценок пока нет

- Informe 7 de Electronica DigitalДокумент4 страницыInforme 7 de Electronica DigitalDiego ManchayОценок пока нет

- Laboratorio 4Документ3 страницыLaboratorio 4Cristian Laura GalvezОценок пока нет

- Guia de LABORATORIO s7 SumadoresДокумент5 страницGuia de LABORATORIO s7 SumadoresEdwin Jhon0% (1)

- Paso1 - Grupo 28 - Ap Freddy CañarДокумент16 страницPaso1 - Grupo 28 - Ap Freddy CañarCesarAugustoОценок пока нет

- ContadorДокумент13 страницContadorEdwin GavilanezОценок пока нет

- EB09 Eq3 Practica9Документ13 страницEB09 Eq3 Practica9Emiliano Isai Granados ValenciaОценок пока нет

- Reporte de Practica 8 ALUДокумент9 страницReporte de Practica 8 ALUDavid Hernández Osorio100% (1)

- Practica 7 Sistemas ElectronicosДокумент7 страницPractica 7 Sistemas ElectronicosServando ValenzuelaОценок пока нет

- Informe ALU 9969 NarvaezДокумент14 страницInforme ALU 9969 Narvaezfrancisco sotalinОценок пока нет

- 3 Informe Sumador y RestadorДокумент4 страницы3 Informe Sumador y Restadordavila arroyoОценок пока нет

- Programador Lógico DigitalДокумент10 страницProgramador Lógico DigitalJosé Fernando Juárez RamírezОценок пока нет

- Circuito Sumador de 2 Números de 2 BitsДокумент6 страницCircuito Sumador de 2 Números de 2 BitsALEX79% (24)

- Practica U AluДокумент5 страницPractica U AluAmigos LolerosОценок пока нет

- Practica 5Документ10 страницPractica 5Diana ObandoОценок пока нет

- Cronometro Flip Flop JKДокумент8 страницCronometro Flip Flop JKDaniel Lajo Carpio100% (1)

- Trabajo FinalfisicaДокумент3 страницыTrabajo FinalfisicaAsesorias PipeОценок пока нет

- Lab 05 Aritmetica BinariaДокумент13 страницLab 05 Aritmetica BinariaRenzo MelendezОценок пока нет

- Actividad de Aprendizaje 3. Análisis y Diseño de CircuitosДокумент9 страницActividad de Aprendizaje 3. Análisis y Diseño de CircuitosMiguel ÁngelОценок пока нет

- Taller 10 PLC - David Esteban LondoñoДокумент16 страницTaller 10 PLC - David Esteban LondoñoDavid LondoñoОценок пока нет

- Alu 74181Документ10 страницAlu 74181Carlos AlbertoОценок пока нет

- Diseo Digital 3Документ13 страницDiseo Digital 3reyna isabel cob gomezОценок пока нет

- 1 Estructura Funcionamiento ALUДокумент6 страниц1 Estructura Funcionamiento ALUAlbri Reyes100% (3)

- Cronometro Flip Flop JKДокумент8 страницCronometro Flip Flop JKDiego V-aОценок пока нет

- Unidad Aritmético LógicaДокумент3 страницыUnidad Aritmético LógicaMaria Minory100% (1)

- Practica 2 Diseño LógicoДокумент14 страницPractica 2 Diseño LógicoAlan LeónОценок пока нет

- Diseño Sumador RestdorДокумент10 страницDiseño Sumador RestdorRamiro David MОценок пока нет

- Labo 2 sdIIДокумент8 страницLabo 2 sdIINatalia Berrocal GámezОценок пока нет

- A. Compuertas LógicasДокумент37 страницA. Compuertas LógicasDiego CastroОценок пока нет

- Proyecto 1 AluДокумент15 страницProyecto 1 AluMondatta TerkhataОценок пока нет

- Sumador BinarioДокумент4 страницыSumador BinarioJefferson Álvarez ÁlvarezОценок пока нет

- PracticaДокумент10 страницPracticaJonathan CamarilloОценок пока нет

- Reloj Digital InformeДокумент5 страницReloj Digital InformeLizeth Katherine Castillo CárdenasОценок пока нет

- Informe Sumador y Restador 1Документ21 страницаInforme Sumador y Restador 1Mery VelásquezОценок пока нет

- CIdigitales Sabatino DanielFДокумент9 страницCIdigitales Sabatino DanielFDavid FernandezОценок пока нет

- Laboratorio 4 y 5Документ7 страницLaboratorio 4 y 5Johan RMОценок пока нет

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208От EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Оценок пока нет

- UF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasОт EverandUF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasРейтинг: 2.5 из 5 звезд2.5/5 (3)

- Tipos de Temporizadores para AutomatizacionДокумент4 страницыTipos de Temporizadores para Automatizacionjuan0% (1)

- Modelo de Vida - Don BoscoДокумент3 страницыModelo de Vida - Don BoscoPablo Andrés QuichimboОценок пока нет

- Dispositivos Logicos Programables-Quichimbo PabloДокумент3 страницыDispositivos Logicos Programables-Quichimbo PabloPablo Andrés QuichimboОценок пока нет

- Pasa Banda Polos y CerosДокумент4 страницыPasa Banda Polos y CerosPablo Andrés QuichimboОценок пока нет

- Sistemas Microprocesados Practica 4Документ4 страницыSistemas Microprocesados Practica 4Pablo Andrés QuichimboОценок пока нет

- Sistemas Microprocesados Practica 4Документ4 страницыSistemas Microprocesados Practica 4Pablo Andrés QuichimboОценок пока нет

- Frecuencia y PeriodoДокумент2 страницыFrecuencia y PeriodoDafe MontesОценок пока нет

- DocxДокумент13 страницDocxSebastian PaucarОценок пока нет

- R-Reporte Práctica 8 Resistencia y Ley de OhmДокумент8 страницR-Reporte Práctica 8 Resistencia y Ley de OhmRosario Valenzuela BarrazaОценок пока нет

- Valor Del Dinero en El TiempoДокумент27 страницValor Del Dinero en El TiempomanuelОценок пока нет

- Comunicación PLC Simatic s7 Con LabviewДокумент11 страницComunicación PLC Simatic s7 Con LabviewWagner Aguirre RiveraОценок пока нет

- Informe de LecturaДокумент5 страницInforme de LecturaEdward Fernandez MartinezОценок пока нет

- Silabo Programación I 2016 IIДокумент9 страницSilabo Programación I 2016 IIRUBEN GALEAS ARANAОценок пока нет

- Transporte y Asignación Tema 3 MetodosДокумент24 страницыTransporte y Asignación Tema 3 MetodosJULIO MISAEL VARGAS LOPEZОценок пока нет

- Síntesis de Las Ecuaciones para El Cálculo de Las Reactancias Inductiva y Capacitiva de Las Líneas de TransmisiónДокумент5 страницSíntesis de Las Ecuaciones para El Cálculo de Las Reactancias Inductiva y Capacitiva de Las Líneas de TransmisiónGustavoОценок пока нет

- Operadores Aritméticos en CДокумент4 страницыOperadores Aritméticos en CJesús ReañoОценок пока нет

- Ejercicios para ClaseДокумент4 страницыEjercicios para ClaseLuis Egberto Alvarado PintadoОценок пока нет

- Clasificación y Propiedades de Los Polígonos para Segundo Grado de SecundariaДокумент3 страницыClasificación y Propiedades de Los Polígonos para Segundo Grado de Secundariajulio sanchez camones100% (1)

- Cuestionario Ing. IbethДокумент10 страницCuestionario Ing. IbethBOG ESTER VILLAMIL HURTADOОценок пока нет

- Manual Inacap Base Datos I.pdf - Adobe Reader, Versión - Firma1, Firmado Por DAI, 2002.04.26 13 - 24 - 43 - 04'00'Документ97 страницManual Inacap Base Datos I.pdf - Adobe Reader, Versión - Firma1, Firmado Por DAI, 2002.04.26 13 - 24 - 43 - 04'00'Oscar Fabian Parra SepulvedaОценок пока нет

- Cuestionario de EvaluacionДокумент13 страницCuestionario de EvaluacionFidel LantiguaОценок пока нет

- Tarea 1.1 EcuaДокумент3 страницыTarea 1.1 EcuaMAURICIO GABRIEL CANUL POOTОценок пока нет

- Valor Actual NetoДокумент6 страницValor Actual NetoRogger JAckОценок пока нет

- 01 Sistema de NumeracionДокумент8 страниц01 Sistema de NumeracionM23PОценок пока нет

- Taller CompiladoresДокумент6 страницTaller CompiladoresJuan MontesОценок пока нет

- Que Son Los QuarksДокумент3 страницыQue Son Los QuarksJhanet Ampuero100% (2)

- Números Pseudo AleatoriosДокумент6 страницNúmeros Pseudo AleatoriosVictor Enrique Toro AlvarezОценок пока нет

- DennisДокумент19 страницDennisJhoel Sebastian Janampa SernaОценок пока нет

- Nucleo Asfaltico 2Документ8 страницNucleo Asfaltico 2Leyva Castillo Luis Antonio100% (1)

- Aaguia4-5 EST INTERVДокумент6 страницAaguia4-5 EST INTERVFlashero ZzОценок пока нет

- PRÁCTICA DIRIGIDA N°02-Var.Документ2 страницыPRÁCTICA DIRIGIDA N°02-Var.danielОценок пока нет

- Arquitecturas Paralelas y DistribuidasДокумент32 страницыArquitecturas Paralelas y DistribuidasgigipaezespinosaОценок пока нет

- Finales de Mecanica y MecanismosДокумент2 страницыFinales de Mecanica y MecanismosTato FloresОценок пока нет

- Curso Adr (Vcdse - r2m)Документ130 страницCurso Adr (Vcdse - r2m)Jael Castellanos Morales100% (1)

- Tema 2 Tablas de Distribucion de Frecuencia (Una Dos o Multiples EntradasДокумент27 страницTema 2 Tablas de Distribucion de Frecuencia (Una Dos o Multiples EntradasClau GОценок пока нет

- Ensayo SIMCE (6° Básico)Документ4 страницыEnsayo SIMCE (6° Básico)Elcira Alejandra Jaque JaqueОценок пока нет