Академический Документы

Профессиональный Документы

Культура Документы

B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015

Загружено:

jayarami reddy pИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015

Загружено:

jayarami reddy pАвторское право:

Доступные форматы

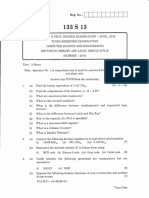

Code: 13A04306 R13

B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015

DIGITAL LOGIC DESIGN

(Common to IT and CSE)

Time: 3 hours Max. Marks: 70

PART – A

(Compulsory Question)

*****

1 Answer the following: (10 X 02 = 20 Marks)

(a) Determine the value of base ‘X’ if (225) x = (341)8.

(b) Find the complement of the function, F = x (y'z' + yz) by taking their duals and complementing each literal.

(c) Define don’t care condition with an example.

(d) Implement EX-OR gate using only NAND gates.

(e) Define priority encoder.

(f) Give the design procedure for the design of a combinational circuit.

(g) What is race around condition? How can we eliminate the race around condition?

(h) Define shift registers.

(i) What are the differences between PLA and PAL?

(j) Define fan out of a logic gate.

PART – B

(Answer all five units, 5 X 10 = 50 Marks)

UNIT - I

2 (a) Convert the following (3456)8 to base 3 and base 7.

(b) Using 2’s complement, perform (42)10-(68)10

OR

3 (a) Simplify the following three variable expression using Boolean algebra: Y = ∑m(1, 3, 5, 7).

(b) Convert the given expression in standard POS form: Y = A.(A + B + C)

UNIT - II

4 (a) Minimize the following function using Karnaugh map method.

f(w,x,y,z)= ∑m(0,7,8,9,10,12) + ∑d (2,5,13)

(b) Implement the following function in NAND-NAND two level forms and draw the circuits.

Y = AC+ABC+A’BC+AB+D

OR

5 Minimize the following function using tabular method.

f(A,B,C,D) = ∑m(0,1,9,15,24,29,30) + ∑d (8,11,31)

UNIT - III

6 (a) Design and draw a full adder circuit.

(b) Implement the following Boolean function using 4 x 1 MUX.

F(a,b,c) = ∑m (1,3,5,6)

OR

7 Design 2 bit magnitude comparator and draw its logic circuit diagram.

UNIT - IV

8 (a) Draw and explain the operation of RS flip-flop.

(b) Design and draw the 3 bit up-down synchronous counter.

OR

9 What are the different types of shift registers? Explain any one type of shift register.

UNIT - V

10 Implement the following functions using PLA.

A (x,y,z )= ∑m (1,2,4,6)

B (x,y,z) = ∑m (0,1,6,7)

C (x,y,z) = ∑m (2,6)

OR

11 (a) Differentiate between RAM and ROM.

(b) Draw and explain the operation of 2 input TTL NAND gate with totem pole output.

*****

Вам также может понравиться

- 15A04306 Digital Logic Design4Документ2 страницы15A04306 Digital Logic Design4Lakshmi PrashanthОценок пока нет

- Question Paper Code:: Y Abcababc + + +Документ3 страницыQuestion Paper Code:: Y Abcababc + + +karthick VijayanОценок пока нет

- B.Tech II Year I Semester (R13) Supplementary Examinations June 2017Документ2 страницыB.Tech II Year I Semester (R13) Supplementary Examinations June 2017Kareem KhanОценок пока нет

- Switching Theory and Logic Design Exam QuestionsДокумент4 страницыSwitching Theory and Logic Design Exam QuestionsrangerОценок пока нет

- Digital Logic Design Exam QuestionsДокумент2 страницыDigital Logic Design Exam QuestionsKareem KhanОценок пока нет

- Digital Logic DesignДокумент4 страницыDigital Logic DesignShareef KhanОценок пока нет

- KEE401 ASSIGNMENTS and QUESTION BANKДокумент17 страницKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaОценок пока нет

- QBank DPSD cs2202Документ6 страницQBank DPSD cs2202kunarajОценок пока нет

- Switching Theory and Logic DesignДокумент6 страницSwitching Theory and Logic DesignVijay MОценок пока нет

- Switching Theory and Logic DesignДокумент8 страницSwitching Theory and Logic DesignVenkat ChadalavadaОценок пока нет

- Question Paper Code:: (10×2 20 Marks)Документ2 страницыQuestion Paper Code:: (10×2 20 Marks)kenny kannaОценок пока нет

- Code No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020Документ2 страницыCode No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020VEMANA DHANESHОценок пока нет

- 9A04401 Switching Theory & Logic DesignДокумент4 страницы9A04401 Switching Theory & Logic DesignsivabharathamurthyОценок пока нет

- ECE211 Digital ElectronicsДокумент3 страницыECE211 Digital Electronicstejaputta6Оценок пока нет

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Документ18 страницUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduОценок пока нет

- 9a04306-Digital Logic DesignДокумент1 страница9a04306-Digital Logic DesignSheikh Noor MohammadОценок пока нет

- 08AB303 DIGITAL LOGIC CIRCUITSДокумент4 страницы08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyОценок пока нет

- Ecs-301 Digital Logic Design 2010-11Документ4 страницыEcs-301 Digital Logic Design 2010-11Satyedra MauryaОценок пока нет

- S T L DДокумент12 страницS T L DMohan Krishna0% (1)

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignДокумент4 страницыWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaОценок пока нет

- STLD Previous PapersДокумент24 страницыSTLD Previous PapersRaju Vericherla100% (1)

- 21 - 2010 - Nov - R09 - STLDДокумент8 страниц21 - 2010 - Nov - R09 - STLDvasuvlsiОценок пока нет

- Nov 2019Документ6 страницNov 2019ponniОценок пока нет

- Srinivasa Ramanujan Institute of TechnologyДокумент2 страницыSrinivasa Ramanujan Institute of TechnologyPandu RangareddyОценок пока нет

- 9A04401 Switching Theory & Logic DesignДокумент4 страницы9A04401 Switching Theory & Logic DesignsivabharathamurthyОценок пока нет

- 9A04306 Digital Logic DesignДокумент4 страницы9A04306 Digital Logic DesignsivabharathamurthyОценок пока нет

- Switching Theory and Logic DesignДокумент8 страницSwitching Theory and Logic DesignSubrahmanyam VjsОценок пока нет

- 07a4ec09 STLDДокумент6 страниц07a4ec09 STLDSRINIVASA RAO GANTAОценок пока нет

- Rr311901 Digital Systems DesignДокумент8 страницRr311901 Digital Systems DesignSrinivasa Rao GОценок пока нет

- 07af303 - Digital Integrated Circuits and Logical DesignДокумент3 страницы07af303 - Digital Integrated Circuits and Logical DesignChandru RamaswamyОценок пока нет

- Sir Padampat Singhania University Digital Electronics ExamДокумент5 страницSir Padampat Singhania University Digital Electronics ExamIyyakutti GanapathiОценок пока нет

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesДокумент12 страницEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PОценок пока нет

- 13A04306 Digital Logic Design1Документ1 страница13A04306 Digital Logic Design1Mahaboob SubahanОценок пока нет

- 08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNДокумент4 страницы08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNChandru RamaswamyОценок пока нет

- Important 16 Mark Questions-19!1!2024Документ5 страницImportant 16 Mark Questions-19!1!2024FLOWERОценок пока нет

- 113BU032016Документ2 страницы113BU032016mushahedОценок пока нет

- 08AC304 - DIGITAL ELECTRONICSДокумент3 страницы08AC304 - DIGITAL ELECTRONICSChandru RamaswamyОценок пока нет

- 9A04306 Digital Logic DesignДокумент4 страницы9A04306 Digital Logic DesignsivabharathamurthyОценок пока нет

- Design Digital Logic Circuits Using K-Maps and Flip-FlopsДокумент2 страницыDesign Digital Logic Circuits Using K-Maps and Flip-FlopsBhaswar ChakrabortyОценок пока нет

- De 7321Документ2 страницыDe 7321नीरज बंसलОценок пока нет

- EC6302-Digital ElectronicsДокумент14 страницEC6302-Digital Electronicsmagy1989Оценок пока нет

- Digital Logic DesignДокумент4 страницыDigital Logic DesignrppvchОценок пока нет

- STLDДокумент2 страницыSTLDANUPAMA PonnuОценок пока нет

- Question Paper Code:: Reg. No.Документ2 страницыQuestion Paper Code:: Reg. No.Monica NareshОценок пока нет

- 9A04401 Switching Theory and Logic DesignДокумент4 страницы9A04401 Switching Theory and Logic DesignsivabharathamurthyОценок пока нет

- WWW - Manaresults.Co - In: (Common To CSE, IT)Документ2 страницыWWW - Manaresults.Co - In: (Common To CSE, IT)Suresh ThallapelliОценок пока нет

- Digital Logic Design (Jntu - Uandistar.org)Документ4 страницыDigital Logic Design (Jntu - Uandistar.org)Arepalli SathibabuОценок пока нет

- R7220404 Switching Theory and Logic DesignДокумент1 страницаR7220404 Switching Theory and Logic DesignsivabharathamurthyОценок пока нет

- P15ec33 Z1Документ2 страницыP15ec33 Z1Arun Kumar K MОценок пока нет

- 9A04306 Digital Logic DesignДокумент2 страницы9A04306 Digital Logic DesignsivabharathamurthyОценок пока нет

- DSD Model Paper 1Документ7 страницDSD Model Paper 1VigneshОценок пока нет

- Logic CircuitsДокумент2 страницыLogic CircuitsRaman yadavОценок пока нет

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeДокумент2 страницыQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarОценок пока нет

- Epc Questions - Cs8351 Digital Principles and System DesignДокумент2 страницыEpc Questions - Cs8351 Digital Principles and System DesignaltaОценок пока нет

- Digital Logic Design Exam Questions and AnswersДокумент38 страницDigital Logic Design Exam Questions and AnswersRajesh ViswanadhamОценок пока нет

- 08AB303 - DIGITAL LOGIC CIRCUITSДокумент3 страницы08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyОценок пока нет

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsОт EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsРейтинг: 5 из 5 звезд5/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxОт EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxРейтинг: 4 из 5 звезд4/5 (2)

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesОт EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesРейтинг: 1.5 из 5 звезд1.5/5 (2)

- 16 17Документ1 страница16 17jayarami reddy pОценок пока нет

- Dr. K.V. Subba Reddy Institute of Technology: Electronics & Communication EngineeringДокумент1 страницаDr. K.V. Subba Reddy Institute of Technology: Electronics & Communication Engineeringjayarami reddy pОценок пока нет

- DLD - PDF 1Документ7 страницDLD - PDF 1karkambadiОценок пока нет

- 1.M.Tech - ECE-Digital Electronics and Communication Systems (DECS) R17 Course Structure & SyllabiДокумент38 страниц1.M.Tech - ECE-Digital Electronics and Communication Systems (DECS) R17 Course Structure & Syllabijayarami reddy pОценок пока нет

- Wireless USBДокумент18 страницWireless USBgluciferОценок пока нет

- MathДокумент76 страницMathJHOEMEL TANGOОценок пока нет

- Sapl Only: High Performance Green Mode PWM ControllerДокумент20 страницSapl Only: High Performance Green Mode PWM ControllerIvan ZuñigaОценок пока нет

- Metal DetectorДокумент3 страницыMetal DetectorRoberto Managay Benitez Jr.67% (3)

- Managing High Voltage Lithium-Ion Batteries in HEVs - M Kultgen - EDN 2009Документ8 страницManaging High Voltage Lithium-Ion Batteries in HEVs - M Kultgen - EDN 2009rogererfredererОценок пока нет

- Parallel Timer InterfaceДокумент13 страницParallel Timer InterfaceRiham AbdallahОценок пока нет

- TV Video Symptoms Terms TroubleshootingДокумент2 страницыTV Video Symptoms Terms Troubleshootingrosnie22Оценок пока нет

- EM Waves and Guide Structure Chapter 3 & 4 worksheet solutionsДокумент5 страницEM Waves and Guide Structure Chapter 3 & 4 worksheet solutionsAbrham GojjamОценок пока нет

- Technical Information Date: 02/2011Документ12 страницTechnical Information Date: 02/2011Satya0% (1)

- HTS Systeme - RPT600 English ManualДокумент4 страницыHTS Systeme - RPT600 English ManualDolfin ChefОценок пока нет

- Iron Inox Provapor ©Документ6 страницIron Inox Provapor ©pukymottoОценок пока нет

- Led ControlДокумент43 страницыLed ControlJunior GodoiОценок пока нет

- F21 - F24 Manual 4aДокумент48 страницF21 - F24 Manual 4alukasОценок пока нет

- Complete Guide to Circle2's Sound Design FeaturesДокумент91 страницаComplete Guide to Circle2's Sound Design FeaturesJuanОценок пока нет

- DatasheetДокумент7 страницDatasheetMonica XiomaraОценок пока нет

- General Features: High-Voltage High-Current Source Driver ArrayДокумент4 страницыGeneral Features: High-Voltage High-Current Source Driver ArrayvideoОценок пока нет

- Thunderbolt IgnitionДокумент18 страницThunderbolt IgnitionChristoffer ChristiansenОценок пока нет

- Control Technique For Single Phase Inverter Photovoltaic Syst - 2020 - Energy ReДокумент9 страницControl Technique For Single Phase Inverter Photovoltaic Syst - 2020 - Energy ReИлия ГеоргиевОценок пока нет

- Data Sheet PDFДокумент344 страницыData Sheet PDFangie. bcfcОценок пока нет

- UPS Inverter Battery AVR LogДокумент8 страницUPS Inverter Battery AVR LogDAltОценок пока нет

- Dip Ups ProjДокумент37 страницDip Ups ProjGIRISH KUMAR AlikkalОценок пока нет

- Polytron 5000 Series Ifu 9033825 Deen 1Документ130 страницPolytron 5000 Series Ifu 9033825 Deen 1SANTIAGO ZUÑIGA TRELLESОценок пока нет

- Cambridge IGCSE: PHYSICS 0625/32Документ16 страницCambridge IGCSE: PHYSICS 0625/32Hriday KadamОценок пока нет

- GME TAR Book Comp WiseДокумент117 страницGME TAR Book Comp WiseOm Prakash RajОценок пока нет

- TLW Question PaperДокумент2 страницыTLW Question PaperHemalatha SanthanamОценок пока нет

- VoLTE One Pager MoS DriveBasedДокумент1 страницаVoLTE One Pager MoS DriveBasedJITU_VISHОценок пока нет

- Understanding The CBEMA CurveДокумент6 страницUnderstanding The CBEMA CurveJesús Valdez RОценок пока нет

- Level Sensors: Product CharacteristicsДокумент3 страницыLevel Sensors: Product CharacteristicsfadhlidzilОценок пока нет

- Cable Arrangement For Reduced Magnetic FieldДокумент5 страницCable Arrangement For Reduced Magnetic FieldzwerrОценок пока нет

- Ba BT300 DLT1201 enДокумент212 страницBa BT300 DLT1201 enKan ChoraОценок пока нет