Академический Документы

Профессиональный Документы

Культура Документы

Digital Systems Design Using Verilog: Charles Roth, Lizy Kurian John, Byeong Kil Lee

Загружено:

Brayan Espinoza Garcia0%(1)0% нашли этот документ полезным (1 голос)

972 просмотров2 страницыThis document provides a list of errata for the first printing of the book "Digital Systems Design Using Verilog" by Charles Roth, Lizy Kurian John, and Byeong Kil Lee. It contains over 50 corrections to page numbers, equations, code examples, figures, tables, and problem descriptions within the book. The errata cover mistakes in syntax, numbering, labeling, and textual descriptions.

Исходное описание:

libro de 1.ásd

Оригинальное название

1285051076_490966

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThis document provides a list of errata for the first printing of the book "Digital Systems Design Using Verilog" by Charles Roth, Lizy Kurian John, and Byeong Kil Lee. It contains over 50 corrections to page numbers, equations, code examples, figures, tables, and problem descriptions within the book. The errata cover mistakes in syntax, numbering, labeling, and textual descriptions.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0%(1)0% нашли этот документ полезным (1 голос)

972 просмотров2 страницыDigital Systems Design Using Verilog: Charles Roth, Lizy Kurian John, Byeong Kil Lee

Загружено:

Brayan Espinoza GarciaThis document provides a list of errata for the first printing of the book "Digital Systems Design Using Verilog" by Charles Roth, Lizy Kurian John, and Byeong Kil Lee. It contains over 50 corrections to page numbers, equations, code examples, figures, tables, and problem descriptions within the book. The errata cover mistakes in syntax, numbering, labeling, and textual descriptions.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

Digital Systems Design Using Verilog

Charles Roth, Lizy Kurian John, Byeong Kil Lee

1st Edition

978-1-285-05107-9

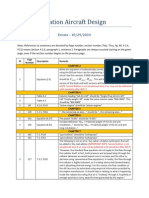

Errata for First Printing

Page Number Correction Description

20 In the bottom-right example, “0010” should be “0011”

37 In Equation (1-38), the “+” between “fmax” and “1” should be “=”

39 For Question (a) of the example, “minimum clock period” should be “maximum clock frequency”

46 At the bottom of the page, “The last waveform in Figure 1-45 illustrates” should be “The last

waveform in Figure 1-52 illustrates”

70 In the middle of the page, the second logic equation should be “Cout = XY + YCin + XCin”

80 On line 16, “{“ should be inserted so that it reads { else if (condition)

82 8 lines from the bottom, “@” should be “wait” so that it reads

wait(posedge CLK);

86 In line 7, add “//” before “will be”

103 In line 4 of Section 2.13.2, “Sel” should be “(Sel)”

103 In the last line of the page, remove semicolon

126 In line 9, “reg [7:0]” should be removed

138 For Problem 2.14, the last line of code should be “B <= B + 7;”

154 For Problem 2.56, “=” should be “<=” for the following instances:

sel <= 0;

sel <= sel + 1;

sel <= sel + 2;

F <= I0;

F <= I1;

F <= I2;

F <= I3;

167 In Equation (3-1), “ A’B’+AC ” should be “ A’B’ + AC’ ”

203 In line 4, “[TomaHawk reference]” should be “[34]”

225 In line 9 of Section 4.5, the em-dash between “1” and “0” should be replaced by two normal dashes

so that it reads “1- -0/0110”

319 In the caption for TABLE 5-3, remove “b” after “Figure 5-29”

319 In the second-to-last line, “muliplexer” should be “multiplexer”

326 In the second paragraph, the line “The two-address microcode entry is based on Table 5-7, and the

single-address microcode entry is based on Table 5-6.” should be “The two-address microcode entry

is based on Table 5-6, and the single-address microcode entry is based on Table 5-7.”

335 In the table at the top of the page, the second “X1” should be “X2” and the third “X1” should be “X3”

355 The paragraph under “The Xilinx Kintex Configurable Logic Block” should read:

“The Xilinx Kintex FPGA uses four copies of the basic block shown in Figure 6-13 to form a slice. Two

such slices are combined to form a Configurable Logic Block (CLB). Each slice thus contains four six-

input Look Up Tables (LUT6), 8 flip-flops, the carry chain, and several multiplexers.”

355 The paragraph under Figure 6-13 should read:

“Each LUT6 can be used to generate one 6-variable function or two 5-variable functions. The 6-

variable function is generated by combining two 5-variable functions using a 2-to-1 multiplexer.

There are 2 outputs from the LUT6, namely O6 and O5. One of the outputs (O6) can use up to 6 input

variables. The second output (O5) can use only up to 5 input variables. It should be noted that these

are not independent variables or independent functions. Five of the variables are common between

O6 and O5 and the function O5 has to be a sub-function of the function O6. There are 3 external

outputs from the slice, AMUX, A and AQ, but only two of them can be used simultaneously. One of

the outputs, A is a combinational output, while the AQ output is always a registered output. The

AMUX output can be either combinational or registered. The O6 function can be brought out

through any of the 3 output lines, however, the O5 output can be brought out only via AMUX and

AQ. There are several multiplexers and other gates to allow this routing. The slices also support carry

chaining. The Kintex chips use two slight variations of this slice structure, which they call SLICEL and

SLICEM.”

377 In the third line after “Synthesis of a Case Statement”, “inputs a and b are each implemented with 2-

bit binary numbers.” should be “input a and output b are 2-bit binary numbers.”

384 In the top left block of Figure 6-31b, “4-Bit Counter” should be “4-Bit Adder” The second instance

should remain as is

385 In the “Major Vendors of FPGA CAD Tools” box, “XIlinx” should be “Xilinx”

419 In Figure 7-12, the No path from Step 7 of the flowchart should go back to Step 4 instead of Step 2

433 In Figure 8-2, the “end” after “cin = cout;” should be aligned with the “begin” three lines above it

441 In the first line following Figure 8-9, “The first 12” should be “The first 14”

462 In the middle of the page, “Figure 8-22 shows a Verilog code that read a file” should be “Figure 8-22

shows Verilog code that reads a file”

483 In the second row and last column of Table 9-7, “$s3” should be “$3”

483 In the second row and first column of Table 9-7, “Add” should be “add”

483 In the third row and first column of Table 9-7, “Sub” should be “sub”

490 Three lines from the bottom, “R-format” should be “I-format”

490 Two lines from the bottom, “I-format” should be “R-format”

495 In Figure 9-7, Line 8 should be deleted:

reg[6:0] counter; should be deleted.

495 In Figure 9-7, “//” should be added to Line 14 so it reads:

//$readmemh(“MIPS_Instructions.txt”, RAM):

503 14 lines from the bottom, “$16” should be “16”

508 In Problem 9.1, delete “Pentium 4 ->” and “Pentium 3 ->”

521 In line 5, “S5” should be “S2”

553 In the middle of the page, “LSFR” should be “LFSR”

555 For (e) case expression, remove the semicolon after “endcase”

Вам также может понравиться

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DОт EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DОценок пока нет

- Errata For "Principles of Distributed Database System" 2nd EditionДокумент7 страницErrata For "Principles of Distributed Database System" 2nd EditionmatiasaitamОценок пока нет

- Field Programmable Gate Array: Full Adder Implementation Using FPGAДокумент32 страницыField Programmable Gate Array: Full Adder Implementation Using FPGAshabi0904Оценок пока нет

- Errata For Digital Control of Dynamic Systems, 3rd EditionДокумент1 страницаErrata For Digital Control of Dynamic Systems, 3rd EditionFad SaelioОценок пока нет

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxОт EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxРейтинг: 4 из 5 звезд4/5 (1)

- Errata List For Algorithm Manual SkienaДокумент13 страницErrata List For Algorithm Manual Skienacoolvar90Оценок пока нет

- PRODUCTION: Planning, Control and Integration: Sipper & Bulfin Errata SheetДокумент3 страницыPRODUCTION: Planning, Control and Integration: Sipper & Bulfin Errata SheetJorge Luis FloresОценок пока нет

- Learn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.От EverandLearn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.Оценок пока нет

- Cisco CCNA Exam #640-607 Certification Guide, 3 - EditionДокумент6 страницCisco CCNA Exam #640-607 Certification Guide, 3 - EditionKRONERKRONERОценок пока нет

- 5th Edition Errata - US - First PrintingДокумент2 страницы5th Edition Errata - US - First PrintingInfo EsocketОценок пока нет

- Sample CSE370 Final Exam Questions: Logic MinimizationДокумент8 страницSample CSE370 Final Exam Questions: Logic MinimizationQaseem HussainОценок пока нет

- Revision For The Final-1Документ7 страницRevision For The Final-1Shady MagedОценок пока нет

- 2007 Anna University B.E Electrical and Electronics Digital Systems Question PaperДокумент3 страницы2007 Anna University B.E Electrical and Electronics Digital Systems Question PapernarencharuОценок пока нет

- CCNA 200 301 Vol1 Errata 2020 05 12Документ2 страницыCCNA 200 301 Vol1 Errata 2020 05 12Vishal VermaОценок пока нет

- Consider The Following Multi-Level Boolean Expression Y (A.B.C) + (A + D') - (A' + C')Документ1 страницаConsider The Following Multi-Level Boolean Expression Y (A.B.C) + (A + D') - (A' + C')manihatnОценок пока нет

- I. 7-Segment Display: Elektronski Fakultet Katedra Za MikroelektronikuДокумент39 страницI. 7-Segment Display: Elektronski Fakultet Katedra Za MikroelektronikuMaki MakicОценок пока нет

- Introduction To C++ Programming: First Printing Errata (December 20, 2006)Документ3 страницыIntroduction To C++ Programming: First Printing Errata (December 20, 2006)doanson44Оценок пока нет

- BOOK ERRORS - Engineering Vibrations 3E InmanДокумент4 страницыBOOK ERRORS - Engineering Vibrations 3E InmanmetaenderОценок пока нет

- CCNA 200-301 Official Cert Guide, Volume 1: ISBN-10: 0-13-579273-8 ISBN-13: 978-0-13-579273-5Документ2 страницыCCNA 200-301 Official Cert Guide, Volume 1: ISBN-10: 0-13-579273-8 ISBN-13: 978-0-13-579273-5Monu ChouhanОценок пока нет

- Errata To January 4, 2010: Air-Conditioning System Design Manual, 2nd EditionДокумент2 страницыErrata To January 4, 2010: Air-Conditioning System Design Manual, 2nd EditionNeal JohnsonОценок пока нет

- An Introduction To Formal Languages and Automata - Third Edition (Peter Linz) Mamad - Solution-ManualДокумент6 страницAn Introduction To Formal Languages and Automata - Third Edition (Peter Linz) Mamad - Solution-Manualmamad233233% (3)

- Chapter 6 LogicДокумент49 страницChapter 6 LogicProspect Teaches MathematicsОценок пока нет

- Class 12Документ5 страницClass 12kishlaysinha5Оценок пока нет

- Errata, Volume 1 and 2Документ2 страницыErrata, Volume 1 and 2borjageОценок пока нет

- CE802: Advance Computer ArchitectureДокумент3 страницыCE802: Advance Computer Architecturepavan_25Оценок пока нет

- Digital Communications Proakis 4th Ed ErrataДокумент8 страницDigital Communications Proakis 4th Ed ErrataavivroОценок пока нет

- 11 Usp Computer Science 05 PDFДокумент4 страницы11 Usp Computer Science 05 PDFVikas SaxenaОценок пока нет

- CS XII PB2 Silchar QPДокумент10 страницCS XII PB2 Silchar QPklaus MikaelsonОценок пока нет

- Fundamentals of Computer Design Errata 1Документ28 страницFundamentals of Computer Design Errata 1Khalid SaifОценок пока нет

- Corrections and Minor Revisions of Mathematical Methods in The Physical Sciences, Third Edition, by Mary L. Boas (Deceased)Документ6 страницCorrections and Minor Revisions of Mathematical Methods in The Physical Sciences, Third Edition, by Mary L. Boas (Deceased)Era BudiОценок пока нет

- Logic GateДокумент12 страницLogic Gateapi-254068557Оценок пока нет

- CA07Документ7 страницCA07Yu Onn ChuaОценок пока нет

- ERRATA Rabaey, Chandrakasan - Digital Integrated CircuitsДокумент4 страницыERRATA Rabaey, Chandrakasan - Digital Integrated CircuitsbeppesОценок пока нет

- Electronic Assignment QuestionsДокумент6 страницElectronic Assignment QuestionsCalculus Chong Wei ChoonОценок пока нет

- S07 273 Lab6Документ7 страницS07 273 Lab6Carlos V.Оценок пока нет

- ErrataДокумент40 страницErrataabul_1234Оценок пока нет

- Griffiths Errata.. Introduction To Quantum Mechanics, 1st Ed. (2000) 1995Документ3 страницыGriffiths Errata.. Introduction To Quantum Mechanics, 1st Ed. (2000) 1995rafael_pazin5105Оценок пока нет

- General Aviation AC Design - Errata 10-29-2014Документ3 страницыGeneral Aviation AC Design - Errata 10-29-2014snorrigОценок пока нет

- Cs 60Документ80 страницCs 60Sirsendu RoyОценок пока нет

- Encs211 Experiment 3Документ17 страницEncs211 Experiment 3Prince IshtaОценок пока нет

- CSA Test PaperДокумент65 страницCSA Test Paperhimanshumis2022Оценок пока нет

- Matlab CourseДокумент114 страницMatlab CourseGeorge IskanderОценок пока нет

- Financial Analytics With R Errata Sheet: Mark J. Bennett and Dirk L. Hugen July 11, 2019Документ6 страницFinancial Analytics With R Errata Sheet: Mark J. Bennett and Dirk L. Hugen July 11, 2019BОценок пока нет

- EG2061 Electronics and ControlДокумент9 страницEG2061 Electronics and ControlTudor Octavian RusuОценок пока нет

- Department of EceДокумент8 страницDepartment of Ecerajendr_46Оценок пока нет

- Embedded Networking With Can and Canopen: 1St Edition ErrataДокумент2 страницыEmbedded Networking With Can and Canopen: 1St Edition ErrataCharbel SemaanОценок пока нет

- Dica Question BankДокумент4 страницыDica Question BankOmprakash KuswahaОценок пока нет

- 2011 12 Lyp Computer Science 01Документ91 страница2011 12 Lyp Computer Science 01Dhirendra SinghОценок пока нет

- Text Errata v4-2.1Документ3 страницыText Errata v4-2.1ammar369Оценок пока нет

- Loki 97Документ22 страницыLoki 97Diego Durán100% (1)

- Ya Y Ya Y2 Ya Y A Y2: Common Data For Questions 3 & 4Документ19 страницYa Y Ya Y2 Ya Y A Y2: Common Data For Questions 3 & 4Rahul RoyОценок пока нет

- Working With Combinational Logic: SimplificationДокумент24 страницыWorking With Combinational Logic: SimplificationMain RizwanОценок пока нет

- Lab 1Документ8 страницLab 1Leo AzОценок пока нет

- Final Apr 03 SolnsДокумент16 страницFinal Apr 03 Solnsapi-3755462Оценок пока нет

- EE6301 QB FinalДокумент21 страницаEE6301 QB FinallithijanarОценок пока нет

- Appendix B: Analysis of Ipv6 PacketsДокумент10 страницAppendix B: Analysis of Ipv6 PacketsCarlos Andres Pulgarin GomezОценок пока нет

- Schematic Sony St26iДокумент3 страницыSchematic Sony St26iNiceMen SafaniОценок пока нет

- TS431/431A/431B: Adjustable Precision Shunt RegulatorДокумент8 страницTS431/431A/431B: Adjustable Precision Shunt RegulatordarioОценок пока нет

- IEC 391-1972 - InactivaДокумент14 страницIEC 391-1972 - InactivaCristian SnchezОценок пока нет

- Stp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageДокумент12 страницStp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageOsmir MonteiroОценок пока нет

- 1.1K - 3.3KTL-G3 User Manual20210519Документ72 страницы1.1K - 3.3KTL-G3 User Manual20210519Maureu Jefferson BenvenhoОценок пока нет

- ELE001 - Basic Electricity and ElectronicsДокумент4 страницыELE001 - Basic Electricity and ElectronicsHarold LuceroОценок пока нет

- Chapter 5 Energy Storage ElementsДокумент11 страницChapter 5 Energy Storage ElementsAkmal Hakim Bin IdrisОценок пока нет

- Hitronic TIG 300A DC Inverter Welding Machine - Goldpeak Tools PH PDFДокумент5 страницHitronic TIG 300A DC Inverter Welding Machine - Goldpeak Tools PH PDFRodney LanagОценок пока нет

- Time Borring and Clock SkewДокумент18 страницTime Borring and Clock SkewNitin Suyan PanchalОценок пока нет

- A1100 Servo Drives: Installation GuideДокумент23 страницыA1100 Servo Drives: Installation GuideasdlksadasfОценок пока нет

- B Power-Supplies 05-21 enДокумент28 страницB Power-Supplies 05-21 entv1603Оценок пока нет

- Instruction Manual MPU Analog Output 4-20 MaДокумент20 страницInstruction Manual MPU Analog Output 4-20 MaSIDHANT JOSHIОценок пока нет

- h1 Styleclearboth Idcontentsection0the Only Guide To Commercial Fisheries Reviewh1jbfch PDFДокумент14 страницh1 Styleclearboth Idcontentsection0the Only Guide To Commercial Fisheries Reviewh1jbfch PDFgalleymark22Оценок пока нет

- Power Transformers and ReactorsДокумент49 страницPower Transformers and ReactorsroyclhorОценок пока нет

- Sony KD AF8 Service Manual Common, Chassis GN4TRДокумент92 страницыSony KD AF8 Service Manual Common, Chassis GN4TRJohnОценок пока нет

- Gen Elcs - 1. Bridge Rectifier and Zener Regulated Power SupplyДокумент6 страницGen Elcs - 1. Bridge Rectifier and Zener Regulated Power SupplyPrasanthОценок пока нет

- Build Your Own Butler RobotДокумент45 страницBuild Your Own Butler RobotWeb devОценок пока нет

- Metering All Your Needs: BEC44 RangeДокумент2 страницыMetering All Your Needs: BEC44 RangeAntónio BarrosОценок пока нет

- Alarm 4 N 1Документ2 страницыAlarm 4 N 1Chairuddin SaidОценок пока нет

- Acs 800Документ208 страницAcs 800Юрий НасретдиновОценок пока нет

- FT-7900R-TCB-FCC Id-K6620165x40Документ1 страницаFT-7900R-TCB-FCC Id-K6620165x40Leandro MarconОценок пока нет

- Studio Sound 1986 03 OCR Page 0049Документ1 страницаStudio Sound 1986 03 OCR Page 0049MANUEL ENRIQUE HOYOS ANAYAОценок пока нет

- PowerSeries Neo HSM2108 Spec Sheets LT enДокумент3 страницыPowerSeries Neo HSM2108 Spec Sheets LT enHalin ReyesОценок пока нет

- Battery Status Check and Charging Manual MethodДокумент1 страницаBattery Status Check and Charging Manual MethodS KumarОценок пока нет

- V01 - Waves On Transmission LinesДокумент16 страницV01 - Waves On Transmission LinesNabil DakhliОценок пока нет

- Manual Alstom S2DAДокумент50 страницManual Alstom S2DABagla100% (2)

- Accelerometer Test FixtureДокумент7 страницAccelerometer Test FixtureMitchОценок пока нет

- Drive Mode System: SectionДокумент19 страницDrive Mode System: SectionАндрей НадточийОценок пока нет

- LV762XXДокумент6 страницLV762XXRaulОценок пока нет

- Low Power Instrument Transformers For Smart Grids and PLC CouplersДокумент4 страницыLow Power Instrument Transformers For Smart Grids and PLC CouplersAntonio Solis MurilloОценок пока нет