Академический Документы

Профессиональный Документы

Культура Документы

Dec 2005

Загружено:

sandeepaprАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Dec 2005

Загружено:

sandeepaprАвторское право:

Доступные форматы

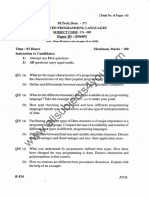

Computer Architecture

(CS-201, Dec 2005)

Time: 3 Hrs Max Marks: 60

Note: Section A is compulsory. Attempt five questions from Section B & C, taking at least two

questions from each section.

Section-A

1. (a) Convert the following logic function into minterm.

ABC`DE` + AB`C`DE` +ABCDE` + AB`CD`E`

(b) Define the terms real time computer and process control computer.

(c) Give the layered view of a computer system.

(d) What is the role of shift Registers in digital computers?

(e) Perform the subtraction with the following unsigned binary number by taking the 2’s

compliment of the subtrahend.

1010100 – 1010100

(f) Explain the meaning of the memory-reference instruction STA.

(g) What is the difference between micro program and micro code?

(h) What do you mean by software interrupt?

(i) How Cache Memory is useful in memory hierarchy?

(j) What do you mean by Iterrupt – initiated I/O Concept?

Section-B

2. Explain in brief about MIMD machines.

3. Give an overview of CISC Architecture.

4. A Computer employs RAM chips of 256 X 8 and ROM chips of 1024 X 8. The computer

system needs 2K bytes of RAM, 4K bytes of ROM, and four interface units, each with

four registers. A memory-mapped I/O configuration is used. The two highest-order bits

of the address bus are assigned 00 for RAM, 01 for ROM, and 10 for interface registers.

Give the address range in hexadecimal for RAM, ROM and interface.

5. A DMA controller transfers 16-bit words to memory using cycle stealing. The words are

assembled from a device that transmits characters at a rate of 2400 characters per

second. The CPU is fetching the executing instructions at an average rate of 1 million

instructions per second. By how much will the CPU be slowed down because of the DMA

transfer?

6. Discuss the hardware implementation of division for signed-magnitude data.

Section-C

7. Explain in detail the main features of at least two performance evaluation benchmarks.

8. (a) Explain why poor load balancing leads to less than-linear speed up?

(b) A given processor has 32 registers, uses 16-bit immediates, and has 142

instructions in its ISA. In a given program, 20% of the instructions take one input

register and have one output register, 30% have two input registers and one output

register, 25% have one output and one input register and take an immediate input as

well, and the remaining 25% have one immediate input register. For each of the four

types of instructions, how many bits are required? Assume that the ISA requires that all

instructions be a multiple of 8 bits in length.

9. (a) How does pipelining improve performance?

(b) What is the result of the following operations when executed on a 8-bit processor

that uses a 2’s complement representation for negative integers?

LSH 14, 3

ASH 17, 5

LSH-23, -2

ASH-23, -2

Вам также может понравиться

- MCQ1 C++Документ12 страницMCQ1 C++sandeepaprОценок пока нет

- Design Considerations: Applications Impacts of Delay and LossДокумент8 страницDesign Considerations: Applications Impacts of Delay and LosssandeepaprОценок пока нет

- ATM-Based Protocol Interworking and Public Service OfferingДокумент8 страницATM-Based Protocol Interworking and Public Service OfferingsandeepaprОценок пока нет

- Java MCQs 1Документ39 страницJava MCQs 1sandeepaprОценок пока нет

- Java MCQ 3Документ14 страницJava MCQ 3sandeepaprОценок пока нет

- Chapter 11 Object-Oriented DesignДокумент47 страницChapter 11 Object-Oriented DesignsandeepaprОценок пока нет

- 2D TransformationsДокумент14 страниц2D TransformationssandeepaprОценок пока нет

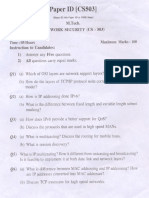

- M.Tech.: Advanced Programming Languages Subject Code:CsДокумент2 страницыM.Tech.: Advanced Programming Languages Subject Code:CssandeepaprОценок пока нет

- Paper ID (CSS09) : M. TechДокумент2 страницыPaper ID (CSS09) : M. TechsandeepaprОценок пока нет

- Advantages of Batch SystemsДокумент4 страницыAdvantages of Batch SystemssandeepaprОценок пока нет

- Punjab Technical University: Computer ArchitectureДокумент2 страницыPunjab Technical University: Computer ArchitecturesandeepaprОценок пока нет

- Assembly Language ProgrammingДокумент85 страницAssembly Language ProgrammingsandeepaprОценок пока нет

- Traffic ManagementДокумент10 страницTraffic ManagementsandeepaprОценок пока нет

- Cs 503 PDFДокумент1 страницаCs 503 PDFsandeepaprОценок пока нет

- Note: Please Fill Subject Code and Paper ID On OMRДокумент2 страницыNote: Please Fill Subject Code and Paper ID On OMRsandeepaprОценок пока нет

- Paper Id: (A0451) : B. Tech. (Sem. - 3'O) Computerarchitecture Subjeci Code: Cs - 201 R) Nrvl'Atlsubi Ctsa'Tr':L I'RnДокумент2 страницыPaper Id: (A0451) : B. Tech. (Sem. - 3'O) Computerarchitecture Subjeci Code: Cs - 201 R) Nrvl'Atlsubi Ctsa'Tr':L I'RnsandeepaprОценок пока нет

- Computer Architecture (CSE-201, Dec-07) Section-AДокумент1 страницаComputer Architecture (CSE-201, Dec-07) Section-AsandeepaprОценок пока нет

- M.Tech. (Sem. - 1") ' Advancbd Programming Languagbs Sub - Ibct CODE: CS - 509 Paper ID: (E0689)Документ2 страницыM.Tech. (Sem. - 1") ' Advancbd Programming Languagbs Sub - Ibct CODE: CS - 509 Paper ID: (E0689)sandeepaprОценок пока нет

- Dec 2009Документ2 страницыDec 2009sandeepaprОценок пока нет

- Punjab Technical University: B.Tech. (Sem. - 3) Computer ArchitectureДокумент2 страницыPunjab Technical University: B.Tech. (Sem. - 3) Computer ArchitecturesandeepaprОценок пока нет

- Hours L) 2) 3) : Li HmoДокумент2 страницыHours L) 2) 3) : Li HmosandeepaprОценок пока нет

- Dec 2008Документ2 страницыDec 2008sandeepaprОценок пока нет

- Question Paper PDFДокумент2 страницыQuestion Paper PDFsandeepaprОценок пока нет

- Paper Id (Css03) : .' /T. ' ('1. /) Q M. Tech. (Sed1Документ2 страницыPaper Id (Css03) : .' /T. ' ('1. /) Q M. Tech. (Sed1sandeepaprОценок пока нет

- Computer Architecture: Roll No. Total No. of Pages: 02 Total No. of Questions: 09Документ2 страницыComputer Architecture: Roll No. Total No. of Pages: 02 Total No. of Questions: 09sandeepaprОценок пока нет

- Paper ID (CS503) : (Please Fill This Paper ID in OMR Sheet)Документ2 страницыPaper ID (CS503) : (Please Fill This Paper ID in OMR Sheet)sandeepaprОценок пока нет

- Papei-U) : Ur0402L: Reseaii Cfi Meti (Odology Sijb - Iect Qqde: Mntre - 5$2Документ2 страницыPapei-U) : Ur0402L: Reseaii Cfi Meti (Odology Sijb - Iect Qqde: Mntre - 5$2sandeepaprОценок пока нет

- Questions of Network SecurityДокумент2 страницыQuestions of Network SecuritysandeepaprОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- RFoF Link Design GuidelineДокумент12 страницRFoF Link Design GuidelineSantosh KumarОценок пока нет

- Printed Circuit BoardДокумент6 страницPrinted Circuit BoardSayan Das KarmakarОценок пока нет

- KRK Rokit 8 ManualДокумент20 страницKRK Rokit 8 ManualRussell HodgesОценок пока нет

- Network Infrastructure ConceptsДокумент130 страницNetwork Infrastructure ConceptsEthan BooisОценок пока нет

- Group Presentation Digital Communication SystemsДокумент29 страницGroup Presentation Digital Communication SystemsShawn MoyoОценок пока нет

- Kuliah 2 Properties of Transmission SystemsДокумент69 страницKuliah 2 Properties of Transmission SystemsMuhammad Fikri Hidayat FikriОценок пока нет

- EQP 8 Channel Analog Input Module InstructionsДокумент143 страницыEQP 8 Channel Analog Input Module InstructionsJosë RodríguezОценок пока нет

- Hydranm2 Gea 12934a HRДокумент2 страницыHydranm2 Gea 12934a HRMarcus SiaОценок пока нет

- Group 4 Connectors: 1. Connector DestinationДокумент17 страницGroup 4 Connectors: 1. Connector DestinationRafał DworakОценок пока нет

- Temp Project Report PIDДокумент46 страницTemp Project Report PIDJahangeer BukhariОценок пока нет

- LTE Optimization and TroubleshootingДокумент200 страницLTE Optimization and TroubleshootingardianОценок пока нет

- Lecture Notes 1 MOBILE NETWORKS 1 NOWДокумент13 страницLecture Notes 1 MOBILE NETWORKS 1 NOWNorris Nana ChinjongОценок пока нет

- Integrity™ V500 User's ManualДокумент281 страницаIntegrity™ V500 User's ManualRicardo CamargosОценок пока нет

- Ea-679798 001 0000Документ1 страницаEa-679798 001 0000engrabbas75Оценок пока нет

- PCB DiagramДокумент4 страницыPCB Diagramvee8power100% (1)

- 60-03 EFD20 enДокумент102 страницы60-03 EFD20 enIonut RacaruОценок пока нет

- Domae ELCB - DOMR01240Документ3 страницыDomae ELCB - DOMR01240ditlantas ditlantasОценок пока нет

- DSP Filter BankДокумент6 страницDSP Filter BankTabish AliОценок пока нет

- Powerflex 700h PDFДокумент120 страницPowerflex 700h PDFEvandro PavesiОценок пока нет

- 02A Lesson Proper For Week 7Документ9 страниц02A Lesson Proper For Week 7Maxela CastroОценок пока нет

- Cat 6a Futp Patch CordsДокумент2 страницыCat 6a Futp Patch CordsMANUEL CASTROОценок пока нет

- Ground Radio and Telluric CurrentsДокумент18 страницGround Radio and Telluric CurrentsfghjhgfОценок пока нет

- HD 450SE Manual ENДокумент36 страницHD 450SE Manual ENJoyОценок пока нет

- CMP Catalogue 2014Документ44 страницыCMP Catalogue 2014Joseph TingОценок пока нет

- Katalog 120212Документ8 страницKatalog 120212Agus ZulhendriОценок пока нет

- Nokia BSC 3i For Sale From Used Telecoms: Telephone: +44 1273 391 291Документ4 страницыNokia BSC 3i For Sale From Used Telecoms: Telephone: +44 1273 391 291Jinzhe WangОценок пока нет

- HEF4521B: 1. General DescriptionДокумент17 страницHEF4521B: 1. General DescriptionpaulpuscasuОценок пока нет

- Product Parameter: Details PDFДокумент1 страницаProduct Parameter: Details PDFAndrés Atlético Nacional BustamanteОценок пока нет

- Automatic Voltage Regulation AimДокумент5 страницAutomatic Voltage Regulation AimFazle RabbiОценок пока нет

- 5G Trial Offer Viettel 2019 - Scope - v1.0 - VTДокумент9 страниц5G Trial Offer Viettel 2019 - Scope - v1.0 - VTQuốc DũngОценок пока нет