Академический Документы

Профессиональный Документы

Культура Документы

4922 12-Bit DAC With SPI Interface - 21897b

Загружено:

le kietАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

4922 12-Bit DAC With SPI Interface - 21897b

Загружено:

le kietАвторское право:

Доступные форматы

MCP4921/4922

12-Bit DAC with SPI™ Interface

Features Description

• 12-Bit Resolution The Microchip Technology Inc. MCP492X are 2.7 –

• ±0.2 LSB DNL (typ) 5.5V, low-power, low DNL, 12-Bit Digital-to-Analog Con-

• ±2 LSB INL (typ) verters (DACs) with optional 2x buffered output and SPI

interface.

• Single or Dual Channel

The MCP492X are DACs that provide high accuracy

• Rail-to-Rail Output

and low noise performance for industrial applications

• SPI™ Interface with 20 MHz Clock Support where calibration or compensation of signals (such as

• Simultaneous Latching of the Dual DACs w/LDAC temperature, pressure and humidity) are required.

• Fast Settling Time of 4.5 µs The MCP492X are available in the extended tempera-

• Selectable Unity or 2x Gain Output ture range and PDIP, SOIC, MSOP and TSSOP

• 450 kHz Multiplier Mode packages.

• External VREF Input The MCP492X devices utilize a resistive string archi-

tecture, with its inherent advantages of low DNL error,

• 2.7V to 5.5V Single-Supply Operation

low ratio metric temperature coefficient and fast settling

• Extended Temperature Range: -40°C to +125°C time. These devices are specified over the extended

Applications temperature range. The MCP492X include double-

buffered inputs, allowing simultaneous updates using

• Set Point or Offset Trimming the LDAC pin. These devices also incorporate a

• Sensor Calibration Power-On Reset (POR) circuit to ensure reliable

• Digitally-Controlled Multiplier/Divider power-up.

• Portable Instrumentation (Battery-Powered) Package Types

• Motor Feedback Loop Control

8-Pin PDIP, SOIC, MSOP

Block Diagram

VDD 1 8 VOUTA

MCP4921

CS SDI SCK LDAC

CS 2 7 AVSS

SCK 3 6 VREFA

VDD

Interface Logic Power-on SDI 4 5 LDAC

Reset

AVSS

Input Input 14-Pin PDIP, SOIC, TSSOP

Register A Register B

VDD 1 14 V OUTA

DACA DACB NC 2 13 VREFA

MCP4922

Register Register CS 3 12 AVSS

VREF VREF

SCK 4 11 VREFB

A String String B

DACB SDI 5 10 V OUTB

DACA

Buffer NC 6 9 SHDN

Buffer

NC 7 8 LDAC

Gain Gain

Logic Output Logic

Op Amps

Output

Logic

VOUTA VOUTB

SHDN

2007 Microchip Technology Inc. DS21897B-page 1

MCP4921/4922

1.0 ELECTRICAL † Notice: Stresses above those listed under “Maximum Rat-

ings” may cause permanent damage to the device. This is a

CHARACTERISTICS stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

Absolute Maximum Ratings † operational listings of this specification is not implied. Expo-

sure to maximum rating conditions for extended periods may

VDD ............................................................................................................. 6.5V affect device reliability.

All inputs and outputs w.r.t ............. AVSS –0.3V to VDD+0.3V

Current at Input Pins ....................................................±2 mA

Current at Supply Pins ...............................................±50 mA

Current at Output Pins ...............................................±25 mA

Storage temperature .....................................-65°C to +150°C

Ambient temp. with power applied ................-55°C to +125°C

ESD protection on all pins 4 kV (HBM), 400V (MM)

Maximum Junction Temperature (TJ) . .........................+150°C

5V AC/DC CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, VDD = 5V, AVSS = 0V, VREF = 2.048V, output buffer gain (G) = 2x, RL = 5 k

to GND, CL = 100 pF TA = -40 to +85°C. Typical values at +25°C.

Parameters Sym Min Typ Max Units Conditions

Power Requirements

Input Voltage VDD 2.7 — 5.5

Input Current - MCP4921 IDD — 175 350 µA Input unbuffered, digital inputs

Input Current - MCP4922 — 350 700 grounded, output unloaded,

code at 0x000

Hardware Shutdown Current ISHDN — 0.3 2 µA

Software Shutdown Current ISHDN_SW — 3.3 6 µA

Power-on-Reset Threshold VPOR — 2.0 — V

DC Accuracy

Resolution n 12 — — Bits

INL Error INL -12 2 12 LSB

DNL DNL -0.75 ±0.2 +0.75 LSB Device is Monotonic

Offset Error VOS — ±0.02 1 % of FSR Code 0x000h

Offset Error Temperature VOS/°C — 0.16 — ppm/°C -45°C to 25°C

Coefficient — -0.44 — ppm/°C +25°C to 85°C

Gain Error gE — -0.10 1 % of FSR Code 0xFFFh, not including offset

error.

Gain Error Temperature G/°C — -3 — ppm/°C

Coefficient

Input Amplifier (VREF Input)

Input Range - Buffered Mode VREF 0.040 — VDD – 0.040 V Note 1

Input Range - Unbuffered VREF 0 — VDD V Code = 2048

Mode VREF = 0.2v p-p, f = 100 Hz and 1 kHz

Input Impedance RVREF — 165 — k Unbuffered Mode

Input Capacitance - CVREF — 7 — pF

Unbuffered Mode

Multiplier Mode fVREF — 450 — kHz VREF = 2.5V ±0.2Vp-p, Unbuffered,

-3 dB Bandwidth G=1

fVREF — 400 — kHz VREF = 2.5V ±0.2 Vp-p, Unbuffered,

G=2

Multiplier Mode - THDVREF — -73 — dB VREF = 2.5V ±0.2Vp-p,

Total Harmonic Distortion Frequency = 1 kHz

Note 1: By design, not production tested.

2: Too small to quantify.

DS21897B-page 2 2007 Microchip Technology Inc.

MCP4921/4922

5V AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise indicated, VDD = 5V, AVSS = 0V, VREF = 2.048V, output buffer gain (G) = 2x, RL = 5 k

to GND, CL = 100 pF TA = -40 to +85°C. Typical values at +25°C.

Parameters Sym Min Typ Max Units Conditions

Output Amplifier

Output Swing VOUT — 0.010 — Accuracy is better than 1 LSB for

to VDD VOUT = 10 mV to (VDD – 40 mV)

– 0.040

Phase Margin m — 66 — degrees

Slew Rate SR — 0.55 — V/µs

Short Circuit Current ISC — 15 24 mA

Settling Time tsettling — 4.5 — µs Within 1/2 LSB of final value from 1/4

to 3/4 full-scale range

Dynamic Performance

DAC-to-DAC Crosstalk — 10 — nV-s Note 2

Major Code Transition Glitch — 45 — nV-s 1 LSB change around major carry

(0111...1111 to 1000...0000)

Digital Feedthrough — 10 — nV-s Note 2

Analog Crosstalk — 10 — nV-s Note 2

Note 1: By design, not production tested.

2: Too small to quantify.

3V AC/DC CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, VDD = 3V, AVSS = 0V, VREF = 2.048V external, output buffer gain (G) = 1x,

RL = 5 k to GND, CL = 100 pF TA = -40 to +85°C. Typical values at 25°C

Parameters Sym Min Typ Max Units Conditions

Power Requirements

Input Voltage VDD 2.7 — 5.5

Input Current - MCP4921 IDD — 125 250 µA Input unbuffered, digital inputs

Input Current - MCP4922 — 250 500 grounded, output unloaded,

code at 0x000

Hardware Shutdown Current ISHDN — 0.25 2 µA

Software Shutdown Current ISHDN_SW — 2 6 µA

Power-On Reset threshold VPOR — 2.0 — V

DC Accuracy

Resolution n 12 — — Bits

INL Error INL -12 ±3 +12 LSB

DNL DNL -0.75 ±0.3 +0.75 LSB Device is Monotonic

Offset Error VOS — ±0.02 1 % of FSR Code 0x000h

Offset Error Temperature VOS/°C — 0.5 — ppm/°C -45°C to 25°C

Coefficient — -0.77 — ppm/°C +25°C to 85°C

Gain Error gE — -0.15 1 % of FSR Code 0xFFFh, not including offset

error.

Gain Error Temperature G/°C — -3 — ppm/°C

Coefficient

Input Amplifier (VREF Input)

Input Range - Buffered Mode VREF 0.040 — VDD-0.040 V Note 1

Input Range - Unbuffered VREF 0 — VDD V Code = 2048,

Mode VREF = 0.2v p-p, f = 100 Hz and 1 kHz

Input Impedance RVREF — 165 — k Unbuffered Mode

Note 1: By design, not production tested.

2: Too small to quantify.

2007 Microchip Technology Inc. DS21897B-page 3

MCP4921/4922

3V AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise indicated, VDD = 3V, AVSS = 0V, VREF = 2.048V external, output buffer gain (G) = 1x,

RL = 5 k to GND, CL = 100 pF TA = -40 to +85°C. Typical values at 25°C

Parameters Sym Min Typ Max Units Conditions

Input Capacitance – CVREF — 7 — pF

Unbuffered Mode

Multiplier Mode fVREF — 440 — kHz VREF = 2.048V ±0.1 Vp-p, unbuffered,

-3 dB Bandwidth G=1

fVREF — 390 — kHz VREF = 2.048V ±0.1 Vp-p, unbuffered,

G=2

Multiplier Mode – THDVREF — -73 — dB VREF = 2.5V ±0.1 Vp-p,

Total Harmonic Distortion Frequency = 1 kHz

Output Amplifier

Output Swing VOUT — 0.010 — Accuracy is better than 1 LSB for

to VDD VOUT = 10 mV to (VDD – 40 mV)

– 0.040

Phase Margin m — 66 — degrees

Slew Rate SR — 0.55 — V/µs

Short Circuit Current ISC — 14 24 mA

Settling Time tsettling — 4.5 — µs Within 1/2 LSB of final value from 1/4

to 3/4 full-scale range

Dynamic Performance

DAC-to-DAC Crosstalk — 10 — nV-s Note 2

Major Code Transition Glitch — 45 — nV-s 1 LSB change around major carry

(0111...1111 to 1000...0000)

Digital Feedthrough — 10 — nV-s Note 2

Analog Crosstalk — 10 — nV-s Note 2

Note 1: By design, not production tested.

2: Too small to quantify.

5V EXTENDED TEMPERATURE SPECIFICATIONS

Electrical Specifications: Unless otherwise indicated, VDD = 5V, AVSS = 0V, VREF = 2.048V, output buffer gain (G) = 2x, RL = 5 k

to GND, CL = 100 pF. Typical values at +125°C by characterization or simulation.

Parameters Sym Min Typ Max Units Conditions

Power Requirements

Input Voltage VDD 2.7 — 5.5

Input Current - MCP4921 IDD — 200 — µA Input unbuffered, digital inputs

Input Current - MCP4922 — 400 — grounded, output unloaded,

code at 0x000

Hardware Shutdown Current ISHDN — 1.5 — µA

Software Shutdown Current ISHDN_SW — 5 — µA

Power-On Reset threshold VPOR — 1.85 — V

DC Accuracy

Resolution n 12 — — Bits

INL Error INL — ±4 — LSB

DNL DNL — ±0.25 — LSB Device is Monotonic

Offset Error VOS — ±0.02 — % of FSR Code 0x000h

Offset Error Temperature VOS/°C — -5 — ppm/°C +25°C to +125°C

Coefficient

Note 1: By design, not production tested.

2: Too small to quantify.

DS21897B-page 4 2007 Microchip Technology Inc.

MCP4921/4922

5V EXTENDED TEMPERATURE SPECIFICATIONS (CONTINUED)

Electrical Specifications: Unless otherwise indicated, VDD = 5V, AVSS = 0V, VREF = 2.048V, output buffer gain (G) = 2x, RL = 5 k

to GND, CL = 100 pF. Typical values at +125°C by characterization or simulation.

Parameters Sym Min Typ Max Units Conditions

Gain Error gE — -0.10 — % of FSR Code 0xFFFh, not including offset

error

Gain Error Temperature G/°C — -3 — ppm/°C

Coefficient

Input Amplifier (VREF Input)

Input Range - Buffered Mode VREF — 0.040 to — V Note 1

VDD- Code = 2048,

0.040 VREF = 0.2v p-p, f = 100 Hz and 1 kHz

Input Range - Unbuffered VREF 0 — VDD V

Mode

Input Impedance RVREF — 174 — k Unbuffered Mode

Input Capacitance - CVREF — 7 — pF

Unbuffered Mode

Multiplying Mode fVREF — 450 — kHz VREF = 2.5V ±0.1 Vp-p, Unbuffered,

-3 dB Bandwidth G=1

fVREF — 400 — kHz VREF = 2.5V ±0.1 Vp-p, Unbuffered,

G=2

Multiplying Mode - Total THDVREF — — — dB VREF = 2.5V ±0.1Vp-p,

Harmonic Distortion Frequency = 1 kHz

Output Amplifier

Output Swing VOUT — 0.010 to — Accuracy is better than 1 LSB for

VDD – VOUT = 10 mV to (VDD – 40 mV)

0.040

Phase Margin m — 66 — degrees

Slew Rate SR — 0.55 — V/µs

Short Circuit Current ISC — 17 — mA

Settling Time tsettling — 4.5 — µs Within 1/2 LSB of final value from 1/4

to 3/4 full-scale range

Dynamic Performance

DAC to DAC Crosstalk — 10 — nV-s Note 2

Major Code Transition Glitch — 45 — nV-s 1 LSB change around major carry

(0111...1111 to 1000...0000)

Digital Feedthrough — 10 — nV-s Note 2

Analog Crosstalk — 10 — nV-s Note 2

Note 1: By design, not production tested.

2: Too small to quantify.

2007 Microchip Technology Inc. DS21897B-page 5

MCP4921/4922

AC CHARACTERISTICS (SPI TIMING SPECIFICATIONS)

Electrical Specifications: Unless otherwise indicated, VDD= 2.7V – 5.5V, TA= -40 to +125°C.

Typical values are at +25°C.

Parameters Sym Min Typ Max Units Conditions

Schmitt Trigger High-Level VIH 0.7 VDD — — V

Input Voltage (All digital input

pins)

Schmitt Trigger Low-Level VIL — — 0.2 VD V

Input Voltage D

(All digital input pins)

Hysteresis of Schmitt Trigger VHYS — 0.05 VDD —

Inputs

Input Leakage Current ILEAKAGE -1 — 1 A SHDN = LDAC = CS = SDI =

SCK + VREF = VDD or AVSS

Digital Pin Capacitance CIN, — 10 — pF VDD = 5.0V, TA = +25°C,

(All inputs/outputs) COUT fcLK = 1 MHz (Note 1)

Clock Frequency FCLK — — 20 MHz TA = +25°C (Note 1)

Clock High Time tHI 15 — — ns Note 1

Clock Low Time tLO 15 — — ns Note 1

CS Fall to First Rising CLK tCSSR 40 — — ns Applies only when CS falls with

Edge CLK high. (Note 1)

Data Input Setup Time tSU 15 — — ns Note 1

Data Input Hold Time tHD 10 — — ns Note 1

SCK Rise to CS Rise Hold tCHS 15 — — ns Note 1

Time

CS High Time tCSH 15 — — ns Note 1

LDAC Pulse Width tLD 100 — — ns Note 1

LDAC Setup Time tLS 40 — — ns Note 1

SCK Idle Time before CS Fall tIDLE 40 — — ns Note 1

Note 1: By design and characterization, not production tested.

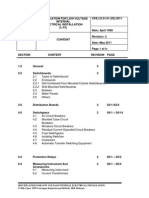

tCSH

CS

tIDLE

tCSSR tHI tLO tCHS

Mode 1,1

SCK Mode 0,0

tSU tHD

SI

MSB in LSB in

LDAC

tLS tLD

FIGURE 1-1: SPI™ Input Timing.

DS21897B-page 6 2007 Microchip Technology Inc.

MCP4921/4922

TEMPERATURE CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, VDD = +2.7V to +5.5V, AVSS = GND.

Parameters Sym Min Typ Max Units Conditions

Temperature Ranges

Specified Temperature Range TA -40 — +125 °C

Operating Temperature Range TA -40 — +125 °C Note 1

Storage Temperature Range TA -65 — +150 °C

Thermal Package Resistances

Thermal Resistance, 8L-PDIP JA — 85 — °C/W

Thermal Resistance, 8L-SOIC JA — 163 — °C/W

Thermal Resistance, 8L-MSOP JA — 206 — °C/W

Thermal Resistance, 14L-PDIP JA — 70 — °C/W

Thermal Resistance, 14L-SOIC JA — 120 — °C/W

Thermal Resistance, 14L-TSSOP JA — 100 — °C/W

Note 1: The MCP492X family of DACs operate over this extended temperature range, but with reduced

performance. Operation in this range must not cause TJ to exceed the Maximum Junction Temperature of

150°C.

2007 Microchip Technology Inc. DS21897B-page 7

MCP4921/4922

2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein

are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V , AVSS = 0V, VREF = 2.048V, Gain = 2, RL = 5 k , CL = 100 pF.

FIGURE 2-1: DNL vs. Code. FIGURE 2-4: Absolute DNL vs. Ambient

Temperature.

FIGURE 2-2: DNL vs. Code and Ambient FIGURE 2-5: Absolute DNL vs. Voltage

Temperature. Reference.

FIGURE 2-3: DNL vs. Code and VREF.

Gain=1.

DS21897B-page 8 2007 Microchip Technology Inc.

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- ADS Tutorial: A Beginners Tutorial: Modes of OperationДокумент23 страницыADS Tutorial: A Beginners Tutorial: Modes of OperationShakil Ahmed ChowdhuryОценок пока нет

- Trasistor Mosfet Placa MotorДокумент9 страницTrasistor Mosfet Placa MotorDemóstenes Moraes OlintoОценок пока нет

- 33 KV Control Relay Spec PDFДокумент75 страниц33 KV Control Relay Spec PDFMohanta Amrit100% (2)

- Jameco Part Number 894542: Distributed byДокумент22 страницыJameco Part Number 894542: Distributed byVeGiОценок пока нет

- III 7 Hall EffectДокумент8 страницIII 7 Hall EffectHa ZimОценок пока нет

- Ch-11 Electricity and MagДокумент56 страницCh-11 Electricity and MagTakkee BireeОценок пока нет

- Nadar Saraswathi College of Engineering and Technology, TheniДокумент11 страницNadar Saraswathi College of Engineering and Technology, Thenipriya dharshiniОценок пока нет

- Gel EarthingДокумент6 страницGel EarthingVasudha EarthingОценок пока нет

- 140M Motor Protection Circuit Breaker For Multiple Motor Installation With DrivesДокумент2 страницы140M Motor Protection Circuit Breaker For Multiple Motor Installation With DrivesNelsonОценок пока нет

- Fem100 PDFДокумент12 страницFem100 PDFmissoum mohamedОценок пока нет

- Is 9482 1996 PDFДокумент30 страницIs 9482 1996 PDFabcОценок пока нет

- LM2901x-Q1 Quadruple Automotive Comparator: 1 Features 3 DescriptionДокумент21 страницаLM2901x-Q1 Quadruple Automotive Comparator: 1 Features 3 DescriptionMAXIMILIANO CASTILLO ANTONIOОценок пока нет

- Soft Starter Design For 3 Phase Induction MotorДокумент3 страницыSoft Starter Design For 3 Phase Induction MotorInternational Journal of Innovative Science and Research TechnologyОценок пока нет

- Refurbishment and Life Extension of Circuit Breakers As An Asset Management ToolДокумент8 страницRefurbishment and Life Extension of Circuit Breakers As An Asset Management ToolLaura RoseroОценок пока нет

- Kongu PDFДокумент95 страницKongu PDFArunMozhiDevan3Оценок пока нет

- AN1895 - L6562 375W Step by StepДокумент16 страницAN1895 - L6562 375W Step by Stepbetodias30Оценок пока нет

- What Are The Types of Potential Transformer (PT) ? Describe EachДокумент7 страницWhat Are The Types of Potential Transformer (PT) ? Describe EachFEMAE DOMANEOОценок пока нет

- Pdu Lab Manual 2017 LabsДокумент125 страницPdu Lab Manual 2017 LabsUmar MasoodОценок пока нет

- 502 LM324N PDFДокумент13 страниц502 LM324N PDFmantenimiento74Оценок пока нет

- Common Tools and Equipment CSSДокумент2 страницыCommon Tools and Equipment CSSSharmyne Leigh CorpuzОценок пока нет

- Electrical EngineeringДокумент10 страницElectrical Engineeringkim jeonОценок пока нет

- D7E M07 ElecDrPT EN TXTДокумент84 страницыD7E M07 ElecDrPT EN TXTvicente456Оценок пока нет

- Physics of Nanoscale Transistors - An Introduction To Electronics From The Bottom UpДокумент52 страницыPhysics of Nanoscale Transistors - An Introduction To Electronics From The Bottom UpLIAKMANОценок пока нет

- Operation Guide - RX Path ImbalanceДокумент3 страницыOperation Guide - RX Path ImbalanceBiodun123456775% (4)

- Prevectron 3® S40 ConnectДокумент2 страницыPrevectron 3® S40 ConnectIndelec IndiaОценок пока нет

- PowerFlex 755 Install ManualДокумент116 страницPowerFlex 755 Install Manualkande666Оценок пока нет

- JKR Specs L-S1 Specification For Low Internal Electrical Installation May-2011 Rev.2Документ114 страницJKR Specs L-S1 Specification For Low Internal Electrical Installation May-2011 Rev.2Leong Km86% (7)

- PIP ELSMC13 Low-Voltage Motor Control Centers - May 2018 PDFДокумент24 страницыPIP ELSMC13 Low-Voltage Motor Control Centers - May 2018 PDFist93993Оценок пока нет

- 7SS52 enДокумент418 страниц7SS52 envsrikala68Оценок пока нет

- Fuzzy Logic Controller On DC/DC Boost Converter: November 2010Документ7 страницFuzzy Logic Controller On DC/DC Boost Converter: November 2010RahmadBòzОценок пока нет