Академический Документы

Профессиональный Документы

Культура Документы

Mar Vell 88MC200 - Microcontroller - Datasheet - Rev - B PDF

Загружено:

Franklin JimenezОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Mar Vell 88MC200 - Microcontroller - Datasheet - Rev - B PDF

Загружено:

Franklin JimenezАвторское право:

Доступные форматы

Marvell® 88MC200

Microcontroller

Datasheet

Doc. No. MV-S108780-U0 Rev. B

July 2013

Document Classification: Proprietary

Marvell. Moving Forward Faster Information

88MC200 Microcontroller

Datasheet

1

Document Conventions

2

3

Note: Provides related information or information of special importance. 4

5

6

Caution: Indicates potential damage to hardware or software, or loss of data. 7

8

9

10

Warning: Indicates a risk of personal injury. 11

12

13

Document Status 14

Doc Status: Not applicable Technical Publication: 0.xx 15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

For more information, visit our website at: www.marvell.com 43

Disclaimer 44

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, 45

without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any

kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any 46

particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. 47

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use

Marvell products in these types of equipment or applications.

48

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees: 49

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control 50

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are 51

controlled for national security reasons by the EAR; and, 52

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant,

not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons

53

by the EAR, or is subject to controls under the U.S. Munitions List ("USML"). 54

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any

55

such information.

Copyright © 2013. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, 56

Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. 57

Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All

other trademarks are the property of their respective owners. 58

59

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 2 Document Classification: Proprietary Information July 2013

Table of Contents

Table of Contents

1 Product Overview ........................................................................................................................ 23

1.1 Introduction .....................................................................................................................................................23

1.2 Features ..........................................................................................................................................................24

1.3 Pin Descriptions ..............................................................................................................................................26

1.3.1 Pinout................................................................................................................................................26

1.4 Feature Descriptions .......................................................................................................................................39

1.4.1 ARM Cortex-M3 CPU Core ..............................................................................................................39

1.4.2 Embedded SRAM .............................................................................................................................39

1.4.3 In-Package Flash ..............................................................................................................................39

1.4.4 Boot ROM .........................................................................................................................................39

1.4.5 AHB Bus Matrix ................................................................................................................................39

1.4.6 Power, Reset and Clock Control.......................................................................................................39

1.4.7 Direct Memory Access (DMA)...........................................................................................................39

1.4.8 General Purpose IO (GPIO) .............................................................................................................40

1.4.9 Watchdog Timer (WDT) ....................................................................................................................40

1.4.10 Real Time Clock (RTC).....................................................................................................................41

1.4.11 General Purpose Timers...................................................................................................................41

1.4.12 Advanced Encryption Standard (AES) Engine .................................................................................41

1.4.13 Cyclic Redundancy Check (CRC).....................................................................................................42

1.4.14 General Purpose ADC ......................................................................................................................42

1.4.15 Analog Comparators.........................................................................................................................42

1.4.16 DAC ..................................................................................................................................................43

1.4.17 UART ................................................................................................................................................43

1.4.18 I2C ....................................................................................................................................................43

1.4.19 QSPI Interface .................................................................................................................................44

1.4.20 SSP...................................................................................................................................................44

1.4.21 SDIO .................................................................................................................................................45

1.4.22 USB ..................................................................................................................................................45

1.5 Part Ordering...................................................................................................................................................45

2 Processor Overview .................................................................................................................... 49

2.1 Overview .........................................................................................................................................................49

2.1.1 Cortex M3 Features ..........................................................................................................................49

2.1.2 Memory Protection Unit (MPU) .........................................................................................................49

2.1.3 Nested Vectored Interrupt Controller (NVIC) ....................................................................................49

2.1.4 SysTick Timer ...................................................................................................................................50

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 3

88MC200 Microcontroller

Datasheet

3 I/O Configuration ........................................................................................................................ 51

3.1 Pinmux Alternate Functions ............................................................................................................................51

3.1.1 GPIO_0 (Offset=0x0) ......................................................................................................................52

3.1.2 GPIO_1 (Offset=0x4) ......................................................................................................................52

3.1.3 GPIO_2 (Offset=0x8) ......................................................................................................................53

3.1.4 GPIO_3 (Offset=0xC) .....................................................................................................................53

3.1.5 GPIO_4 (Offset=0x10) ....................................................................................................................54

3.1.6 GPIO_5 (Offset=0x14) ....................................................................................................................54

3.1.7 GPIO_6 (Offset=0x18) ....................................................................................................................55

3.1.8 GPIO_7 (Offset=0x1C) ...................................................................................................................55

3.1.9 GPIO_8 (Offset=0x20) ....................................................................................................................56

3.1.10 GPIO_9 (Offset=0x24) ...................................................................................................................56

3.1.11 GPIO_10 (Offset=0x28) ..................................................................................................................57

3.1.12 GPIO_11 (Offset=0x2C) .................................................................................................................57

3.1.13 GPIO_16 (Offset=0x40) ..................................................................................................................58

3.1.14 GPIO_17 (Offset=0x44) ..................................................................................................................58

3.1.15 GPIO_18 (Offset=0x48) ..................................................................................................................59

3.1.16 GPIO_19 (Offset=0x4C) .................................................................................................................59

3.1.17 GPIO_20 (Offset=0x50) ..................................................................................................................60

3.1.18 GPIO_21 (Offset=0x54) ..................................................................................................................60

3.1.19 GPIO_22 (Offset=0x58) ..................................................................................................................60

3.1.20 GPIO_23 (Offset=0x5C) .................................................................................................................61

3.1.21 GPIO_24 (Offset=0x60) ..................................................................................................................61

3.1.22 GPIO_25 (Offset=0x64) ..................................................................................................................62

3.1.23 GPIO_26 (Offset=0x68) ..................................................................................................................63

3.1.24 GPIO_27 (Offset=0x6C) .................................................................................................................63

3.1.25 GPIO_28 (Offset=0x70) ..................................................................................................................64

3.1.26 GPIO_29 (Offset=0x74) ..................................................................................................................64

3.1.27 GPIO_30 (Offset=0x78) ..................................................................................................................65

3.1.28 GPIO_32 (Offset=0x80) ..................................................................................................................65

3.1.29 GPIO_33 (Offset=0x84) ..................................................................................................................66

3.1.30 GPIO_34(Offset=0x88) ..................................................................................................................66

3.1.31 GPIO_35(Offset=0x8C) ..................................................................................................................67

3.1.32 GPIO_40(Offset=0xA0) ...................................................................................................................67

3.1.33 GPIO_41(Offset=0xA4) ...................................................................................................................68

3.1.34 GPIO_42(Offset=0xA8) ...................................................................................................................69

3.1.35 GPIO_43 (Offset=0xAC) .................................................................................................................69

3.1.36 GPIO_44 (Offset=0xB0) ..................................................................................................................70

3.1.37 GPIO_45 (Offset=0xB4) ..................................................................................................................70

3.1.38 GPIO_50 (Offset=0xC8) .................................................................................................................71

3.1.39 GPIO_51 (Offset=0xCC) .................................................................................................................71

3.1.40 GPIO_52 (Offset=0xD0) .................................................................................................................72

3.1.41 GPIO_53 (Offset=0xD4) .................................................................................................................72

3.1.42 GPIO_54 (Offset=0xD8) .................................................................................................................73

3.1.43 GPIO_55 (Offset=0xDC) .................................................................................................................73

3.1.44 GPIO_56 (Offset=0xE0) ..................................................................................................................74

3.1.45 GPIO_57(Offset=0xE4) ...................................................................................................................74

3.1.46 GPIO_58 (Offset=0xE8) ..................................................................................................................75

3.1.47 GPIO_59 (Offset=0xEC) .................................................................................................................75

3.1.48 GPIO_60 (Offset=0xF0) ..................................................................................................................76

3.1.49 GPIO_61 (Offset=0xF4) ..................................................................................................................76

3.1.50 GPIO_62 (Offset=0xF8) ..................................................................................................................77

3.1.51 GPIO_63 (Offset=0xFC) .................................................................................................................77

3.1.52 GPIO_64 (Offset=0x100) ................................................................................................................78

3.1.53 GPIO_65 (Offset=0x104) ................................................................................................................78

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 4 Document Classification: Proprietary Information July 2013

Table of Contents

3.1.54 GPIO_66 (Offset=0x108) ................................................................................................................79

3.1.55 GPIO_68 (Offset=0x110) ...............................................................................................................79

3.1.56 GPIO_72 (Offset=0x120) ................................................................................................................80

3.1.57 GPIO_73 (Offset=0x124) .................................................................................................................80

3.1.58 GPIO_74 (Offset=0x128) ................................................................................................................81

3.1.59 GPIO_75 (Offset=0x12C) ...............................................................................................................81

3.1.60 GPIO_76 (Offset=0x130) ................................................................................................................82

3.1.61 GPIO_77 (Offset=0x134) ................................................................................................................82

3.1.62 GPIO_78 (Offset=0x138) ................................................................................................................83

3.1.63 GPIO_79 (Offset=0x13C) ...............................................................................................................83

3.1.64 I/O Padding .....................................................................................................................................84

4 System Control ............................................................................................................................ 87

4.1 Overview .........................................................................................................................................................87

4.2 Features ..........................................................................................................................................................87

4.3 Register Description ........................................................................................................................................87

5 Power, Reset, and Clock Control ............................................................................................... 89

5.1 Overview .........................................................................................................................................................89

5.2 Power Supply ..................................................................................................................................................89

5.2.1 Power Pins........................................................................................................................................90

5.2.2 I/O Power Configuration ...................................................................................................................91

5.2.3 AON Domain.....................................................................................................................................92

5.2.3.1 Ultra Low-Power Comparator .............................................................................................92

5.2.3.2 Brownout Detection ............................................................................................................93

5.3 Power Modes ..................................................................................................................................................93

5.4 Power Mode Transitions .................................................................................................................................96

5.5 Wake-up Sources............................................................................................................................................97

5.5.1 Wake-up from PM1 Mode .................................................................................................................97

5.5.2 Wake-up from PM2/3/4 Modes .........................................................................................................97

5.5.3 Reset Controller ................................................................................................................................98

5.6 Clock Controller...............................................................................................................................................98

5.6.1 Overview ..........................................................................................................................................98

5.6.2 Clock Sources...................................................................................................................................99

5.6.3 SFLL ...............................................................................................................................................101

5.6.4 Cortex-M3 Core Clock and Bus Clock ............................................................................................101

5.6.5 UART Clocks ..................................................................................................................................102

5.6.6 AUPLL for Audio Clock and USB Clock..........................................................................................102

5.6.7 CAU Clock ......................................................................................................................................103

5.6.8 GPT Clock ......................................................................................................................................104

5.6.8.1 GPT Sampling Clock ........................................................................................................104

5.6.9 Clock Output ...................................................................................................................................104

5.7 Register Description ......................................................................................................................................105

6 Memory Map, Interrupts and AHB Bus Fabric ........................................................................107

6.1 Overview .......................................................................................................................................................107

6.2 Memory Map .................................................................................................................................................107

6.3 Interrupts .......................................................................................................................................................110

6.4 AHB Bus Fabric.............................................................................................................................................113

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 5

88MC200 Microcontroller

Datasheet

7 Direct Memory Access Controller (DMA) ................................................................................117

7.1 Overview .......................................................................................................................................................117

7.2 Features ........................................................................................................................................................117

7.2.1 DMA Operation ..............................................................................................................................117

7.2.2 DMA Block Diagram .......................................................................................................................117

7.2.3 Basic Definitions .............................................................................................................................118

7.2.4 Peripheral Burst Transaction Requests ..........................................................................................119

7.2.4.1 Watermark Level and Transmit FIFO Underflow ..............................................................121

7.2.4.2 Choosing the Transmit Watermark Level .........................................................................121

7.2.4.3 Selecting DEST_MSIZE and Transmit FIFO Overflow.....................................................123

7.2.4.4 Receive Watermark Level and Receive FIFO Overflow ...................................................123

7.2.4.5 Choosing the Receive Watermark Level ..........................................................................123

7.2.4.6 Selecting SRC_MSIZE and Receive FIFO Underflow......................................................124

7.2.5 Interrupt ..........................................................................................................................................124

7.2.6 DMA Channel Mapping...................................................................................................................125

7.2.7 Operation Mode ..............................................................................................................................125

7.3 Register Descriptions ....................................................................................................................................126

8 Real Time Clock (RTC) ..............................................................................................................127

8.1 Overview .......................................................................................................................................................127

8.2 Functional Description...................................................................................................................................127

8.2.1 Counter Clock .................................................................................................................................127

8.2.2 Counting Mode ...............................................................................................................................128

8.2.3 Counter Update Mode ....................................................................................................................128

8.2.4 Interrupt ..........................................................................................................................................128

8.3 Programming Notes ......................................................................................................................................128

8.3.1 Initialization .....................................................................................................................................128

8.3.2 UPP_VAL........................................................................................................................................129

8.4 Register Description ......................................................................................................................................129

9 General Purpose Timers (GPT) ................................................................................................131

9.1 Overview .......................................................................................................................................................131

9.2 Functional Description...................................................................................................................................131

9.2.1 Counter ..........................................................................................................................................133

9.2.1.1 Counter Clock...................................................................................................................133

9.2.1.2 Counting Mode .................................................................................................................133

9.2.1.3 Counter Update Mode ......................................................................................................134

9.2.2 Interrupt ..........................................................................................................................................134

9.2.3 Channel Operation Modes ..............................................................................................................135

9.2.3.1 Counter Match Register 0 and 1 (CMR0 and CMR1).......................................................135

9.2.3.2 No Function Mode ............................................................................................................135

9.2.3.3 Input Capture Mode..........................................................................................................135

9.2.3.4 One-Shot Pulse Mode ......................................................................................................136

9.2.3.5 One-Shot Edge Mode.......................................................................................................137

9.2.3.6 Pulse-Width Modulation (PWM) Edge-Aligned Mode.......................................................138

9.2.3.7 Pulse-Width Modulation (PWM) Center-Aligned Mode ....................................................139

9.2.4 ADC Trigger ...................................................................................................................................141

9.2.5 DAC Trigger ....................................................................................................................................142

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 6 Document Classification: Proprietary Information July 2013

Table of Contents

9.3 Programming Notes ......................................................................................................................................143

9.3.1 Initialization .....................................................................................................................................143

9.3.2 UPP_VAL........................................................................................................................................144

9.3.3 User Request Register ...................................................................................................................144

9.4 Register Description ......................................................................................................................................144

10 Secure Digital Input/Output (SDIO Controller)........................................................................145

10.1 Overview .......................................................................................................................................................145

10.2 Signal Descriptions .......................................................................................................................................145

10.3 Controller Operation ......................................................................................................................................146

10.3.1 Operation ........................................................................................................................................148

10.3.1.1 Data Transfers..................................................................................................................148

10.4 Commands and Operations ..........................................................................................................................149

10.4.1 Overview .........................................................................................................................................149

10.4.1.1 Read/Write Commands ....................................................................................................149

10.4.2 Controller Functional Description....................................................................................................150

10.5 Interrupts .......................................................................................................................................................152

10.6 Clock Control.................................................................................................................................................153

10.7 Data FIFOs....................................................................................................................................................153

10.7.1 Command Response Register........................................................................................................153

10.7.2 Receive Data FIFO Configuration...................................................................................................154

10.7.3 Transmit Data FIFO Configuration..................................................................................................154

10.7.4 DMA and Programmed I/O .............................................................................................................154

10.8 Low-Power Mode Operation .........................................................................................................................155

10.9 Card Communication Protocol ......................................................................................................................155

10.9.1 PIO Operation .................................................................................................................................155

10.9.2 DMA Operation ...............................................................................................................................156

10.9.3 Abort Transaction ...........................................................................................................................157

10.9.3.1 Synchronous Abort ...........................................................................................................157

10.10 Register Descriptions ....................................................................................................................................158

11 USB OTG Interface Controller ..................................................................................................159

11.1 Features ........................................................................................................................................................159

11.2 Internal Bus Interface ....................................................................................................................................160

11.2.1 DMA Engine....................................................................................................................................160

11.2.2 Dual Port RAM Controller ...............................................................................................................161

11.2.3 Protocol Engine ..............................................................................................................................161

11.2.4 Port Controller.................................................................................................................................161

11.3 Signal Descriptions .......................................................................................................................................161

11.4 Functional Description...................................................................................................................................162

11.4.1 Host Data Structure ........................................................................................................................162

11.5 USB Controller Operation .............................................................................................................................163

11.5.1 FIFO Operation in Device Mode .....................................................................................................163

11.5.1.1 Streaming Mode ...............................................................................................................163

11.5.1.2 Additional Notes on TX FIFO Buffering – IN Endpoints ...................................................164

11.5.1.3 Non-Streaming Mode .......................................................................................................165

11.5.1.4 FIFO Operation in Host Mode ..........................................................................................165

11.5.2 Clock Control and Enables .............................................................................................................168

11.5.3 Programming Guidelines ................................................................................................................168

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 7

88MC200 Microcontroller

Datasheet

11.6 Register Descriptions ....................................................................................................................................168

12 WatchDog Timer (WDT) ............................................................................................................169

12.1 Functional Description...................................................................................................................................169

12.1.1 Counter Operation ..........................................................................................................................169

12.1.2 Interrupt ..........................................................................................................................................169

12.1.3 System Reset .................................................................................................................................170

12.1.4 Reset Pulse Length ........................................................................................................................170

12.2 Initialization Sequence ..................................................................................................................................170

12.3 Register Description ......................................................................................................................................171

13 Quad Serial Peripheral Interface (QSPI) Controller ................................................................173

13.1 Overview .......................................................................................................................................................173

13.2 Features List .................................................................................................................................................173

13.3 Block Diagram ...............................................................................................................................................173

13.4 IO Description ...............................................................................................................................................174

13.5 Functional Description...................................................................................................................................174

13.5.1 Basic Operation ..............................................................................................................................174

13.5.2 Serial Flash Data Format ................................................................................................................175

13.6 Usage Models and Programming Notes ......................................................................................................182

13.7 QSPI0 Interface to In-package Serial Flash ..................................................................................................182

13.7.1 Basic Read to Serial Flash Without DMA and Using Polling ..........................................................182

13.7.1.1 Page Program to Serial Flash Without DMA and Using Polling .......................................182

13.8 Register Description ......................................................................................................................................183

14 In-Package Flash .......................................................................................................................185

14.1 Overview .......................................................................................................................................................185

14.2 Features ........................................................................................................................................................185

14.3 Block Diagram ..............................................................................................................................................186

14.4 Functional Description...................................................................................................................................187

14.4.1 QSPI0 Interface ..............................................................................................................................187

14.4.1.1 Standard SPI Operation ...................................................................................................187

14.4.1.2 Dual SPI Operation ..........................................................................................................187

14.4.1.3 Quad SPI Operation .........................................................................................................187

14.4.2 Write Protection ..............................................................................................................................187

14.4.2.1 Write Protect Features .....................................................................................................187

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 8 Document Classification: Proprietary Information July 2013

Table of Contents

14.5 Control and Status Registers ........................................................................................................................188

14.5.1 Status Register ...............................................................................................................................188

14.5.1.1 BUSY................................................................................................................................188

14.5.1.2 Write Enable Latch (WEL) ................................................................................................188

14.5.1.3 Block Protect Bits (BP2, BP1, BP0) .................................................................................188

14.5.1.4 Top/Bottom Block Protect (TB).........................................................................................188

14.5.1.5 Sector/Block Protect (SEC) ..............................................................................................188

14.5.1.6 Complement Protect (CMP) .............................................................................................188

14.5.1.7 Status Register Protect (SRP1, SRP0) ............................................................................189

14.5.1.8 Erase/Program Suspend Status (SUS) ............................................................................189

14.5.1.9 Security Register Lock Bits (LB3, LB2, LB1) ....................................................................189

14.5.1.10Quad Enable (QE) ...........................................................................................................189

14.5.2 Instructions .....................................................................................................................................192

14.5.2.1 Instruction Set Table 1 (Erase, Program Instructions) 1 ..................................................194

14.5.2.2 Instruction Set Table 2 (Read Instructions) ......................................................................195

14.5.2.3 Instruction Set Table 3 (ID, Security Instructions) ............................................................196

15 General Purpose Input Output (GPIO) .....................................................................................197

15.1 Overview .......................................................................................................................................................197

15.2 GPIO Block Diagram .....................................................................................................................................197

15.3 GPIO Function Description ...........................................................................................................................197

15.3.1 GPIO Ports ....................................................................................................................................197

15.3.2 I/O Control ......................................................................................................................................198

15.3.3 GPIO Interrupt ................................................................................................................................198

15.3.4 External Interrupts .........................................................................................................................198

15.4 GPIO Register ...............................................................................................................................................199

16 Advanced Encryption Standard (AES) ....................................................................................201

16.1 Features ........................................................................................................................................................201

16.2 Functional Description...................................................................................................................................201

16.2.1 AES Operational Flow ....................................................................................................................201

16.2.2 AES Configuration ..........................................................................................................................202

16.2.3 Data Access Method.......................................................................................................................203

16.2.4 Starting the AES Engine .................................................................................................................203

16.2.5 Interrupt Request ............................................................................................................................203

16.2.6 Partial Code Support ......................................................................................................................204

16.2.7 Error Status Check .........................................................................................................................204

16.2.8 Output Vector..................................................................................................................................204

16.2.9 AES Operation Pseudo Code .........................................................................................................205

16.3 References for AES Standard .......................................................................................................................206

16.4 Register Description ......................................................................................................................................206

17 Cyclic Redundancy Check (CRC) ............................................................................................207

17.1 Overview .......................................................................................................................................................207

17.2 Features ........................................................................................................................................................207

17.3 CRC Operation Flow .....................................................................................................................................207

17.4 Register Descriptions ....................................................................................................................................208

18 Universal Asynchronous Receiver Transmitter (UART) ........................................................209

18.1 Overview .......................................................................................................................................................209

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 9

88MC200 Microcontroller

Datasheet

18.2 Block Diagram ...............................................................................................................................................209

18.3 Function Description .....................................................................................................................................210

18.3.1 External Signal Descriptions ..........................................................................................................210

18.3.2 Protocol...........................................................................................................................................211

18.3.3 SIR Protocol....................................................................................................................................211

18.3.4 FIFO Access ...................................................................................................................................212

18.3.5 Calculating Baud Rates ..................................................................................................................213

18.3.6 Interrupts.........................................................................................................................................213

18.3.7 DMA Support .................................................................................................................................213

18.3.8 Auto Flow Control ..........................................................................................................................214

18.4 Register Descriptions ....................................................................................................................................216

19 Inter-Integrated Circuit (I2C) .....................................................................................................217

19.1 Overview .......................................................................................................................................................217

19.2 Features ........................................................................................................................................................217

19.3 Signal Descriptions .......................................................................................................................................217

19.4 Operation ......................................................................................................................................................218

19.4.1 I2C Block Diagram..........................................................................................................................218

19.4.2 I2C Bus Terminology ......................................................................................................................218

19.5 I2C Behavior .................................................................................................................................................219

19.5.1 START and STOP Generation .......................................................................................................220

19.5.1.1 Combined Formats ...........................................................................................................221

19.5.2 I2C Protocols ..................................................................................................................................221

19.5.2.1 START and STOP Conditions ..........................................................................................221

19.5.2.2 Addressing Slave Protocol ...............................................................................................221

19.5.2.3 Transmitting and Receiving Protocol................................................................................222

19.5.3 Multiple Master Arbitration ..............................................................................................................224

19.5.4 Clock Synchronization ....................................................................................................................224

19.5.5 Operation Modes ............................................................................................................................225

19.5.5.1 Slave Mode Operation......................................................................................................225

19.5.5.2 Master Mode Operation....................................................................................................228

19.5.6 I2C.CLK Frequency Configuration ..................................................................................................229

19.5.6.1 Calculating High and Low Counts ....................................................................................229

19.5.7 DMA Controller Interface ................................................................................................................230

19.6 Register Descriptions ....................................................................................................................................230

20 Synchronous Serial Protocol (SSP).........................................................................................231

20.1 Overview .......................................................................................................................................................231

20.2 Features ........................................................................................................................................................231

20.3 External Signal Descriptions .........................................................................................................................231

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 10 Document Classification: Proprietary Information July 2013

Table of Contents

20.4 Operation ......................................................................................................................................................232

20.4.1 FIFO Operation ...............................................................................................................................232

20.4.1.1 Parallel Data Formats for FIFO Storage...........................................................................233

20.4.1.2 FIFO Operation in Packed Mode......................................................................................233

20.4.1.3 Trailing Bytes in RXFIFO..................................................................................................233

20.4.2 Using Programmed I/O Data Transfers ..........................................................................................234

20.4.3 Using DMA Data Transfers .............................................................................................................234

20.4.4 Data Formats ..................................................................................................................................234

20.4.4.1 Serial Data Formats for Transfer to/from Peripherals.......................................................234

20.4.4.2 TI-SSP Format Details .....................................................................................................235

20.4.4.3 Motorola SPI Format Details ............................................................................................237

20.4.5 Programmable Serial Protocol (PSP) Format .................................................................................240

20.4.5.1 High Impedance on SSPx_TXD .......................................................................................244

20.4.6 Network Mode.................................................................................................................................247

20.4.6.1 Network Mode Registers ..................................................................................................248

20.4.7 I2S Emulation Using SSP ...............................................................................................................249

20.5 Register Descriptions ....................................................................................................................................251

21 Analog Digital Converter (ADC) ...............................................................................................253

21.1 Overview .......................................................................................................................................................253

21.2 Features ........................................................................................................................................................253

21.3 External Signal Description ...........................................................................................................................253

21.4 ADC Functional Description ..........................................................................................................................254

21.4.1 ADC Block Diagram ........................................................................................................................254

21.4.2 ADC On-Off Control and Conversion Trigger .................................................................................255

21.4.3 ADC Input .......................................................................................................................................255

21.4.4 Input Range ....................................................................................................................................257

21.4.5 Temperature Measurement ............................................................................................................257

21.4.6 ADC Reference Voltage .................................................................................................................258

21.4.7 ADC Throughput and Resolution ....................................................................................................259

21.4.8 ADC Conversion Results ................................................................................................................259

21.4.9 ADC Interrupts ................................................................................................................................261

21.4.10 ADC Calibration ..............................................................................................................................261

21.4.11 DMA Request .................................................................................................................................262

21.4.12 Battery Monitor ...............................................................................................................................262

21.4.13 External Trigger from GPT..............................................................................................................262

21.5 Register Description ......................................................................................................................................262

22 Digital Analog Converter (DAC) ...............................................................................................263

22.1 Overview .......................................................................................................................................................263

22.2 Features ........................................................................................................................................................263

22.3 External Signal Description ...........................................................................................................................263

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 11

88MC200 Microcontroller

Datasheet

22.4 DAC Configuration ........................................................................................................................................263

22.4.1 Synchronous Mode .........................................................................................................................264

22.4.2 Asynchronous Mode .......................................................................................................................265

22.4.3 Sinusoidal Waveform Generation ..................................................................................................265

22.4.4 Triangle Waveform Generation.......................................................................................................266

22.4.4.1 Up and Down Mode..........................................................................................................266

22.4.4.2 Up Mode ...........................................................................................................................266

22.4.5 Noise Generation ............................................................................................................................267

22.4.6 DMA Request .................................................................................................................................267

22.4.7 Event Trigger from GPT or GPIO ...................................................................................................267

22.5 Registers Description ....................................................................................................................................267

23 Analog Comparator (ACOMP) ..................................................................................................269

23.1 Overview .......................................................................................................................................................269

23.1.1 Features..........................................................................................................................................269

23.2 External Signal Description ...........................................................................................................................269

23.3 Functional Description...................................................................................................................................270

23.3.1 ACOMP0/1 Control Signals ............................................................................................................270

23.3.1.1 Warmup Time ...................................................................................................................270

23.3.1.2 Response Time ................................................................................................................270

23.3.1.3 Hysteresis.........................................................................................................................270

23.3.2 Comparator Output .........................................................................................................................271

23.3.2.1 Asynchronous Comparison Output at Register ................................................................271

23.3.2.2 Synchronous/Asynchronous Comparison Output at GPIO ..............................................271

23.3.2.3 Comparison Output Inversion...........................................................................................272

23.3.3 Comparator Output Edge Detection ...............................................................................................272

23.3.4 Interrupt ..........................................................................................................................................274

23.4 Register Description ......................................................................................................................................276

24 Boot ROM ..................................................................................................................................277

24.1 Overview .......................................................................................................................................................277

24.2 Boot ROM Flow Charts ................................................................................................................................277

24.2.1 Loading Code Through UART ........................................................................................................281

24.2.2 Loading Code Directly from Flash ..................................................................................................281

24.2.3 PM3 Wakeup ..................................................................................................................................281

24.3 Flash Image Format ......................................................................................................................................281

24.3.1 BootInfo/Section Header.................................................................................................................282

24.3.2 Code Image ....................................................................................................................................284

24.3.3 Retention Data Format ...................................................................................................................285

24.4 UART Download Protocol .............................................................................................................................285

25 Electrical, Mechanical and Thermal Specifications ...............................................................287

25.1 Package Information .....................................................................................................................................287

25.2 Maximum Ratings and Operating Conditions................................................................................................291

25.2.1 Absolute Maximum Ratings ............................................................................................................291

25.2.2 Operating Conditions ......................................................................................................................292

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 12 Document Classification: Proprietary Information July 2013

Table of Contents

25.3 Electrical Characteristics ...............................................................................................................................293

25.3.1 DC Voltage and Current Characteristics.........................................................................................293

25.3.2 I/O Port Characteristics...................................................................................................................293

25.3.3 Clock Characteristics ......................................................................................................................294

25.3.4 Power and Brownout Detection ......................................................................................................295

25.3.5 ADC Electrical Characteristics ........................................................................................................297

25.3.6 Analog Temperature Sensor Characteristics ..................................................................................300

25.3.7 ACOMP Electrical Characteristics ..................................................................................................301

25.3.8 DAC Electrical Characteristics ........................................................................................................302

25.3.9 AC Electrical Characteristics ..........................................................................................................304

25.3.9.1 SSP Timing Diagram and Specifications..........................................................................305

25.3.9.2 QSPI Timing Diagram and Specifications .......................................................................305

25.3.9.3 SDIO Timing Diagram and Specifications ........................................................................306

25.3.9.4 RESETn Pin Specification ................................................................................................307

Appendix A: 88MC200 Microcontroller Register Tables ........................................................................................A-1

Copyright © 2013 Marvell Doc. No. MV-S108780-U0 Rev. B

July 2013 Document Classification: Proprietary Information Page 13

88MC200 Microcontroller

Datasheet

Doc. No. MV-S108780-U0 Rev. B Copyright © 2013 Marvell

Page 14 Document Classification: Proprietary Information July 2013

List of Figures

List of Figures

1 Product Overview ............................................................................................................................ 23

Figure 1: 88MC200 Block Diagram ..................................................................................................................24

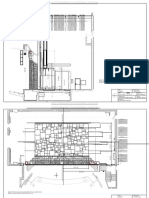

Figure 2: 88MC200 QFN88 Pinouts.................................................................................................................27

Figure 3: 88MC200 QFN68 Pinout ..................................................................................................................28

Figure 4: 88MC200 Microcontroller Package Markings for 88-Pin Part ...........................................................46

Figure 5: Part Ordering Number ......................................................................................................................46

2 Processor Overview ........................................................................................................................ 49

3 I/O Configuration ............................................................................................................................ 51

Figure 6: I/O Padding Structure .......................................................................................................................85

4 System Control ................................................................................................................................ 87

5 Power, Reset, and Clock Control ................................................................................................... 89

Figure 7: 88MC200 MCU Power Supply Overview ..........................................................................................89

Figure 8: Power Mode Transitions ...................................................................................................................97

Figure 9: High-Level Clocking Diagram .........................................................................................................100

6 Memory Map, Interrupts and AHB Bus Fabric ............................................................................ 107

Figure 10: System Memory Map Diagram .......................................................................................................108

Figure 11: Bus Matrix Interconnection .............................................................................................................114

7 Direct Memory Access Controller (DMA) .................................................................................... 117

Figure 12: DMA Block Diagram .......................................................................................................................118

Figure 13: Breakdown of DMA Transfer into Burst Transactions.....................................................................120

Figure 14: Breakdown of DMA Transfer into Single and Burst Transactions...................................................121

Figure 15: Case 1 Watermark Levels where IC_DMA_TDLR = 2....................................................................122

Figure 16: Case 2 Watermark Levels where IC_DMA_TDLR = 6....................................................................122

Figure 17: I2C Receive FIFO ...........................................................................................................................124

8 Real Time Clock (RTC) .................................................................................................................. 127

Figure 18: RTC Block Diagram ........................................................................................................................127

Figure 19: Count-up Mode ...............................................................................................................................128

9 General Purpose Timers (GPT) .................................................................................................... 131

Figure 20: GPT Block Diagram ........................................................................................................................132

Figure 21: Clock Source Selection...................................................................................................................133

Figure 22: Count Up Mode...............................................................................................................................134

Figure 23: Input Capture ..................................................................................................................................136