Академический Документы

Профессиональный Документы

Культура Документы

Interfaces

Загружено:

Nivin PaulАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Interfaces

Загружено:

Nivin PaulАвторское право:

Доступные форматы

Chapter 10

SystemVerilog Interfaces

Page 283

10.1 Interface concepts

Page 284

signals for main_bus must

be individually connected

to each module instance

Page 285

ports for main_bus must

be individually declared in

each module definition

Page 287

10.1.1 Disadvantages of Verilog’s module ports

• Declarations must be duplicated in multiple modules.

• Communication protocols must be duplicated in several modules.

• There is a risk of mismatched declarations in different modules.

• A change in the design specification can require modifications in

multiple modules.

connecting

modules in a

netlist requires

redundant port

declarations

The replicated port declarations also mean that, should the specifi

cation of the bus change during the design process, or in a next gen

eration of the design, then each and every module that shares the

bus must be changed.

A weakness in the Verilog

language is that a change to the ports in one module will usually

require changes in other modules.

protocols must

be duplicated in

each module

If, for example, three

modules read and write from a shared memory device, then the read

and write control logic must be duplicated in each of these modules.

disadvantage of using module ports to connect the

blocks of a design together is that detailed interconnections for the

design must be determined very early in the design cycle.

module ports

inhibit abstract

top-down design

Before any block of the design can be

modeled, the bus must first be broken down to individual signals

10.1.2 Advantages of SystemVerilog interfaces

Page 292

10.1.3 SystemVerilog interface contents

10.1.4 Differences between modules and interfaces

Page 293

10.2 Interface declarations

Page 295

10.2.1 Source code declaration order

10.2.2 Global and local interface definitions

Page 296

10.3 Using interfaces as module ports

10.3.1 Explicitly named interface ports

Page 297

10.3.2 Generic interface ports

10.3.3 Synthesis guidelines

10.4 Instantiating and connecting interfaces

Interface connection rules

Page 298

Interfaces connected to interface instances

10.5 Referencing signals within an interface

Page 300

10.6 Interface modports

Page 301

10.6.1 Specifying which modport view to use

Selecting the modport in the module instance

Page 302

Selecting the modport in the module port declaration

Page 304

Connecting to interfaces without specifying a modport

Synthesis considerations

Page 305

10.6.2 Using modports to define different sets of connections

Restricting module access to interface signals

Page 307

10.7 Using tasks and functions in interfaces

Page 308

10.7.1 Interface methods

10.7.2 Importing interface methods

Page 309

Import using a task or function name

Import using a task or function prototype

Page 310

Calling imported interface methods

Alternate methods within interfaces

Page 311

10.7.3 Synthesis guidelines for interface methods

Page 312

10.7.4 Exporting tasks and functions

Page 313

Exporting a task or function to the entire interface

Page 314

Restrictions on exporting tasks and functions

Page 315

10.8 Using procedural blocks in interfaces

10.9 Reconfigurable interfaces

Page 316

Parameterized interfaces

Page 317

Using generate blocks

10.10 Verification with interfaces

Page 318

10.11 Summary

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Manual Prevention An Control of Lost Cir PDFДокумент222 страницыManual Prevention An Control of Lost Cir PDFAna Maria TovarОценок пока нет

- STA TempДокумент34 страницыSTA TempNivin PaulОценок пока нет

- Speech Recognition Using Discrete Hidden Markov Model: Department of ECE, Saveetha Engineering College, Chennai, IndiaДокумент6 страницSpeech Recognition Using Discrete Hidden Markov Model: Department of ECE, Saveetha Engineering College, Chennai, IndiaNivin PaulОценок пока нет

- Coreapb3: Nivin PaulДокумент19 страницCoreapb3: Nivin PaulNivin PaulОценок пока нет

- SPI I2C Interface AnДокумент13 страницSPI I2C Interface AnNivin PaulОценок пока нет

- Implementation of PODEM Algorithm: OutlineДокумент2 страницыImplementation of PODEM Algorithm: OutlineNivin PaulОценок пока нет

- Low Noise Amplifier: Project Report Cmos RficДокумент11 страницLow Noise Amplifier: Project Report Cmos RficNivin PaulОценок пока нет

- Assignment 2Документ2 страницыAssignment 2Nivin PaulОценок пока нет

- Lab 4: BER of BPSK in AWGN Channel: TransmitterДокумент2 страницыLab 4: BER of BPSK in AWGN Channel: TransmitterNivin PaulОценок пока нет

- 4.uses of Metals - 1-32 For StudentsДокумент13 страниц4.uses of Metals - 1-32 For StudentsnergisalihpasaogluОценок пока нет

- Transmission Line TowersДокумент3 страницыTransmission Line TowersSoumik Dandapat100% (2)

- Vogue 201602 Japan PDFДокумент254 страницыVogue 201602 Japan PDFJack Douglas YooОценок пока нет

- Applied Physics: Ayesha Anwer Ul Haq Qureshi MCS Karachi University (UBIT) E-Mail: Ayesha - Anwer@indus - Edu.pkДокумент37 страницApplied Physics: Ayesha Anwer Ul Haq Qureshi MCS Karachi University (UBIT) E-Mail: Ayesha - Anwer@indus - Edu.pkEhsan JavedОценок пока нет

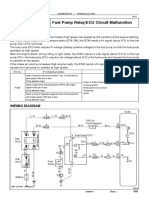

- DTC P1200 Fuel Pump Relay/ECU Circuit MalfunctionДокумент4 страницыDTC P1200 Fuel Pump Relay/ECU Circuit MalfunctiononealОценок пока нет

- Dual Axis Solar Activity Tracker For Solar Panels: Department of Engineering, Sciences and Humanities (DESH)Документ5 страницDual Axis Solar Activity Tracker For Solar Panels: Department of Engineering, Sciences and Humanities (DESH)sujay patilОценок пока нет

- HVSI804T WGD 83Документ6 страницHVSI804T WGD 83mnezamiОценок пока нет

- Overview of Missile Flight Control Systems: Paul B. JacksonДокумент16 страницOverview of Missile Flight Control Systems: Paul B. JacksonrobjohniiiОценок пока нет

- Ubd Planning Template With QuestionsДокумент3 страницыUbd Planning Template With Questionsapi-217297849Оценок пока нет

- Upcoming: Advisor Webcast: Oracle Database Resource ManagerДокумент41 страницаUpcoming: Advisor Webcast: Oracle Database Resource ManagerLayne MoránОценок пока нет

- MMW (Data Management) - Part 2Документ43 страницыMMW (Data Management) - Part 2arabellah shainnah rosalesОценок пока нет

- La 3391p Rev0.3novo DesbloqueadoДокумент48 страницLa 3391p Rev0.3novo DesbloqueadoRogeriotabiraОценок пока нет

- SolutionsДокумент8 страницSolutionsJavid BalakishiyevОценок пока нет

- Active Mathematics PDFДокумент22 страницыActive Mathematics PDFgoingforward77Оценок пока нет

- ECA 2markДокумент4 страницыECA 2markthangarajelectresОценок пока нет

- MSC Academic Guide - Admission Test PDFДокумент13 страницMSC Academic Guide - Admission Test PDFTonoy Peter CorrayaОценок пока нет

- The C Puzzle BookДокумент93 страницыThe C Puzzle Bookabhijeetnayak67% (3)

- 2016 FSAE Electric Vehicle Pedal Assembly DesignДокумент40 страниц2016 FSAE Electric Vehicle Pedal Assembly Designshubham rastogiОценок пока нет

- 1SC0 2PF Exam-Paper 20180616Документ20 страниц1SC0 2PF Exam-Paper 20180616Thasanya AlgamaОценок пока нет

- Design Method of 6-Element Boundary Gain For LLC Resonant Converter of Electric VehicleДокумент11 страницDesign Method of 6-Element Boundary Gain For LLC Resonant Converter of Electric VehicleSh M AaqibОценок пока нет

- PDF To Image Converter v2 HOW TO USEДокумент3 страницыPDF To Image Converter v2 HOW TO USEfairfaxcyclesОценок пока нет

- Test A: Two-Dimensional Motion and VectorsДокумент9 страницTest A: Two-Dimensional Motion and VectorsAref DahabrahОценок пока нет

- Coding in Communication System: Channel Coding) Will Be AddressedДокумент5 страницCoding in Communication System: Channel Coding) Will Be AddressedDuge PlakolliОценок пока нет

- Handwritten English Alphabet RecognitionДокумент8 страницHandwritten English Alphabet RecognitionIJRASETPublicationsОценок пока нет

- Clase 13-06Документ28 страницClase 13-06Jhurema NihuaОценок пока нет

- Numerical Methods in Rock Mechanics - 2002 - International Journal of Rock Mechanics and Mining SciencesДокумент19 страницNumerical Methods in Rock Mechanics - 2002 - International Journal of Rock Mechanics and Mining SciencesAnderson Lincol Condori PaytanОценок пока нет

- Reducing The Efficiency Gap by Optimal Allocation Using Modified Assignment Problem For Apparel Industry in Sri LankaДокумент1 страницаReducing The Efficiency Gap by Optimal Allocation Using Modified Assignment Problem For Apparel Industry in Sri LankaShivam BhandariОценок пока нет

- 8051 Serial CommunicationДокумент35 страниц8051 Serial CommunicationSanthosh CricketОценок пока нет

- LogДокумент7 страницLogHerdi YantoОценок пока нет