Академический Документы

Профессиональный Документы

Культура Документы

Ldica 1

Загружено:

RAJOLI GIRISAI MADHAVОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ldica 1

Загружено:

RAJOLI GIRISAI MADHAVАвторское право:

Доступные форматы

www.FirstRanker.com www.FirstRanker.

com

Code: 15A04509 R15

B.Tech III Year I Semester (R15) Supplementary Examinations June 2018

LINEAR & DIGITAL IC APPLICATIONS

(Electrical & Electronics Engineering)

Time: 3 hours Max. Marks: 70

PART – A

(Compulsory Question)

*****

1 Answer the following: (10 X 02 = 20 Marks)

(a) When is an Op-Amp said to be an ideal?

(b) Draw sample and hold circuit.

(c) Draw the functional diagram of successive approximation ADC.

(d) A 12 bit DAC has a resolution of 20m V/LSB. Find the full scale output voltage.

(e) Find the order of a low pass Butterworth filter that is to provide 40dB attenuation at 𝜔𝜔/𝜔𝜔ℎ = 2.

(f) Design a phase shift oscillator to oscillate at 100Hz.

(g) Mention the advantages of integrated circuits over discrete components.

(h) What happens when excess gate voltage is given to CMOS devices?

(i) Design a full adder circuit using decoder.

(j) Design an 1-bit magnitude comparator.

PART – B

(Answer all five units, 5 X 10 = 50 Marks)

UNIT – I

2 (a) Elaborate on an Op-Amp circuit which can generate single output pulse with adjustable time duration in

response to a trigger signal.

om

(b) Design an amplifier with a gain of -10 and input resistance equal to 10 kΩ.

r.c

OR

3 State the need for frequency compensation technique. With neat gain VS frequency curves elaborate and

ke

derive the necessary equations used for different compensating techniques.

an

UNIT – II

tR

4 What output voltage will be produced by a D/A converter whose output range is 0 to 10 V and whose

irs

input binary number is:

.F

(i) 10 (for 2-bit DAC)

(ii) 0110 (for 4-bit DAC)

w

w

(iii) 10111100 (for 8-bit DAC).

w

OR

5 Derive lock-in range and capture range of PLL with its neat block diagram and its explanation.

UNIT – III

6 (a) What are delay equalizers and why is it called so? With circuit diagram, derive the necessary equations

to justify it.

(b) Design a triangular wave generator using Op-Amp.

OR

7 Derive the output frequency of VCO.

UNIT – IV

8 Differentiate between MOS and CMOS. Elaborate on open drain and tristate CMOS outputs.

OR

9 Design a two input NAND gate using TTL open collector output and tristate output.

UNIT – V

10 Design a synchronous decade counter using D flip-flop.

OR

11 (a) Design a full subtractor circuit using 4x1 multiplexers.

(b) Design a 2-bit magnitude comparator.www.FirstRanker.com

*****

Вам также может понравиться

- Azure 900 QuestionsДокумент13 страницAzure 900 QuestionsRAJOLI GIRISAI MADHAV50% (2)

- Emi Sheet: Amount:-50,000 Period:-20 Months SL - No Principal Interest (8%) Total BalanceДокумент10 страницEmi Sheet: Amount:-50,000 Period:-20 Months SL - No Principal Interest (8%) Total BalanceRAJOLI GIRISAI MADHAVОценок пока нет

- Inequality Reasoning NotesДокумент14 страницInequality Reasoning NotesRAJOLI GIRISAI MADHAVОценок пока нет

- Inequalities (, / )Документ10 страницInequalities (, / )RAJOLI GIRISAI MADHAVОценок пока нет

- Simple Equations: Free Distribution by A.P. GovernmentДокумент10 страницSimple Equations: Free Distribution by A.P. GovernmentRAJOLI GIRISAI MADHAVОценок пока нет

- Svcet Eee Course Material Unit 2Документ41 страницаSvcet Eee Course Material Unit 2RAJOLI GIRISAI MADHAVОценок пока нет

- PSOC Unit-4 2 MarksДокумент10 страницPSOC Unit-4 2 MarksRAJOLI GIRISAI MADHAVОценок пока нет

- Operations Part-2Документ11 страницOperations Part-2RAJOLI GIRISAI MADHAVОценок пока нет

- Psa Question PapersДокумент17 страницPsa Question PapersRAJOLI GIRISAI MADHAVОценок пока нет

- PSOC UNIT-2 2marksДокумент3 страницыPSOC UNIT-2 2marksRAJOLI GIRISAI MADHAVОценок пока нет

- Ldica Objective..Unit WiseДокумент5 страницLdica Objective..Unit WiseRAJOLI GIRISAI MADHAVОценок пока нет

- PSOC Unit-1 2 MarksДокумент3 страницыPSOC Unit-1 2 MarksRAJOLI GIRISAI MADHAVОценок пока нет

- Index: Sl. No. NO. Date of Proposal Policy Number Life Proposed Contact Number Basic Sum AssuredДокумент4 страницыIndex: Sl. No. NO. Date of Proposal Policy Number Life Proposed Contact Number Basic Sum AssuredRAJOLI GIRISAI MADHAVОценок пока нет

- 2 Marks Ldica NotesДокумент8 страниц2 Marks Ldica NotesRAJOLI GIRISAI MADHAV100% (2)

- How It Works: Electricity GenerationДокумент16 страницHow It Works: Electricity GenerationRAJOLI GIRISAI MADHAVОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Aashtoware Darwin ® Pavement Design and Analysis SystemДокумент5 страницAashtoware Darwin ® Pavement Design and Analysis SystemMarcelinoОценок пока нет

- Procedure For Realdisp4Документ5 страницProcedure For Realdisp4ridhwan wahyudiОценок пока нет

- Compal - La-9861p - r1-38068.0 - Satellite c45 - Schematics PDFДокумент57 страницCompal - La-9861p - r1-38068.0 - Satellite c45 - Schematics PDFLuis Alberto ArizaОценок пока нет

- Audacity: Free Open Source Audio Recording and Editing SoftwareДокумент26 страницAudacity: Free Open Source Audio Recording and Editing SoftwareJune Mae Roque Budaden100% (2)

- Oracle® Applications - Installation Guide R12.1.1Документ150 страницOracle® Applications - Installation Guide R12.1.1abbasbajwaОценок пока нет

- DS Imager IntenseДокумент2 страницыDS Imager Intensesainipan91Оценок пока нет

- Questions and AnswersДокумент9 страницQuestions and AnswersAnfinvargheseОценок пока нет

- NG Book 2 Table of ContentsДокумент3 страницыNG Book 2 Table of ContentsAswin GirmajiОценок пока нет

- Ethical HackingДокумент24 страницыEthical HackingGANYA JOKERОценок пока нет

- Lab 9.1.5b Trunking With 802.1q: ObjectiveДокумент8 страницLab 9.1.5b Trunking With 802.1q: ObjectiveShamsol AriffinОценок пока нет

- InfrastructureДокумент6 страницInfrastructureArchana RajОценок пока нет

- en KIX4OTRSДокумент82 страницыen KIX4OTRSbeachboy_samОценок пока нет

- CSE Ethical HackingДокумент26 страницCSE Ethical HackingVinod Gupta0% (1)

- Siemens MC45 (DIL/NetPC DNP/9200 - microHOWTO)Документ2 страницыSiemens MC45 (DIL/NetPC DNP/9200 - microHOWTO)AlexОценок пока нет

- An Efficient Hardware Accelerator For Structured Sparse Convolutional Neural Networks On FpgasДокумент12 страницAn Efficient Hardware Accelerator For Structured Sparse Convolutional Neural Networks On FpgasSelva KumarОценок пока нет

- Terminals Guide For WiMAX Macro BSДокумент35 страницTerminals Guide For WiMAX Macro BSRamiz RzaogluОценок пока нет

- Palo Alto CLi Cheat SheetДокумент12 страницPalo Alto CLi Cheat SheetSharib NomaniОценок пока нет

- Charles Dowd - Jazz, Rock and Latin Sourcebook PDFДокумент64 страницыCharles Dowd - Jazz, Rock and Latin Sourcebook PDFRoy Verges100% (5)

- Intensive VSAT Field and WIFI Systems EngineeringДокумент12 страницIntensive VSAT Field and WIFI Systems EngineeringImran SadiqОценок пока нет

- Oracle RAC InstructionsДокумент18 страницOracle RAC Instructionsmlazar20009720100% (1)

- Detailed Lesson Plan For Demo TomorrowДокумент8 страницDetailed Lesson Plan For Demo TomorrowEllioliza Herrera TownsendОценок пока нет

- Apache Spark With JavaДокумент209 страницApache Spark With Javavenkatraji719568Оценок пока нет

- Online Shopping SynopsisДокумент30 страницOnline Shopping SynopsisAditya Srivastava76% (172)

- Vlsi Lab Manual 17ecl77 2020 SaitДокумент157 страницVlsi Lab Manual 17ecl77 2020 Saitsuraj jha100% (1)

- 3FE-64746-AAAA-TQZZA-02-NANT-E Unit Data SheetДокумент12 страниц3FE-64746-AAAA-TQZZA-02-NANT-E Unit Data SheetMatheus AcacioОценок пока нет

- 200-120 CCNA Exam TopicsДокумент6 страниц200-120 CCNA Exam Topicsrudycarlos4129Оценок пока нет

- Uploading, Sharing, and Image Hosting PlatformsДокумент12 страницUploading, Sharing, and Image Hosting Platformsmarry janeОценок пока нет

- Installing and Configuring The Microsoft IIS Plug-InДокумент16 страницInstalling and Configuring The Microsoft IIS Plug-Inrameshk2000Оценок пока нет

- CSE 219 Computer Science III: Code ProfilingДокумент25 страницCSE 219 Computer Science III: Code ProfilingZeb AslamОценок пока нет

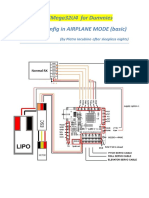

- Nanowii Atmega32U4 For Dummies - How To Config in Airplane Mode (Basic)Документ6 страницNanowii Atmega32U4 For Dummies - How To Config in Airplane Mode (Basic)zileОценок пока нет