Академический Документы

Профессиональный Документы

Культура Документы

VLSI

Загружено:

Sanjana Pulapa0 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров1 страницаVLSI notes

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документVLSI notes

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров1 страницаVLSI

Загружено:

Sanjana PulapaVLSI notes

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 1

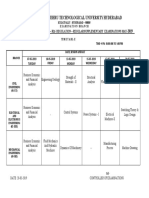

Illustrate about different steps involved in the IC fabrication briefly

Evaluate the process steps a) Oxidation b) Diffusion c) Lithography

What are the additional two layers in Bi-CMOS technology compared to others

With neat sketches explain CMOS fabrication using n-well process.

Determine different steps involved in the IC fabrication briefly

Elucidate about processing steps in fabrication of NMOS technology with neat Sketches

Construct the processing steps in fabrication of PMOS technology with neat sketches

Evaluate how the BiCMOS inverter performance can be improved

Discuss design rule for wires (orbit 2µm CMOS)

Find gm and RDS for n- channel transistor with Vgs=1.5v, Vtn=0.9v, W/L=20, Cox=92µA / V2 and VDS=Veff + 0.5V and λ=90.3X10-3V-1

nMOS transistor is operated in triode region with following parameters: Vgs=4v,Vtn=1V,Vds=2v,W/L=100,µnCox=-90µ A/V2.Find Id and Rds

Determine pull-up to pull-down ratio of an n MOS inverter driven through one or more pass transistors

Draw the stick diagram and layout for the following function f=(A+B)C by using NMOS

Derive the relation between Ids and Vds of MOSFET

Demonstrate the different types of design rules and give some examples

What is a stick diagram? Draw the stick diagram and layout for a CMOS inverter

For NMOS Inverter driven by another NMOS inverter, derive the expression for Zpu/Zpd ratio?

Illustrate in detail Enhancement mode transistor Action

With neat sketches, explain the transfer characteristics of a CMOS inverter

Determine pull-up to pull-down ratio of an n MOS inverter driven through one or more pass transistors

Design a stick diagram and layout for two input CMOS NAND gate.

Derive the expression for propagation delay τD in the case of cascaded pass transistors

Draw the stick diagram and layout for the following function Y= (A+B+C)’

Derive the expressions for Rise-time (τR) and Fall-Time (τF) in the case of CMOS inverters

Define threshold voltage and explain the terms.

Explain the relation for Cg, K, Co, β.

Identify the expression for τSD in the case of a MOSFET

Draw the stick diagram for 2 input EX-OR and 2 input Ex-Nor

Appraise the word s fan-in and fan-out. Explain their effects on propagation delay

Formulate figure of merit and transconductance?

Sketch µm design rule for diffusion

Define Stick Diagram. Draw the stick digram for PMOS inverter

What is pass transistor?

What is the need of Transistor threshold voltage.

Distinguish between NMOS and PMOS.

List the various color coding used in stick diagram.

List the types of design rules

What is the full form of ULSI & GSI

What are the types in CMOS? Define BI-CMOS

Sketch the aspects of λ-based design rules for Diffusion

Classify the various types of IC packages. List the advantages of IC

List out Alternate Gate Circuits types

Define Rise time. Fall time. Delay time

Sketch the stick diagram for 2 i/p nMOS nor gate.

write Micro meter based design Rules

What is the Need of scaling of MOS circuits

State the λ based design rules

Sketch stick diagram for NMOS inverter

Draw the circuit three input And Or Invert CMOS gate.

State Moore’s law. Write 2 steps in VLSI Design flow

What are the steps involved in twin - tub process

Sketch NMOS inverter circuit, Draw the layout diagram for NMOS inverter.

Why scaling is required. State the different types of CMOS process

What is the difference between ENMOS and DNMOS

The rate of oxidation depends on. -------, ---------------is the process of dividing a large and complex system into smaller modules.

The process of introducing high energy charged particles into the substrate is called----

Advantage of IC technology is: --------------------.

what are the approaches for CMOS fabrication--------------------.

The layers of MOS technology are isolated from each other by--------------------.

The Oxidation in IC technology refers to chemical process of reaction of --------------------.

Using HDL, the description of hardware is carried out in ---------------- Level.

-------------------- is the process of checking the design’s functional correctness.

Technology is used for I/O and driver circuits while-------------------technology is used for logic only-.

The process of introducing high energy charged particles into the substrate is called.-----

-------------------- is due to the leakage current drawn from the power supply.

The process of transferring patterns of geometric shapes in a mask to a layer of radiation

The total amplitude level of the signal is divided into fixed no. of amplitude levels is called ----------

--------------------is the process of dividing a large and complex system into smaller modules.

The process of introducing high energy charged particles into the substrate is called---------

The process of transferring patterns of geometric shapes in a mask to a layer of radiation sensitive material for covering surface of semiconductor

wafer is called--------------------. cascade arrangement of transmission gate and inverter is called--------------------.

-------------------- are the approaches for CMOS fabrication.

Transistors are fabricated within the regions called---------. The Fermi potential value for typical p-type silicon substrates is----------

When Polysilicon thinox layers cross each other what are formed--------------------.

Standard unit of capacitance is defined as gate to channel capacitance of MOS transistor having--------------------.

Non saturation mode of MOS transistor is-------. --------Technology is used for I/O and driver circuits while -----technology is used for

logic only. saturation mode of MOS transistor is--------------------.

The layers of MOS technology are isolated from each other by -----. In 2µm CMOS design rules for BICMOSp-base the color is ------------.

A stick diagram is Schematic representation of a circuit at--------------------.

The basic idea of CMOS scaling is to reduce--------------------of the CMOS transistors

In BiCMOS inverters, bipolar transistors functionality is to --------------------.

The pull-up to pull-down ratio for an inverter driven using one or more pass transistors is-------------------

The pull-up to pull-down ratio for an inverter driven another inverter is---------------

------------------- due to the leakage current drawn from the power supply

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Tunnel ConstructionДокумент171 страницаTunnel ConstructionBhaskar Reddy94% (16)

- Chapter 4 Newton's Laws of Motion Fundamentals of Physics: A Senior CourseДокумент29 страницChapter 4 Newton's Laws of Motion Fundamentals of Physics: A Senior CourseMichael Carnovale0% (1)

- Befa Unit2Документ35 страницBefa Unit2Sanjana PulapaОценок пока нет

- SSB ModulationДокумент66 страницSSB ModulationSanjana PulapaОценок пока нет

- Emi 1Документ36 страницEmi 1Sanjana PulapaОценок пока нет

- Emi All in One Key Points and Important QuestiinsДокумент42 страницыEmi All in One Key Points and Important QuestiinsSanjana PulapaОценок пока нет

- B.tech 2-2 R16 TimetableДокумент5 страницB.tech 2-2 R16 Timetableganesh dragoОценок пока нет

- UNIT-5: Realization of Logic Gates and Sampling GatesДокумент11 страницUNIT-5: Realization of Logic Gates and Sampling GatesSanjana PulapaОценок пока нет

- Befa Unit Ii Study MaterialsДокумент28 страницBefa Unit Ii Study MaterialsSanjana PulapaОценок пока нет

- Befa Unit 1Документ22 страницыBefa Unit 1Sanjana PulapaОценок пока нет

- Befa Unit2Документ35 страницBefa Unit2Sanjana PulapaОценок пока нет

- Time Base GeneratorsДокумент22 страницыTime Base GeneratorsSanjana PulapaОценок пока нет

- Unit - 2 Real Time Applications: This Chapter Deals With Non Linear Wave Shaping CircuitsДокумент1 страницаUnit - 2 Real Time Applications: This Chapter Deals With Non Linear Wave Shaping CircuitsSanjana PulapaОценок пока нет

- Ac Important Questions For Model ExamДокумент2 страницыAc Important Questions For Model ExamSanjana PulapaОценок пока нет

- UNIT 3 Real Time Application FormatДокумент2 страницыUNIT 3 Real Time Application FormatSanjana PulapaОценок пока нет

- Multivibrator Circuit AnalysisДокумент41 страницаMultivibrator Circuit AnalysisSanjana PulapaОценок пока нет

- Noise in Analog Communication SystemsДокумент32 страницыNoise in Analog Communication SystemsSanjana PulapaОценок пока нет

- Theory QTNS For Internal-Ii - 2017Документ1 страницаTheory QTNS For Internal-Ii - 2017Sanjana PulapaОценок пока нет

- Document PDFДокумент52 страницыDocument PDFM S TejaОценок пока нет

- Ac Notes - Unit-IДокумент61 страницаAc Notes - Unit-ISanjana PulapaОценок пока нет

- MUltiple Integrals Introduction As UNIT-III For I MidДокумент2 страницыMUltiple Integrals Introduction As UNIT-III For I MidSanjana PulapaОценок пока нет

- LT and Special Functions (UNIT II)Документ1 страницаLT and Special Functions (UNIT II)Sanjana PulapaОценок пока нет

- Angle ModulationДокумент34 страницыAngle ModulationSanjana PulapaОценок пока нет

- Ac Notes - Unit-IДокумент61 страницаAc Notes - Unit-ISanjana PulapaОценок пока нет

- ST Unit 1Документ188 страницST Unit 1Sanjana PulapaОценок пока нет

- VECTOR Calculus Unit IV VДокумент6 страницVECTOR Calculus Unit IV VSanjana PulapaОценок пока нет

- ARM: A Concise Overview of Advanced RISC MachinesДокумент33 страницыARM: A Concise Overview of Advanced RISC MachinesSanjana PulapaОценок пока нет

- Cs Unit 5Документ101 страницаCs Unit 5Sanjana PulapaОценок пока нет

- Lecture Notes: Digital Logic DesignДокумент66 страницLecture Notes: Digital Logic DesignJyoti GroverОценок пока нет

- Differential Global Positioning System: Marri Laxman Reddy Institute of Technology and ManagementДокумент26 страницDifferential Global Positioning System: Marri Laxman Reddy Institute of Technology and ManagementSanjana PulapaОценок пока нет

- R18B TECHECEIIYearSyllabusДокумент29 страницR18B TECHECEIIYearSyllabusShiv StreamingОценок пока нет

- Differential Global Positioning System: Marri Laxman Reddy Institute of Technology and ManagementДокумент11 страницDifferential Global Positioning System: Marri Laxman Reddy Institute of Technology and ManagementSanjana PulapaОценок пока нет

- Turbidites and Foreland Basins An Apenninic PerspectiveДокумент6 страницTurbidites and Foreland Basins An Apenninic PerspectivekoloshrabeaaОценок пока нет

- BEMO Roof Brochure en 2019Документ27 страницBEMO Roof Brochure en 2019Anonymous wzuyBcОценок пока нет

- Genetic Algorithms in OptimizationДокумент38 страницGenetic Algorithms in OptimizationssbhonsaleОценок пока нет

- Oxford International Aqa As Physics ph01Документ14 страницOxford International Aqa As Physics ph01Zink KobayashiОценок пока нет

- Curvas de Crecimiento MicrobianoДокумент30 страницCurvas de Crecimiento Microbianoluis villamarinОценок пока нет

- Thermodynamics of Phase TransformationДокумент20 страницThermodynamics of Phase TransformationSaiCharan Dharavath100% (1)

- Geosynthetic Institute: GRI Test Method GM19Документ12 страницGeosynthetic Institute: GRI Test Method GM19HeiderHuertaОценок пока нет

- Measure Density & Test Hooke's LawДокумент2 страницыMeasure Density & Test Hooke's LawArt Angel GingoОценок пока нет

- IRC Ammendments 2018Документ31 страницаIRC Ammendments 2018ਸੁਖਬੀਰ ਸਿੰਘ ਮਾਂਗਟ100% (1)

- 22 - Muhammad Rifky Hasan - 172112238Документ4 страницы22 - Muhammad Rifky Hasan - 172112238Rifky hasanОценок пока нет

- Respect The Unstable PDFДокумент14 страницRespect The Unstable PDFMarcelo Quispe CcachucoОценок пока нет

- Relativistic Time Dilation and The Muon ExperimentДокумент6 страницRelativistic Time Dilation and The Muon ExperimentConexão Terra PlanaОценок пока нет

- Therm6.3 10211 ValidationДокумент7 страницTherm6.3 10211 ValidationJavierОценок пока нет

- EditДокумент2 страницыEditEvey HernándezОценок пока нет

- Convolution and Frequency Response For LTI Systems: HapterДокумент9 страницConvolution and Frequency Response For LTI Systems: HapterJ. SamОценок пока нет

- Heater DetailsДокумент35 страницHeater DetailsPushkar Pandit100% (1)

- Unit & DimensionsДокумент9 страницUnit & DimensionsRandhir SinghОценок пока нет

- CHAPTER3 Groundimprovementbypreloadingandverticaldrain PDFДокумент19 страницCHAPTER3 Groundimprovementbypreloadingandverticaldrain PDFAqua OxyОценок пока нет

- 6 14D 13 PDFДокумент17 страниц6 14D 13 PDFRiyon Sanjaya IrmalОценок пока нет

- Car crushing hydraulic circuit analysisДокумент22 страницыCar crushing hydraulic circuit analysisphankhoa83100% (1)

- Bdm100 User ManualДокумент36 страницBdm100 User Manualsimon_someone217Оценок пока нет

- Table A. Equivalent Length, (L/D) of Valves and Pipe FittingsДокумент7 страницTable A. Equivalent Length, (L/D) of Valves and Pipe Fittingst_i_f_anoОценок пока нет

- Risk Assessment of Existing Bridge StructuresДокумент262 страницыRisk Assessment of Existing Bridge StructuresShadi0% (1)

- TDS PH MacTexMXL May2014Документ1 страницаTDS PH MacTexMXL May2014Catherine MagnayeОценок пока нет

- Center of Mass and The Motion of A SystemДокумент13 страницCenter of Mass and The Motion of A SystemNitin SharmaОценок пока нет

- Thermodynamics of Heating PDFДокумент19 страницThermodynamics of Heating PDFMatias MuñozОценок пока нет

- AbbrebiationДокумент8 страницAbbrebiationMahade Hasan DipuОценок пока нет

- Passive Flow Separation Control Over NACA 63018Документ1 страницаPassive Flow Separation Control Over NACA 63018miladrakhshaОценок пока нет