Академический Документы

Профессиональный Документы

Культура Документы

(ECE) /HD Examination: Se:Vleste

Загружено:

RanveerОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

(ECE) /HD Examination: Se:Vleste

Загружено:

RanveerАвторское право:

Доступные форматы

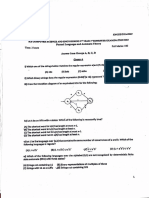

Roll No .

BE (ECE)

\HD SE:VlESTER EXAMINATION (September-2018)

F:CD-14 : Digital System Design Using VHDL/V \!rilog

fimt ·· 1· 3P, Hour.')

Max. M~rks: 15

'rHe: AH . .

questions car~, equal marks. Assume suitable missing data, if any .

I,

(1+3+l=5 )

~ Dihprenuat b · ·

- e e1ween menial delay and transport delay with the help of sunabk

example

\,, me 3 'H DL coae tor b4-bit I-ull Adder using Generate Statement in Structural

modelling

Declare ar. integer data type to create a memory of 512 bytes with 8 address lines.

ff I

(1 +1+2+ J=5)

. ' l .. l3 ··rn l .. _ :.rnd C = ··()l O''. what arc the value~ 0 1· the folk•\.\ m~

tatcr.i.t nt:-

"' & B or I JJ & C ,

11 , •.\ rnr :

.ii 1 .-\ sla :

, J .; ··: 11I 1n--

& not B

-.. \\ me a \'IiDL process that 1s equivalent to thl! fo llowing concurrent statemen'. :

\ · B 1 when ( · 1 else 132 \\ hen C - 2 else B3 when C=3 else') :

Drnv, ,-. a, erorm J 1agram to explain ··wan fo r Ons··.

1 xpi au1h()\', hlod , .')tJtcment can he useJ to remo ve dri,er for any signal.

HJ , (3+2=5)

.; DD t1Jp-1lop 1:> ~1milar w a L) nip-flo p. except that the flip-flop can change state

f_l D1 on both the nsing edge and fall ing edge of the clock input. The flip-fl op has

Jircc 1 re~c l input. R. ,md P ·()' resets the flip -fiop to Q .: ' O' independent of the

,uc.t-: 'l!milarl~ . 11 has a direct ) Cl input. S. that sets the flip -Cop to · i rnd-:p(.'nde n: cf

the clock. ,~·rite a VHDL description of a DD flip-flop .

in tht 1ollowing \' HDI. code. A. B. C & D are bit signals that are O at t1me 4ns. lf A

..:hange~ to l at nme 5ns. make a table showing the values of A. B. C & D as a

'. unction of time until time = 18ns (Include IJ. delta). indicate the times at which each

;Jrocess begms executing.

Pl : process ( A)

begin

8 '= l>. after 5 ns :

- <- P, i\fter 2 'I ~ ·

e nd process ;

P Z: prOCllSS

beg in

w:n t on R:

¢ ' '10t t);

J •·= n0t A xor B·

end pro ce ~!- ;

Вам также может понравиться

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99От EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99Оценок пока нет

- Quantu1n Optical Technologies: NameДокумент13 страницQuantu1n Optical Technologies: NameGuillermo Prol CasteloОценок пока нет

- And RC Ulls: Lowinj:R Equence ofДокумент4 страницыAnd RC Ulls: Lowinj:R Equence ofrojei mcbeanОценок пока нет

- CLL121 Equations Minor Ch1 5Документ2 страницыCLL121 Equations Minor Ch1 5jaggumeenaiitdОценок пока нет

- 6 95-Estt. (D)Документ1 страница6 95-Estt. (D)Thilakavathi RamarОценок пока нет

- Chapter1 S PDFДокумент4 страницыChapter1 S PDFkskumargieОценок пока нет

- Validate username and password with RegExДокумент10 страницValidate username and password with RegExCM5I109Aniket HiraskarОценок пока нет

- FOM Pr. 9Документ3 страницыFOM Pr. 9Shreyash BhoiteОценок пока нет

- General Instructions for Question PaperДокумент7 страницGeneral Instructions for Question PaperVaishakh VarierОценок пока нет

- PT - 09Документ7 страницPT - 09261217raghavsharmaОценок пока нет

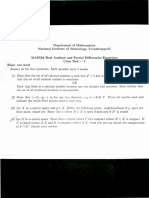

- Department of Mathematics National Institute of Technology, TiruchirappalliДокумент6 страницDepartment of Mathematics National Institute of Technology, TiruchirappalliprathikОценок пока нет

- Hollistic Exam Electrical and Computer Engineering BduДокумент6 страницHollistic Exam Electrical and Computer Engineering Bduecedcom12345100% (2)

- Principles of Computer Programming - A Mathematical ApproachДокумент688 страницPrinciples of Computer Programming - A Mathematical ApproachchesterpetersОценок пока нет

- Chapter8 SДокумент10 страницChapter8 StoshitОценок пока нет

- Experiment No 7Документ4 страницыExperiment No 7vedant patilОценок пока нет

- 5th Semester Past Papers (Final Term) - 2Документ14 страниц5th Semester Past Papers (Final Term) - 2jawad.bsee416Оценок пока нет

- ChE - Old Papers (Before 2011-12 I)Документ14 страницChE - Old Papers (Before 2011-12 I)Mukul ParasharОценок пока нет

- MA1101 2018 MidSemesterДокумент1 страницаMA1101 2018 MidSemesterCrazy ExperimentsОценок пока нет

- Civil Engineering Objective Questions PDFДокумент16 страницCivil Engineering Objective Questions PDFPra BhaОценок пока нет

- Electrical Engineering Objective Questions Part 2Документ15 страницElectrical Engineering Objective Questions Part 2Hero ArairaОценок пока нет

- Analysis: NlueДокумент16 страницAnalysis: NlueMayaОценок пока нет

- Sem 4Документ20 страницSem 4Kartik Yallappa NamdeОценок пока нет

- VLSI Interview QuestionsДокумент112 страницVLSI Interview QuestionsrAM100% (10)

- GATE2005Документ12 страницGATE2005anunay.mishra4141Оценок пока нет

- IAS Mains Civil Engineering 2004Документ15 страницIAS Mains Civil Engineering 2004rfvz6sОценок пока нет

- DSD Midsem PapersДокумент14 страницDSD Midsem PapersRanveerОценок пока нет

- HW 10Документ7 страницHW 10Dharna BhayaniОценок пока нет

- Komer Fiasco Last PageДокумент1 страницаKomer Fiasco Last PagePhoenix Program FilesОценок пока нет

- Hydraulics of Flow Regime: Chapter - 2Документ24 страницыHydraulics of Flow Regime: Chapter - 2Arnab MondalОценок пока нет

- Powell, J. David - Workman, Michael L. - Franklin, Gene F. - Solutions Manual For Digital Control of Dynamic Systems-Addison-Wesley (1998)Документ454 страницыPowell, J. David - Workman, Michael L. - Franklin, Gene F. - Solutions Manual For Digital Control of Dynamic Systems-Addison-Wesley (1998)Francisco GarciaОценок пока нет

- M Thebehae Ass1Документ5 страницM Thebehae Ass1MalefaneОценок пока нет

- PN::DR: Pe n9 (Pron Hnu-AhaanДокумент2 страницыPN::DR: Pe n9 (Pron Hnu-AhaanDodosayankОценок пока нет

- Theoretical Calculations of The Distribution of Aerodynamic Loading On A Delta WingДокумент35 страницTheoretical Calculations of The Distribution of Aerodynamic Loading On A Delta WingHarsha HarОценок пока нет

- HPL Brims 96 04Документ18 страницHPL Brims 96 04jeannotkabОценок пока нет

- Taller 2 Luis David Preciado MartínezДокумент9 страницTaller 2 Luis David Preciado MartínezLuis David PreciadoОценок пока нет

- Mechanical Engineering Paper I Thermodynamics QuestionsДокумент24 страницыMechanical Engineering Paper I Thermodynamics QuestionsMAheshОценок пока нет

- 15EC53-Verilog HDL Scheme and Solution Sunil Kumar K H PDFДокумент23 страницы15EC53-Verilog HDL Scheme and Solution Sunil Kumar K H PDFsaketОценок пока нет

- فاينل ميكانيك التربه ثالث مدني 10 11Документ4 страницыفاينل ميكانيك التربه ثالث مدني 10 11Samer al sadikОценок пока нет

- Sample Question Paper For MathssssДокумент6 страницSample Question Paper For MathssssMitali NailwalОценок пока нет

- Adobe Scan 11 Feb 2023 PDFДокумент10 страницAdobe Scan 11 Feb 2023 PDFUshaarvee GhoshОценок пока нет

- Advanced SCMethods 1Документ27 страницAdvanced SCMethods 1eros amendolaraОценок пока нет

- Alberto - Leon-Garcia 2009 Student Solutions ManualДокумент204 страницыAlberto - Leon-Garcia 2009 Student Solutions ManualPeps Peps Peps86% (7)

- Auditing Theory Multiple Choice QuestionsДокумент16 страницAuditing Theory Multiple Choice QuestionsAbigail CianoОценок пока нет

- 3.1SemPYQ - SabnamLaskar (1) - RemovedДокумент5 страниц3.1SemPYQ - SabnamLaskar (1) - Removednayakcodes143Оценок пока нет

- Adobe Scan 18 Jan 2023Документ9 страницAdobe Scan 18 Jan 2023bhargavjain2006Оценок пока нет

- Scan Apr 16, 2022Документ10 страницScan Apr 16, 2022Ashish GuptaОценок пока нет

- Scan Aug 13, 2019Документ3 страницыScan Aug 13, 2019hotboudi dolaОценок пока нет

- Ch3 Review QuestionsДокумент15 страницCh3 Review Questionsave estillerОценок пока нет

- SequencingДокумент11 страницSequencingdivya rashmiОценок пока нет

- 12th Physics 2016 March (Eng) (VisionPapers - In)Документ18 страниц12th Physics 2016 March (Eng) (VisionPapers - In)Dev Patel latest movies on my channelОценок пока нет

- AERO2358 Propeller Blade Element 2011Документ27 страницAERO2358 Propeller Blade Element 2011Daniel 'funkD' Quan100% (1)

- Commensurabilities among Lattices in PU (1,n). (AM-132), Volume 132От EverandCommensurabilities among Lattices in PU (1,n). (AM-132), Volume 132Оценок пока нет

- Tables of Coefficients for the Analysis of Triple Angular Correlations of Gamma-Rays from Aligned NucleiОт EverandTables of Coefficients for the Analysis of Triple Angular Correlations of Gamma-Rays from Aligned NucleiОценок пока нет

- Imo Sample Paper Class-6Документ2 страницыImo Sample Paper Class-6shivam verma100% (1)

- SCHEDULING ALGORITHMS - I: FCFS, SJF, RR, AND PRIORITYДокумент5 страницSCHEDULING ALGORITHMS - I: FCFS, SJF, RR, AND PRIORITYksajjОценок пока нет

- Imo Maths Olympiad Sample Question Paper 1 Class 6 PDFДокумент25 страницImo Maths Olympiad Sample Question Paper 1 Class 6 PDFRanveer100% (1)

- I SourcesДокумент5 страницI SourcesKiran KumarОценок пока нет

- Solution of Triangle (MT)Документ31 страницаSolution of Triangle (MT)mann123456789Оценок пока нет

- Registers Counters Finite State Machine (FSM) DesignДокумент23 страницыRegisters Counters Finite State Machine (FSM) DesignRanveerОценок пока нет

- Experiment No - 14: Objective - To Implement 11011 Nonoverlapping Mealy Sequence DetectorДокумент7 страницExperiment No - 14: Objective - To Implement 11011 Nonoverlapping Mealy Sequence DetectorRanveerОценок пока нет

- 23 TrafficLightControllerДокумент3 страницы23 TrafficLightControllerKishore Kumar100% (1)

- Research Design and Methodology ChapterДокумент10 страницResearch Design and Methodology ChapterShefali Aggarwal NeemaОценок пока нет

- Questions Mathematics Workbook-8 Matrices Determinants Properties of Triangle (2020) PDFДокумент102 страницыQuestions Mathematics Workbook-8 Matrices Determinants Properties of Triangle (2020) PDFRanveerОценок пока нет

- Basics Experimental Design GuideДокумент2 страницыBasics Experimental Design GuideRachel Baltazar VitancolОценок пока нет

- DSD Midsem PapersДокумент14 страницDSD Midsem PapersRanveerОценок пока нет

- Dice Game Chap 22: Control - VHDДокумент2 страницыDice Game Chap 22: Control - VHDRanveerОценок пока нет

- Chapter-1 Relation and FunctionsДокумент17 страницChapter-1 Relation and FunctionsPrateek ChattopadhyayОценок пока нет

- 7 - BTS - (12th) - JEE Adv. (Paper-II) - 29-11-2015 - AllДокумент15 страниц7 - BTS - (12th) - JEE Adv. (Paper-II) - 29-11-2015 - AllRanveerОценок пока нет

- NewMicrosoftOfficeExcelWorksheet2 Xlsx-Sheet1 PDFДокумент1 страницаNewMicrosoftOfficeExcelWorksheet2 Xlsx-Sheet1 PDFRanveerОценок пока нет

- 1 FTS 18-05-2015 Results (Pitampura)Документ8 страниц1 FTS 18-05-2015 Results (Pitampura)RanveerОценок пока нет

- 7th Advance ClassesДокумент3 страницы7th Advance ClassesRanveerОценок пока нет

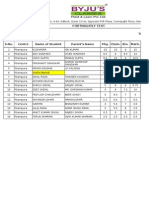

- Fortnightly Test: Fts - 03: Byju'S Classes: 1Документ10 страницFortnightly Test: Fts - 03: Byju'S Classes: 1RanveerОценок пока нет

- NCДокумент2 страницыNCRanveerОценок пока нет

- New Text DocumentДокумент29 страницNew Text DocumentRanveerОценок пока нет

- 2 BPT (11th) Vidhu & Shashank ShekharДокумент4 страницы2 BPT (11th) Vidhu & Shashank ShekharRanveerОценок пока нет

- Fortnightly Test: Fts - 03: Byju'S Classes: 1Документ10 страницFortnightly Test: Fts - 03: Byju'S Classes: 1RanveerОценок пока нет

- DiffeДокумент10 страницDiffeRanveerОценок пока нет

- Fortnightly Test: Fts - 03: Byju'S Classes: 1Документ10 страницFortnightly Test: Fts - 03: Byju'S Classes: 1RanveerОценок пока нет

- Capacitor plates separation effect on voltmeter readingДокумент4 страницыCapacitor plates separation effect on voltmeter readingRanveerОценок пока нет

- Fortnightly Test: Fts - 02: Byju'S Classes: 1Документ10 страницFortnightly Test: Fts - 02: Byju'S Classes: 1RanveerОценок пока нет

- Sbu MailДокумент4 страницыSbu MailRanveerОценок пока нет

- B Tech+degree CompressedДокумент1 страницаB Tech+degree CompressedRanveerОценок пока нет

- Kooltherm PipeДокумент8 страницKooltherm Pipenaseema1Оценок пока нет

- Airfix 2011 CatalogueДокумент132 страницыAirfix 2011 CatalogueGordon Sorensen0% (1)

- Philippine Mango Seed Oil: An Untapped ResourceДокумент8 страницPhilippine Mango Seed Oil: An Untapped ResourceFrancis Peñaflor0% (1)

- Which Delivery Method Is Best Suitable For Your Construction Project?Документ13 страницWhich Delivery Method Is Best Suitable For Your Construction Project?H-Tex EnterprisesОценок пока нет

- Right To Resist Unlawful ArrestДокумент1 страницаRight To Resist Unlawful ArrestThoth AtlanteanОценок пока нет

- Outdoor Composting Guide 06339 FДокумент9 страницOutdoor Composting Guide 06339 FAdjgnf AAОценок пока нет

- GFRDДокумент9 страницGFRDLalit NagarОценок пока нет

- 2011 REV SAE Suspension Kiszco PDFДокумент112 страниц2011 REV SAE Suspension Kiszco PDFRushik KudaleОценок пока нет

- Family health assessment nursing problemsДокумент8 страницFamily health assessment nursing problemsMari MazОценок пока нет

- Kj1010-6804-Man604-Man205 - Chapter 7Документ16 страницKj1010-6804-Man604-Man205 - Chapter 7ghalibОценок пока нет

- Adobe Photoshop 9 Cs2 Serial + Activation Number & Autorization Code AДокумент1 страницаAdobe Photoshop 9 Cs2 Serial + Activation Number & Autorization Code ARd Fgt36% (22)

- Spec 2 - Activity 08Документ6 страницSpec 2 - Activity 08AlvinTRectoОценок пока нет

- Practice Questions & Answers: Made With by SawzeeyyДокумент141 страницаPractice Questions & Answers: Made With by SawzeeyyPhake CodedОценок пока нет

- Memo in Motion For ContemptДокумент118 страницMemo in Motion For ContemptMark SternОценок пока нет

- 91 SOC Interview Question BankДокумент3 страницы91 SOC Interview Question Bankeswar kumarОценок пока нет

- Newcomb Theodore MДокумент20 страницNewcomb Theodore MBang Ahmad UstuhriОценок пока нет

- 38-St. Luke - S vs. SanchezДокумент25 страниц38-St. Luke - S vs. SanchezFatzie MendozaОценок пока нет

- Grand Viva Question For Ece StudentДокумент17 страницGrand Viva Question For Ece Studentapi-35904739086% (7)

- AAFA Webinar Intertek Jan 2012 V5Документ29 страницAAFA Webinar Intertek Jan 2012 V5rabiulfОценок пока нет

- CRM Chapter 3 Builds Customer RelationshipsДокумент45 страницCRM Chapter 3 Builds Customer RelationshipsPriya Datta100% (1)

- Culture GuideДокумент44 страницыCulture GuideLeonardo TamburusОценок пока нет

- How To Google Like A Pro-10 Tips For More Effective GooglingДокумент10 страницHow To Google Like A Pro-10 Tips For More Effective GooglingMinh Dang HoangОценок пока нет

- Manual Circulação Forçada PT2008Документ52 страницыManual Circulação Forçada PT2008Nuno BaltazarОценок пока нет

- Daftar Pustaka Marketing ResearchДокумент2 страницыDaftar Pustaka Marketing ResearchRiyan SaputraОценок пока нет

- SM 2021 MBA Assignment Forecasting InstructionsДокумент3 страницыSM 2021 MBA Assignment Forecasting InstructionsAmit Anand KumarОценок пока нет

- All India Corporate Photography Contest Promotes Workplace ArtДокумент3 страницыAll India Corporate Photography Contest Promotes Workplace Artharish haridasОценок пока нет

- Model 200-30A200P-31-21A Solenoid ValveДокумент4 страницыModel 200-30A200P-31-21A Solenoid Valveemuno008Оценок пока нет

- CIS2103-202220-Group Project - FinalДокумент13 страницCIS2103-202220-Group Project - FinalMd. HedaitullahОценок пока нет

- Capital Asset Pricing ModelДокумент11 страницCapital Asset Pricing ModelrichaОценок пока нет

- Application For Freshman Admission - PDF UA & PДокумент4 страницыApplication For Freshman Admission - PDF UA & PVanezza June DuranОценок пока нет