Академический Документы

Профессиональный Документы

Культура Документы

Dica Lab Manual PDF

Загружено:

Ruchithareddy MandaИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Dica Lab Manual PDF

Загружено:

Ruchithareddy MandaАвторское право:

Доступные форматы

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

DEPARTMENT OF

ELECTRONICS & COMMUNICATION ENGINEERING

LABORATORY MANUAL

FOR

DIGITAL IC APPLICATIONS LAB

III B.Tech. ECE - I – Sem

Prepared by

P.MAHENDER

Assistant Professor

Department of Electronics and Communication Engineering

ANURAG COLLEGE OF ENGINEERING

(Approved by AICTE, New Delhi & Affiliated to JNTU-HYD)

AUSHAPUR (V), GHATKESAR (M), MEDCHAL.DIST, T.S.501301.

DIGITAL IC APPLICATIONS LAB MANUAL Page 1

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

ANURAG COLLEGE OF ENGINEERING

AUSHAPUR(V),GHATKESAR(M),MEDCHAL(DIST)-501301

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERING

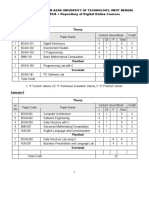

DIGITAL IC APPLICATIONS LAB

B.Tech. III Year I Sem. LTPC

Course Code: EC506PC 0032

Note:

• To perform any twelve experiments

• Verify the functionality of the IC in the given application.

Design and Implementation of:

1. Design a 16 x 4 priority encoder using two 8 x 3 priority encoder.

2. Design a 16 bit comparator using 4 bit Comparators.

3. Design a model to 53 counter using two decade counters.

4. Design a 450 KHz clock using NAND / NOR gates.

5. Design a 4 bit pseudo random sequence generator using 4 – bit ring counter.

6. Design a 16 x 1 multiplexer using 8 x 1 multiplexer.

7. Design a 16 bit Adder / Subtractor using 4 – bit Adder / Subtractor IC’s

8. Plot the transform Characteristics of 74H, LS, HS series IC’s.

9. Design a 4 – bit Gray to Binary and Binary to Gray Converter.

10. Design a two Digit 7 segment display unit using this display the Mod counter output

of experiment 3.

11. Design an 8 bit parallel load and serial out shift register using two 4 bit shift register.

12. Design an 8 bit Serial in and serial out shift register using two 4 bit shift register.

13. Design a Ring counter and Twisted ring counter using a 4-bit shift register

14. Design a 4 digit hex counter using synchronous one digit hex counters.

15. Design a 4 digit hex counter using Asynchronous one digit hex counters.

DIGITAL IC APPLICATIONS LAB MANUAL Page 2

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

ANURAG COLLEGE OF ENGINEERING

AUSHAPUR(V),GHATKESAR(M),MEDCHAL(DIST)-501301

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERING

DIGITAL IC APPLICATIONS LAB

LIST OF THE EXPERIMENTS

Name of the experiment Page No.

1. Design a 16 x 4 priority encoder using two 8 x 3 priority encoder. 4-8

2. Design a 16 bit comparator using 4 bit Comparators. 9-14

3. Design a model to 53 counter using two decade counters. 15-19

4. Design a 450 KHz clock using NAND / NOR gates. 20-23

5. Design a 4 bit pseudo random sequence generator using 4 – bit ring counter. 24-26

6. Design a 16 x 1 multiplexer using 8 x 1 multiplexer. 27-31

7. Design a 16 bit Adder / Subtractor using 4 – bit Adder / Subtractor IC’s 32-35

8. Plot the transform Characteristics of 74H, LS, HS series IC’s. 36-40

9. Design a 4 – bit Gray to Binary and Binary to Gray Converter. 41-44

10. Design a two Digit 7 segment display unit using this display the Mod counter

output of experiment 3. 45-49

11. Design an 8 bit parallel load and serial out shift register using two 4 bit

shift register. 50-55

12. Design an 8 bit Serial in and serial out shift register using two 4 bit shift register. 56-61

13. Design a Ring counter and Twisted ring counter using a 4-bit shift register 62-66

14. Design a 4 digit hex counter using synchronous one digit hex counters. 67-70

15. Design a 4 digit hex counter using Asynchronous one digit hex counters. 71-74

DIGITAL IC APPLICATIONS LAB MANUAL Page 3

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-1

DESIGN A 16×4 PRIORITY ENCODER USING TWO 8×3

PRIORITY ENCODER

AIM: To verify the truth table of 16x4 Priority Encoder.

EQUIPMENT REQUIRED: 1. 16x4 Priority encoder trainer kit.

2. Patch Cards.

3. Power Supply.

THEORY:

A priority encoder is a circuit or algorithm that compresses multiple binary inputs into a

smaller number of outputs. The output of a priority encoder is the binary representation of the original

number starting from zero of the most significant input bit. They are often used to control interrupt

requests by acting on the highest priority encoder.

If two or more inputs are given at the same time, the input having the highest priority will

take precedence. An example of a single bit 4 to 2 encoder , where highest-priority inputs are to the

left and "x" indicates an irrelevant value - i.e. any input value there yields the same output since it is

superseded by higher-priority input. The output V indicates if the input is valid.

Priority encoders can be easily connected in arrays to make larger encoders, such as one 16-to-

4 encoder made from six 4-to-2 priority encoders - four 4-to-2 encoders having the signal source

connected to their inputs, and the two remaining encoders take the output of the first four as input. The

priority encoder is an improvement on a simple encoder circuit, in terms of handling all possible

input configurations.

A simple encoder circuit is a one-hot to binary converter. That is, if there are 2n input lines, and

at most only one of them will ever be high, the binary code of this 'hot' line is produced on the n-bit

output lines.

The Priority Encoder solves the problems mentioned above by allocating a priority level to

each input. The priority encoders output corresponds to the currently active input which has the

highest priority. So when an input with a higher priority is present, all other inputs with a lower

priority will be ignored.

DIGITAL IC APPLICATIONS LAB MANUAL Page 4

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PIN DIAGRAM:

BLOCK DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 5

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

TRUTH TABLE:

Encoder Data (Active Low):

Inputs Outputs

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EI GS 3 2 1 0

X X X X X X X X X X X X X X X X H H H H H H

L L L L L L L L L L L L L L L L L L L L L L

L L L L L L L L L L L L L L L H L L L L L L

L L L L L L L L L L L L L L H H L L L L L H

L L L L L L L L L L L L L H H H L L L L H L

L L L L L L L L L L L L H H H H L L L L H H

L L L L L L L L L L L H H H H H L L L H L L

L L L L L L L L L L H H H H H H L L L H L H

L L L L L L L L L H H H H H H H L L L H H L

L L L L L L L L H H H H H H H H L L L H H H

L L L L L L L H H H H H H H H H L L H L L L

L L L L L L H H H H H H H H H H L L H L L H

L L L L L H H H H H H H H H H H L L H L H L

L L L L H H H H H H H H H H H H L L H L H H

L L L H H H H H H H H H H H H H L L H H L L

L L H H H H H H H H H H H H H H L L H H L H

L H H H H H H H H H H H H H H H L L H H H L

H H H H H H H H H H H H H H H H L L H H H H

DIGITAL IC APPLICATIONS LAB MANUAL Page 6

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE: (Active Low)

1. Make Connections as per the above Circuit Diagram.

2. 0 to 15 Inputs are connected to Inputs Switches.

3. Connect EI (Pin no. 5) of 1st Encoder to E0 (Pin no.15) of 2nd Encoder.

4. Connect A0, A1, A2 (Pin No’s 9,7, 6) of 1st Encoder to Inputs of Three AND (74LS08) Gate.

5. Connect A0, A1, A2 (Pin no’s 9, 7, 6) of 2nd Encoder to Inputs of Three AND (74LS08) Gate.

6. Connect GS (Pin no.14) of Both Encoders to the Input of Fourth AND (74LS08) Gate.

7. Connect Outputs of Three AND (74LS08) Gates to Connect Output Switches.

8. Connect GS (Pin no.14) of 2nd Encoder to Output Switch.

9. Give Inputs as per the Truth Table & Observe Output.

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 7

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Truth table:

Encoder Data (Active High):

Inputs Outputs

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EI GS 3 2 1 0

L L L L L L L L L L L L L L L L H L L L L L

L L L L L L L L L L L L L L L L L H H H H H

L L L L L L L L L L L L L L L H L H H H H H

L L L L L L L L L L L L L L H H L H H H H L

L L L L L L L L L L L L L H H H L H H H L H

L L L L L L L L L L L L H H H H L H H H L L

L L L L L L L L L L L H H H H H L H H L H H

L L L L L L L L L L H H H H H H L H H L H L

L L L L L L L L L H H H H H H H L H H` L L H

L L L L L L L L H H H H H H H H L H H L L L

L L L L L L L H H H H H H H H H L H L H H H

L L L L L L H H H H H H H H H H L H L H H L

L L L L L H H H H H H H H H H H L H L H L H

L L L L H H H H H H H H H H H H L H L H L L

L L L H H H H H H H H H H H H H L H L L H H

L L H H H H H H H H H H H H H H L H L L H L

L H H H H H H H H H H H H H H H L H L L L H

H H H H H H H H H H H H H H H H L H L L L L

PROCEDURE: (Active High)

1. Make Connections as per the above Circuit Diagram.

2. 0 to 15 Inputs are connected to Inputs Switches.

3. Connect EI (Pin no. 5) of 1st Encoder to E0 (Pin no.15) of 2nd Encoder.

4. Connect A0, A1, A2 (Pin no’s 9, 7, 6) of 1st Encoder to Inputs of Three NAND (74LS00) Gate.

5. Connect A0, A1, A2 (Pin no’s 9, 7, 6) of 2nd Encoder to Inputs of Three NAND (74LS00)

Gate.

6. Connect GS (Pin no.14) of Both Encoders to the Input of Fourth NAND (74LS00) Gate.

7. Connect Outputs of Three NAND (74LS00) Gates to Connect Output Switches.

8. Connect EI (Pin no.5) of 1st Encoder to Output Switch.

9. Give Inputs as per the Truth Table & Observe Output.

Results: Hence the truth table of 16x4 Priority Encoder has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 8

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-2

DESIGN A 16 BIT COMPARATOR USING 4 BIT COMPARATORS

AIM: To verify the truth table of 16-bit Comparator.

APPARATUS: 1. 16-bit comparator trainer kit.

2. Patch cords.

3. Power Supply.

THEORY:

Digital comparators actually use Exclusive-NOR gates within their design for comparing their

respective pairs of bits. When we are comparing two binary or BCD values or variables against each

other, we are comparing the “magnitude” of these values, a logic “0” against a logic “1” which is

where the term Magnitude Comparator comes from.

As well as comparing individual bits, we can design larger bit comparators by cascading

together n of these and produce a n-bit comparator just as we did for the n-bit adder in the previous

tutorial. Multi-bit comparators can be constructed to compare whole binary or BCD words to produce

an output if one word is larger, equal to or less than the other.

A very good example of this is the 4-bit Magnitude Comparator. Here, two 4-bit words

(“nibbles”) are compared to each other to produce the relevant output with one word connected to

inputs A and the other to be compared against connected to input B as shown below.

4-bit Magnitude Comparator:

DIGITAL IC APPLICATIONS LAB MANUAL Page 9

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Some commercially available digital comparators such as the TTL 74LS85 or CMOS 4063 4-

bit magnitude comparator have additional input terminals that allow more individual comparators to be

“cascaded” together to compare words larger than 4-bits with magnitude comparators of “n”-bits being

produced. These cascading inputs are connected directly to the corresponding outputs of the previous

comparator as shown to compare 8, 16 or even 32-bit words.

When comparing large binary or BCD numbers like the example above, to save time the

comparator starts by comparing the highest-order bit (MSB) first. If equality exists, A = B then it

compares the next lowest bit and so on until it reaches the lowest-order bit, (LSB). If equality still

exists then the two numbers are defined as being equal.

If inequality is found, either A > B or A < B the relationship between the two numbers is

determined and the comparison between any additional lower order bits stops. Digital Comparator are

used widely in Analogue-to-Digital converters, (ADC) and Arithmetic Logic Units, (ALU) to perform

a variety of arithmetic operations. Magnitude Comparator is a logical circuit , which compares two

signals A and B and generates three logical outputs, whether A > B, A = B, or A < B . IC 7485

is a high speed 4-bit Magnitude comparator , which compares two 4-bit words . The A = B Input

must be held high for proper compare operation.

PIN DIAGRAM :

DIGITAL IC APPLICATIONS LAB MANUAL Page 10

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

4-BIT COMPARATOR IC CIRCUIT DIAGRAM:

data inputs

A0

A1

A2

A<B

A3

cascade inputs A<B A=B circuitoutputs

A=B 7485 IC

A>B A>B

data inputs B0

B1

B2

B3

DIGITAL IC APPLICATIONS LAB MANUAL Page 11

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

A0

A1

A2

A3

B0 7485

B1

B2

B3

Cascaded inputs

A4

A5

A6

A7

B4

B5 7485

B6

B7

Cascaded inputs

A8

A9

A10

A11

7485

B8

B9

B10

B11

Cascaded inputs

A12

A13

A14 A>B

A15 7485

B12 A=B

B13

B14 A<B

B15

Circuits outputs

DIGITAL IC APPLICATIONS LAB MANUAL Page 12

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE: (4-bit Comparator)

1. Connect Inputs ( A0,A1,A2,A3,B0,B1,B2,B3) to Input Switches.

2. Connect Cascade Inputs (A<B,A>B,A=B) to Input Switches.

3. Connect Outputs (A<B,A>B,A=B) to Output Switches.

4. Observe the Truth Table.

TRUTH TABLE FOR 4-BIT COMPARATOR:

COMPARING CASCADING OUTPUTS

INPUTS INPUTS

A3,B3 A2,B2 A1,B1 A0,B0 A>B A<B A=B A>B A<B A=B

A3>B3 X X X X X X H L L

A3<B3 X X X X X X L H L

A3=B3 A2>B2 X X X X X H L L

A3=B3 A2<B2 X X X X X L H L

A3=B3 A2=B2 A1>B1 X X X X H L L

A3=B3 A2=B2 A1<B1 X X X X L H L

A3=B3 A2=B2 A1=B1 A0>B0 X X X H L L

A3=B3 A2=B2 A1=B1 A0<B0 X X X L H L

A3=B3 A2=B2 A1=B1 A0=B0 H L L H L L

A3=B3 A2=B2 A1=B1 A0=B0 L H L L H L

A3=B3 A2=B2 A1=B1 A0=B0 L L H L L H

A3=B3 A2=B2 A1=B1 A0=B0 X X H L L H

DIGITAL IC APPLICATIONS LAB MANUAL Page 13

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:(16-bit Comparator)

1. Connect Inputs ( A0,A1,A2,A3,A5,A6,A7,A8,A9,A10,A11,A12,A13,A14,A15,

B0,B1,B2,B3,B4,B5,B6,B7,B8,B9,B10,B11,B12,B13,B14,B15) to Input Switches.

2. Connect Cascade Inputs (A<B,A>B,A=B) of the LSB COMPARATOR to Input Switches.

3. Connect the 1st( LSB) comparator OUTPUTS to 2nd(LSB) comparator CASCADED inputs.

4. Connect the 2nd ( LSB) comparator OUTPUTS to 3rd (LSB) comparator CASCADED inputs.

5. Connect the 3rd ( LSB) comparator OUTPUTS to 4th(MSB) comparator CASCADED inputs.

6. Connect Outputs (A<B,A>B,A=B) of MSB COMPARATOR to Output Switches.

7. Observe the Truth Table.

TRUTH TABLE FOR 16-BIT COMPARATOR:

COMPARING CASCADING OUTPUTS

INPUTS INPUTS

A15,B15 A14,B14 …. A0,B0 A>B A<B A=B A>B A<B A=B

A15>B15 X …. X X X X H L L

A15<B15 X …. X X X X L H L

A15=B15 A14>B14 …. X X X X H L L

A15=B15 A14<B14 …. X X X X L H L

A15=B15 A14=B14 …. X X X X H L L

A15=B15 A14=B14 …. X X X X L H L

. . . . . . . . . .

. . . . . . . . . .

. . . . . . . . . .

. . . . . . . . . .

A15=B15 A14=B14 …. A0>B0 X X X H L L

A15=B15 A14=B14 …. A0<B0 X X X L H L

A15=B15 A14=B14 …. A0=B0 H L L H L L

A15=B15 A14=B14 …. A0=B0 L H L L H L

A15=B15 A14=B14 …. A0=B0 L L H L L H

A15=B15 A14=B14 …. A0=B0 X X H L L H

Result: Hence the truth table of 16- Comparator has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 14

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-3

DESIGN A MODEL TO 53 COUNTER USING TWO DECADE COUNTER

AIM: To Verify The Truth Table of Decade Counter.

EQUIPMENTS REQUIRED: 1. Decade counter trainer kits-2.

2. Patch cords.

3. IC 7421.

4. Bread Board.

5. Connecting wires.

6. Power Supply.

THEORY:

Decade counter (7490):

The IC 7490 is a decade counter, which divides input by 10 counts and provides BCD outputs

0 to 9; this is also called as decimal counter. This counter comprises of a divide by '2' and divide by '5'

counters. To use as decade counter we have to cascade divide by '2' and divide by '5'. Outputs Q0 to

Q3 are BCD outputs, inputs A and B are clock inputs to the, divide by '2' and divide by '5' counters

respectively. Ro1 and Ro2 are the reset inputs; when these are activated counter output go to 0000.

So1 and So2 are the set inputs to the counter, when these inputs are activated counter output goes to

1001.

The counters four outputs are designated by the letter symbol Q with a numeric subscript

equal to the binary weight of the corresponding bit in the BCD counter circuits code. So for example

QA, QB, QC and QD. The 74LS90 counting sequence is triggered on the negative going edge of the

clock signal, that is when the clock signal CLK goes from logic 1 (HIGH) to logic 0 (LOW).The

additional input pins R1 and R2 are counter “reset” pins while inputs S1 and S2 are “set” pins. When

connected to logic 1, the Reset inputs R1 and R2 reset the counter back to zero, 0 (0000), and when the

Set inputs S1 and S2 are connected to logic 1, they Set the counter to maximum, or 9 (1001) regardless

of the actual count number or position.

As we said before, the 74LS90 counter consists of a divide-by-2 counter and a divide-by-5

counter within the same package. Then we can use either counter to produce a divide-by-2 frequency

counter only, a divide-by-5 frequency counter only or the two together to produce our desired divide-

by-10 BCD counter. With the four flip-flops making up the divide-by-5 counter section disabled, if a

clock signal is applied to input pin 14 (CLKA) and the output taken from pin 12 (QA), we can produce

a standard divide-by-2 binary counter for use in Pin Diagram circuits as shown below

DIGITAL IC APPLICATIONS LAB MANUAL Page 15

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Pin Diagrams of 7490 IC is as below:

Four Input AND Gate IC (7421):

DIGITAL IC APPLICATIONS LAB MANUAL Page 16

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 17

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

TRUTH TABLE:

Outputs

Reset INPUTS

RESET RESET

0 0 R3 R2 QD2 QC2 QB2 QA2 QD1 QC1 QB1 QA1

(PIN 2) (PIN 3)

H H L X L L L L L L L L

H H X L L L L L L L L L

X X H H H L L H H L L H

X L X L L L L L L L L L

L X L X L L L L L L L H

L X L X L L L L L L H L

L X L X L L L L L L H H

L X L X L L L L L H L L

L X L X L L L L L H L H

L X L X L L L L L H H L

L X L X L L L L L H H H

L X L X L L L L H L L H

L X L X L L L H L L L L

L X L X COUNT

L X L X COUNT

L X L X COUNT

L X L X L H L H L L H L

H H H H L L L L L L L L

DIGITAL IC APPLICATIONS LAB MANUAL Page 18

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:

1. Short the pin3,6&7,1&12 of first counter and short the 2,6&7,1&12of second counter.

2. Connect +VCC to pin 5 of first and second of counters and shorted to the pin14 of four input AND

gate IC (7421).

3. Short the GND to 10thpin of first and second counters and 7thpin of IC7421.

4. Connect the clock pulse to the 14th pin of first counter.

5. Short the 14th pin (clock pulse) of second counter to first counter 11thpin (QD1).

6. Short the first counter 12thpin (QA1) to first pin of 7421 IC.

7. Connect the first counter 9th pin (QB1) to 2nd pin of 7421 IC.

8. Connect the 8th pin(QC2) of second counter to 4th pin of 7421 IC.

9. Connect the 12th pin (QA2) of second counter to 5th pin of 7421 IC.

10 Short the Reset pins and set pins of the both the decade counter IC's.

11. Connect the output pin (6pin) of the four input AND gate 7421 IC to shorted SET and RESET

pins.

12. Connect the output pins QA1 (12), QB1 (9), QC1 (8), QD1 (11), QA2 (12), QB2 (9), QC2 (8),

QD2 (11), of both counters to seven segment display inputs.

13. Feed the logic signals either H/L as shown in the truth table.

14. Monitor the outputs QA1, QB1, QC1, QD1, QA2, QB2, QC2, and QD2.

15. Verify the truth table.

Result: Hence the display the mod 53 counter using two decade counters has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 19

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-4

DESIGN A 450KHZ CLOCK USING NAND/NOR GATES

AIM: To design a 450 KHZ clock using NAND/NOR gates.

EQUIPMENT REQUIRED:

1. CDT KIT.

2. CRO & CRO Probes.

3. IC 7400/IC4093.

4. Connecting wires.

5. Capacitor-0.0001uF.

6. Resistor-3.5kΩ.

7. Power Supply.

THEORY:

The NAND (Not – AND) gate has an output that is normally at logic level “1” and only goes “LOW”

to logic level “0” when all of its inputs are at logic level “1”. The Logic NAND Gate is the reverse or

“Complementary” form of the AND gate.

Logic NAND Gate Equivalence

The logic or Boolean expression given for a logic NAND gate is that for Logical

addition, which is the opposite to the AND gate, and which it performs on the complements of the

inputs. The Boolean expression for a logic NAND gate is denoted by a single dot or full stop symbol,

( . ) with a line or Over line, ( ‾‾ ) over the expression to signify the NOT or logical negation of

the NAND gate giving us the Boolean expression of: A.B = Q.

Then we can define t he operation of a 2-input digital logic NAND gate as being:

“If either A or B are NOT true, then Q is true”

DIGITAL IC APPLICATIONS LAB MANUAL Page 20

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Logic NAND Gates are available using digital circuits to produce the desired logical function and is

given a symbol whose shape is that of a standard AND gate with a circle, sometimes called an

“inversion bubble” at its output to represent the NOT gate symbol with the logical operation of

the NAND gate given as.

The Boolean Expression for this 4-input logic NAND gate will therefore be: Q = A.B.C.D

The “Universal” NAND Gate:

The Logic NAND Gate is generally classed as a “Universal” gate because it is one of the most

commonly used logic gate types. NAND gates can also be used to produce any other type of logic gate

function, and in practice the NAND gate forms the basis of most practical logic circuits.

By connecting them together in various combinations the three basic gate types

of AND, OR and NOT function can be formed using only NAND‘s, for example.

Various Logic Gates: various Logic gates using only NAND Gates As well as the three common

types above, Ex-Or, Ex-Nor and standard NOR gates can be formed using just

individual NAND gates.

Commonly available digital logic NAND gate IC’s include:

TTL Logic NAND Gates

• 74LS00 Quad 2-input

• 74LS10 Triple 3-input

• 74LS20 Dual 4-input

• 74LS30 Single 8-input

CMOS Logic NAND Gates

• CD4011 Quad 2-input

• CD4023 Triple 3-input

• CD4012 Dual 4-input

DIGITAL IC APPLICATIONS LAB MANUAL Page 21

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

NAND gate: (7400/4093):

BLOCK DIAGRAM:

Voutput

DIGITAL IC APPLICATIONS LAB MANUAL Page 22

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:

1. Connect the NAND/NOR gate inputs as for circuit diagram.

2. Connect the Capacitor to input of NAND/NOR gate and with respect to the Ground.

3. Connect the Resistor feedback or parallel to the NAND/NOR gate.

4. Take the output at NAND/NOR gate output and at the ground.

5. Observe the waveform at the CRO and calculate the frequency of clock pulse.

Theoretical Calculations:-

F=450 KHz

F= 1/2πRC

Assume C=0.0001uF

R= 1/2π*450K*0.0001uF

R=3.5KΏ

EXPECTED OUTPUT:

Result: Hence the design of a 450 KHZ clock pulse using NAND/NOR gates has been verified

practically.

DIGITAL IC APPLICATIONS LAB MANUAL Page 23

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-5

DESIGN A 4 BIT PSEUDO RANDOM SEQUENCE GENERATOR

USING 4-BIT RING COUNTER

AIM: To verify the 4-bit Ring Counter.

EQUIPMENT REQUIRED:

1. 4-bit Ring Counter trainer kit.

2. Patch Cards.

3. Power Supply.

THEORY:

In the Shift register if we apply a serial data signal to the input of a serial-in to serial-out shift

register, the same sequence of data will exit from the last flip-flop in the register chain after a preset

number of clock cycles thereby acting as a sort of time delay circuit to the original signal. But what if

we were to connect the output of this shift register back to its input so that the output from the last flip-

flop, QD becomes the input of the first flip-flop, DA. We would then have a closed loop circuit that "re-

circulates" the DATA around a continuous loop for every state of its sequence, and this is the principal

operation of a Ring Counter. Then by looping the output back to the input, we can convert a standard

shift register into a ring counter. Consider the circuit below.

The synchronous Ring Counter example above is preset so that exactly one data bit

in the register is set to logic "1" with all the other bits reset to "0". To achieve this, a "CLEAR" signal

is firstly applied to all the flip-flops together in order to "RESET" their outputs to a logic "0" level and

then a "PRESET" pulse is applied to the input of the first flip-flop (FFA) before the clock pulses are

applied. This then places a single logic "1" value into the circuit of the ring counter.

So on each successive clock pulse, the counter circulates the same data bit between

the four flip-flops over and over again around the "ring" every fourth clock cycle. But in order to cycle

the data correctly around the counter we must first "load" the counter with a suitable data pattern as all

logic "0's" or all logic "1's" outputted at each clock cycle would make the ring counter invalid. This

type of data movement is called "rotation", and like the previous shift register, the effect of the

movement of the data bit from left to right through a ring counter can be presented graphically as

follows along with its timing diagram.

DIGITAL IC APPLICATIONS LAB MANUAL Page 24

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

4-bit Ring Counter:

DIGITAL IC APPLICATIONS LAB MANUAL Page 25

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:

1. Connect Input pins A,B & CLR to the input switches, CLK to the pulsar switch.

2. Connect the outputs QA, QB, QC and QD to the output switches.

3. First make the clear input high, then make both input A & B high.

4. Now give the clock pulse, for every pulse the output shifts from one flip flop to another.

5. Verify the 4-bit ring counter truth table.

TRUTH TABLE:

INPUTS OUTPUTS

A B CLK CLR QA QB QC QD

L L 0 L L L L L

X X L L L L L

H H H H L L L

H H H H H L L

H H H H H H L

H H H H H H H

H L H SHIFT LEFT WITH LOW

L H H SHIFT LEFT WITH LOW

H H L L L L L

NOTE: When you are giving the clear input high all the outputs may not become zero and hence

count continues in the same manner.

Result: Hence the truth table of 4-bit Ring Counter has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 26

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-6

DESIGN A 16:1 MULTIPLEXER USING 8:1 MULTIPLEXER

AIM: To verify the truth table of Multiplexer.

EQUIPMENT REQUIRED:

1. 16X1 MULTIPLEXER TRAINER KIT.

2. PATCH CORDS.

3. Power Supply.

THEORY:

DIGITAL IC APPLICATIONS LAB MANUAL Page 27

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PIN DIAGRAM: (74151)

\

DIGITAL IC APPLICATIONS LAB MANUAL Page 28

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 29

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

TRUTH TABLE:

INPUTS

OUT

SELECTION PUT

INPUTS FROM I’0-I’15

LINES

S S S S I I I I I I

I9 I8 I7 I6 I5 I4 I3 I2 I1 I0 Z

3 2 1 0 15 14 13 12 11 10

L L L L X X X X X X X X X X X X X X X X

L

L L L L X X X X X X X X X X X X X X X H

I0

L L L H X X X X X X X X X X X X X X H X

I1

L L H L X X X X X X X X X X X X X H X X

I2

L L H H X X X X X X X X X X X X H X X X

I3

L H L L X X X X X X X X X X X H X X X X

I4

L H L H X X X X X X X X X X H X X X X X

I5

L H H L X X X X X X X X X H X X X X X X

I6

L H H H X X X X X X X X H X X X X X X X

I7

H L L L X X X X X X X H X X X X X X X X

I8

H L L H X X X X X X H X X X X X X X X X

I9

H L H L X X X X X H X X X X X X X X X X

I10

H L H H X X X X H X X X X X X X X X X X

I11

H H L L X X X H X X X X X X X X X X X X

I12

H H L H X X H X X X X X X X X X X X X X

I13

H H H L X H X X X X X X X X X X X X X X

I14

H H H H H X X X X X X X X X X X X X X X

I15

DIGITAL IC APPLICATIONS LAB MANUAL Page 30

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:

1. Internally Connected I0(Sw1), I1(Sw2), I2(Sw3), I3(Sw4), I4(Sw5), I5(Sw6), I6(Sw7),

I7(Sw8), I8(Sw9), I9(Sw10), I10(Sw11), I11(Sw12), I12(Sw13), I13(Sw14),

I14(Sw15),I15(Sw16).

2. Connect Input terminals S2 (Sw18),S1(Sw19), S0(Sw20) from any of the Multiplexer circuit.

3. Connect Enable (E) to S3(Sw17) to input terminals as per circuit diagram.

4. Check output at Green LED (LD1) (INTERNALLY CONNECTED).

5. Verify output with given Truth Table.

Result: Hence the truth table of 16:1 Multiplexer has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 31

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 7

16 BIT ADDER/SUBTRACTOR USING 4 BIT ADDER/SUBTRACTOR

AIM:- To study and implement 16 bit adder/subtractor using 4 bit adder/ subtractor

APPARATUS:-

1) 16-bit adder/ Subtractor Trainer kit.

2) Patch chords.

3) Power supply.

Theory:-

Adders are important not only in computers but in many types of digital system in which numerical

data are processed. An understanding of the basic adder operation is fundamental to the study of digital

system. In this experiment using the 4 bit add/sub constructing the 16 bit add/sub. The IC number for 4

bit add/sub is 74LS83A. These full adders perform the addition of two 4-bit binary numbers. The sum

(∑) outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit. These

adders feature full internal look ahead across all four bits. This provides the system designer with

partial look ahead performance at the economy and reduced package count of a ripple-carry

implementation. The adder logic, including the carry, is implemented in its true form meaning that the

end-around carry can be accomplished without the need for logic or level inversion. The cascading of

the 4 bit adder we can form the 16 bit adder. The carry should be forwarded to another IC.

PIN CONFIGURATION:-

Figure (1) pin diagram of 74LS83A

DIGITAL IC APPLICATIONS LAB MANUAL Page 32

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:-

Figure(2):Cascading of 4 bit adder/subtractor

DIGITAL IC APPLICATIONS LAB MANUAL Page 33

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:-

ADDITION:-

1) Connect the A0-A15 to the logic switches provided on the trainer kit.

2) Connect the B0-B15 to the logic switches provided on the trainer kit.

3) Connect the outputs to the led indicators.

4) Connect the mode switch to the logic switches.

5) Now put the mode switch in logic ‘0’ it is indicated that addition operation performing.

6) Now give the input data using the A0-A15 and B0-B15 logic switches. Ex:-

Input data A0-A15 = 0000 0000 0000 1010

Inputdata B0-B15 = 0000 0000 0000 0101

Output 0000 0000 0000 1111

SUBTRACTION:-

1) Connect the A0-A15 to the logic switches provided on the trainer kit.

2) Connect the B0-B15 to the logic switches provided on the trainer kit.

3) Connect the outputs to the led indicators.

4) Connect the mode switch to the logic switches.

5) Now put the mode switch in logic ‘1’ it is indicated that Subtraction operation performing.

6) Now give the input data using the A0-A15 and B0-B15 logic switches.

7) To perform the subtraction operation we 1’s compliment the data of the ‘B’ input.

8) Now Add two data’s A and B when u get the result add ‘1’ to the result data.

Ex:-

Input data A0-A15 = 0000 0000 0000 1010

Input data B0-B15 = 0000 0000 0000 0101

1’s compliment i/p B data 1111 1111 1111 1010

DIGITAL IC APPLICATIONS LAB MANUAL Page 34

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

9) Now add the data input A and 1’s Complimented data B

1111 1111 1111 1

Input data A0-A15= 0000 0000 0000 1010

1’s compliment i/p B data 11111111111 1010

Output data

1 0000 0000 0000 0100

Carry bit

10) Now add the ‘1’ to the result data

1 0000 0000 0000 0100

1

Final o/p 1 0000 0000 0000 0101

11) You can perform with different data’s.

Result: Hence the 16 bit addition and subtraction is verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 35

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT -8

PLOT THE TRANSFER CHARATERSTICS OF 74H, LS, HS SERIES ICs

AIM: Plot the transfer characteristics of 74H, LS, HS series ICs.

COMPONENTS REQUIRED:-

1. 74LS04-1.

2. 74HC86-1.

3. DMM.

4. PATCH CORDS.

5. POWER SUPPLY.

6. CDT KIT.

THEORY:

74LS Series ICs

The 74LS (Low-power Schottky) family (like the original) uses TTL (Transistor-

Transistor Logic) circuitry which is fast but requires more power than later families. The

74 series is often still called the 'TTL series' even though the latest ICs do not use TTL!

74HC Series ICs

The 74HC family has High-speed CMOS circuitry, combining the speed of TTL with the

very low power consumption of the 4000 series. They are CMOS ICs with the same pin

arrangements as the older 74LS family. Note that 74HC inputs cannot be reliably driven

by 74LS outputs because the voltage ranges used for logic 0 are not quite compatible, use

74HCT instead.

74HCT Series ICs

The 74HCT family is a special version of 74HC with 74LS TTL-compatible inputs so

74HCT can be safely mixed with 74LS in the same system. In fact 74HCT can be used as

low-power direct replacements for the older 74LS ICs in most circuits. The minor

disadvantage of 74HCT is a lower immunity to noise, but this is unlikely to be a problem

in most situations.

74LS family TTL characteristics

Supply: 5V ±0.25V, it must be very smooth, a regulated supply is best. In addition

to the normal supply smoothing, a 0.1µF capacitor should be connected across the

supply near the IC to remove the 'spikes' generated as it switches state, one

capacitor is needed for every 4 ICs.

Inputs 'float' high to logic 1 if unconnected, but do not rely on this in a permanent

(soldered) circuit because the inputs may pick up electrical noise. 1mA must be

DIGITAL IC APPLICATIONS LAB MANUAL Page 36

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

drawn out to hold inputs at logic 0. In a permanent circuit it is wise to connect any

unused inputs to +Vs to ensure good immunity to noise

Outputs can sink up to 16mA (enough to light an LED), but they can source only

about 2mA. To switch larger currents you can connect a transistor.

Fan-out: one output can drive up to 10 74LS inputs, but many more 74HCT inputs.

Gate propagation time: about 10ns for a signal to travel through a gate.

Frequency: up to about 35MHz (under the right conditions).

Power consumption (of the IC itself) is a few mW.

4HC and 74HCT family characteristics

The CMOS circuitry used in the 74HC and 74HCT series ICs means that they are static

sensitive. Touching a pin while charged with static electricity (from your clothes for

example) may damage the IC. In fact most ICs in regular use are quite tolerant and

earthling your hands by touching a metal water pipe or window frame before handling

them will be adequate. ICs should be left in their protective packaging until you are ready

to use them.

➢ 74HC Supply: 2 to 6V, small fluctuations are tolerated.

➢ 74HCT Supply: 5V ±0.5V, a regulated supply is best.

➢ Inputs have very high impedance (resistance), this is good because it means they

will not affect the part of the circuit where they are connected. However, it also

means that unconnected inputs can easily pick up electrical noise and rapidly

change between high and low states in an unpredictable way. This is likely to make

the IC behave erratically and it will significantly increase the supply current. To

prevent problems all unused inputs MUST be connected to the supply (either

+Vs or 0V), this applies even if that part of the IC is not being used in the circuit!

74HC and 74HCT family characteristics

The CMOS circuitry used in the 74HC and 74HCT series ICs means that they are static

sensitive. Touching a pin while charged with static electricity (from your clothes for

example) may damage the IC. In fact most ICs in regular use are quite tolerant and

earthling your hands by touching a metal water pipe or window frame before handling

them will be adequate. ICs should be left in their protective packaging until you are ready

to use them.

➢ 74HC Supply: 2 to 6V, small fluctuations are tolerated.

➢ 74HCT Supply: 5V ±0.5V, a regulated supply is best.

DIGITAL IC APPLICATIONS LAB MANUAL Page 37

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

➢ Inputs have very high impedance (resistance), this is good because it means they

will not affect the part of the circuit where they are connected. However, it also

means that unconnected inputs can easily pick up electrical noise and rapidly

change between high and low states in an unpredictable way. This is likely to make

the IC behave erratically and it will significantly increase the supply current. To

prevent problems all unused inputs MUST be connected to the supply (either

+Vs or 0V), this applies even if that part of the IC is not being used in the circuit!

➢ Note that 74HC inputs cannot be reliably driven by 74LS outputs because the

voltage ranges used for logic 0 are not quite compatible. For reliability use 74HCT

if the system includes some 74LS ICs.

➢ Outputs can sink and source about 4mA if you wish to maintain the correct output

voltage to drive logic inputs, but if there is no need to drive any inputs the maximum

current is about 20mA. To switch larger currents you can connect a transistor.

➢ Fan-out: one output can drive many inputs (50+), except 74LS inputs because

these require a higher current and only 10 can be driven.

➢ Gate propagation time: about 10ns for a signal to travel through a gate.

➢ Frequency: up to 25MHz.

➢ Power consumption (of the IC itself) is very low, a few µW. It is much greater

at high frequencies, a few mW at 1MHz for example.

PROCEDURE:

74LS04:

1) Assemble the circuit as per the circuit on the digital IC trainer kit.

2) Switch ON the power supply.

3) Apply the input voltage = 0 and note down the output.

4) Repeat step 3 for input voltages = 1V, 2V, 3V, 4V, 5V and note down the corresponding

outputs.

74HC86:

1. Assemble the circuit as per the circuit on the digital IC trainer kit.

2. Switch ON the power supply.

3. Apply the input voltage = 0 and note down the output.

4. Repeat step 3 for input voltages = 1V, 2V, 3V, 4V, 5V and note down the corresponding

outputs.

DIGITAL IC APPLICATIONS LAB MANUAL Page 38

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM AND TRANSFER CHARACTERISTICS:

CIRCUIT DIAGRAM OF 74LS04: &

TRANSFER CHARACTERSISTICS OF 74LS04:

CIRCUIT DIAGRAM OF74HC86 TRANSFER CHARACTERSISTICS OF 74H

DIGITAL IC APPLICATIONS LAB MANUAL Page 39

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

OBSERVATIONS:

74LS04:

S.NO. VOLTAGE I/P VOLTAGE O/P

1 0V

2 1V

3 2V

4 3V

5 4V

6 5V

74HS86:

S.NO. VOLTAGE I/P VOLTAGE O/P

1 0V

2 1V

3 2V

4 3V

5 4V

6 5V

RESULT: The transfer characteristics of 74H, LS, HS series ICs are studied, observed, and

verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 40

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-9

DESIGN A 4-BIT GRAY TO BINARY AND

BINARY TO GRAY CODE CONVERTER

AIM: Observe Binary to Gray & Gray to Binary Code Conversion

.

EQUIPMENT REQUIRED: 1) Gray - binary - gray Trainer kit.

2) Patch Cords.

3) Power Supply.

THEORY:

The logical circuit which converts binary code to equivalent gray code is known

as binary to gray code converter. The gray code is a non weighted code. The successive gray

code differs in one bit position only that means it is a unit distance code. It is also referred as

cyclic code. It is not suitable for arithmetic operations. It is the most popular of the unit distance

codes. It is also a reflective code. An n-bit Gray Code can be obtained by reflecting an n-1 bit

code about an axis after 2n-1 rows, and putting the MSB of 0 above the axis and the MSB of 1

below the axis.

In gray to binary code converter, input is a multiplies gray code and output is its

equivalent binary code. Let us consider a 4 bit gray to binary code converter. To design a 4 bit

gray to binary code converter, we first have to draw a conversion table.

DIGITAL IC APPLICATIONS LAB MANUAL Page 41

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 42

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

TRUTH TABLE: BINARY TO GRAY CODE CONVERTER:

INPUTS OUTPUTS

BINARY CODE GRAY CODE

A B C D G1 G2 G3 G4

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 43

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

TRUTH TABLE FOR GRAY TO BINARY CODE CONVERTER:

INPUTS OUTPUTS

GRAY CODE BINARY CODE

A B C D B4 B3 B2 B1

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 1 0 0 1 0

0 0 1 0 0 0 1 1

0 1 1 0 0 1 0 0

0 1 1 1 0 1 0 1

0 1 0 1 0 1 1 0

0 1 0 0 0 1 1 1

1 1 0 0 1 0 0 0

1 1 0 1 1 0 0 1

1 1 1 1 1 0 1 0

1 1 1 0 1 0 1 1

1 0 1 0 1 1 0 0

1 0 1 1 1 1 0 1

1 0 0 1 1 1 1 0

1 0 0 0 1 1 1 1

PROCEDURE:

BINARY TO GRAY:

1. Connect Inputs (A, B, C, D) to Input Switches (Red LED).

2. Connect Outputs (G1, G2, G3, G4) to Output Switches (Green LED).

3. Give Binary Inputs at A, B, C, D & Observe Gray Code Outputs as per Truth Table.

GRAY TO BINARY:

1. Connect Inputs (A, B, C, D) to Input Switches (Red LED).

2. Connect Outputs (B1, B2, B3, B4) to Output Switches (Green LED).

3. Give Gray Code Inputs at A, B, C, D & Observe Binary Code Outputs as per Truth

Table.

Result: Hence the Binary to Gray & Gray to Binary Code Conversion has been verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 44

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT-10

DESIGN A TWO DIGIT 7 SEGMENT DISPLAY UNIT

USING TO DISPLAY THE MOD 53 COUNTER.

AIM:To verify the modulo to 53 counter using two digit 7 Segment Display

EQUIPMENTS REQUIRED: 1. Decade counter trainer kits-2.

2. Patch cords.

3. IC 7421 four input and gate.

4. Bread Board.

5. Connecting wires.

6. Power Supply.

THEORY:

The counters four outputs are designated by the letter symbol Q with a numeric

subscript equal to the binary weight of the corresponding bit in the BCD counter circuits code.

So for example, QA, QB, QC and QD. The 74LS90 counting sequence is triggered on the negative

going edge of the clock signal, that is when the clock signal CLK goes from logic 1 (HIGH) to

logic 0 (LOW).

The additional input pins R1 and R2 are counter “reset” pins while inputs S1 and S2 are

“set” pins. When connected to logic 1, the Reset inputs R1 and R2 reset the counter back to zero,

0 (0000), and when the Set inputs S1 and S2 are connected to logic 1, they Set the counter to

maximum, or 9 (1001) regardless of the actual count number or position.

As we said before, the 74LS90 counter consists of a divide-by-2 counter and a divide-

by-5 counter within the same package. Then we can use either counter to produce a divide-by-2

frequency counter only, a divide-by-5 frequency counter only or the two together to produce our

desired divide-by-10 BCD counter. With the four flip-flops making up the divide-by-5 counter

section disabled, if a clock signal is applied to input pin 14 (CLKA) and the output taken from

pin 12 (QA), we can produce a standard divide-by-2 binary counter for use in Pin Diagram

circuits as shown below.

7421 IC diagram:-

DIGITAL IC APPLICATIONS LAB MANUAL Page 45

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PIN DIAGRAM OF IC 7447:

PROCEDURE:

1. Connect BCD Outputs (Qa, Qb, Qc, Qd) to 7 Segment Display (A, B, C, D).

2. a,b,c,d,e,f,g Connections are Internally Connected.

3. Verify the Count Outputs 0,1,2,3,4,5,6,7,8,9.

7 SEGMENT DISPLAY:

DIGITAL IC APPLICATIONS LAB MANUAL Page 46

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

CIRCUIT DIAGRAM:

DIGITAL IC APPLICATIONS LAB MANUAL Page 47

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

TRUTH TABLE:

Reset INPUTS Outputs

RESET RESET TWO 7

0 0 R3 R2 QD2 QC2 QB2 QA2 QD1 QC1 QB1 QA1 SEGMENT

(PIN 2) (PIN 3) DISPLAY

H H L X L L L L L L L L 0 0

H H X L L L L L L L L L 0 0

X X H H H L L H H L L H 9 9

X L X L L L L L L L L L 0 0

L X L X L L L L L L L H 0 1

L X L X L L L L L L H L 0 2

L X L X L L L L L L H H 0 3

L X L X L L L L L H L L 0 4

L X L X L L L L L H L H 0 5

L X L X L L L L L H H L 0 6

L X L X L L L L L H H H 0 7

L X L X L L L L H L L L 0 8

L X L X L L L L H L L H 0 9

L X L X L L L H L L L L 1 0

L X L X COUNT

COUNT

L X L X COUNT

COUNT

L X L X COUNT

COUNT

L X L X L H L H L L H L

5 2

H H H H L L L L L L L L

0 0

DIGITAL IC APPLICATIONS LAB MANUAL Page 48

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PROCEDURE:

1. Short the pin 3, 6&7,1&12 of first counterand short the 2,6&7,1&12 of second counter.

2. Connect +VCC to pin 5 of first and second of counters and shorted to the pin 14 of four

input AND gate IC (7421).

3. Short the GND to 10th pin of first and second counters and 7th pin of IC 7421.

4. Connect the clock pulse to the 14th pin of first counter.

5. Short the 14th pin (clock pulse) of second counter to first counter 11th pin (QD1).

6. Short the first counter 12th pin (QA1) to firstpin of 7421 IC.

7. Connect the first counter 9th pin (QB1) to 2nd pin of 7421 IC .

8. Connect the 8th pin (QC2) of second counter to 4th pin of 7421 IC.

9. Connect the 12th pin(QA2) of second counter to 5th pin of 7421 IC .

10. Short the Reset pins and set pins of the both the decade counter IC's.

11. Connect the output pin(6 pin) of the four input and gate 7421 IC's to shorted SET and

RESET pins.

12. Connect the output pins QA1 (12), QB1 (9), QC1 (8), QD1 (11), QA2 (12), QB2 (9),

QC2 (8), QD2 (11), of both counters to seven segment display inputs.

13. Feed the logic signals either H/L as shown in the truth table.

14. Monitor the outputs QA1, QB1, QC1, QD1, QA2, QB2, QC2, QD2.

15. Verify the truth table.

Result: Hence the display the mod53 counter using two digits7 Segment Display has been

verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 49

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 11

8 BIT PARALLEL LOAD AND SERIAL OUT USING TWO 4 BIT SHIFT

REGISTER

Aim: - To study and implementation of 8 bit parallel load and serial out

using two 4 bit shift Register.

Apparatus:-

1) 8 bit shift register Trainer kit.

2) Patch chords.

3) Power supply.

Theory:-

A register is simply a group of flip flops that can be used to store a binary

number. A shift register is a group of flip flops connected such that the binary number can be

entered (shifted) into the register and possibly shifted out. There are two ways to shift the data

(bits in the binary number) from one place to another. The first method involves shifting the data

1 bit at a time in a serial fashion, beginning with either MSB or LSB. This technique is referred to

as serial shifting. The second method involves shifting all the data bits simultaneously and is

referred to as parallel shifting. There are two ways to shift data into a register (serial or parallel)

and similarly two ways to shift data out of the register. This leads to the construction of four

basic types of registers.This bidirectional shift register is designed to incorporate virtually all of

the features a system designer may want in a shift register; they feature parallel inputs, parallel

outputs, right- shift and left-shift serial inputs, operating-mode-control inputs, and a direct

overriding clear line. The register has four distinct modes of operation, namely:

Parallel (broadside) load Shift right (in the direction QA toward QD) Shift left (in the

direction QD toward QA) Inhibit clock (do nothing) Synchronous parallel loading is

accomplished by applying the four bits of data and taking both mode control inputs, S0 and S1,

HIGH. The data is loaded into the associated flip-flops and appear at the outputs after the

positive transition of the clock input. During loading, serial data flow is inhibited. Shift right is

accomplished synchronously with the rising edge of the clock pulse when S0 is HIGH and S1 is

LOW. Serial data for this mode is entered at the shift-right data input. When S0 is LOW and S1

is HIGH, data shifts left synchronously and new data is entered at the shift-left serial input.

DIGITAL IC APPLICATIONS LAB MANUAL Page 50

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Pin diagram (74LS194):-

DIGITAL IC APPLICATIONS LAB MANUAL Page 51

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

INTERNAL DIAGRAM OF 74194:-

DIGITAL IC APPLICATIONS LAB MANUAL Page 52

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

8 bit parallel load and serial out using two 4 bit shift register:-

Circuit Diagram:-

DIGITAL IC APPLICATIONS LAB MANUAL Page 53

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Procedure:-

1. Connect the above circuit on the trainer kit.

2. Here the selection lines of the two IC can be shorted then it can be form the S0 and S1.

3. Connect the first pin of the two IC’s then it can be form a clear then it connect to the logic

switch.

4. Short the pin number 11 of the both the IC’s then it forms a common clock line then it is

connected to the 1Hz clock generator or the pulsar switch.

5. Now connect the parallel data inputs of the first IC and the second IC to the logic switches

6. Connect the QA, QB, QC and QD of the first IC to the led’s shown in the circuit.

7. Connect the QA, QB, QC and QD of the second IC to the led’s shown in the circuit assume it

as QE, QF, QG and QH.

8. Connect the serial input of the second IC (pin7) to the logic switch put in logic‘0’.

9. Connect the 2pin of the second IC to the 12pin of the first IC.

10. Connect the 7pin of the second IC to the 15pin of the first IC.

11. Connect the parallel inputs (ABCD) first IC to the logic switches similarly connect the

Parallel inputs (ABCD) of the second IC to the logic switches and assume it as EFGH.

12. Now put the selection lines both are high that is S0=’1’ and S1=’1’ now apply the input Data.

Whatever you given it will be indicated on the led’s.

Ex:

A=1, B=0,C=0,D=0,A=0,B=0,C=0,D=0=1000 0000

1. After applying the parallel data put the S0=’1’ and S1=’0’ then the data is shifted

right side.

2. The input data serially exited at the QA you will observe that using the pulsar

switch giving a single pulse at a time.

Observe the truth table below.

DIGITAL IC APPLICATIONS LAB MANUAL Page 54

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Truth Table:

SERIA

PARALLEL OUTPUTS L

INPU TS OUTPU

T

Mode S0 S1 Clear Clock Q Q Q Q QH

A B C D E F G H A QB QC D QE QF G H

Hold 1 1 H 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

1 0 H 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

1 0 H 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

Shift 1 0 H 1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0

right 1 0 H 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

1 0 H 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

1 0 H 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

1 0 H 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1

Result: - Hence the 8 bit parallel load and serial out using two 4 bit shift Register constructed

and verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 55

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 12

8 BIT SERIAL IN AND SERIAL OUT USING TWO 4 BIT SHIFT

REGISTER

Aim: - To study and implementation of 8 bit serial in and serial out using two

4 bit shift Register.

Apparatus:-

1) B-bit shift register Trainer kit.

2) Patch chords.

3) Power supply.

Theory:-

A register is simply a group of flip flops that can be used to store a number. A

shift register is a group of flip flops connected such that the binary number can be entered

(shifted) into the register and possibly shifted out. There are two ways to shift the data (bits in

the binary number) from one place to another. The first method involves shifting the data 1 bit at

a time in a serial fashion, beginning with either MSB or LSB. This technique is referred to as

serial shifting. The second method involves shifting all the data bits simultaneously and is

referred to as parallel shifting. There are two ways to shift data into a register (serial or parallel)

and similarly two ways to shift data out of the register. This leads to the construction of four

basic types of registers.

This bidirectional shift register is designed to incorporate virtually all of the

features a system designer may want in a shift register; they feature parallel inputs, parallel

outputs, right- shift and left-shift serial inputs, operating-mode-control inputs, and a direct

overriding clear line. The register has four distinct modes of operation, namely: Parallel

(broadside) load Shift right (in the direction QA toward QD) Shift left (in the direction QD

toward QA) Inhibit clock (do nothing) Synchronous parallel loading is accomplished by applying

the four bits of data and taking both mode control inputs, S0 and S1, HIGH. The data is loaded

into the associated flip-flops and appear at the outputs after the positive transition of the clock

input. During loading, serial data flow is inhibited. Shift right is accomplished synchronously

with the rising edge of the clock pulse when S0 is HIGH and S1 is LOW. Serial data for this

mode is entered at the shift-right data input. When S0 is LOW and S1 is HIGH, data shifts left

synchronously and new data is entered at the shift-left serial input.

DIGITAL IC APPLICATIONS LAB MANUAL Page 56

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Pin diagram (74LS194):-

DIGITAL IC APPLICATIONS LAB MANUAL Page 57

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

INTERNAL DIAGRAM OF 74194:-

DIGITAL IC APPLICATIONS LAB MANUAL Page 58

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

8 bit serial in and serial out using 4-bit shift register:-

Circuit Diagram:-

Figure(2) Parallel Load and Serial out circuit

DIGITAL IC APPLICATIONS LAB MANUAL Page 59

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Procedure:-

1. Connect the above circuit on the trainer kit.

2. Here the selection lines of the two IC can be shorted then it can be form the

S0 and S1.

3. Connect the first pin of the two IC’s then it can be form a clear then it

connect to the logic switch.

4. Short the pin number 11 of the both the IC’s then it forms a common clock

line then it is Connected to the 1Hz clock generator or the pulsar switch.

5. Now connect the shift right serial input data inputs of the first IC to the

logic switches.

6. Connect the QA, QB, QC and QD of the first IC to the led’s

shown in the circuit.

7. Connect the QA, QB, QC and QD of the second IC to the led’s shown in the

circuit assume it as QE, QF, QG and QH.

8. Connect the 7pin of the first IC to the 15pin of the second IC.

9. Connect the 2pin of the second IC to the 12pin of the first IC.

10. Connect the serial input of the second IC pin7 to the logic switch.

Now put the selection lines S0=’0’ and S1=’1’ now apply the input data through

the pin7 of second IC Data serially by varying the logic switch. Whatever you

given it will be indicated on the led’s and it is exited at the top led.

Ex: Shift right serial input=1

a. The input data serially exited at the QA you

will observe that using the pulsar switch

giving a single pulse at a time.

b. Observe the truth table below.

DIGITAL IC APPLICATIONS LAB MANUAL Page 60

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Truth table:-

PARALLEL OUTPU TS SERIAL

OUTPUT

Mode

S0 S1 Clear Clock QA QB QC QD QE QF QG QH QH

Hold 1 1 H 1 0 0 0 0 0 0 0 0

1 0 H 0 1 0 0 0 0 0 0 0

1 0 H 0 0 1 0 0 0 0 0 0

Shift 1 0 H 0 0 1 1 0 0 0 0 0

right 1 0 H 0 0 0 0 1 0 0 0 0

SERIAL 1 0 H 0 0 0 0 0 1 0 0 0

INPUT 1 0 H 0 0 0 0 0 0 1 0 0

1 0 H 0 0 0 0 0 0 0 1 1

Result: - Hence the 8 bit serial in and serial out using two 4 bit shift register Constructed and

verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 61

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 13

4 BIT RING AND TWISTED RING COUNTER

Aim: - To study and implementation of 4 bit ring and twisted ring counter.

Apparatus:-

1) 4-bit ring counter Trainer kit.

2) Patch chords.

3) Power supply.

Theory:

The Ring Counter

In the previous Shift Register tutorial we saw that if we apply a serial data signal to the

input of a serial-in to serial-out shift register, the same sequence of data will exit from the last

flip-flip in the register chain after a preset number of clock cycles thereby acting as a sort of time

delay circuit to the original signal. But what if we were to connect the output of this shift register

back to its input so that the output from the last flip-flop, QD becomes the input of the first flip-

flop, DA. We would then have a closed loop circuit that "recalculates" the DATA around a

continuous loop for every state of its sequence, and this is the principal operation of a Ring

Counter. Then by looping the output back to the input, we can convert a standard shift register

into a ring counter. Consider the circuit below.

4-bit Ring and twisted Counter

DIGITAL IC APPLICATIONS LAB MANUAL Page 62

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

The synchronous Ring Counter example above, is preset so that exactly one data bit in the

register is set to logic "1" with all the other bits reset to "0". To achieve this, a "CLEAR" signal

is firstly applied to all the flip-flops together in order to "RESET" their outputs to a logic "0"

level and then a "PRESET" pulse is applied to the input of the first flip-flop (FFA) before the

clock pulses are applied. This then places a single logic "1" value into the circuit of the ring

counter. On each successive clock pulse, the counter circulates the same data bit between the

four flip-flops over and over again around the "ring" every fourth clock cycle. But in

order to cycle the data correctly around the counter we must first "load" the counter

with a suitable data pattern as all logic "0"'s or all logic "1"'s outputted at each

clock cycle would make the ring counter invalid.This type of data movement is

called "rotation", and like the previous shift register, the effect of the movement of

the data bit from left to right through a ring counter can be presented graphically

as follows along with its timing diagram:

Rotational Movement of a Ring Counter

DIGITAL IC APPLICATIONS LAB MANUAL Page 63

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Since the ring counter example shown above has four distinct states, it is also known as a

"modulo-4" or "mod-4" counter with each flip-flop output having a frequency value equal to

one-fourth or a quarter (1/4) that of the main clock frequency.The "MODULO" or "MODULUS"

of a counter is the number of states the counter counts or sequences through before repeating

itself and a ring counter can be made to output any modulo number. A "mod-n" ring counter will

require "n" number of flip-flops connected together to circulate a single data bit providing "n"

different output states. For example, a mod-8 ring counter requires eight flip-flops and a mod-16

ring counter would require sixteen flip-flops. However, as in our example above, only four of the

possible sixteen states are used, making ring counters very inefficient in terms of their output

state usage.

Twisted Ring Counter

DIGITAL IC APPLICATIONS LAB MANUAL Page 64

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

The Johnson Ring Counter or "Twisted Ring Counters", is another shift register with

feedback exactly the same as the standard Ring Counter above, except that this time the inverted

output Q of the last flip-flop is now connected back to the input D of the first flip-flop as shown

below. The main advantage of this type of ring counter is that it only needs half the number of

flip-flops compared to the standard ring counter then it’s modulo number is halved. So a "n-

stage" Johnson counter will circulate a single data bit giving sequence of 2n different states and

can therefore be considered as a "mod-2n counter".

4-bit twisted Counter

This inversion of Q before it is fed back to input D causes the counter to "count" in a

different way. Instead of counting through a fixed set of patterns like the normal ring counter

such as for a 4-bit counter, "0001"(1), "0010"(2), "0100"(4), "1000"(8) and repeat, the Johnson

counter counts up and then down as the initial logic "1" passes through it to the right replacing

the preceding logic "0". A 4-bit Johnson ring counter passes blocks of four logic "0" and then

four logic "1" thereby producing an 8-bit pattern. As the inverted output Q is connected to the

input D this 8-bit pattern continually repeats. For example, "1000", "1100", "1110", "1111",

"0111", "0011", "0001", "0000" and this is demonstrated in the following table below.

DIGITAL IC APPLICATIONS LAB MANUAL Page 65

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Truth Table for a 4-bit twisted Ring Counter

Clock Pulse No FFA FFB FFC FFD

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 1 0

4 1 1 1 1

5 0 1 1 1

6 0 0 1 1

7 0 0 0 1

As well as counting or rotating data around a continuous loop, ring counters can

also be used to detect or recognize various patterns or number values within a set

of data. By connecting simple logic gates such as the AND or the OR gates to the

outputs of the flip-flops the circuit can be made to detect a set number or value.

Standard 2, 3 or 4-stage Johnson ring counters can also be used to divide the

frequency of the clock signal by varying their feedback connections and divide-

by-3 or divide-by-5 outputs are also available. A 3-stage Johnson Ring Counter

can also be used as a 3-phase, 120 degree phase shift square wave generator by

connecting to the data outputs at A, B and NOT-B. The standard 5-stage Johnson

counter such as the commonly available CD4017 is generally used as a

synchronous decade counter/divider circuit. The smaller 2-stage circuit is also

called a "Quadrature" (sine/cosine) Oscillator/Generator and is used to produce

four individual outputs that are each "phase shifted" by 90 degrees with respect to

each other, and this is shown below.

Result: - Hence the 8 bit serial In and serial OUT using two 4-bit shift register is constructed

and verified

DIGITAL IC APPLICATIONS LAB MANUAL Page 66

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 14

4 DIGIT HEX COUNTER USING SYNCHRONOUS ONE DIGIT HEX

COUNTER

Aim: - To study and implementation of 4 digit hex counter using synchronous

one digit hex Counter.

Apparatus:-

1) 4- Digit Hex counter Trainer kit

2) Patch chords

3) Power supply

Theory:-

The external clock pulses (pulses to be counted) are fed directly to each of the J-K flip-

flops in the counter chain and that both the J and K inputs are all tied together in toggle mode,

but only in the first flip-flop, flip-flop FFA (LSB) are they connected HIGH, logic “1” allowing

the flip-flop to toggle on every clock pulse. Then the synchronous counter follows a

predetermined sequence of states in response to the common clock signal, advancing one state

for each pulse.The J and K inputs of flip-flop FFB are connected directly to the output QA of

flip-flop FFA, but the J and K inputs of flip-flops FFC and FFD are driven from separate AND

gates which are also supplied with signals from the input and output of the previous stage. These

additional AND gates generate the required logic for the JK inputs of the next stage. If we enable

each JK flip-flop to toggle based on whether or not all preceding flip-flop outputs (Q) are

“HIGH” we can obtain the same counting sequence as with the asynchronous circuit but without

the ripple effect, since each flip-flop in this circuit will be clocked at exactly the same time.Then

as there is no inherent propagation delay in synchronous counters, because all the counter stages

are triggered in parallel at the same time, the maximum operating frequency of this type of

frequency counter is much higher than that for a similar asynchronous counter circuit

DIGITAL IC APPLICATIONS LAB MANUAL Page 67

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Pin-diagram:-

Circuit Connection:

DIGITAL IC APPLICATIONS LAB MANUAL Page 68

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Procedure:-

1. Connect the first J-K flip-flop to logic switch using a patch chord.

2. Connect the output of 1st flip-flop ‘1QA’ to the 2nd flip-flop J-K.

Connect this point to the 7seg ‘A’ input using patch chord and connect

this point to the AND gate input.

3. Connect the output of 2nd flip-flop ‘1QB’ to the 3rd flip-flop J-K.

Connect this point to the 7seg ‘B’ input using patch chord and connect this

point to the AND gate input.

4. Connect the output of AND gate ‘1QC’ to the 4th flip-flop J-K. Connect

this point to the output LED ‘C’ input using patch chord connect this

point to the AND gate input.

5. Make the all connection shown in the circuit connection diagram.

6. Connect the 1st stage outputs QA, QB, QC and QD to the output LEDs.

7. Connect the 2nd stage outputs QA, QB, QC and QD to the output LEDs.

8. Connect the 3rd stage outputs QA, QB, QC and QD to the output LEDs.

9. Connect the 4th stage outputs QA, QB, QC and QD to the output LEDs.

Now switch on the trainer kit put the reset and the J-K flip-flop

switches in logic switch put in logic’1’.

10. Verify the counting on output LEDs. The first stage completes the

‘HHHH’ the second stage will be incremented by one this process is

continues until the all the stages reaches to the ‘HHHH HHHH HHHH

HHHH’.

11. After completion of the all the stages ‘HHHH’ the counter will be

automatically resets and it starts from ‘LLLL’.

DIGITAL IC APPLICATIONS LAB MANUAL Page 69

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

FUNCTION TABLE: (UP COUNT)

OUTPUTS

COUNT

QD QC QB QA

0 L L L L

1 L L L H

2 L L H L

3 L L H H

4 L H L L

5 L H L H

6 L H H L

7 L H H H

8 H L L L

9 H L L H

10 H L H L

11 H L H H

12 H H L L

13 H H L H

14 H H H L

15 H H H H

Result:- Hence the implementation of 4 digit hex counter using synchronous

one digit hex Counter is verified.

DIGITAL IC APPLICATIONS LAB MANUAL Page 70

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

EXPERIMENT NO: 15

4 DIGIT HEX COUNTER USING ASYNCHRONOUS ONE DIGT HEX

COUNTER

Aim: - To study and implementation of 4 digit hex counter using

asynchronous one digit hex Counter.

Apparatus:-

1) 4 Digit Hex counter Trainer kit.

2) Patch chords.

3) Power supply.

Theory:-

Asynchronous Counters use flip-flops that are serially connected together so that the

input clock pulse ripples through the counter giving them the name of ripple counter. In this

asynchronous circuit the clock signal should be connected to the only the first J-K flip-flop and

the output of the first flip-flop that is ‘Q’ is connected to the clock input of the second flip-flop.

It means that whenever the first flip-flop complete its function then the output ‘Q’ will be

activated it gives a clock pulse to the next flip-flop. The second flip-flop will be activated then

the output of the second stage is given to the third stage clock input of the J-K flip-flop. The

sequence is four stages so the outputs will be QA, QB, QC and QD. The QA is the output of the

first stage and QB is the output of the second stage similarly remaining QC and QD respective

stages. The output of the single stage counts the 0000- 1111 it means that it counts the zero to

fifteen so it is called the one hex count. This is only for the single stage using this single stage we

are build the four digit hex counter. To build this we are using the 74LS73 it is having the two J-

K flip-flops.

DIGITAL IC APPLICATIONS LAB MANUAL Page 71

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

PIN DIAGRAM:74LS73

Circuit connection diagram:-

DIGITAL IC APPLICATIONS LAB MANUAL Page 72

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

Procedure:-

1) Connect the Reset to the logic switch through the patch chord.

2) Connect the first J-K flip-flop all to be shorted and give them to logic switch

using a patch chord.

3) Connect the output of 1st flip-flop ‘1QA’ to the 2nd flip-flop clk. Connect this point to

the 7seg ‘A’ input using patch chord.

4) Connect the output of 2nd flip-flop ‘1QB’ to the 3rd flip-flop clk. Connect this point

to the 7seg ‘B’ input using patch chord.

5) Connect the output of 3rd flip-flop ‘1QC’ to the 4th flip-flop clk. connect this point to

the 7seg ‘C’ input using patch chord.

6) Connect the output of 4th flip-flop ‘1QD’ to the output LED ‘D’ input using patch

chord this is only for the single digit.

7) Connect the output of 1st stage ‘1QD’ to the clock input of the 2nd stage.

8) Make the all connection shown in the circuit connection diagram.

9) Connect the 1st stage outputs QA, QB, QC and QD to the output LEDs.

10) Connect the 2nd stage outputs QA, QB, QC and QD to the output LEDs.

11) Connect the 3rd stage outputs QA, QB, QC and QD to the output LEDs.

12) Connect the 4th stage outputs QA, QB, QC and QD to the output LEDs.

13) Now switch on the trainer kit input the reset and the J-K flip-flop switches in logic

switch.

14) Verify the counting on output LEDs. The first stage completes the ‘F’ the second

stage will be incremented by one this process is continues until the all the stages

reaches to the ‘FFFF’.

15) After completion of the all the stages ‘F’ the counter will be automatically resets

and it starts from ‘LLLL’.

DIGITAL IC APPLICATIONS LAB MANUAL Page 73

ANURAG COLLEGE OF ENGINEERING DEPT OF ECE

FUNCTION TABLE: (UP COUNT)

OUTPUTS

COUNT

QD QC QB QA

0 L L L L

1 L L L H

2 L L H L

3 L L H H

4 L H L L

5 L H L H

6 L H H L

7 L H H H

8 H L L L

9 H L L H

10 H L H L

11 H L H H

12 H H L L

13 H H L H

14 H H H L

15 H H H H

NOTE: All the inputs connected may be high or low.They are just connected to close the circuit.

For every count pulse should be given then only the output changes.

Result:- Hence the implementation of 4 digit hex counter using asynchronous one digit hex

Counter is verified

DIGITAL IC APPLICATIONS LAB MANUAL Page 74

Вам также может понравиться

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsОт EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsРейтинг: 4.5 из 5 звезд4.5/5 (2)

- DICA Lab Manual PDFДокумент64 страницыDICA Lab Manual PDFssptc MagazineОценок пока нет

- Syllabus: Department of Computer Science & Engineering Lab Manual Digital Lab Class: 2 Yr, 3 SemДокумент104 страницыSyllabus: Department of Computer Science & Engineering Lab Manual Digital Lab Class: 2 Yr, 3 SemPECMURUGANОценок пока нет

- Dica Lab ManualДокумент88 страницDica Lab ManualRaghavendra RaghavaОценок пока нет

- CO Lab Manual-MinДокумент40 страницCO Lab Manual-MinMatheen TabidОценок пока нет

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreДокумент115 страницDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiОценок пока нет

- 16×4 EncoderДокумент6 страниц16×4 Encoderrmedu07.officialОценок пока нет

- ECE 2003 ManualДокумент79 страницECE 2003 Manualannambaka satishОценок пока нет

- Linear Integrated Circuits Lab ManualДокумент74 страницыLinear Integrated Circuits Lab Manualarivurp100% (2)

- Digital Electronics LAB ManualДокумент61 страницаDigital Electronics LAB ManualKiranmai KonduruОценок пока нет

- DLD Lab ManualДокумент101 страницаDLD Lab ManualHamza100% (1)

- (Question Bank) : Dr. Harjinder SinghДокумент12 страниц(Question Bank) : Dr. Harjinder SinghSanjay DuttОценок пока нет

- DSDДокумент45 страницDSDnama varapuОценок пока нет

- LD Lab ManualДокумент92 страницыLD Lab ManualSunil BegumpurОценок пока нет

- Logic Design Lab ManualДокумент22 страницыLogic Design Lab ManualAzarkhan Mokashi100% (1)

- UNIT V Digital Integrated Circuits Introduction Part IIДокумент135 страницUNIT V Digital Integrated Circuits Introduction Part IINayab Rasool SK100% (1)