Академический Документы

Профессиональный Документы

Культура Документы

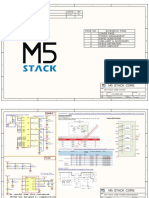

S32k144evb SCH 29248 RB1

Загружено:

Ionuţ HwОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

S32k144evb SCH 29248 RB1

Загружено:

Ionuţ HwАвторское право:

Доступные форматы

5 4 3 2 1

Table of Contents Revisions

Rev Description Date

2 Notes and Block Diagram Approved

XA Initial Release APR-13-2016 O. Romero

3 S32K144 MCU

A Prototype Production APR-14-2016 O. Romero

4 OpenSDA interface

AX1 Development AUG-16-2016 O. Romero

5 Power Supply/SWD

B 2nd Release SEP-02-2016 O. Romero

6 I/O Headers

D D

C C

S32K144EVB-Q100

B B

A Microcontroller Solutions Group A

6501 William Cannon Drive West

Austin, TX 78735-8598

This document contains information proprietary to Freescale Semiconductor and shall not be used for

engineering design, procurement or manufacture in whole or in part without the express written permission

of Freescale Semiconductor.

ICAP Classification: FCP: ____ FIUO: X PUBI: ____

Designer: Drawing Title:

Osvaldo Romero

S32K144EVB-Q100

Drawn by: Page Title:

Osvaldo Romero TITLE PAGE

Approved: Size Document Number Rev

APPROVER C SCH-29248 PDF: SPF-29248 B

Date: Friday, September 02, 2016 Sheet 1 of 6

5 4 3 2 1

5 4 3 2 1

1. Unless Otherwise Specified:

All resistors are in ohms, 1% and 5 %

All capacitors are in uF, 10% , 20 % and 5%

All voltages are DC

All polarized capacitors are aluminum electrolytic

2. Interrupted lines coded with the same letter or letter

combinations are electrically connected.

D D

3. Device type number is for reference only. The number

varies with the manufacturer.

4. Special signal usage:

_B Denotes - Active-Low Signal

<> or [] Denotes - Vectored Signals

5. Interpret diagram in accordance with American

National Standards Institute specifications, current

revision, with the exception of logic block symbology.

C C

B B

A A

ICAP Classification: FCP: ___ FIUO: X PUBI: ___

Drawing Title:

S32K144EVB-Q100

Page Title:

Notes and Block Diagram

Size Document Number Rev

C SCH-29248 PDF: SPF-29248 B

Date: Friday, September 02, 2016 Sheet 2 of 6

5 4 3 2 1

5 4 3 2 1

Note: VREFH can be selected from

the following 3 options: VDD_MCU VREFH

- Option 1(default): VREFH =

VDD_MCU, place R103, dnp R99, R109 R103 0 R109 DNP 0

and D7. AREF P[6]

- Option 2: VREFH = 3.0V from D7,

place D7 and R99, dnp R103 and C43 C145 R99 DNP 1K

R109.

C

- Option 3: VREFH=AREF, place R109, 1UF 0.1uF

dnp R103,R99 and D7. DNP D7

BZX384-C30

DNP

A

D

AREF D

VREFH

VDD_MCU

C129 C140 C131 C141 C133 C142 C146 C143 C137 C144

1UF 0.1uF 1UF 0.1uF 1UF 0.1uF 1UF 0.1uF 1UF 0.1uF

DNP DNP DNP DNP DNP

C147 C148 PTD0 P[6]

1000PF 1000PF 0 R156 RGB_BLUE P[6]

DNP DNP

P[6] PTA4

P[4,5] JTAG_TMS/SWD_DIO_PTA4 R122 0

U17

11

10

38

61

87

13

12

PS32K144HFT0VLLT

VREFH

VDDA

VDD1

VDD2

VDD3

VDD4

VREFL

P[6] PTA0 79 PTD6 P[6]

78 PTA0/ADC0_SE0/CMP0_IN0/FTM2_CH1/LPI2C0_SCLS/FXIO_D2/FTM2_QD_PHA/LPUART0_CTS/TRGMUX_OUT3 4 R130 0

P[6] PTA1 PTA1/ADC0_SE1/CMP0_IN1/FTM1_CH1/LPI2C0_SDAS/FXIO_D3/FTM1_QD_PHA/LPUART0_RTS/TRGMUX_OUT0 PTD0/FTM0_CH2/LPSPI1_SCK/FTM2_CH0/FXIO_D0/TRGMUX_OUT1 LIN_RX P[5]

P[6] PTA2 73 3 PTD1 P[6]

72 PTA2/ADC1_SE0/FTM3_CH0/LPI2C0_SDA/EWM_OUT/FXIO_D4/LPUART0_RX PTD1/FTM0_CH3/LPSPI1_SIN/FTM2_CH1/FXIO_D1/TRGMUX_OUT2 71

P[6] PTA3 PTA3/ADC1_SE1/FTM3_CH1/LPI2C0_SCL/EWM_IN/FXIO_D5/LPUART0_TX PTD2/ADC1_SE2/FTM3_CH4/LPSPI1_SOUT/FXIO_D4/FXIO_D6/TRGMUX_IN5 PTD2 P[6] PTD7 P[6]

98 70 PTD3 P[6] R131 0 LIN_TX P[5]

97 PTA4/JTAG_TMS/SWD_DIO/CMP0_OUT/EWM_OUT PTD3/ADC1_SE3/FTM3_CH5/LPSPI1_PCS0/FXIO_D5/FXIO_D7/TRGMUX_IN4/NMI 69

P[4,5,6] RST_TGTMCU_B PTA5/RESET/TCLK1 PTD4/ADC1_SE6/FTM0_FLT3/FTM3_FLT3 PTD4 P[6]

P[6] PTA6 58 33 PTD5 P[6]

57 PTA6/ADC0_SE2/FTM0_FLT1/LPSPI1_PCS1/LPUART1_CTS PTD5/FTM2_CH3/LPTMR0_ALT2/FTM2_FLT1/TRGMUX_IN7 32

P[6] PTA7 PTA7/ADC0_SE3/FTM0_FLT2/RTC_CLKIN/LPUART1_RTS PTD6/CMP0_IN7/LPUART2_RX/FTM2_FLT2

P[6] PTA8 100 31

99 PTA8/LPUART2_RX/LPSPI2_SOUT/FXIO_D6/FTM3_FLT3 PTD7/CMP0_IN6/LPUART2_TX/FTM2_FLT3 42

C P[6] PTA9 PTD8 P[6] C

92 PTA9/LPUART2_TX/LPSPI2_PCS0/FXIO_D7/FTM3_FLT2/FTM1_FLT3 PTD8/FTM2_FLT2/FTM1_CH4 41

P[6] PTA10 PTA10/JTAG_TDO/NOETM_TRACE_SWO/FTM1_CH4/FXIO_D0 PTD9/FTM2_FLT3/FTM1_CH5 PTD9 P[6]

P[6] PTA11 91 36 PTD10 P[6]

R123 0 90 PTA11/FTM1_CH5/FXIO_D1/CMP0_RRT PTD10/FTM2_CH0/FTM2_QD_PHB 35

P[5] JTAG_TDO P[6] PTA12 PTA12/FTM1_CH6/CAN1_RX/FTM2_QD_PHB PTD11/FTM2_CH1/FTM2_QD_PHA/LPUART2_CTS PTD11 P[6]

P[6] PTA13 89 34 PTD12 P[6] PTD15 P[6]

88 PTA13/FTM1_CH7/CAN1_TX/FTM2_QD_PHA PTD12/FTM2_CH2/LPUART2_RTS 25 0 R154

P[6] PTA14 PTA14/FTM0_FLT0/FTM3_FLT1/EWM_IN/FTM1_FLT0 PTD13/FTM2_CH4/LPUART1_RX/RTC_CLKOUT PTD13 P[6] RGB_RED P[6]

CAD Note: R125 and 83 24

R126 POKA-YOKE: P[6] PTA15 PTA15/ADC1_SE12/FTM1_CH2/LPSPI0_PCS3/LPSPI2_PCS3 PTD14/FTM2_CH5/LPUART1_TX/CLKOUT PTD14 P[6]

P[6] PTA16 82 22 PTD16 P[6]

Place R125 and 62 PTA16/ADC1_SE13/FTM1_CH3/LPSPI1_PCS2 PTD15/FTM0_CH0/LPSPI0_SCK 21 0 R155

R126 with the same P[6] PTA17 PTA17/FTM0_CH6/FTM3_FLT0/EWM_OUT PTD16/FTM0_CH1/LPSPI0_SIN/CMP0_RRT RGB_GREEN P[6]

20 PTD17 P[6]

orientation and PTD17/FTM0_FLT2/LPUART2_RX

provide same airgap P[6] PTB0 54

53 PTB0/ADC0_SE4/ADC1_SE14/LPUART0_RX/LPSPI0_PCS0/LPTMR0_ALT3/CAN0_RX 94

between the two P[6] PTB1 PTB1/ADC0_SE5/ADC1_SE15/LPUART0_TX/LPSPI0_SOUT/TCLK0/CAN0_TX PTE0/LPSPI0_SCK/TCLK1/LPSPI1_SOUT/FTM1_FLT2 PTE0 P[6]

resistors terminals P[6] PTB2 48 93 PTE1 P[6] PTE4 P[6]

47 PTB2/ADC0_SE6/FTM1_CH0/LPSPI0_SCK/FTM1_QD_PHB/TRGMUX_IN3 PTE1/LPSPI0_SIN/LPI2C0_HREQ/LPSPI1_PCS0/FTM1_FLT1 85 R137 0

in a square P[6] PTB3 PTE2 P[6] SBC_CAN_RX P[5]

fashion.P[6] PTB14 28 PTB3/ADC0_SE7/FTM1_CH1/LPSPI0_SIN/FTM1_QD_PHA/TRGMUX_IN2 PTE2/ADC1_SE10/LPSPI0_SOUT/LPTMR0_ALT3/FTM3_CH6/LPUART1_CTS 18

P[6] PTB4 PTB4/FTM0_CH4/LPSPI0_SOUT/TRGMUX_IN1 PTE3/FTM0_FLT0/LPUART2_RTS/FTM2_FLT0/TRGMUX_IN6/CMP0_OUT PTE3 P[6]

P[5] SBC_SCK R124 0 P[6] PTB5 27 9 PTE5 P[6]

16 PTB5/FTM0_CH5/LPSPI0_PCS1/LPSPI0_PCS0/CLKOUT/TRGMUX_IN0 PTE4/FTM2_QD_PHB/FTM2_CH2/CAN0_RX/FXIO_D6/EWM_OUT 8 R136 0

P[6] PTB6 PTB6/XTAL/LPI2C0_SDA PTE5/TCLK2/FTM2_QD_PHA/FTM2_CH3/CAN0_TX/FXIO_D7/EWM_IN SBC_CAN_TX P[5]

P[6] PTB15 P[6] PTB7 15 84 PTE6 P[6]

R125 0 77 PTB7/EXTAL/LPI2C0_SCL PTE6/ADC1_SE11/LPSPI0_PCS2/FTM3_CH7/LPUART1_RTS 59

P[5] SBC_MISO P[6] PTB8 PTB8/FTM3_CH0 PTE7/FTM0_CH7/FTM3_FLT0 PTE7 P[6]

P[6] PTB9 76 26 PTE8 P[6] PTE9 P[6]

75 PTB9/FTM3_CH1/LPI2C0_SCLS PTE8/CMP0_IN3/FTM0_CH6 23 R529 0

P[6] PTB16 P[6] PTB10 PTB10/FTM3_CH2/LPI2C0_SDAS PTE9/FTM0_CH7/LPUART2_CTS LIN_SLP P[5]

P[5] SBC_MOSI R126 0 P[6] PTB11 74 6 PTE10 P[6]

68 PTB11/FTM3_CH3/LPI2C0_HREQ PTE10/CLKOUT/LPSPI2_PCS1/FTM2_CH4/FXIO_D4/TRGMUX_OUT4 5

P[6] PTB12 PTB12/ADC1_SE7/FTM0_CH0/FTM3_FLT2/CAN2_RX PTE11/LPSPI2_PCS0/LPTMR0_ALT1/FTM2_CH5/FXIO_D5/TRGMUX_OUT5 PTE11 P[6]

P[6] PTB17 P[6] PTB13 67 19 PTE12 P[6]

0 R129 66 PTB13/ADC1_SE8/ADC0_SE8/FTM0_CH1/FTM3_FLT1/CAN2_TX PTE12/FTM0_FLT3/LPUART2_TX 7

P[5] SBC_CS PTB14/ADC1_SE9/ADC0_SE9/FTM0_CH2/LPSPI1_SCK PTE13/LPSPI2_PCS2/FTM2_FLT0 PTE13 P[6]

65 17 PTE14 P[6] R532 0 SBC_LIMP P[5]

64 PTB15/ADC1_SE14/FTM0_CH3/LPSPI1_SIN PTE14/FTM0_FLT1/FTM2_FLT1 2

PTB16/ADC1_SE15/FTM0_CH4/LPSPI1_SOUT PTE15/LPUART1_CTS/LPSPI2_SCK/FTM2_CH6/FXIO_D2/TRGMUX_OUT6 PTE15 P[6]

63 1 PTE16 P[6]

PTB17/FTM0_CH5/LPSPI1_PCS3 PTE16/LPUART1_RTS/LPSPI2_SIN/FTM2_CH7/FXIO_D3/TRGMUX_OUT7

P[6] PTC0 40

39 PTC0/ADC0_SE8/FTM0_CH0/LPSPI2_SIN/FTM1_CH6

P[6] PTC1 PTC1/ADC0_SE9/FTM0_CH1/LPSPI2_SOUT/FTM1_CH7

P[6] PTC2 30

29 PTC2/ADC0_SE10/CMP0_IN5/FTM0_CH2/CAN0_RX/LPUART0_RX

P[6] PTC4 P[6] PTC3 PTC3/ADC0_SE11/CMP0_IN4/FTM0_CH3/CAN0_TX/LPUART0_TX

P[4,5] JTAG_TCLK/SWD_CLK R127 0 96

95 PTC4/JTAG_TCLK/SWD_CLK/CMP0_IN2/FTM1_CH0/RTC_CLKOUT/EWM_IN/FTM1_QD_PHB

81 PTC5/JTAG_TDI/FTM2_CH0/RTC_CLKOUT/FTM2_QD_PHB

80 PTC6/ADC1_SE4/LPUART1_RX/CAN1_RX/FTM3_CH2/FTM1_QD_PHB

56 PTC7/ADC1_SE5/LPUART1_TX/CAN1_TX/FTM3_CH3/FTM1_QD_PHA

B P[6] PTC5 P[6] PTC8 PTC8/LPUART1_RX/FTM1_FLT0/LPUART0_CTS B

P[5] JTAG_TDI R128 0 P[6] PTC9 55

52 PTC9/LPUART1_TX/FTM1_FLT1/LPUART0_RTS

P[6] PTC10 PTC10/FTM3_CH4/TRGMUX_IN11

P[6] PTC6 P[6] PTC11 51

R161 0 50 PTC11/FTM3_CH5/TRGMUX_IN10

P[4] UART_RX PTC12/FTM3_CH6/FTM2_CH6/LPUART2_CTS

49

46 PTC13/FTM3_CH7/FTM2_CH7/LPUART2_RTS

45 PTC14/ADC0_SE12/FTM1_CH2/LPSPI2_PCS0/TRGMUX_IN9

P[6] PTC7 P[6] PTC15 PTC15/ADC0_SE13/FTM1_CH3/LPSPI2_SCK/TRGMUX_IN8

P[4] UART_TX R162 0 P[6] PTC16 44

43 PTC16/ADC0_SE14/FTM1_FLT2/CAN2_RX

P[6] PTC17 PTC17/ADC0_SE15/FTM1_FLT3/CAN2_TX

VSS1

VSS2

VSS3

VSS4

P[6] PTC12

P[6] BTN0 R152 0

P[6] PTC13

14

37

60

86

P[6] BTN1 R153 0

P[6] PTC14

P[6] ADC0_SE12 R164 0

A A

ICAP Classification: FCP: ___ FIUO: X PUBI: ___

Drawing Title:

S32K144EVB-Q100

Page Title:

S32K144 MCU

Size Document Number Rev

C SCH-29248 PDF: SPF-29248 B

Date: Friday, September 02, 2016 Sheet 3 of 6

5 4 3 2 1

5 4 3 2 1

OpenSDA Interface U8 P3V3_SDA

RESET P3V3_SDA

R3

10.0K

C19

P3V3_SDA

0.1UF

C3

4.7uF 1

U1

VCCA VCCB

V_TGTMCU

C2 C4

8 4.7uF 0.1UF

V_TGTMCU

R4

180K

D SDA_RST_TGTMCU_J_B 2 7 D

P3V3_SDA TP500 TP_2102_A 3 A1 B1 6 TP_2102_B TP501

R42 U9 P3V3_SDA A2 B2

1 10.0K 74LVC2G14GF,132 4 5

C7 VDD1 GND OE LVLRST_EN

C12 C6 SDA_SWD_EN_B_R 1 A1 Y1 6 SDA_SWD_EN P3V3_SDA

10uF 1.0UF 0.1UF NTSX2102GU8H

7 2 GND VCC

5 1-2: Default. J104 R1 4.7K

VDDA 2-3: Reset signal direct to the MCU, HDR TH 1X3

P3V3_SDA 3 A2 Y2 4 SDA_SWD_OE to use when OpenSDA is not powered. RST Push Button

R49 Bypass

8 0 C10 SW5

1

2

3

VSSA 12 SDA_JTAG_TCLK R39

JTAG_TCLK/SWD_CLK/EZP_CLK/TSI0_CH1/PTA0/UART0_CTS/UART0_COL/FTM0_CH5 13 SDA_JTAG_TDI 10.0K 0.1UF 1 2 SW1_RST_B V_TGTMCU

JTAG_TDI/EZP_DI/TSI0_CH2/PTA1/UART0_RX/FTM0_CH6 SDA_JTAG_TDO D1

14 3 4 R2

P3V3_SDA JTAG_TDO/TRACE_SWO/EZP_DO/TSI0_CH3/PTA2/UART0_TX/FTM0_CH7 15 SDA_JTAG_TMS SDA_SWD_OE_B_R C1 C A SDA_RST_LED

JTAG_TMS/SWD_DIO/TSI0_CH4/PTA3/UART0_RTS/FTM0_CH0 16 SDA_SWD_EN_B 1000pF

NMI/EZP_CS/TSI0_CH5/PTA4/FTM0_CH1/LLWU_P3 EVQ-P2402W

P5V_SDA 330 OHM

L1 RED

11

1 2 VBAT R32

SDA_EXTAL 0

8

TARGET MCU

C11 P5V_SDA SDA_XTAL Y1

330 OHM 10uF 1 3

SHELL3

SHELL4

1 P5V0_SDA_USB_CONN_VBUS

SDA_VOUT33

EXTAL0/PTA18/FTM0_FLT2/FTM_CLKIN0

17

18 C20 8.00MHZ C23

INTERFACE

SIGNALS

SDA_USBSHIELD

2

VBUS XTAL0/PTA19/FTM1_FLT0/FTM_CLKIN1/LPTMR0_ALT1

2 SDA_USB_CONN_DN 6 22PF 22PF Output to system

10 D- 3 5 VREGIN DNP DNP J105 1 from Level shifter

SHELL5 D+ 4 R25 33 SDA_USB_DN 4 VOUT33 DNP 2

ID USB0_DM

SHELL2

SHELL1

5 SDA_USB_CONN_DP R21 33 SDA_USB_DP 3 HDR 1X2 TH

GND USB0_DP SDA_SWD_OE_B

TC_SDA_USB_ID_TP TP6 SDA_RST_TGTMCU_B SDA_RST_TGTMCU_J_B R5 0 RST_TGTMCU_B P[3,5,6]

C9 20

ADC0_SE8/TSI0_CH0/PTB0/I2C0_SCL/FTM1_CH0/FTM1_QD_PHA/LLWU_P5

2

2

2.2UF 21 DNP

7

J7 D17 D18 D19 10 ADC0_SE9/TSI0_CH6/PTB1/I2C0_SDA/FTM1_CH1/FTM1_QD_PHB

USB_MICRO_AB PESD5V0R1BSF PESD5V0R1BSF 9 EXTAL32 P3V3_SDA

PESD5V0R1BSF XTAL32 V_TGTMCU

TP11 TC_EXTAL_TP

TP10 TC_XTAL_TP U4

1 6

L2

1

19 SDA_RX_EN 5 VCCA VCCB UART1_RX_TGTMCU_BUF R24 0 UART1_RX_TGTMCU

RESET DIR UART_RX P[3]

1 2

UART1_RX_TGTMCU_R 3 4

A B

330 OHM P3V3_SDA

P5V_SDA 22 SDA_SPI0_RST_B TP8 R16 R15 2 Output to system

ADC0_SE15/TSI0_CH14/PTC1/SPI0_PCS3/UART1_RTS/FTM0_CH0/I2S0_TXD0/LLWU_P6 GND from Level shifter

Isolation

2 23 SDA_SPI0_CS TP7 10.0K 4.7K

VSS1 ADC0_SE4B/CMP1_IN0/TSI0_CH15/PTC2/SPI0_PCS2/UART1_CTS/FTM0_CH1/I2S0_TX_FS 24 UART1_TX_TGTMCU_R

CMP1_IN1/PTC3/SPI0_PCS1/UART1_RX/FTM0_CH2/I2S0_TX_BCLK/LLWU_P7 UART1_RX_TGTMCU_R 74LVCH1T45

R57 25

Resistors

4.7K PTC4/SPI0_PCS0/UART1_TX/FTM0_CH3/CMP1_OUT/LLWU_P8 26 SDA_SPI0_SCK

PTC5/SPI0_SCK/LPTMR0_ALT2/I2S0_RXD0/CMP0_OUT/LLWU_P9 27 SDA_SPI0_SOUT P3V3_SDA V_TGTMCU

C SDA_RST CMP0_IN0/PTC6/SPI0_SOUT/PDB0_EXTRG/I2S0_RX_BCLK/I2S0_MCLK/LLWU_P10 28 SDA_SPI0_SIN C

CMP0_IN1/PTC7/SPI0_SIN/USB_SOF_OUT/I2S0_RX_FS

R62 TP12 P3V3_SDA U2

10.0K

7 8

UART1_TX_TGTMCU_R 6 VCCA VCCB 1 UART1_TX_TGTMCU_BUF R18 0 UART1_TX_TGTMCU

UART_TX P[3]

A

33 D2 R12 SDA_SPI0_SIN 5 1A 1B 2

SDA_LED_R

EPAD 4 2A 2B 3

220 GND DIR

LED GREEN

PU/PD LOGIC:

SERIAL INTERFACE 74LVC2T45GM,125 Output to system

IS ALWAYS RESET from Level shifter

WHEN USB PORT

C

IS DISCONNECTED P3V3_SDA HDR 1X2 TH

29 SDA_LED V_TGTMCU J106

PTD4/SPI0_PCS1/UART0_RTS/FTM0_CH4/EWM_IN/LLWU_P14 30 DNP

ADC0_SE6B/PTD5/SPI0_PCS2/UART0_CTS/UART0_COL/FTM0_CH5/EWM_OUT 31 POWER_EN U7 SWD_DIO_TGTMCU_BUF SWD_DIO_TGTMCU

JTAG_TMS/SWD_DIO_PTA4 P[3,5]

1

2

ADC0_SE7B/PTD6/SPI0_PCS3/UART0_RX/FTM0_CH6/FTM0_FLT0/LLWU_P15 32 VTRG_FAULT_B 1 6

PTD7/CMT_IRO/UART0_TX/FTM0_CH7/FTM0_FLT1 SDA_SWD_OE R35 0 SDA_SWD_OE_R 5 VCCA VCCB

P5V_SDA DIR SWD_CLK_TGTMCU_BUF

JTAG_TCLK/SWD_CLK P[3,5]

1

2

SDA_SPI0_SOUT 3 4

A B

R14 R31 R30 J8

4.7K 10.0K 4.7K 2 HDR 1X2 TH

DNP GND DNP

SDA_USB_P5V_SENSE

74LVCH1T45

MK20DX128VFM5 HW Designer: Rafael del Rey

R20

10.0K P3V3_SDA OPEN SDA

DNP V_TGTMCU POWER OUTPUTS

U10 OPEN SDA

SDA_SWD_EN

R47

0 SDA_SWD_EN_R

1

5 VCCA VCCB

6 INPUT POWER

DIR

P3V3_SDA

i path SDA_VOUT33

i path

SDA_SPI0_SCK 3 4

A B

Note: You can power openSDA

1

2

R51 R52 with your own power supplies

10.0K 4.7K 2 3.3VDC, 10mA should be provided by replacing this rail

GND to this rail (P3V3_SDA) J9 HDR 1X2 TH (SDA_VOUT33)

in order to power openSDA DNP with your 3.3V power supply rail

74LVCH1T45 module SHORTING HEADER ON BOTTOM LAYER

PWR SWITCH

Jumper is shorted by a cut-trace

on bottom layer. Cutting the trace

OpenSDA INTERFACE JTAG CONNECTOR

will effectively isolate the on-board

P5V_SDA MCU from the OpenSDA

(To enable 5v from Isolation and level shift stage PU/PD LOGIC (DIR PIN): debug interface.

BUFFER IS TRISTATED WHEN

USB connector) P5V_SDA C25 C15 (for 1.8 to 5V compatibility) P3V3_SDA IS UNPOWERED

i path

18PF U11 P5V_SDA_PSW

0.1UF DNP 1 6

VIN VOUT

10.0K

B DNP MIC2005_CSLEW

5 4 P3V3_SDA SDA_VOUT33 can provide up to 120mA B

P3V3_SDA R70 CSLEW FAULT of power at 3.3VDC to your system

VTRG_EN 3 2

R68 ENABLE GND R60 P3V3_SDA V_TGTMCU P5V_TRG_SDA can provide up to 450mA

R77 MIC2005-0.8YM6 (per USB spec) of power at 5VDC

10.0K to your system

10.0K ACTIVE HIGH

J12 VTRG_FAULT_B

P3V3_SDA C18 C8

1 2 SDA_JTAG_TMS 15K

3 4 SDA_JTAG_TCLK 4.7uF 4.7uF

I/O POWER

5 6 SDA_JTAG_TDO

C26 7 8 SDA_JTAG_TDI POWER_EN R69 1.0K

9 10 SDA_RST i path INPUT

0.1UF V_TGTMCU SH1

HDR 2X5 VDD

V_BRD is supported

from 1.8V to 5V

0

Power should be provided

to this rail for the logic

related to your platform I/O

SDA_SPI0_RST_B R41 0 SDA_SWD_EN

DNP

SDA_SPI0_CS R38 0 SDA_SWD_OE

DNP

{For enablement purposes only}

A A

ICAP Classification: FCP: ___ FIUO: X PUBI: ___

Drawing Title:

S32K144EVB-Q100

Page Title:

OpenSDA interface

Size Document Number Rev

D SCH-29248 PDF: SPF-29248 B

Date: Friday, September 02, 2016 Sheet 4 of 6

5 4 3 2 1

5 4 3 2 1

P5V_SBC P5V_SDA_PSW P5V0 P3V3

TP38

VBATT VIN VSUP TP14 TP13

J107

J16 Q1 3

1 PHPT61003PY 2

3 3 TP15 1

2 2

A

D

1 5 U15 D

CON PWR 3 D9 D13 HDR TH 1X3 1 5

SH1

SH2

PNS40010ER TP36 VIN VOUT

PNS40010ER

2

CAD Note: Place R169 0 GND

4

C22 and C21 close 3 4

C27 to U15 VIN C22 C21 R170 0 EN BYP

6.8uF 0.1uF 10uF DNP C24

SPX3819M5-L-3-3 C59 10uF

20mOhm Resistor

C128 Place C29 as in layout

22uF C47 close as possible C29 0.01UF

0.1uF to Q1 emitter, 0.01uf

P5V_SBC U32 VDD P5V_SBC pins 1-3.

1 8

VCCA VCCB

P[5] SBC_RST R565 DNP 0 2 7 R563 DNP 0 RST_TGTMCU_B P[3,4,5,6]

3 A1 B1 6

A2 B2

4 5

GND OE R562 4.7K

NTSX2102GU8H

P5V_SBC

VDD

U33 R535

1 6 P5V_SBC

5 VCCA VCCB

R564 4.7K DIR TP24

R566 DNP 0 3 4 2.2

P[5] SBC_LIMP_LS A B SBC_LIMP P[3]

2

GND TP20

C C

TP502 TP33 TP23 TP25 TP27 TP21

74LVCH1T45 R536

4.7K U19

15

DNP

6

UJA1169TK/F

5 14

VEXCC

VEXCTRL

TP22 TP19 V1 BAT

8 7 VSUP

P[5] SBC_RST RST RXD SBC_CAN_RX_LS P[5]

HDR 1X4 RA 2 SBC_CAN_TX_LS P[5]

11 TXD

P[5] SBC_LIMP_LS LIMP

1 CAN_HI 10 SBC_SCK_LS P[5]

2 13 SCK 3 R537

V2 SDI SBC_MOSI_LS P[5]

3 9 SBC_MISO_LS P[5] 10k

4 18 SDO 20

CANH SCS SBC_CS_LS P[5]

GND4

GND3

GND2

GND1

R92 17

CANL

2

1

12

EP

J13 WAKE

C40 60.4 J109

CAN HDR 1X2

21

19

16

4

1

C536

3

1

4700 PF 6.8uF

R98 SW9

2

1

EVQ-P2402W

60.4 J108

HDR 1X2

P5V_SBC

4

2

VSUP

TP35 TP37

MASTER OPTION

CAN_LO

PMEG3050EP P5V_SBC P5V_SBC

R538 Note: Place R530 U28 VDD

D6 P5V_SBC

4.7K only after R529

R80 2K C A

has been 1 8

VCCA VCCB

7

VBATT TP18 R171 2K U21 removed.

1 2 7

VBAT

RXD LIN_RX_LS P[5] R530 P[5] LIN_RX_LS A1 B1 LIN_RX P[3]

HDR 1X4 RA P[5] LIN_TX_LS 3 6 LIN_TX P[3]

4.7K A2 B2

3

NC1 DNP

1 LIN 8 4 LIN_TX_LS P[5] 4 5

B

2 NC2 TXD GND OE R558 4.7K B

3 6

4 LIN C17 LIN 2 NTSX2102GU8H

GND

SLP LIN_SLP P[3]

J11 220PF

TJA1027T/20

5

VREG + CANPHY + LINPHY

VDD

DNP DNP DNP

P5V0 P3V3 VDD TP4 TP9 TP16 TP31 TP34

R121

VDD VDD_MCU 10K

VDD

J14

R63 0 R117 0

1 2 JTAG_TMS/SWD_DIO_PTA4 P[3,4]

DNP 3 4 JTAG_TCLK/SWD_CLK P[3,4]

J10

5 6 R119 0 JTAG_TDO P[3]

1

2

1 7 8 R120 0 JTAG_TDI P[3]

2 R56 330 PWR_LED 9 10 RST_TGTMCU_B P[3,4,5,6]

3

HDR 2X5

A

J15

HDR TH 1X3 DNP DNP DNP D3 HDR 1X2

DNP TP17 TP1 TP32 GREEN DNP

R64 0

MCU Current Measurement SWD CONNECTOR

C

Power Supply Selection S32K144 Programming

A A

P5V_SBC

P5V_SBC VDD VDD

P5V_SBC P5V_SBC P5V_SBC CAD Note: Place level shifters

U30 P5V_SBC U26 VDD VDD on this page as close as

C538 possible.

1 8 1 8 U29 U31 C537

VCCA VCCB VCCA VCCB 1 6 0.1UF 1 6

2 7 2 7 5 VCCA VCCB 5 VCCA VCCB 0.1UF ICAP Classification: FCP: ___ FIUO: X PUBI: ___

P[5] SBC_CAN_TX_LS A1 B1 SBC_CAN_TX P[3] P[5] SBC_SCK_LS A1 B1 SBC_SCK P[3] DIR DIR

P[5] SBC_CAN_RX_LS 3 6 SBC_CAN_RX P[3] P[5] SBC_MOSI_LS 3 6 SBC_MOSI P[3] R559 4.7K Drawing Title:

A2 B2 A2 B2 3 4 3 4

4 5 4 5

P[5] SBC_MISO_LS A B SBC_MISO P[3] P[5] SBC_CS_LS A B SBC_CS P[3] S32K144EVB-Q100

GND OE R560 4.7K GND OE R556 4.7K Page Title:

2 2 Power Supply/SWD/Reset

NTSX2102GU8H NTSX2102GU8H GND GND

74LVCH1T45 74LVCH1T45 LEVEL SHIFTERS Size

C

Document Number

SCH-29248 PDF: SPF-29248

Rev

B

Date: Friday, September 02, 2016 Sheet 5 of 6

5 4 3 2 1

5 4 3 2 1

P[3] PTA11

P[3] PTA17

P[3,6] PTD10

P[3,6] PTD11

P[3] PTD12 PTE4 P[3]

P[3] PTD5 PTE5 P[3] VDD

P[3,6] PTD3 PTA12 P[3]

D P[3] PTE3 PTA13 P[3] D

P[3] PTD15

P[3] PTD16 PTC16 P[3]

P[3,6] PTD0 PTC17 P[3]

P[3,6] PTE8 PTD3 P[3,6]

P[3] PTC12 PTD1 P[3]

P[3] PTC13

P[3] PTE7

P[3] PTA14

NOTE:

J1,J2,J3 and J4: Arduino UNO R84 0 PTB6_XTAL

compatible headers. P[3,6] PTB6

P[3,6] PTB7 R88 0

J5 and J6: Arduino Mega

PTB7_EXTAL

compatible headers.

20

18

16

14

12

10

16

14

12

10

20

18

16

14

12

10

8

6

4

2

8

6

4

2

8

6

4

2

J1 J6 R91 1.0M

J2 CON 2X8

CAD NOTE:

PLACE NEAR TO PROCESSOR. Y3

19

17

15

13

11

9

7

5

3

1

19

17

15

13

11

9

7

5

3

1

NOTE: R539 0 DNP 1 2

P[3,6] PTA3

15

13

11

9

7

5

3

1

PTA2 and PTA3 I2C via LPI2C R540 0 DNP

PTE10 and PTE11 I2C via FLEXIO P[3,6] PTA2

PTD0 P[3,6] 8MHZ

P[3,6] PTE10 R567 0 SH13 0 PTD2 P[3] C126 C127

R568 0 12PF 12PF

P[3,6] PTE11 PTD9 P[3]

P[3] AREF PTD8 P[3]

PTC8 P[3]

P[3] PTB2 PTC9 P[3]

P[3] PTB3 PTD17 P[3]

GND P[3] PTB4 PTE12 P[3]

NOTE: J2-15.

R134, place it by deafult for extra

P[3]

P[3]

PTB5

PTD14

PTA8

PTA9

P[3]

P[3]

XTAL

GPIO/PWM. P[3] PTD13

R135, place it and remove R134 to have

CMP functionality.

P[3,6] PTE8 R135 0 DNP

NOTE: J2-13. R134 0 Note J5-1:

R133, place it by deafult for extra P[3] PTC11 R167 place it by defualt for

C R132 0 DNP NOTE: J4-9, J4-11 VDD C

GPIO/PWM. P[3,6] PTC3 R146, and R147 placed by deafult, ADC channel.

P[3] PTC10 R133 0

R132, place it and remove R133 to have remove and place R544 and R543 for R168 place it and remove R167

CMP functionality. P[3] PTB11 I2C functionality with FLEXIO or when using FSL BLDC shield.

P[3] PTB10 place PTA2 and PTA3 for LPI2C . TP5

Note J5-3:

P[3] PTB9

1

R165 place it by defualt for R13

P[3] PTB8 ADC channel.

P[3,6] PTA3 SH12 0

SH11 0 R544 0 DNP R166 place it and remove R165 2

P[3,6] PTA2 PTE11 P[3,6] when using FSL BLDC shield. ADC0_SE12 P[3]

R542 0 DNP PTA2 P[3,6]

P[3] PTE6 5K

P[3] PTE2 R543 0 DNP PTE10 P[3,6]

3

P[3,6] PTC0 R146 0 R541 0 DNP PTA3 P[3,6] R168 0 DNP PTD11 P[3,6] C5

P[3] PTA6 R147 0 R167 0 PTA15 P[3]

P[3] PTB1 0.1UF

P3V3 P5V0 P[3] PTB0 R166 0 DNP PTD10 P[3,6]

P[3] PTB12 R165 0 PTA16 P[3]

P[3] PTD4 PTA1 P[3]

VDD VIN

PTA0

PTA7

P[3]

P[3]

POTENTIOMETER

PTB13 P[3]

PTC1 P[3,6]

P[3,4,5] RST_TGTMCU_B VIN PTC2 P[3,6]

C49

11

13

15

11

13

15

11

13

15

17

19

1

3

5

7

9

1

3

5

7

9

1

3

5

7

9

2.2UF

J3 J4 J5

CON 2X8 CON 2X8

VDD

2

4

6

8

10

12

14

16

18

20

2

4

6

8

10

12

14

16

2

4

6

8

10

12

14

16

P[3,6] PTB6 R81 0 DNP PTC15 P[3]

P[3,6] PTB7 R90 0 DNP PTD6 P[3]

B P[3] PTE0 PTD7 P[3] B

P[3] PTE9 PTE1 P[3]

P[3] PTC5

P[3] PTC4

P[3] PTA10 R545 0 DNP PTE13 P[3]

P[3] PTA4 R546 0 DNP PTE14 P[3]

PTE15 P[3]

P[3] PTC7 PTE16 P[3]

P[3] PTC6

P[3] PTB17

P[3] PTB14

P[3] PTB15

P[3] PTB16

P[3] PTC14

P[3,6] PTC3

VDD

D11

A1 C1 LEDRGB_RED R97 RGB_RED P[3]

TP30 220

VDD VDD

A2 C2 LEDRGB_GREEN R96 RGB_GREEN P[3]

SW3 SW2 TP29 220

C533 R533 0 PTC3 P[3,6] C535 R534 0 PTC0 P[3,6]

1 2 1 2 10pF 10pF A3 C3 LEDRGB_BLUE R95 RGB_BLUE P[3]

3 4 3 4 TP28 220

EVQ-P2402W EVQ-P2402W R525 R528

BTN1 P[3] BTN0 P[3] 4.7K 4.7K LED RED/GRN/BL

R74 R44

10.0K C28

0.1UF

10.0K C16

0.1UF

SW7 SW8

RGB LED

P[3,6] PTC1 R172 0 1 P[3,6] PTC2 R527 01

CAD NOTE: Place electrodes next to each

other, electrodes spacing at least 5mm, Electrode Electrode

A A

10mm preferred.

USER BUTTONS Keep a space between electrodes and GND

plane of 3mm.

Do not place traces underneath the TOUCH PADS

electrodes.

ICAP Classification: FCP: ___ FIUO: X PUBI: ___

Drawing Title:

S32K144EVB-Q100

Page Title:

I/O Headers

Size Document Number Rev

C SCH-29248 PDF: SPF-29248 B

Date: Friday, September 02, 2016 Sheet 6 of 6

5 4 3 2 1

Вам также может понравиться

- Advance Excel Formula For All UsersДокумент66 страницAdvance Excel Formula For All UsersArjun100% (2)

- Advanced Document Scanner Parts Reference ListДокумент17 страницAdvanced Document Scanner Parts Reference ListPaul Albu100% (1)

- Hypermesh Basics Tutorials-1Документ40 страницHypermesh Basics Tutorials-1api-3717939100% (8)

- Error Code Printer CanonДокумент3 страницыError Code Printer CanonLaras Ahmad Stoedioe100% (1)

- Realize The Full Potential of Artificial IntelligenceДокумент32 страницыRealize The Full Potential of Artificial IntelligencemajowkaОценок пока нет

- S32k144evb SCH 29248 RBДокумент6 страницS32k144evb SCH 29248 RB정현우Оценок пока нет

- Freedom BLDC Motor Driver Shield Block DiagramДокумент6 страницFreedom BLDC Motor Driver Shield Block DiagramVitaliy BespalovОценок пока нет

- Cy8cproto 062 4343w SchematicДокумент8 страницCy8cproto 062 4343w SchematicAymane FahmiОценок пока нет

- SPF-47236 A1Документ6 страницSPF-47236 A1정현우Оценок пока нет

- Iphone 6 Plus 5.5'' 820-3675 051-0517 N56 MLB Rev 6.0.0 - 05.09.2014 Schematic DiagramДокумент55 страницIphone 6 Plus 5.5'' 820-3675 051-0517 N56 MLB Rev 6.0.0 - 05.09.2014 Schematic DiagramJose Perez GarciaОценок пока нет

- FRDM Ke02z SCHДокумент5 страницFRDM Ke02z SCHmichaelОценок пока нет

- Orange Pi PC Power Schematic Revision HistoryДокумент15 страницOrange Pi PC Power Schematic Revision HistoryMark SorianoОценок пока нет

- Revision History: Schematics IndexДокумент15 страницRevision History: Schematics IndexMarcello AlmeidaОценок пока нет

- DEVKIT-MPC5744P Schematic - RevB (SCH-29333) PDFДокумент10 страницDEVKIT-MPC5744P Schematic - RevB (SCH-29333) PDFPhuRioОценок пока нет

- DEVKIT-MPC5744P Schematic - RevB (SCH-29333)Документ10 страницDEVKIT-MPC5744P Schematic - RevB (SCH-29333)PhuRioОценок пока нет

- FRDM k22f SCHДокумент5 страницFRDM k22f SCHnagapenmetsaОценок пока нет

- ADC32RFXXEVM-SCH_DДокумент10 страницADC32RFXXEVM-SCH_Daprince6311Оценок пока нет

- Anexo 3 - Orange Pi - Zero2 - H616 - Schematic - v1.3Документ11 страницAnexo 3 - Orange Pi - Zero2 - H616 - Schematic - v1.3drmwndrrОценок пока нет

- FOXCONN - 865a05Документ39 страницFOXCONN - 865a05Guillermo OspinaОценок пока нет

- CY8CKIT-028-EPD SchematicДокумент4 страницыCY8CKIT-028-EPD SchematicAshwin MahoneyОценок пока нет

- MK21 MCU & Peripheral Power and Ground NetsДокумент8 страницMK21 MCU & Peripheral Power and Ground NetsEvgeniKosakovskiОценок пока нет

- Document Title: Revision: Vendor Rev.: Facility Identifier: Discipline: Document Type: Project Doc. Number: Vendor Doc. NumberДокумент4 страницыDocument Title: Revision: Vendor Rev.: Facility Identifier: Discipline: Document Type: Project Doc. Number: Vendor Doc. Numberrajindo1Оценок пока нет

- Schematic Page 1 2 Notes 3: A Original Release Designer DateДокумент3 страницыSchematic Page 1 2 Notes 3: A Original Release Designer DateAhsan ShabbirОценок пока нет

- M5 STACK CORE COVER PAGEДокумент6 страницM5 STACK CORE COVER PAGED RuОценок пока нет

- SPF-28011 A1Документ5 страницSPF-28011 A1BOLFRAОценок пока нет

- Compal LA-5151P KAT00 Discrete VGA POITIER Montevina M96-M92 Dell Studio 1745 PDFДокумент60 страницCompal LA-5151P KAT00 Discrete VGA POITIER Montevina M96-M92 Dell Studio 1745 PDFMichael Davenport0% (1)

- La A301pДокумент51 страницаLa A301pDENSОценок пока нет

- Val90 La-9931pДокумент62 страницыVal90 La-9931pPhan ThanhОценок пока нет

- IPC-P01-Z02-sch-2022Документ17 страницIPC-P01-Z02-sch-2022Rostislav NikitinОценок пока нет

- Schematic Laser Light Security Alarm LLSS Circuit 20180505224459Документ1 страницаSchematic Laser Light Security Alarm LLSS Circuit 20180505224459Anonymous TvppppОценок пока нет

- GPIO ASSIGNMENT TITLEДокумент14 страницGPIO ASSIGNMENT TITLEmaicuongdt2Оценок пока нет

- 04 Board Schematic DEMO9S08AW60Документ5 страниц04 Board Schematic DEMO9S08AW60IONUȚ-DRAGOȘ NEREMZOIUОценок пока нет

- OMF405 425 450 SCHДокумент5 страницOMF405 425 450 SCHNosdan LemosОценок пока нет

- SPF 27486 Kit33813 SCHДокумент3 страницыSPF 27486 Kit33813 SCH刘杰Оценок пока нет

- Orange Pi Zero v1 11Документ12 страницOrange Pi Zero v1 11JederVieiraОценок пока нет

- Compal La-5461p r1.0 SchematicsДокумент21 страницаCompal La-5461p r1.0 SchematicsDiego LopezОценок пока нет

- ODU-BB-SCHДокумент38 страницODU-BB-SCHArjun TiwariОценок пока нет

- Aegis M/B schematics page DESCRДокумент62 страницыAegis M/B schematics page DESCRGleison GomesОценок пока нет

- PCA10040 Schematic and PCB PDFДокумент12 страницPCA10040 Schematic and PCB PDFtestОценок пока нет

- Dell Alienware 17 R4 Compal La-D753p Bap20 Rev 0.2 (X01)Документ82 страницыDell Alienware 17 R4 Compal La-D753p Bap20 Rev 0.2 (X01)Hoang Tran Huy100% (1)

- Alto A1000.4 Power Amp Service Manual PDFДокумент28 страницAlto A1000.4 Power Amp Service Manual PDFmundomusicalmeriaОценок пока нет

- Interfacing diagram of key componentsДокумент24 страницыInterfacing diagram of key componentsChandrashekar ReddyОценок пока нет

- Schematic M/B LA-8321Документ67 страницSchematic M/B LA-8321Hh woo't hoofОценок пока нет

- General Arrangement DiagramДокумент2 страницыGeneral Arrangement DiagramsubudhiprasannaОценок пока нет

- RDDRONE-BMS772 NotesДокумент9 страницRDDRONE-BMS772 Notesa9841140155Оценок пока нет

- Acer 8481 La-7361p R1.0Документ65 страницAcer 8481 La-7361p R1.0ziegatiОценок пока нет

- AAV8790601-00 MergedДокумент7 страницAAV8790601-00 Mergedengineeringcem99Оценок пока нет

- Rogue-2 SHB SVT Logic SchematicsДокумент77 страницRogue-2 SHB SVT Logic SchematicsPopa MarinОценок пока нет

- Dell Latitude E6440Документ62 страницыDell Latitude E6440ivanka petrova0% (1)

- Dell La-9931p PDFДокумент62 страницыDell La-9931p PDFFabregas RonaldОценок пока нет

- Fujitsu Siemens Pi1505 Uniwill L50II0 RevB SchematicДокумент33 страницыFujitsu Siemens Pi1505 Uniwill L50II0 RevB SchematicmigsantОценок пока нет

- Compal Cdl50 La-D707p Rev 0.2Документ60 страницCompal Cdl50 La-D707p Rev 0.2Julio BelloОценок пока нет

- PJ-2Документ1 страницаPJ-2kizdavОценок пока нет

- Tarjmadredell Insp5520Документ57 страницTarjmadredell Insp5520Gabriel Gamez100% (1)

- TB 96ai SchematicsДокумент23 страницыTB 96ai Schematicsvenugopal mОценок пока нет

- Compal La 6552p r1 Schematics PDFДокумент46 страницCompal La 6552p r1 Schematics PDFMihael PolakОценок пока нет

- COMPAL LS-3807P (JBL00, JBL01, JBL02) 2008-06-10, Rev 1.0 (A00) - Sniffer Board PDFДокумент4 страницыCOMPAL LS-3807P (JBL00, JBL01, JBL02) 2008-06-10, Rev 1.0 (A00) - Sniffer Board PDFGerman ValenciaОценок пока нет

- BLE-UNO SchematicДокумент4 страницыBLE-UNO Schematiclamine mhamedОценок пока нет

- QCG Pe 2020-02Документ13 страницQCG Pe 2020-02Roosevelt A. SantosОценок пока нет

- Token Ring Technology ReportОт EverandToken Ring Technology ReportОценок пока нет

- Anglo–American Microelectronics Data 1968–69: Manufacturers A–PОт EverandAnglo–American Microelectronics Data 1968–69: Manufacturers A–PОценок пока нет

- MCAL SampleApplicationДокумент27 страницMCAL SampleApplicationIonuţ Hw100% (1)

- Artistcloud Overall UpperДокумент1 страницаArtistcloud Overall UpperIonuţ HwОценок пока нет

- Raspunsuri Mid-TermДокумент19 страницRaspunsuri Mid-TermIonuţ HwОценок пока нет

- A Comparative Study of In-Sensor ProcessingДокумент6 страницA Comparative Study of In-Sensor ProcessingIonuţ HwОценок пока нет

- A Comparative Analysis of BLE and 6LoWPAN For U-HealthCare ApplicationsДокумент6 страницA Comparative Analysis of BLE and 6LoWPAN For U-HealthCare ApplicationsIonuţ HwОценок пока нет

- STR91xfirmare LibraryДокумент303 страницыSTR91xfirmare LibraryIonuţ HwОценок пока нет

- Linux Mint - Docs - 01 - English - 11.1Документ50 страницLinux Mint - Docs - 01 - English - 11.1bolamoОценок пока нет

- Database Management System: Practical FileДокумент24 страницыDatabase Management System: Practical FileAastha GroverОценок пока нет

- Lab ManualДокумент13 страницLab ManualakhilОценок пока нет

- Universal Orlando Resort Error Message GuideДокумент16 страницUniversal Orlando Resort Error Message Guidemanjunathganguly771275Оценок пока нет

- A 2D Electromagnetic Scattering Solver For MatlabДокумент23 страницыA 2D Electromagnetic Scattering Solver For MatlabjalopeztОценок пока нет

- 100 Cloze Test QuestionsДокумент21 страница100 Cloze Test QuestionsDeekshit KumarОценок пока нет

- Project Report on Summer Training at Panasonic Battery India Co. LtdДокумент53 страницыProject Report on Summer Training at Panasonic Battery India Co. LtdnaranahirОценок пока нет

- Computer Network Architecture GuideДокумент19 страницComputer Network Architecture GuideCarl CarlОценок пока нет

- Johnny Sha ResumeДокумент2 страницыJohnny Sha ResumeJohnny ShaОценок пока нет

- Book BankДокумент10 страницBook Bank02 - Adwin PrajishaОценок пока нет

- Zilog DatasheetДокумент282 страницыZilog DatasheetmaazioОценок пока нет

- Bli 221b1e PDFДокумент115 страницBli 221b1e PDFKhalid Sayeed0% (1)

- MSP 34x0G Multistandard Sound Processor Family: MicronasДокумент106 страницMSP 34x0G Multistandard Sound Processor Family: MicronasasistekОценок пока нет

- Avinash Singh (Resume)Документ2 страницыAvinash Singh (Resume)AvinashSingh100% (2)

- 8086 Bios and Dos Interrupts (IBM PC)Документ20 страниц8086 Bios and Dos Interrupts (IBM PC)tonynascОценок пока нет

- AttachmentДокумент258 страницAttachmentJaime EduardoОценок пока нет

- What is JavaScript: A beginner's guideДокумент45 страницWhat is JavaScript: A beginner's guidedevendraОценок пока нет

- Animation: COM269 Multiplatform Interactive Design Wan Anis Aqilah Megat ZambriДокумент23 страницыAnimation: COM269 Multiplatform Interactive Design Wan Anis Aqilah Megat ZambriAhmad Shah BullahОценок пока нет

- Global Maintenance and Reliability Indicators - Flyer - GMARI - V3 PDFДокумент2 страницыGlobal Maintenance and Reliability Indicators - Flyer - GMARI - V3 PDFgecko232243100% (1)

- Unit 7 Protection and SecurityДокумент18 страницUnit 7 Protection and SecurityMeghana AmmuОценок пока нет

- Getting Started in IAB (061-120)Документ60 страницGetting Started in IAB (061-120)Anh Kha Võ DânОценок пока нет

- Accelerating Convolutional Neural Networks Via Activation Map CompressionДокумент12 страницAccelerating Convolutional Neural Networks Via Activation Map CompressionAskar MyktybekovОценок пока нет

- TADIG Code Naming ConventionsДокумент18 страницTADIG Code Naming ConventionsivopiskovОценок пока нет

- Gulliver: Automations For Collective and Industrial Sliding GatesДокумент6 страницGulliver: Automations For Collective and Industrial Sliding Gatesmohammad maraghaОценок пока нет

- "Quo Teinp Ut" "Color Outpu T" "Col Orin Put" "Fontf Amilyi Nput" "Feed Backo Utput" "Quo Teou Tput" "Font Sizei Nput"Документ3 страницы"Quo Teinp Ut" "Color Outpu T" "Col Orin Put" "Fontf Amilyi Nput" "Feed Backo Utput" "Quo Teou Tput" "Font Sizei Nput"colin leachОценок пока нет

- Jawaban Latihan Soal Sistem Basis DataДокумент3 страницыJawaban Latihan Soal Sistem Basis DataRizki Rian AnugrahaniОценок пока нет

- Development of QR-code Based Interactive Dynamic Billboard System With Motion DetectionДокумент10 страницDevelopment of QR-code Based Interactive Dynamic Billboard System With Motion DetectionEditor IjasreОценок пока нет