Академический Документы

Профессиональный Документы

Культура Документы

TC4421-22 Datasheet

Загружено:

shreeblr79Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

TC4421-22 Datasheet

Загружено:

shreeblr79Авторское право:

Доступные форматы

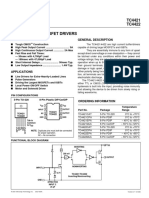

TC4421A/TC4422A

9A High-Speed MOSFET Drivers

Features General Description

• High Peak Output Current: 10A (typ.) The TC4421A/TC4422A are improved versions of the

• Low Shoot-Through/Cross-Conduction Current in earlier TC4421/TC4422 family of single-output

Output Stage MOSFET drivers. These devices are high-current buf-

• Wide Input Supply Voltage Operating Range: fer/drivers capable of driving large MOSFETs and Insu-

lated Gate Bipolar Transistors (IGBTs). The

- 4.5V to 18V

TC4421A/TC4422A have matched output rise and fall

• High Continuous Output Current: 2A (max.) times, as well as matched leading and falling-edge

• Matched Fast Rise and Fall Times: propagation delay times. The TC4421A/TC4422A

- 15 ns with 4,700 pF Load devices also have very low cross-conduction current,

- 135 ns with 47,000 pF Load reducing the overall power dissipation of the device.

• Matched Short Propagation Delays: 42 ns (typ.) These devices are essentially immune to any form of

• Low Supply Current: upset, except direct overvoltage or over-dissipation.

They cannot be latched under any conditions within

- With Logic ‘1’ Input – 130 µA (typ.)

their power and voltage ratings. These parts are not

- With Logic ‘0’ Input – 33 µA (typ.) subject to damage or improper operation when up to

• Low Output Impedance: 1.2 (typ.) 5V of ground bounce is present on their ground

• Latch-Up Protected: Will Withstand 1.5A Output terminals. They can accept, without damage or logic

Reverse Current upset, more than 1A inductive current of either polarity

• Input Will Withstand Negative Inputs Up To 5V being forced back into their outputs. In addition, all

• Pin-Compatible with the TC4420/TC4429 terminals are fully protected against up to 4 kV of

and TC4421/TC4422 MOSFET Drivers electrostatic discharge.

• Space-Saving, Thermally-Enhanced, 8-Pin DFN The TC4421A/TC4422A inputs may be driven directly

Package from either TTL or CMOS (3V to 18V). In addition,

300 mV of hysteresis is built into the input, providing

Applications noise immunity and allowing the device to be driven

from slowly rising or falling waveforms.

• Line Drivers for Extra Heavily-Loaded Lines

With both surface-mount and pin-through-hole

• Pulse Generators

packages, in addition to a wide operating temperature

• Driving the Largest MOSFETs and IGBTs range, the TC4421A/TC4422A family of 9A MOSFET

• Local Power ON/OFF Switch drivers fit into most any application where high gate/line

• Motor and Solenoid Driver capacitance drive is required.

• LF Initiator

Package Types(1)

8-Pin TC4421A TC4422A 8-Pin DFN(2) TC4421A TC4422A 5-Pin TO-220

PDIP/SOIC

Tab is

VDD 1 8 VDD VDD Common

VDD 1 8 VDD VDD

INPUT 2 TC4421A 7 OUTPUT OUTPUT INPUT 2 to VDD

TC4421A 7 OUTPUT OUTPUT

NC 3 TC4422A 6 OUTPUT OUTPUT TC4422A TC4421A

NC 3 6 OUTPUT OUTPUT

GND 4 5 GND GND TC4422A

GND 4 5 GND GND

OUTPUT

GND

VDD

INPUT

GND

Note 1: Duplicate pins must both be connected for proper operation.

2: Exposed pad of the DFN package is electrically isolated.

2005-2013 Microchip Technology Inc. DS21946B-page 1

TC4421A/TC4422A

Functional Block Diagram

VDD

TC4421A

Inverting

130 µA

300 mV Output

Cross-Conduction

Reduction and Pre-Drive Output

Circuitry

Input TC4422A

Non-Inverting

4.7V

GND

Effective

Input

C = 25 pF

DS21946B-page 2 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

1.0 ELECTRICAL † Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device. These

CHARACTERISTICS are stress ratings only and functional operation of the device

at these or any other conditions above those indicated in the

Absolute Maximum Ratings † operation sections of the specifications is not implied.

Exposure to Absolute Maximum Rating conditions for

Supply Voltage ..................................................... +20V extended periods may affect device reliability.

Input Voltage .................... (VDD + 0.3V) to (GND – 5V)

Input Current (VIN > VDD)................................... 50 mA

DC CHARACTERISTICS

Electrical Specifications: Unless otherwise noted, TA = +25°C with 4.5V VDD 18V.

Parameters Sym Min Typ Max Units Conditions

Input

Logic ‘1’, High Input Voltage VIH 2.4 1.8 — V

Logic ‘0’, Low Input Voltage VIL — 1.3 0.8 V

Input Current IIN –10 — +10 µA 0VVINVDD

Input Voltage VIN –5 — VDD – 0.3 V

Output

High Output Voltage VOH VDD – 0.025 — — V DC Test

Low Output Voltage VOL — — 0.025 V DC Test

Output Resistance, High ROH — 1.25 1.5 IOUT = 10 mA, VDD = 18V

Output Resistance, Low ROL — 0.8 1.1 IOUT = 10 mA, VDD = 18V

Peak Output Current IPK — 10.0 — A VDD = 18V

Continuous Output Current IDC 2 — — A 10V VDD 18V, TA = +25°C

(TC4421A/TC4422A CAT only)

(Note 2)

Latch-Up Protection IREV — >1.5 — A Duty cycle2%, t 300 µsec

Withstand Reverse Current

Switching Time (Note 1)

Rise Time tR — 28 34 ns Figure 4-1, CL = 10,000 pF

Fall Time tF — 26 32 ns Figure 4-1, CL = 10,000 pF

Propagation Delay Time tD1 — 38 45 ns Figure 4-1, CL = 10,000 pF

Propagation Delay Time tD2 — 42 49 ns Figure 4-1, CL = 10,000 pF

Power Supply

Power Supply Current IS — 130 250 µA VIN = 3V

— 35 100 µA VIN = 0V

Operating Input Voltage VDD 4.5 — 18 V

Note 1: Switching times ensured by design.

2: Tested during characterization, not production tested.

2005-2013 Microchip Technology Inc. DS21946B-page 3

TC4421A/TC4422A

DC CHARACTERISTICS (OVER OPERATING TEMPERATURE RANGE)

Electrical Specifications: Unless otherwise noted, over operating temperature range with 4.5V VDD 18V.

Parameters Sym Min Typ Max Units Conditions

Input

Logic ‘1’, High Input Voltage VIH 2.4 — — V

Logic ‘0’, Low Input Voltage VIL — — 0.8 V

Input Current IIN –10 — +10 µA 0VVINVDD

Output

High Output Voltage VOH VDD – 0.025 — — V DC Test

Low Output Voltage VOL — — 0.025 V DC Test

Output Resistance, High ROH — — 2.0 IOUT = 10 mA, VDD = 18V

Output Resistance, Low ROL — — 1.6 IOUT = 10 mA, VDD = 18V

Switching Time (Note 1)

Rise Time tR — 38 45 ns Figure 4-1, CL = 10,000 pF

Fall Time tF — 33 40 ns Figure 4-1, CL = 10,000 pF

Propagation Delay Time tD1 — 50.4 60 ns Figure 4-1, CL = 10,000 pF

Propagation Delay Time tD2 — 53 60 ns Figure 4-1, CL = 10,000 pF

Power Supply

Power Supply Current IS — 200 500 µA VIN = 3V

— 50 150 µA VIN = 0V

Operating Input Voltage VDD 4.5 — 18 V

Note 1: Switching times ensured by design.

TEMPERATURE CHARACTERISTICS

Electrical Specifications: Unless otherwise noted, all parameters apply with 4.5V VDD 18V.

Parameters Sym Min Typ Max Units Conditions

Temperature Ranges

Specified Temperature Range (V) TA –40 — +125 °C

Maximum Junction Temperature TJ — — +150 °C

Storage Temperature Range TA –65 — +150 °C

Package Thermal Resistances

Thermal Resistance, 5L-TO-220 JA — 71 — °C/W Without heat sink

Thermal Resistance, 8L-6x5 DFN JA — 33.2 — °C/W Typical 4-layer board with

vias to ground plane

Thermal Resistance, 8L-PDIP JA — 125 — °C/W

Thermal Resistance, 8L-SOIC JA — 155 — °C/W

DS21946B-page 4 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein

are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise indicated, TA = +25°C with 4.5V VDD 18V.

180 300

160

250

140

Rise Time (ns)

5V

Fall Time (ns)

22,000 pF

120 200

100

150 10V

80

60 10,000 pF 100

15V

40

1,000 pF 50

20 100 pF

0 0

4 6 8 10 12 14 16 18 100 1000 10000 100000

Supply Voltage (V) Capacitive Load (pF)

FIGURE 2-1: Rise Time vs. Supply FIGURE 2-4: Fall Time vs. Capacitive

Voltage. Load.

300 55

VDD = 15V

250 50

5V

Rise Time (ns)

45

200

Time (ns)

10V 40

150 tRISE

35

100

15V 30 tFALL

50 25

0 20

100 1000 10000 100000 -40 -25 -10 5 20 35 50 65 80 95 110 125

Capacitive Load (pF) Temperature (°C)

FIGURE 2-2: Rise Time vs. Capacitive FIGURE 2-5: Rise and Fall Times vs.

Load. Temperature.

180 10-7

1E-7

Crossover Energy (A·sec)

160

140

Fall Time (ns)

120

22,000 pF

100

10-8

1E-8

80

60 10,000 pF

40

20 1,000 pF 100 pF

0 10-9

1E-9

4 6 8 10 12 14 16 18 4 6 8 10 12 14 16 18

Supply Voltage (V) Supply Voltage (V)

FIGURE 2-3: Fall Time vs. Supply FIGURE 2-6: Crossover Energy vs Supply

Voltage. Voltage.

2005-2013 Microchip Technology Inc. DS21946B-page 5

TC4421A/TC4422A

Note: Unless otherwise indicated, TA = +25°C with 4.5V VDD 18V.

80 140

CLOAD = 10,000 pF

75

Propagation Delay (nS)

120

70

INPUT = High

IQUIESCENT (µA)

65 100

60

55 80

50 tD2

45 60

40 tD1 INPUT = Low

40

35

30 20

4 6 8 10 12 14 16 18 4 6 8 10 12 14 16 18

Supply Voltage (V) Supply Voltage (V)

FIGURE 2-7: Propagation Delay vs. FIGURE 2-10: Quiescent Supply Current

Supply Voltage. vs. Supply Voltage.

75 220

VDD = 12V VDD = 18V

200

Propagation Delay (ns)

70

180

65

IQUIESCENT (µA)

160

INPUT = High

60 140

120

55 100

50 tD2 80

INPUT = Low

60

45 tD1

40

40 20

2 3 4 5 6 7 8 9 10 -40 -25 -10 5 20 35 50 65 80 95 110 125

Input Amplitude (V) Temperature (°C)

FIGURE 2-8: Propagation Delay vs. Input FIGURE 2-11: Quiescent Supply Current

Amplitude. vs. Temperature.

60 2.0

VDD = 12V VDD = 12V

1.9

Propagation Delay (ns)

VIN = 5V

55

Input Threshold (V)

CLOAD = 10,000 pF 1.8

50 1.7

tD2

1.6 VIH

45 1.5

tD1 1.4

40 1.3

VIL

35 1.2

1.1

30 1.0

-40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125

Temperature (°C) Temperature (°C)

FIGURE 2-9: Propagation Delay vs. FIGURE 2-12: Input Threshold vs.

Temperature. Temperature.

DS21946B-page 6 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

Note: Unless otherwise indicated, TA = +25°C with 4.5V VDD 18V.

2.0 180

VDD = 18V

1.9 160

Supply Current (mA)

200 kHz

Input Threshold (V)

1.8 140

1.7 120 2 MHz

1 MHz

1.6 VIH

100

1.5 100 kHz

80

1.4

1.3 60 50 kHz

VIL 40

1.2 10 kHz

1.1 20

1.0 0

4 6 8 10 12 14 16 18 100 1,000 10,000 100,000

Supply Voltage (V) Capacitive Load (pF)

FIGURE 2-13: Input Threshold vs. Supply FIGURE 2-16: Supply Current vs.

Voltage. Capactive Load (VDD = 18V).

5.0 200

VIN = 5V (TC4422A) VDD = 12V

4.5 VIN = 0V (TC4421A) 180

Supply Current (mA)

4.0 160

3.5 140 200 kHz

ROUT-HI (:)

3.0 TJ = 150°C 120

2 MHz

2.5 100 1 MHz 100 kHz

2.0 80

1.5 TJ = 25°C 60 50 kHz

1.0 40

0.5 20 10 kHz

0.0 0

4 6 8 10 12 14 16 18 100 1,000 10,000 100,000

Supply Voltage (V) Capacitive Load (pF)

FIGURE 2-14: High-State Output FIGURE 2-17: Supply Current vs.

Resistance vs. Supply Voltage. Capactive Load (VDD = 12V).

3.5 220

VIN = 0V (TC4422A) VDD = 6V

VIN = 5V (TC4421A)

200

3.0

Supply Current (mA)

180 1 MHz

2.5 160

TJ = 150°C

ROUT-LO (:)

140 2 MHz

2.0 120

200 kHz

1.5 100

100 kHz

80

1.0 TJ = 25°C 60 50 kHz

40

0.5 10 kHz

20

0.0 0

4 6 8 10 12 14 16 18 100 1,000 10,000 100,000

Supply Voltage (V) Capacitive Load (pF)

FIGURE 2-15: Low-State Output FIGURE 2-18: Supply Current vs.

Resistance vs. Supply Voltage. Capactive Load (VDD = 6V).

2005-2013 Microchip Technology Inc. DS21946B-page 7

TC4421A/TC4422A

Note: Unless otherwise indicated, TA = +25°C with 4.5V VDD 18V.

180 220

VDD = 18V VDD = 6V

160 10,000 pF 200

22,000 pF

Supply Current (mA)

Supply Current (mA)

47,000 pF 180 47,000 pF

140

22,000 pF 160

120 1000 pF 140

100 0.1 µF 120 10,000 pF

80 100 0.1 µF

60 80

60

40 470 pF 1000 pF

40

20 20 470 pF

0 0

10 100 1000 10000 10 100 1000 10000

Frequency (kHz) Frequency (kHz)

FIGURE 2-19: Supply Current vs. FIGURE 2-21: Supply Current vs.

Frequency (VDD = 18V). Frequency (VDD = 6V).

200

VDD = 12V

180 10,000 pF

Supply Current (mA)

160 47,000 pF

140

120 22,000 pF

100

0.1 µF 1000 pF

80

60

40

470 pF

20

0

10 100 1000 10000

Frequency (kHz)

FIGURE 2-20: Supply Current vs.

Frequency (VDD = 12V).

DS21946B-page 8 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

Pin No.

Pin No. Pin No.

8-Pin PDIP, Symbol Description

8-Pin DFN 5-Pin TO-220

SOIC

1 1 — VDD Supply input, 4.5V to 18V

2 2 1 INPUT Control input, TTL/CMOS-compatible input

3 3 — NC No connection

4 4 2 GND Ground

5 5 4 GND Ground

6 6 5 OUTPUT CMOS push-pull output

7 7 — OUTPUT CMOS push-pull output

8 8 3 VDD Supply input, 4.5V to 18V

— PAD — NC Exposed metal pad

— — TAB VDD Metal tab is at the VDD potential

3.1 Supply Input (VDD) 3.3 CMOS Push-Pull Output

The VDD input is the bias supply for the MOSFET driver The MOSFET driver output is a low-impedance,

and is rated for 4.5V to 18V with respect to the ground CMOS, push-pull style output capable of driving a

pin. The VDD input should be bypassed to ground with capacitive load with 9.0A peak currents. The MOSFET

a local ceramic capacitor. The value of the capacitor driver output is capable of withstanding 1.5A peak

should be chosen based on the capacitive load that is reverse currents of either polarity.

being driven. A minimum value of 1.0 µF is suggested.

3.4 Ground

3.2 Control Input

The ground pins are the return path for the bias current

The MOSFET driver input is a high-impedance, and for the high peak currents that discharge the load

TTL/CMOS-compatible input. The input also has capacitor. The ground pins should be tied into a ground

300 mV of hysteresis between the high and low plane or have very short traces to the bias supply

thresholds that prevents output glitching even when the source return.

rise and fall time of the input signal is very slow.

3.5 Exposed Metal Pad

The exposed metal pad of the 6x5 DFN package is not

internally connected to any potential. Therefore, this

pad can be connected to a ground plane or other

copper plane on a Printed Circuit Board (PCB) to aid in

heat removal from the package.

3.6 Metal Tab

The metal tab of the TO-220 package is connected to

the VDD potential of the device. This connection to VDD

can be used as a current carrying path for the device.

2005-2013 Microchip Technology Inc. DS21946B-page 9

TC4421A/TC4422A

4.0 APPLICATIONS INFORMATION

+5V

90%

Input

VDD = 18V 10%

0V

tD1 tD2

tF tR

0.1 µF +18V

0.1 µF 4.7 µF 90% 90%

1 8 Output

VDD VDD 10% 10%

0V

Inverting Driver

Input 2 Input Output 6 Output TC4421A

Output 7

CL = 10,000 pF +5V

90%

GND GND Input

4 5

10%

0V

+18V 90%

tD1 90% tD2

Input: 100 kHz, Output tR tF

square wave,

0V 10% 10%

tRISE = tFALL 10 nsec

Non-Inverting Driver

Note: Pinout shown is for the DFN, PDIP and SOIC packages. TC4422A

FIGURE 4-1: Switching Time Test Circuits.

DS21946B-page 10 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

5.0 PACKAGING INFORMATION

5.1 Package Marking Information

5-Lead TO-220 Example:

XXXXXXXXX TC4421A

XXXXXXXXX e3

XXXXXXXXX

VAT^^

YYWWNNN 0514256

8-Lead DFN Example:

XXXXXXX TC4421A

XXXXXXX VMF^e3

XXYYWW 0514

NNN 256

8-Lead PDIP (300 mil) Example:

XXXXXXXX TC4421A

XXXXXNNN PA e^3 256

YYWW 0514

8-Lead SOIC (150 mil) Example:

XXXXXXXX TC4421A

XXXXYYWW SN e3 0514

NNN 256

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week ‘01’)

NNN Alphanumeric traceability code

e3 Pb-free JEDEC designator for Matte Tin (Sn)

* This package is Pb-free. The Pb-free JEDEC designator ( e3 )

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will

be carried over to the next line, thus limiting the number of available

characters for customer-specific information.

2005-2013 Microchip Technology Inc. DS21946B-page 11

TC4421A/TC4422A

5-Lead Plastic Transistor Outline (AT) (TO-220)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

L H1

Q

e3

e1 E

e

EJECTOR PIN ØP

a (5X)

C1

A

J1

F

D

Units INCHES* MILLIMETERS

Dimension Limits MIN MAX MIN MAX

Lead Pitch e .060 .072 1.52 1.83

Overall Lead Centers e1 .263 .273 6.68 6.93

Space Between Leads e3 .030 .040 0.76 1.02

Overall Height A .160 .190 4.06 4.83

Overall Width E .385 .415 9.78 10.54

Overall Length D .560 .590 14.22 14.99

Flag Length H1 .234 .258 5.94 6.55

Flag Thickness F .045 .055 1.14 1.40

Through Hole Center Q .103 .113 2.62 2.87

Through Hole Diameter P .146 .156 3.71 3.96

Lead Length L .540 .560 13.72 14.22

Base to Bottom of Lead J1 .090 .115 2.29 2.92

Lead Thickness C1 .014 .022 0.36 0.56

Lead Width b .025 .040 0.64 1.02

Mold Draft Angle a 3° 7° 3° 7°

*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or

protrusions shall not exceed .010" (0.254mm) per side.

JEDEC equivalent: TO-220

Drawing No. C04-036

DS21946B-page 12 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

8-Lead Plastic Dual Flat No Lead Package (MF) 6x5 mm Body (DFN-S) – Saw Singulated

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

2005-2013 Microchip Technology Inc. DS21946B-page 13

TC4421A/TC4422A

8-Lead Plastic Dual In-line (PA) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

E1

n 1

A A2

L

c

A1

B1

p

eB B

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 8 8

Pitch p .100 2.54

Top to Seating Plane A .140 .155 .170 3.56 3.94 4.32

Molded Package Thickness A2 .115 .130 .145 2.92 3.30 3.68

Base to Seating Plane A1 .015 0.38

Shoulder to Shoulder Width E .300 .313 .325 7.62 7.94 8.26

Molded Package Width E1 .240 .250 .260 6.10 6.35 6.60

Overall Length D .360 .373 .385 9.14 9.46 9.78

Tip to Seating Plane L .125 .130 .135 3.18 3.30 3.43

Lead Thickness c .008 .012 .015 0.20 0.29 0.38

Upper Lead Width B1 .045 .058 .070 1.14 1.46 1.78

Lower Lead Width B .014 .018 .022 0.36 0.46 0.56

Overall Row Spacing § eB .310 .370 .430 7.87 9.40 10.92

Mold Draft Angle Top 5 10 15 5 10 15

Mold Draft Angle Bottom 5 10 15 5 10 15

* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010” (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-018

DS21946B-page 14 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

8-Lead Plastic Small Outline (OA) – Narrow, 150 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

E1

D

2

B n 1

h

45

c

A A2

L A1

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 8 8

Pitch p .050 1.27

Overall Height A .053 .061 .069 1.35 1.55 1.75

Molded Package Thickness A2 .052 .056 .061 1.32 1.42 1.55

Standoff § A1 .004 .007 .010 0.10 0.18 0.25

Overall Width E .228 .237 .244 5.79 6.02 6.20

Molded Package Width E1 .146 .154 .157 3.71 3.91 3.99

Overall Length D .189 .193 .197 4.80 4.90 5.00

Chamfer Distance h .010 .015 .020 0.25 0.38 0.51

Foot Length L .019 .025 .030 0.48 0.62 0.76

Foot Angle 0 4 8 0 4 8

Lead Thickness c .008 .009 .010 0.20 0.23 0.25

Lead Width B .013 .017 .020 0.33 0.42 0.51

Mold Draft Angle Top 0 12 15 0 12 15

Mold Draft Angle Bottom 0 12 15 0 12 15

* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010” (0.254mm) per side.

JEDEC Equivalent: MS-012

Drawing No. C04-057

2005-2013 Microchip Technology Inc. DS21946B-page 15

TC4421A/TC4422A

NOTES:

DS21946B-page 16 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

APPENDIX A: REVISION HISTORY

Revision A (May 2005)

• Original Release of this Document.

Revision B (January 2013)

Added a note to each package outline drawing.

2005-2013 Microchip Technology Inc. DS21946B-page 17

TC4421A/TC4422A

NOTES:

DS21946B-page 18 l 2005-2013 Microchip Technology Inc.

TC4421A/TC4422A

PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

PART NO. X XX XXX Examples:

a) TC4421AVAT: 9A High-Speed Inverting

Device Temperature Package Tape & Reel MOSFET Driver,

Range TO-220 package,

-40°C to +125°C.

b) TC4421AVOA: 9A High-Speed Inverting

Device: TC4421A: 9A High-Speed MOSFET Driver, Inverting

TC4422A: 9A High-Speed MOSFET Driver, Non-Inverting MOSFET Driver,

SOIC package,

-40°C to +125°C.

Temperature Range: V = -40°C to +125°C c) TC4421AVMF: 9A High-Speed Inverting

MOSFET Driver,

Package: * AT = TO-220, 5-lead DFN package,

MF = Dual, Flat, No-Lead (6x5 mm Body), 8-lead -40°C to +125°C.

MF713 = Dual, Flat, No-Lead (6x5 mm Body), 8-lead

(Tape and Reel) a) TC4422AVPA: 9A High-Speed

PA = Plastic DIP (300 mil Body), 8-lead Non-Inverting MOSFET

OA = Plastic SOIC (150 mil Body), 8-lead Driver, PDIP package,

OA713 = Plastic SOIC (150 mil Body), 8-lead

-40°C to +125°C.

(Tape and Reel)

b) TC4422AVOA: 9A High-Speed

*All package offerings are Pb Free (Lead Free).

Non-Inverting

MOSFET Driver,

SOIC package,

-40°C to +125°C.

c) TC4422AVMF: 9A High-Speed

Non-Inverting MOSFET

Driver, DFN package,

-40°C to +125°C.

2005-2013 Microchip Technology Inc. DS21946B-page 19

TC4421A/TC4422A

NOTES:

DS21946B-page 20 2005-2013 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device Trademarks

applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, dsPIC,

and may be superseded by updates. It is your responsibility to

FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro,

ensure that your application meets with your specifications.

PICSTART, PIC32 logo, rfPIC, SST, SST Logo, SuperFlash

MICROCHIP MAKES NO REPRESENTATIONS OR and UNI/O are registered trademarks of Microchip Technology

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

Incorporated in the U.S.A. and other countries.

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

INCLUDING BUT NOT LIMITED TO ITS CONDITION, MTP, SEEVAL and The Embedded Control Solutions

QUALITY, PERFORMANCE, MERCHANTABILITY OR Company are registered trademarks of Microchip Technology

FITNESS FOR PURPOSE. Microchip disclaims all liability Incorporated in the U.S.A.

arising from this information and its use. Use of Microchip Silicon Storage Technology is a registered trademark of

devices in life support and/or safety applications is entirely at Microchip Technology Inc. in other countries.

the buyer’s risk, and the buyer agrees to defend, indemnify and

Analog-for-the-Digital Age, Application Maestro, BodyCom,

hold harmless Microchip from any and all damages, claims,

chipKIT, chipKIT logo, CodeGuard, dsPICDEM,

suits, or expenses resulting from such use. No licenses are

dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

conveyed, implicitly or otherwise, under any Microchip

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

intellectual property rights.

Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB

Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O,

Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA

and Z-Scale are trademarks of Microchip Technology

Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip

Technology Germany II GmbH & Co. & KG, a subsidiary of

Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

© 2005-2013, Microchip Technology Incorporated, Printed in

the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769218

QUALITY MANAGEMENT SYSTEM Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

CERTIFIED BY DNV Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

== ISO/TS 16949 ==

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2005-2013 Microchip Technology Inc. DS21946B-page 21

Worldwide Sales and Service

AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE

Corporate Office Asia Pacific Office India - Bangalore Austria - Wels

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-3090-4444 Tel: 43-7242-2244-39

Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-3090-4123 Fax: 43-7242-2244-393

Tel: 480-792-7200 Harbour City, Kowloon Denmark - Copenhagen

India - New Delhi

Fax: 480-792-7277 Hong Kong Tel: 45-4450-2828

Tel: 91-11-4160-8631

Technical Support: Tel: 852-2401-1200 Fax: 45-4485-2829

Fax: 91-11-4160-8632

http://www.microchip.com/ Fax: 852-2401-3431

India - Pune France - Paris

support

Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20

Web Address:

Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79

www.microchip.com

Fax: 61-2-9868-6755 Germany - Munich

Atlanta Japan - Osaka

China - Beijing Tel: 49-89-627-144-0

Duluth, GA Tel: 81-6-6152-7160

Tel: 86-10-8569-7000 Fax: 49-89-627-144-44

Tel: 678-957-9614 Fax: 81-6-6152-9310

Fax: 86-10-8528-2104 Italy - Milan

Fax: 678-957-1455 Japan - Tokyo

China - Chengdu Tel: 39-0331-742611

Boston Tel: 81-3-6880- 3770

Tel: 86-28-8665-5511 Fax: 39-0331-466781

Westborough, MA Fax: 81-3-6880-3771

Fax: 86-28-8665-7889 Netherlands - Drunen

Tel: 774-760-0087 Korea - Daegu

Fax: 774-760-0088 China - Chongqing Tel: 82-53-744-4301 Tel: 31-416-690399

Tel: 86-23-8980-9588 Fax: 82-53-744-4302 Fax: 31-416-690340

Chicago

Itasca, IL Fax: 86-23-8980-9500 Spain - Madrid

Korea - Seoul

Tel: 630-285-0071 China - Hangzhou Tel: 34-91-708-08-90

Tel: 82-2-554-7200

Fax: 630-285-0075 Tel: 86-571-2819-3187 Fax: 82-2-558-5932 or Fax: 34-91-708-08-91

Cleveland Fax: 86-571-2819-3189 82-2-558-5934 UK - Wokingham

Independence, OH China - Hong Kong SAR Tel: 44-118-921-5869

Malaysia - Kuala Lumpur

Tel: 216-447-0464 Tel: 852-2943-5100 Fax: 44-118-921-5820

Tel: 60-3-6201-9857

Fax: 216-447-0643 Fax: 852-2401-3431 Fax: 60-3-6201-9859

Dallas China - Nanjing Malaysia - Penang

Addison, TX Tel: 86-25-8473-2460 Tel: 60-4-227-8870

Tel: 972-818-7423 Fax: 86-25-8473-2470 Fax: 60-4-227-4068

Fax: 972-818-2924

China - Qingdao Philippines - Manila

Detroit Tel: 86-532-8502-7355 Tel: 63-2-634-9065

Farmington Hills, MI

Fax: 86-532-8502-7205 Fax: 63-2-634-9069

Tel: 248-538-2250

Fax: 248-538-2260 China - Shanghai Singapore

Tel: 86-21-5407-5533 Tel: 65-6334-8870

Indianapolis Fax: 86-21-5407-5066 Fax: 65-6334-8850

Noblesville, IN

Tel: 317-773-8323 China - Shenyang Taiwan - Hsin Chu

Fax: 317-773-5453 Tel: 86-24-2334-2829 Tel: 886-3-5778-366

Fax: 86-24-2334-2393 Fax: 886-3-5770-955

Los Angeles

Mission Viejo, CA China - Shenzhen Taiwan - Kaohsiung

Tel: 949-462-9523 Tel: 86-755-8864-2200 Tel: 886-7-213-7828

Fax: 949-462-9608 Fax: 86-755-8203-1760 Fax: 886-7-330-9305

Santa Clara China - Wuhan Taiwan - Taipei

Santa Clara, CA Tel: 86-27-5980-5300 Tel: 886-2-2508-8600

Tel: 408-961-6444 Fax: 86-27-5980-5118 Fax: 886-2-2508-0102

Fax: 408-961-6445 China - Xian Thailand - Bangkok

Toronto Tel: 86-29-8833-7252 Tel: 66-2-694-1351

Mississauga, Ontario, Fax: 86-29-8833-7256 Fax: 66-2-694-1350

Canada China - Xiamen

Tel: 905-673-0699 Tel: 86-592-2388138

Fax: 905-673-6509 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040

11/29/12

Fax: 86-756-3210049

DS21946B-page 22 2005-2013 Microchip Technology Inc.

Вам также может понравиться

- Pridiom Multi-Zone Indoor and Outdoor Units GuideДокумент29 страницPridiom Multi-Zone Indoor and Outdoor Units Guidevizion2k4100% (1)

- TC4452 PDFДокумент23 страницыTC4452 PDFCHARIS ZEVGARASОценок пока нет

- TC4451/TC4452: 12A High-Speed MOSFET DriversДокумент24 страницыTC4451/TC4452: 12A High-Speed MOSFET DriversVolodiyaОценок пока нет

- TC4426/TC4427/TC4428: 1.5A Dual High-Speed Power MOSFET DriversДокумент20 страницTC4426/TC4427/TC4428: 1.5A Dual High-Speed Power MOSFET DriversOlavo FelterОценок пока нет

- TC4426/TC4427/TC4428: 1.5A Dual High-Speed Power MOSFET DriversДокумент28 страницTC4426/TC4427/TC4428: 1.5A Dual High-Speed Power MOSFET Driversioan jeanОценок пока нет

- TC4426A/TC4427A/TC4428A: 1.5A Dual High-Speed Power MOSFET DriversДокумент26 страницTC4426A/TC4427A/TC4428A: 1.5A Dual High-Speed Power MOSFET DriversFarhanОценок пока нет

- TC4425AVДокумент22 страницыTC4425AVluisОценок пока нет

- TC4421 TC4422 9A High-Speed Mosfet Drivers: Features General DescriptionДокумент9 страницTC4421 TC4422 9A High-Speed Mosfet Drivers: Features General DescriptionAli JanjuaОценок пока нет

- 6A High-Speed Power MOSFET Drivers: Features General DescriptionДокумент30 страниц6A High-Speed Power MOSFET Drivers: Features General DescriptionDonchon chungОценок пока нет

- TC4420M/TC4429M: 6A High-Speed MOSFET DriversДокумент18 страницTC4420M/TC4429M: 6A High-Speed MOSFET Driversdaniela espinosaОценок пока нет

- TC1413/TC1413N: 3A High-Speed MOSFET DriversДокумент24 страницыTC1413/TC1413N: 3A High-Speed MOSFET DriverskarimОценок пока нет

- Mcp1407driver BufferДокумент28 страницMcp1407driver BufferAntonio NappaОценок пока нет

- TC426/TC427/TC428: 1.5A Dual High-Speed Power MOSFET DriversДокумент18 страницTC426/TC427/TC428: 1.5A Dual High-Speed Power MOSFET DriversShashikant PatilОценок пока нет

- TC4422Документ6 страницTC4422l.siqueiraОценок пока нет

- TC4467/TC4468/TC4469: Logic-Input CMOS Quad DriversДокумент22 страницыTC4467/TC4468/TC4469: Logic-Input CMOS Quad DriversFatih YILDIRIMОценок пока нет

- 4442 FBДокумент14 страниц4442 FBtecnicoeletronico23Оценок пока нет

- LTC4364-1 and - 2 - Surge Stopper With Ideal DiodeДокумент24 страницыLTC4364-1 and - 2 - Surge Stopper With Ideal DiodeVio ChiОценок пока нет

- Driver Mosfet TC428Документ16 страницDriver Mosfet TC428jaimeОценок пока нет

- MCP14A0151/2: 1.5A MOSFET Driver With Low Threshold Input and EnableДокумент24 страницыMCP14A0151/2: 1.5A MOSFET Driver With Low Threshold Input and EnableAdrian RafliОценок пока нет

- Infenion Power Factor Controller 4862GДокумент18 страницInfenion Power Factor Controller 4862GAsimuddin68Оценок пока нет

- Datasheet - HK tc429 1085381Документ7 страницDatasheet - HK tc429 1085381Vladimir KrivenokОценок пока нет

- Toshiba Bipolar IC Drives DC MotorsДокумент14 страницToshiba Bipolar IC Drives DC MotorsrikyОценок пока нет

- TC427CPAДокумент5 страницTC427CPASherif OkdaОценок пока нет

- CLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesДокумент16 страницCLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesPeter SolyomОценок пока нет

- 7.5 Ns Triple High Voltage Video Amplifier: FeatureДокумент10 страниц7.5 Ns Triple High Voltage Video Amplifier: Featureanoosh nymousОценок пока нет

- 5 VregДокумент34 страницы5 VregWaddy123Оценок пока нет

- MCP1824Документ35 страницMCP1824ed251Оценок пока нет

- TPD2015FNДокумент17 страницTPD2015FNLamayah FordОценок пока нет

- Microchip Tech MCP1827S 5002E EB - C641174Документ42 страницыMicrochip Tech MCP1827S 5002E EB - C641174prexo zoneОценок пока нет

- GMT Global Mixed Mode Tech G2898KD1U - C356810Документ8 страницGMT Global Mixed Mode Tech G2898KD1U - C356810ziya tutuОценок пока нет

- 3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Документ11 страниц3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Dwp BhaskaranОценок пока нет

- TC4420/TC4429: 6A High-Speed MOSFET DriversДокумент22 страницыTC4420/TC4429: 6A High-Speed MOSFET DriverssophiaОценок пока нет

- LTC 3124Документ28 страницLTC 3124m3rishorОценок пока нет

- DatasheetДокумент11 страницDatasheetMachineDОценок пока нет

- LM224A-LM324A: Low Power Quad Operational AmplifiersДокумент20 страницLM224A-LM324A: Low Power Quad Operational Amplifiersravisaini_15Оценок пока нет

- Iris 4015Документ6 страницIris 4015vetchboyОценок пока нет

- 28 Channel Ink Jet Driver: Multipower BCD TechnologyДокумент9 страниц28 Channel Ink Jet Driver: Multipower BCD TechnologyVictor JhonОценок пока нет

- Data Sheet: TDA8547TSДокумент21 страницаData Sheet: TDA8547TSbamz pamungkasОценок пока нет

- MCP1825 PDFДокумент38 страницMCP1825 PDFIoan TivgaОценок пока нет

- MCP1825/MCP1825S: 500 Ma, Low Voltage, Low Quiescent Current LDO RegulatorДокумент39 страницMCP1825/MCP1825S: 500 Ma, Low Voltage, Low Quiescent Current LDO RegulatorZireael EDОценок пока нет

- 10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionДокумент24 страницы10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionSergio MuriloОценок пока нет

- TA8428K Datasheet en 20100223Документ15 страницTA8428K Datasheet en 20100223Richard Andrianjaka LuckyОценок пока нет

- Instalacion Modulo 2VID-24VACДокумент2 страницыInstalacion Modulo 2VID-24VACNoelia MurilloОценок пока нет

- IXDD414Документ11 страницIXDD414CHARIS ZEVGARASОценок пока нет

- TC4538BP Datasheet en 20140301Документ9 страницTC4538BP Datasheet en 20140301Strati YovchevОценок пока нет

- 22W Car Radio Power Amplifier IC with Integrated Class-B OutputДокумент11 страниц22W Car Radio Power Amplifier IC with Integrated Class-B OutputamdatiОценок пока нет

- 15W Universal ChargerДокумент11 страниц15W Universal Chargermas udinОценок пока нет

- Liner Ltc4210Документ20 страницLiner Ltc4210ranihij832Оценок пока нет

- Am5890s V1.5TSДокумент11 страницAm5890s V1.5TSflo72afОценок пока нет

- TC4420 TC4429 6A High-Speed Mosfet Drivers: Features General DescriptionДокумент2 страницыTC4420 TC4429 6A High-Speed Mosfet Drivers: Features General DescriptionKSОценок пока нет

- Tda 8588 AjДокумент54 страницыTda 8588 AjAngel Fig100% (1)

- Datasheet TDA 8358JДокумент20 страницDatasheet TDA 8358JJose BenavidesОценок пока нет

- Datasheet TDA8358J PDFДокумент20 страницDatasheet TDA8358J PDFJose BenavidesОценок пока нет

- Datasheet Que Ninguem Pensa em Usar Mas Vai PrecisarДокумент8 страницDatasheet Que Ninguem Pensa em Usar Mas Vai PrecisarAnthony AndreyОценок пока нет

- TDA8511J Philips Elenota - PL PDFДокумент16 страницTDA8511J Philips Elenota - PL PDFMariuszChreptakОценок пока нет

- STR5A460 Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETДокумент32 страницыSTR5A460 Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETalanОценок пока нет

- 1.5A Low Drop Fixed and Adjustable Positive Voltage RegulatorsДокумент18 страниц1.5A Low Drop Fixed and Adjustable Positive Voltage RegulatorsteknoalexОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Variable Frequency Arduino GeneratorДокумент3 страницыVariable Frequency Arduino Generatorshreeblr79Оценок пока нет

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Документ9 страницSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Zoltán HalászОценок пока нет

- Induction Heater - Series Resonant - Uc - PLL Tuning (ReactorForge) - Projects - ForumsДокумент23 страницыInduction Heater - Series Resonant - Uc - PLL Tuning (ReactorForge) - Projects - Forumsshreeblr79Оценок пока нет

- An5030 PDFДокумент20 страницAn5030 PDFCanh LuongtienОценок пока нет

- mc3303 DatasheetДокумент17 страницmc3303 Datasheetshreeblr79Оценок пока нет

- 16F877AДокумент234 страницы16F877AMarius PauletОценок пока нет

- Energies 09 00432Документ20 страницEnergies 09 00432Nikola TrnavacОценок пока нет

- Variable Frequency Arduino ProgramДокумент2 страницыVariable Frequency Arduino Programshreeblr79Оценок пока нет

- PIC18F4525Документ412 страницPIC18F4525Breyk QuinteroОценок пока нет

- DIY Arduino Waveform Generator or Function GeneratorДокумент16 страницDIY Arduino Waveform Generator or Function Generatorshreeblr79Оценок пока нет

- 30 kVA Induction HeaterДокумент8 страниц30 kVA Induction HeaterZoeloe_2100% (3)

- Dip16 eДокумент1 страницаDip16 eshreeblr79Оценок пока нет

- CD 4520 BeДокумент11 страницCD 4520 BeWie SeptiОценок пока нет

- 2 Simple Induction Heater Circuits - Hot Plate Cookers - Homemade Circuit ProjectsДокумент17 страниц2 Simple Induction Heater Circuits - Hot Plate Cookers - Homemade Circuit Projectsshreeblr79Оценок пока нет

- Radio Broadcasting Equipment CatalogДокумент15 страницRadio Broadcasting Equipment CatalogManuel ManjateОценок пока нет

- Future Series - Rover Deluxe - enДокумент49 страницFuture Series - Rover Deluxe - enSteveAbonyiОценок пока нет

- 75 MM & 100 MM Borewell Submersible Pumpset Performance ChartДокумент17 страниц75 MM & 100 MM Borewell Submersible Pumpset Performance ChartRaviОценок пока нет

- AD003, DA003, DA004, MAD01 Analog IO Units Operation ManualДокумент139 страницAD003, DA003, DA004, MAD01 Analog IO Units Operation ManualMD SAIFULNIZAM ABDUL HALIMОценок пока нет

- NEAA 02 05 Servomotor On OffДокумент4 страницыNEAA 02 05 Servomotor On OffLaurentiu LapusescuОценок пока нет

- Final Draft 0Документ47 страницFinal Draft 0Yosef KirosОценок пока нет

- BCC3000 Service Manual New)Документ54 страницыBCC3000 Service Manual New)mustakim gma100% (1)

- AC Drive for Fans, Pumps, HVAC E1000 SeriesДокумент14 страницAC Drive for Fans, Pumps, HVAC E1000 SeriesBiến Tần EasydriveОценок пока нет

- The Design Concept and Operating Principle of A Voltage Sensitive Switching Circuit (VSSC)Документ6 страницThe Design Concept and Operating Principle of A Voltage Sensitive Switching Circuit (VSSC)LevisОценок пока нет

- Quectel BG95 Reference Design V1.0Документ19 страницQuectel BG95 Reference Design V1.0Edilberto SanabriaОценок пока нет

- Dryer: Home/Homestyle/Light OPL Electronic Control Error Codes Master ListДокумент10 страницDryer: Home/Homestyle/Light OPL Electronic Control Error Codes Master ListRustinОценок пока нет

- SH-18-18 IPS, UPS, Dehumidifier, Energy Meter. (Final)Документ8 страницSH-18-18 IPS, UPS, Dehumidifier, Energy Meter. (Final)Md. Nobin KhanОценок пока нет

- 3-Phase Power Factor Correction, Using Vienna Rectifier ApproachДокумент13 страниц3-Phase Power Factor Correction, Using Vienna Rectifier Approachvdiaz1Оценок пока нет

- MiCOM Alstom P847BC Ver70K Manual GB - FR-FRДокумент384 страницыMiCOM Alstom P847BC Ver70K Manual GB - FR-FRAmany MoemenОценок пока нет

- Tle Ict Css 9 q2 Module 3 PitdДокумент25 страницTle Ict Css 9 q2 Module 3 PitdRynel LanzaroteОценок пока нет

- InvertarДокумент61 страницаInvertarspulber alexandruОценок пока нет

- 220323 Cau Hoi Lam Ro Lần 02Документ18 страниц220323 Cau Hoi Lam Ro Lần 02ntphuoc694Оценок пока нет

- GC-1M Installation InstructionsДокумент73 страницыGC-1M Installation Instructionsnhocti007Оценок пока нет

- EZ-SCREEN System 14 MM 30 MM Models PDFДокумент74 страницыEZ-SCREEN System 14 MM 30 MM Models PDFAlexis BraceroОценок пока нет

- Xdlie041en K PDL Dma M ScuДокумент23 страницыXdlie041en K PDL Dma M ScuMauricio CruzОценок пока нет

- YTA70PДокумент3 страницыYTA70PjamesrickynОценок пока нет

- New Rich Text DocumentДокумент11 страницNew Rich Text DocumentPriyanka SinghОценок пока нет

- Zketech-Ebc A20 ManualДокумент6 страницZketech-Ebc A20 ManualScan SekolОценок пока нет

- User Manual PM3250Документ80 страницUser Manual PM3250otavioalcaldeОценок пока нет

- ACS580MV Troubleshooting Manual EN RevfДокумент144 страницыACS580MV Troubleshooting Manual EN RevfSamer ChahroukОценок пока нет

- Toshiba Personal Computer Libretto 100CTДокумент236 страницToshiba Personal Computer Libretto 100CTmoannaОценок пока нет

- XH-3001 Operating InstructionДокумент7 страницXH-3001 Operating InstructionKingsly LeoОценок пока нет

- Subject: GSTP001 - Global Infrastructure and Networks Global Standard - Protection and Control Device For MV Substation - RGDAT Control UnitДокумент40 страницSubject: GSTP001 - Global Infrastructure and Networks Global Standard - Protection and Control Device For MV Substation - RGDAT Control UnitAlexandru HalauОценок пока нет

- TT 3064A ManualДокумент152 страницыTT 3064A Manualspishak494Оценок пока нет