Академический Документы

Профессиональный Документы

Культура Документы

MT6735 PCB Design Guidelines-Simplified Chinese - V0 2 PDF

Загружено:

olger huancara gasparaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MT6735 PCB Design Guidelines-Simplified Chinese - V0 2 PDF

Загружено:

olger huancara gasparaАвторское право:

Доступные форматы

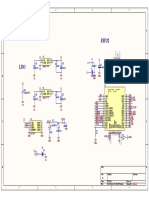

CONFIDENTIAL A

MT6735 PCB设计规范

V 0.2

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

设计规范版本修订记录

版本 日期 描述 编辑者

V0.1 2014/12/17 初版release. Tina Tang, Mason Wu, Jin

T Zh

Tao, Zhuanning Cao,

i C

FK Pan, Charles Chen

V0.2 2015/02/09 1.更改 MT6328 footprint P79~P80 Tina Tang

2.更改Page30图面

3 移除4L叠构建议

3.移除4L叠构建议

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 2

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

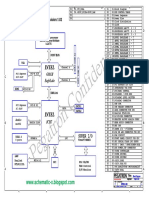

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 3

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 4

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

概述

▪ MT6735是新一代LTE智慧手机芯片,中央处理器采用安谋四核

心CortexA53、28奈米制程,频率最高可达1.5GHz。

Dual SIM Video Telephony

BT/FM/Wi-Fi/GPS 1080p Video Playback

Integrated Video Streaming

Hot Knot MT6735 13M Camera

1080p Video Record

Cortex A53 1.3-1.5GHz Face Detection / Smile Shot

QUAD Core AP

LTE Cat.4

W-HSPA+ Rel.8

TD HSPA R

TD-HSPA Rel.7

l7

4G LTE Support Tier 1 Performance

Tier 1 Performance CDMA/EVDO

Audio/Speech/Modem

Low Power

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 5

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735芯片外形尺寸图

▪ Package info.

– Body size: 12.6x12.6x0.9mm

d

– Ball pitch: 0.4mm

– Ball diameter: 0.25mm

– Ball count: 641

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 6

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 Footprint设计建议

Note:

• MT6735的焊垫使用copper defined设计方式 (如图一))

MT6735的焊垫使用copper defined设计方式。(如图

• 钢网开口设计,建议使用0.25mm方形,并做0.075导R角。(如图二的绿色区域)

• 打在MT6735焊垫上的盲孔(via1‐2)建议使用0.1/0.25mm(4/10mil),以提升SMT良率。

图一 图二

如下图所示,焊垫皆为copper defined。

Pad直径0.25mm,solder mask为0.325mm。 0.25mm

R0.075

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 7

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

A1

MT6735重要信号分布图 eMMC

DDR

DDR area

DDR area

DDR area

area

To

MT6625

SIM1/SIM2

LCM

MAIN

MAIN

DPI

POWER & GND

USB

CAMERA

To PMIC

BPI BUS

BPI BUS

LTE TX

LTE RX C2K TX/RX BPI BUS

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 8

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 9

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 PCB 叠构(Stack‐up)建议

▪ PCB之总叠层厚度请勿超过0.9mm±10%。

▪ 各层铜箔属性、及中间夹层之厚度和材质请尽量遵照以下建议去规划,以达最

佳之电性设计。

▪ 在”Layer definition”中,这里只针对LPDDR3和CPU做建议。其中“空白”的部分

可自行决定,若有空间,可用来做LPDDR2/3和CPU的PWR/GND plane的补强。

▪ 其它讯号之

其它讯号之”Layer definition请遵照这份PCB

请遵照这份 design guideline 描述之设计规范进

行设计即可。

▪ 这边共建议了以下几种叠构 :

• 6层1阶

• 8层1阶

• 8层2阶(疊孔)

• 8层2阶(錯孔)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 10

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

叠构(PCB Stack‐up)建议: 6层1阶

6L HDI-1 (1-4-1), 0.8mm

Layer definition

S

Suggestion

i (0

(0.8

8 mm)

)

Signal/Power/Ground (S/P/G)

Layers Stackup Theoretic Theoretic

GPU/TOP/

thickness thickness Material ER LPDDR2/3 CPU Others

LTE

(mm) (mils)

SR 0.010 0.4 SR 3.5

L1 0.033 1.3 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9

L2 0.030 1.2 Copper G/S S

0.102 4 Prepreg (2116) 4.1

L3 0 015

0.015 06

0.6 C

Copper G G G G

0.305 12.0 Core 4.4

L4 0.015 0.6 Copper G/S P G/P/S

0.102 4.0 Prepreg (2116) 4.1

L5 0.030 1.2 Copper P P G/P/S

0.076 3.0 Prepreg (1080) 3.9

L6 0.033 1.3 Copper G G G G

SR 0.010 0.4 SR 3.5

Total 0.8 mm ±10%

如果板厚需调整,请维持建议的PP厚度不变,仅调整core厚度以达需求.

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 11

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

叠构(PCB Stack‐up)建议: 8层1阶

8L HDI-1 (1-6-1), 0.8mm

Layer definition

Suggestion (0.8 mm)

Signal/Power/Ground (S/P/G)

Layers

aye s Stackup

S ac up Theoretic Theoretic

GPU/TOP/

thickness thickness Material ER LPDDR2/3 CPU Others

LTE

(mm) (mils)

SR 0.010 0.4 SR 3.5

L1 0.033 1.3 Copper G/S S

0.076 3.0 Prepreg (1080) 39

3.9

L2 0.030 1.2 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9

L3 0.015 0.6 Copper G G G G

0.102 4.0 Core 4.1

L4 0.015 0.6 Copper G/S P G/P/S

0.102 4.0 Prepreg (2116) 4.1

L5 0.015 0.6 Copper P G G G/P/S

0.102 4.0 Core 4.1

L6 0 015

0.015 06

0.6 C

Copper G P P/G

0.076 3.0 Prepreg (1080) 3.9

L7 0.030 1.2 Coper G G G/S

0.076 3.0 Prepreg (1080) 3.9

L8 0.033 1.3 Copper G G G G/S

SR 0.010 0.4 SR 3.5

Total 0.8 mm ±10%

如果板厚需调整,请维持建议的PP厚度不变,仅调整core厚度以达需求.

板 调整, 的 厚度不变,仅调整

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 12

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

叠构(PCB Stack‐up)建议: 8层2阶(叠孔)

8L HDI-2 (2-4-2), 0.9mm / 0.65mm

Suggestion (0.9 mm) Suggestion (0.65 mm) Layout definition

Signal/Power/Ground (S/P/G)

Layers Stackup Theoretic Theoretic Theoretic Theoretic

thickness thickness Material ER thickness thickness Material ER LPDDR2 GPU/

(mm) (mils) (mm) (mils) CPU Others

/3 TOP/LTE

SR 0 010

0.010 04

0.4 SR 35

3.5 0 010

0.010 04

0.4 SR 35

3.5

L1 0.033 1.3 Copper 0.033 1.3 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L2 0.030 1.2 Copper 0.030 1.2 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L3 0.031 1.2 Copper 0.030 1.2 Copper G G G G

0.102 4.0 Prepreg (2116) 4.1 0.056 2.2 Prepreg (1080) 3.9

L4 0.014 0.6 Copper 0.014 0.6 Copper G/S P G/P/S

0.178 7.0 Core 4.3 0.102 4.0 Core 4.1

L5 0.014 0.6 Copper 0.014 0.6 Copper P G G/P/S

0.102 4.0 Prepreg (2116) 4.1 0.056 2.2 Prepreg (1080) 3.9

L6 0 031

0.031 12

1.2 C

Copper 0 031

0.031 12

1.2 C

Copper G P P/G

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L7 0.030 1.2 Coper 0.030 1.2 Coper G G G/S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L8 0.033 1.3 Copper 0.033 1.3 Copper G G G G/S

SR 0.010 0.4 SR 3.5 0.010 0.4 SR 3.5

Total 0.9 mm ±10% 0.65 mm ±10%

如果板厚需调整,请维持建议的PP厚度不变,仅调整core厚度以达需求.

板 调整, 的 厚度不变,仅调整

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 13

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

叠构(PCB Stack‐up)建议: 8层2阶(错孔)

8L HDI-2 (1-1-4-1-1), 0.9mm / 0.65mm

Suggestion (0.9 mm) Suggestion (0.65 mm) Layout definition

Signal/Power/Ground (S/P/G)

Layers Stackup Theoretic Theoretic Theoretic Theoretic

thickness thickness Material ER thickness thickness Material ER LPDDR2 GPU/

(mm) (mils) (mm) (mils) CPU Others

/3 TOP/LTE

SR 0 010

0.010 04

0.4 SR 35

3.5 0 010

0.010 04

0.4 SR 35

3.5

L1 0.033 1.3 Copper 0.033 1.3 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L2 0.030 1.2 Copper 0.030 1.2 Copper G/S S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L3 0.031 1.2 Copper 0.030 1.2 Copper G G G G

0.102 4.0 Prepreg (2116) 4.1 0.056 2.2 Prepreg (1080) 3.9

L4 0.014 0.6 Copper 0.014 0.6 Copper G/S P G/P/S

0.178 7.0 Core 4.3 0.102 4.0 Core 4.1

L5 0.014 0.6 Copper 0.014 0.6 Copper P G G/P/S

0.102 4.0 Prepreg (2116) 4.1 0.056 2.2 Prepreg (1080) 3.9

L6 0 031

0.031 12

1.2 C

Copper 0 031

0.031 12

1.2 C

Copper G P P/G

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L7 0.030 1.2 Coper 0.030 1.2 Coper G G G/S

0.076 3.0 Prepreg (1080) 3.9 0.056 2.2 Prepreg (1080) 3.9

L8 0.033 1.3 Copper 0.033 1.3 Copper G G G G/S

SR 0.010 0.4 SR 3.5 0.010 0.4 SR 3.5

Total 0.9 mm ±10% 0.65 mm ±10%

如果板厚需调整,请维持建议的PP厚度不变,仅调整core厚度以达需求.

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 14

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Common Rules and Via Type

▪ 最小线宽/线距:芯片下方使用3/3mil,芯片外部使用4/4 mil。

芯片下方

芯片外部

▪ Via type:

• Blind Via (under chip) 4/10 mil

• Blind Via (outside chip) 4/12 mil

• Buried Via10/18mil

• Through Via12/20 mil

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 15

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

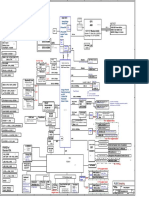

MIC2

Placement Notes

Front

PWR

REC cam KEY

MT6158 WIFI/BT/

BT/FM/ GPS ANT C2K ANT

WiFi/GPS

(MT6625)

Main Mini

camera USB

MCP

LPDDR3 PA

MT6735

Earphone

Audio

MT6328

DEBUG BATT

IO PA

LCM

LCM C

Conn

CON NFC

ANT

MT6169

NFC

SIM1 Bottom

B tt

TOP side

side

SD SIM2 SPK

card

VIBRATOR

LTE

ANT CTP

MIC1

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 16

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

A1

MT6735 Fan Out

第一和第二圈的球(黄色ball )

第 和第 圈的球 黄色

尽量从Layer1出线。

第三到第五圈的球(粉红色ball )

尽量从Layer2出线,盲孔

(4/10mil)请打在焊盘正中。

第五圈之后的球从内层出线

(蓝色ball )在打埋孔时,请注

意PWR/GND plane的完整性。

绿色/红色球标示,

这些球都是PWR/GND ball注意

调整埋孔的位置,保证主地层

以及PWR都有良好的通道。

以及PWR都有良好的通道

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 17

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 18

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB 模块设计

▪ 建议第一优先采用MTK提供之模块

现今智能手机设计趋势走向轻、薄、与大电池容量等需求,系统电路板(PCB)为符合

此设计趋势,必须同时满足CPU 之电源传输网络(PDN),和mobile memory之高频电

性等设计规范,因而大幅增加PCB设计上的时间与复杂度。

为协助客户”快速”设计出”正确”、”性能优异”、且”可靠度良好”的智能手机PCB,本

使用说明主要针对联发科技所提供的MMD方案(M di T kM d l D i )之PCB

使用说明主要针对联发科技所提供的MMD方案(MediaTekModuleDesign)之PCB

Layout模块化进行介绍,提供了最佳的CPU & MCP Memory layout 设计,其目的除了

协助客户缩短PCB设计时间,确保系统稳定性能,亦可大幅减少相关问题所需的测

试和除错处理时间 最终能快速将产品推广到市场上

试和除错处理时间,最终能快速将产品推广到市场上。

▪ 最大化利用MTK提供之模块

主要目的是提供客户端在系统PCB设计上的便利与弹

MTK提供的PCB layout模块,主要目的是提供客户端在系统PCB设计上的便利与弹

MTK提供的PCB layout模块

性。导入模块的理想状况是指机构板型能够契合而能完全一模一样的复制MTK PCB

layout模块;但若机构板型限制而无法完全复制,或需更换零件包装,同样可以

「最大化」(局部)利用MTK提供的模块来提升客户在PCB设计上的效率与正确性。

▪ 如果在使用PCB模块的过程中有任何问题,

请与支持贵单位 之联发科技的工程人员反映。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 19

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Enabling your High-speed Digital Design~

SIE((SignalIntegrityExpress):

g g y p ) SI/PI simulation support

pp

CONFIDENTIAL A

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 Ball List for LPDDR3 Interface

Ball # Signal Name Description Grouping

C7, A8, B8, A9, D9, B10, C10, A11, B11, C11, A12,

B12, D12, B13, A14, A15, B15, D15, B16, A17, B17,

32 DQ[0:31] Data bus

D17, A18, C18, B19, A20, B20, D20, A21, B21, D21, DQ

B22

D7, C14, D14, C19 4 DQM[0:3] Data mask

DQS_T[0:3]

E12, F12, E15, F15, E17, F17, E20, F20 8 Differential data strobe pair DQS

DQS_C[0:3]

D1, B2, C2, D2, A3, C3, A5, A6, B6, D6 10 CA[0:9] Command/Address inputs

CKE

Clock enable

B3, B4, D4 3 CS0_N C/A

Chip select

CS1_N

E2 1 EXTDN Drive Strength Calibration

F16 1 VREF Reference voltage

CLK0_T

E9, F9 2 Differential clock pair CLK

CLK0_C

Provide LPDDR3 DRAM

G9, H9, G12, H12, G14, H14, G16, H16, G18, H18 8 DDRV controller I/O power. LPDDR3_PWR

V=1 2V (1.14V/1.3V)

V=1.2V, (1 14V/1 3V)

MT6735所支持之LPDDR3最快可达1466Mbps。如果PCB未照规范设计,讯号线之间的电磁耦合将会产生

非常严重之讯号完整性(signal integrity)的问题,造成LPDDR3信号之不稳定。强烈建议客户优先导入联发

科技提供之MMD (MediaTek Module Design)方案,并提交PCB设计档案暨相关PCB迭构信息给联发科技支

Design)方案 并提交PCB设计档案暨相关PCB迭构信息给联发科技支

持人工程员进行SI和PDN的仿真。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 21

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Placement Recommendation for LPDDR3_MCP

LPDDR3_eMCP placement guidelines:

摆件时将MT6735和LPDDR3_eMCP尽量靠近,并控制两者间距(△Y)小于0.5mm,△Y愈小愈好。

Y 0.5mm

LPDDR3_eMCP

MT6735

Top‐Side

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 22

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Design Guidelines for LPDDR3_1466Mbps

基本规范和叠构建议:

1. Routing时直接以最短距离将MT6735和LPDDR3_eMCP(221 ball)对接,布线及叠构请依照下图建议。

2. 线宽/线距:Use 3mil/3mil for all traces from MT6735 to LPDD3

3. DQ/DM/CMD/CA(CA5~CA9, CS0, CS1, CKE)走线以L1、L2 为主,走线正下方的L3需保持完整的参考面(GND ) ,

CA0~CA4/DQS/CLK在L4。

4. 所有讯号线均不需要调等长 也不需要特别做阻抗控制 只要让线长越短越好

所有讯号线均不需要调等长,也不需要特别做阻抗控制,只要让线长越短越好。

5. 讯号线分别走在L1 、L2 、L4,如下图所示:

1) DQ:L1走线每3根信号做GND shielding;L2走线保持每1根信号做shielding 。

2) CMD/ADDR(CA5~CA9, CS0, CS1, CKE): L1走线每1根信号做GND shielding;L2走线保持每1根信号做shielding 。

/ ( ) 线需與相鄰走線相距

3)) CMD/ADDR(CA0~CA4):走在L4,走线需與相鄰走線相距2W 。

4) L1/L2走线时尽量上下错开,减少平行重叠的情况。

5) L1 、L2 的GND走线,视情况用Via连接,并在两芯片附近尽可能增加与L3 GND plane相连的

机会,这对提升信号质量非常有帮助。

Y 0.5mm

LPDDR3_eMCP

MT6735

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 23

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Design Guidelines for DQ

Ball # Signal Name Description Grouping

C7, A8, B8, A9, D9, B10, C10, A11, B11, C11, A12,

B12, D12, B13, A14, A15, B15, D15, B16, A17,

32 RDQ[0:31] Data bus

B17, D17, A18, C18, B19, A20, B20, D20, A21, DQ

B21, D21, B22

D7, C14, D14, C19 4 RDQM[0:3] Data mask

1. DQ走线以L1、L2 为主,以最短距离对接,请勿绕线。走线正下方的L3 请保持完整的GND参考面连接。

2. 在L1 的讯号线,每3条讯号线皆以GND trace相互隔开,L1/L2上下走线需错开,以减少crosstalk效应,并在GND线的头尾上下连接L1/L2的

GND走线,如果在GND线的两端无法加via ,请作keep out不铺铜。

3. 在 的讯号线 每条讯号线皆以 相互隔开 线宽/线距皆为 W=3mil,并在GND线的头尾上下连接L2/L3的GND走线,如果在GND

在L2的讯号线,每条讯号线皆以GND trace相互隔开,线宽/线距皆为 并在 线的头尾上下连接 / 的 走线 如果在

线的两端无法加via ,请作keep out不铺铜。

DQ/DM

Recommend!

W W W W W W W W W GND PCB L1 PCB L2

L1 (Signal/GND)

W W W W W W W W W W W

L2(Signal/GND)

L3(GND)

1. Overlapped Byte0 Byte3

NG! 2. L2 without ground shielding Byte0 Byte3

3

3. L3 split ref plane

L3 split ref. plane

Byte2 Byte1

L1 (Signal) Byte2 Byte1

L2(Signal)

Copyright © MediaTek Inc. All rights reserved. 2015/2/9

L3(GND)

CONFIDENTIAL A 24

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Design Guidelines for CA

Ball # Signal Name Description Grouping

D1, B2, C2, D2, A3, C3, A5, A6, B6,

10 RA[0:9] Command/Address inputs

D6

C/A

RCKE/RCS0_B Clock enable

B3, B4, D4 3

RCS1_B Chip select

1. CA5~CA9, CKE,CS0,CS1走线於L1、L2,以最短距离对接。走线下方的 L3 保持完整的GND 主地, 供 L2 GND 線用

via 連接。

2. CA0~CA4,走线於L4 ,走线需與相鄰走線相距2W 。

3. 在L1 的讯号线,每条讯号线皆以GND trace相互隔开,L1/L2上下走线需错开,以减少crosstalk效应,并在GND线的头尾上下

连接

连接L1/L2的GND走线,如果在GND线的两端无法加via

的 走线 如果在 线的两端无法加 ,请作keep out不铺铜。

请作 铺铜

4. 在L2的讯号线,每条讯号线皆以GND trace相互隔开,线宽/线距皆为 W=3mil,此種做法對CA 的降噪非常重要, 需特別

注意之。

PCB L1 PCB L2 PCB L4

!

Recommend!

W W W W W W W W W

L1 (Signal/GND)

W W W W W W W W W W W

L2(Signal/GND)

L3(GND)

W 2W W 2W W 2W W 2W W

L4(Signal/GND)

L5(PWR)

1. Overlapped

C/A

NG! 2

2. L2 i h

L2 without ground shielding

d hi ldi

C/A C/A

3. L3 split ref. plane

L1 (Signal)

L2(Signal)

L3(GND)

For the rest design details. Please refer to P27~P36。

CONFIDENTIAL A 25

GND

CA (CA0~CA4) CA (CA5~CA9, CS0, CS1, CKE)

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Design Guidelines for DQS, CLK

Ball # Signal Name Description

E12, F12, E15, F15, E17, F17, EDQS[0:3]

8 Differential data strobe pair (DQS)

E20, F20 /EDQS[0:3]

EDCLK

E9 F9

E9, 2 Differential clock pair (CLK)

/EDCLK

PCB layout guidelines:

1. DQS和CLK为两两一对之差动讯号:

DQS和CLK为两两 对之差动讯号:

L4

1) 两两平行走线。

2) 走内层L4,上下参考面尽量保持完整。

3) 每对差动讯号两旁需保持PWR shielding。

2 走线之线宽/线距建议,参考下图所示:W=

2. 走线之线宽/线距建议 参考下图所示 W 3

mils,WG ≥ 3 mils。

3. 请注意PTH孔的间隔,Wvia1≥ 10 mils ,以利形成

上下层power与GND的通道。

上下层power与GND的通道

CLK

DQS+/‐ L3(GND)

WG W W W W W WG

L4 (Signal)

Wvia1 L5(PWR)

GND VDD_EMI CLK/DQS

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 26

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for PWR/GND Plane

PCB layout guidelines:

1. 内层的参考平面需要保持完整, L3(GND)

WG W W W W W WG

减少由Via穿孔产生的破碎连接。 L4 (Signal)

2. L3规划为GND平面, L5规划为

PWR平面

PWR平面。 L5(PWR)

3. 请注意PTH孔的间隔(≥ 10

mils) ,以利形成power与GND GND VDD_EMI CLK/DQS

的通道。

的通道

L3/L5 L4

Noted:

PTH

Wvia1≥ 10 mils

GND

GND

CLK DQS+/‐

GND Path

Wvia1

Wvia1

Copyright © MediaTek Inc. All rights reserved.

CONFIDENTIAL A 2015/2/9 27

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

LPDDR3 VREF Guideline L1

Ball # Signal

g Name Description

p 在L1、LL2直接

F16 1 VREF Reference Voltage 下孔接内层

1. EVREF的分压电阻请选用1K~10KΩ 1%电阻。

2. 走线请勿相邻于高速讯号线,如EDQ 、EDQS 、 EDCLK 、 在L1、L2直接

DQM 、或EA等讯号。 下孔接内层

3. EVREF的走线长度无特别规范,但需要确实以地线、地平

面、电源线、或者电源平面包围屏敝。

4. 请参考建议走线,在L1、L2直接下孔接内层,在L4相连并于 在L4相连,并做

两旁需加上PWR shielding,请确保EVREF与 shielding之 gnd‐shielding

L4

间距≥ 3 mils。

5. 请在底层或上层连接分压电阻与耦合电容两颗0.1uF 与一

单面置件

颗1uF 。 MT6735 LPDDR2/3 Cap and Voltage divider

C d V lt di id

EVREF EVREF EVREF

EVREF

L4

双面置件

Cap and Voltage divider 在底层或上层,

在底

连接分压电阻

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved.

与去耦合电容2015/2/9 28

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

LPDDR3 REXTDN Guideline

Ball # Signal Name Description

E2 1 REXTDN Drive Strength Calibration

1. REXTDN的下拉电阻请选用36Ω (1%)电阻。Default不上件。

2. 请参考建议走线,在L1 直接下孔接内层,在L4将讯号线走 REXTDN L1

出,最后在上层连接下拉电阻(或钻孔至背后连接亦可)。 resistor

单面置件

MT6735 LPDDR2/3 Resistor

REXTDN

L4

在L1往外接

电阻

Resistor

双面置件

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 29

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Layout Guidelines for DVDD12_EMI

L1 DRAM caps MT6328

MT6735 (0.1uF x 5)

(2.2uFx2) (PMIC)

DVDD12 EMI

DVDD12_EMI

关键路径

(critical path)

DRAM caps MT6328

MT6735

1. 整个PDN的网络从MT6328(PMIC ) output pin开始,产生DC直流电源,经过电源传输网络后,流入DRAM的电容

群(DRAM caps) ,流入MT6735芯片,,准备做为电流抽载的供给来源。

2. 从”DRAM caps”到MT6735的走线与钻孔为关键路径(critical path),此路径须符合PCB layout guideline的要求。

3

3. 在” DRAM caps”区间请至少放上 5颗0.1uF及2颗2.2uF電容

在” DRAM caps”区间请至少放上 5颗0 1uF及2颗2 2uF電容 ,放置位置离MT6735之DVDD12_EMI愈近愈好。

放置位置离MT6735之DVDD12 EMI愈近愈好

4. L1定义为” DRAM caps”区至MT6735 DVDD12_EMI的相对距离trace,关键路径之长度L1越短越好。此外,其它PCB

layout guideline如下:

1) 双面置件: 请将这5颗0.1uF及2顆2.2uF电容置于MT6735 DVDD12_EMI出球正下方,并以数量适当之Via直

接串接此电容。其关键路径(电容至MT6735 DVDD12_EMI出球的连结)之设计请严格遵守 规范,并参考设

计实例。

2) 单面置件:若因机构之限制而需要将” DRAM caps”和MT6735放置在同一面时,请将这5颗0.1uF及2顆2.2uF

电容尽所能去贴近MT6735 其关键路径(电容至MT6735 DVDD12 EMI出球的连结)之设计请严格遵守规范

电容尽所能去贴近MT6735,其关键路径(电容至MT6735 DVDD12_EMI出球的连结)之设计请严格遵守规范,

并参考设计实例。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 30

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection for DVDD12_EMI

: Via interconnect to PWR

PWR plane/

PWR wide trace

PWR wide trace

GND plane/

GND wide trace

GND wide trace

: Via interconnect to GND

去耦合电容旁之钻孔建议:

1. Via interconnect在PDN掌控跨层之间电流的传递路径, 容易成为各段路径的

瓶颈(短板),因此要注意layout guideline的建议。

瓶颈

2. 在PCB背面位置放置电容,注意尽快换层往上连接power plane或power ball。

3. 在去耦合电容旁要在最近位置打PWR和GND via。

4 最好每个去耦合电容(DRAM caps)至少有一对的

4. 最好每个去耦合电容(DRAM )至少有 对的 PWR和GND via。在空间足够下,

i 在空间足够下

建议多打PWR/GND via。电容 pad/via建议比例 Pad : Laser via : PTH via =

1: 1 : 1,并尽可能平均分配PTH & Laser vias ,使其垂直路径为最短 。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 31

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection for DVDD12_EMI

DVDD12_EMI在PCB上之钻孔建议: (Top view of MT6735 PCB)

1. 在DVDD12_EMI下方区域放置大、小孔的via数量要足够,以MT6735为例, via数量的最低需求是:5小孔(盲孔)配5大孔(埋

/PTH孔)。

2. 小孔(盲孔)尽可能多放(安排5个以上),并请直接将这些小孔在DVDD12_EMI出球做”via on ball”之设计,往下连接power

plane/trace和大孔(埋/PTH孔) 另外,在整个power ball的区域范围内平均放置 这些大孔,如下图示。

plane/trace和大孔(埋/PTH孔)。另外,在整个power 这些大孔,如下图示

3. 除了注意power的设计, 同时注意周围Ground via安排,将 Ground via尽量靠近power via,如下一页所示。适度增加

Ground via的数量, 可降低via之电感性效应。

CLK/CMD/ADR Byte2/Byte0 Byte1/Byte3

NG!!

大 小孔数量不够的!

大、小孔数量不够的!

NG!!

大、小孔数量够,但分布不均匀!

每群ball都拥有自己的小孔及大孔,

彼此间维持固定间距,以保持GND

plane的完整性,为我们建议之设计!

:DVDD12_EMI (PWR balls) :Blind Via : Buried (PTH)via

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 32

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection for DVDD12_EMI

1. 除了注意power的设计,同时注意周围ground的via安排,以减少via之电感效应,并缩小“return path”,

如下图。

如下图

2. GND via之数目和PWR via的比例基本上至少是1 : 1。

3. GND via距离PWR via愈近愈好,以缩小电源之电感性。

HDI‐1 双面置件 HDI‐2 HDI‐1 单面置件

MT6735 MT6735 MT6735 CAP

CAP CAP

Power GND Signal others

2015/2/9 33

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 33

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection for DVDD12_EMI Design Example

在L1尽量多打

L1

CMDADDR

些盲孔以增加

PWR导通性 单面置件

Byte 0/2 Byte 1/3

DRAM CAP

图中所示为PWR对

GND via对应情形,应尽

量缩小其相对距离

LPDDR3_MCP

L2

单面置件摆放电容

单面置件摆放电

应小心埋孔打法,以利 位置需尽量靠近芯

容位置需尽量靠

在L3 /L4GND通道畅通 片为佳

近芯片为佳

L3

在芯片

请尽量维持PWR在芯片

请尽量维持

下方通道完整连接,这

有助于信号质量

L4

MT6735

1. 单面置件:因机构之限制而需要将” DRAM caps”和MT6735放置在同一面,请将这5颗0.1uF及2颗2.2uF

“DRAM caps”尽所能去贴近MT6735与LPDDR2 MCP。

2. 在DRAM caps旁要在最近位置打PWR和GND

旁 注意尽快换层往下连接

via ,注意尽快换层往下连接PWR plane或GND plane.

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 34

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection for DVDD12_EMI Design Example

在L1尽量多打 请尽量维持PWR在芯片

双面置件 些盲孔以增加

PWR导通性

下方通道完整连接,这

有助于信号质量

CMDADDR

Byte 0/2 Byte 1/3

L1 L4

L2 L5

图中所示为PWR对 此层维持PWR通道畅

GND via对应情形,应 通,有助于减少背面电

尽量缩小其相对距离 容的PWR电感性

L6

L3 将PWR/GND via紧随在

背面电容旁边,非常有助

应小心埋孔打法,

于电容的稳压功能

以利在L3 /L5

以利在L3 /L5

GND通道

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 35

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 36

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 Ball List for LPDDR2 Interface

Ball # Signal Name Description Grouping

C7, A8, B8, A9, D9, B10, C10, A11, B11, C11, A12,

B12, D12, B13, A14, A15, B15, D15, B16, A17, B17,

32 DQ[0:31] Data bus

D17, A18, C18, B19, A20, B20, D20, A21, B21, D21, DQ

B22

D7, C14, D14, C19 4 DQM[0:3] Data mask

DQS_T[0:3]

E12, F12, E15, F15, E17, F17, E20, F20 8 Differential data strobe pair DQS

DQS_C[0:3]

D1, B2, C2, D2, A3, C3, A5, A6, B6, D6 10 CA[0:9] Command/Address inputs

CKE

Clock enable

B3, B4, D4 3 CS0_N C/A

p select

Chip

CS1 N

CS1_N

E2 1 EXTDN Drive Strength Calibration

F16 1 VREF Reference voltage

CLK0 T

CLK0_T

E9, F9 2 Differential clock pair CLK

CLK0_C

Provide LPDDR2 DRAM

G9, H9, G12, H12, G14, H14, G16, H16, G18, H18 8 DDRV controller I/O power. LPDDR2_PWR

V=1.2V,

V 1.2V, (1.14V/1.3V)

MT6735所支持之LPDDR2最快可达1066Mbps。如果PCB未照规范设计,讯号线之间的电磁耦合将会产生

非常严重之讯号完整性(signal integrity)的问题,造成LPDDR2信号之不稳定。强烈建议客户优先导入联发

科技提供之MMD (MediaTek Module Design)方案,并提交PCB设计档案暨相关PCB迭构信息给联发科技支

持人工程员进行SI和PDN的仿真

持人工程员进行SI和PDN的仿真。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 37

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Placement Recommendation for LPDDR2_eMCP

LPDDR2+eMMC MCP placement guidelines:

LPDDR2+eMMC_MCP

1. 摆件时将MT6735和LPDDR2_eMCP尽量靠近,并控制两者间距(△Y)小于1mm,△Y愈小愈好。

2. 请依照下图建议位置摆件,若因机构产生位移,请尽量控制MT6735和LPDDR2_eMCP的

LPDDR2的讯号走线为直线对接。

Y 1mm

LPDDR2_eMCP MT6735

Top‐Side

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 38

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PCB Design Guidelines for LPDDR2_1066Mbps

基本规范和叠构建议:

1. Routing时直接以最短距离将MT6735和LPDDR2_eMCP(186 ball)对接,布线及叠构请依照下

图建议。

2. 线宽/线距:

1) MT6735芯片正下方:可以局部走3mil/3mil 。

2) 出MT6735芯片之后:3mil/3mil 。

3. DQ/DM/CMD/CA(CA5~CA9, CS0, CS1, CKE)走线以L1、L2 为主,走线正下方的L3需保持完整

的参考面(GND ) ,CA0

CA0~CA4/DQS/CLK在L4。

CA4/DQS/CLK在L4。

4. 所有讯号线均不需要调等长,也不需要特别做阻抗控制,只要让线长越短越好。

5. 讯号线分别走在L1 、L2 、L4,與LPDDR3一致。

Y 1mm

LPDDR2_eMCP MT6735

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 39

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 40

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

概

PDN之基本概念

▪ 在高端之智能手机上

在高端之智能手机上,CPU为达GHz以上之高速运算,其瞬间需要之

为达 以上之高速运算 其瞬间需要之

电流和功耗,已非一般传统之PCB设计之简单概念可以应付。因此,

PCB上良好之PDN(power delivery network)设计已是高速CPU能正常运

作之必备条件。尤其是MT6735支持四核心CPU,其瞬间电流之需求

更需要优良之PDN设计来支持。

▪ 完整的PDN包含所有从VRM输出端到芯片输入端中电源传输与电流

回流会经过的电器连接网络。PDN的好坏会决定于这PCB中电源传输

路径上电源的走线(trace)、电源和接地之大、小钻孔(PWR/GND via)

和去耦合电容(decoupling capacitor)的数量及位置 这里的guidelines

和去耦合电容(decoupling capacitor)的数量及位置。这里的guidelines

即是要来规范这些布局以达最佳之PDN设计。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 41

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Ball List Table

MT6735 ball list for VPROC & VCORE:

Ball # Signal Name Description

M12, M13, M15, M16, M17, M18, 41 VPROC Provide application processor CPU.

M19, M20, N12, N13, N14, N15, N16, V=1.25V

N17 N18 N19 N20 T12 T13 T14

N17, N18, N19, N20, T12, T13, T14, Maximum current 4 15A

Maximum current 4.15A

T15, T16, T17, T18, T19, T20, U12,

U13, U14, U15, U16, U17, U18, U19,

U20, V14, W14, Y14, AA14, AB14,

AC14

K8, L7, L8, L9, L10, L11, L12, L15, L16, 41 VCORE Provide application processor core power.

L19, L20, L21, L22, M8, M10, M22, V=1.15V

N8, N10, N22, T8, T10, T22, U7, U8, Maximum current 2A

U9, U10, U11, U22, U23, Y7, Y8, Y9,

Y10, Y11, Y12, AA8, AA10, AA12,

AB8, AB10, AB12

W16, W17, W18, W19, W20, W21,

W16 W17 W18 W19 W20 W21 28 VLTE Provide application processor core power.

application processor core power

W22, W23, W24, Y16, Y17, Y18, Y19, V=1.05V

Y20, Y21, Y22, Y23, Y24, AA16, AA18, Maximum current 1.2A

AA20, AA22, AA24, AB16, AB18,

AB20 AB22 AB24

AB20, AB22, AB24

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 42

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

PMIC Placement Suggestions

MT6735

Length≤350mil

Length≤900mil VCORE

MT6328

VPROC Length≤450mil

Length≤900mil

Length≤550mil

Length ≤900mil VLTE

1. VPROC: MT6735與6328 (PMIC)之總距離請保持小於1350mil,其中MT6735至第一電容區的

距離請保持小於450mil ,第一電容區至MT6328的距離請保持小於900mil 。

2. VCORE: MT6735與6328 (PMIC)之總距離請保持小於1250mil,其中MT6735至第一電容區的

距離請保持小於350mil ,第一電容區至MT6333的距離請保持小於900mil 。

3. VLTE: MT6735與6328 (PMIC)之總距離請保持小於1450mil,其中MT6735至第一電容區的距

離請保持小於550mil ,第一電容區至MT6328的距離請保持小於900mil 。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 43

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for CPU Power: VPROC

Bottom Cap 关键路径

(双面上件

(双面上件: 1uF x 6)

) (critical

path) 1st group cap

L2 (双面上件: 4.7uF x 2, 22uF x 1, 47uF x 2 ) L/C MT6328

MT6735 (单面上件: 1uF x 6, 4.7uF x 2, 22uF x 1, 47uF x 2 ) Network

L1 (PMIC)

MT6735 VPROC

L/C

MT6328 Network

Close to BB

1. 整个PDN的网络从MT6328 (PMIC ) output pin开始,经过第一级LC低通滤波器, 产生DC直流电源,再流入第一电容群(1st group cap),准备做为电流

抽载的供给来源。双面上件时,可将部分小电容放至芯片下方,可增强电容稳压能力;

2. 从第一电容群(1st group cap)到MT6735的VPROC之走线为关键路径(critical path),此走线均须符合以下描述之PCB layout guideline。

3

3. 双面上件 在”B

双面上件:在”Bottom cap”区间建议放上6颗0.1uF、2颗4.7uF

”区间建议放上6颗0 1 F 2颗4 7 F 、 颗22uF

颗22 F 、 2颗47uF,放置离VPROC b ll 下方愈近愈好 请依电容值由小而大 由近而

2颗47 F 放置离VPROC balls下方愈近愈好。请依电容值由小而大,由近而

远依序填入电容。

1) L1定义为”正面1st group cap”区至MT6735的VPROC的宽形power trace(“关键路径”),其PCB layout guideline如下:

PWR采用一层走线,L1线长≤ 450mil;L1线宽≥ 120mil 。总共使用1层PWR/1层GND平行走线(请参考下页建议1)。

2)) L2定义为”Bottom cap”区至MT6735之wide power trace的连线,其PCB

p p layout guideline定义如下:

y g

请将这6颗1uF电容置于MT6735的VPROC球正下方附近,并以Via直接串接电容和power trace ,

并使L2愈短愈好。

4. 单面上件:移动背面的6颗1uF至”1st group cap”区。

1) L1定义为”1st group cap”区至MT6735的VPROC的宽形 power trace(“关键路径”),其PCB layout guideline如下:

PWR总共采用1层走线 L1线长≤ 450mil;L

PWR总共采用1层走线,L 线长≤ 450 il;L1线宽≥ 240mil。总共使用1层PWR/1层GND平行走线(请参考下页建议2)。

线宽≥ 240 il 总共使用1层PWR/1层GND平行走线(请参考下页建议2)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 44

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for CPU Power: VPROC

建议2 (单面上件)

建议1(双面上件)

MT6735

1. ”1st group cap”区至 L4 L1

VPROC

VPROC的 power trace

Length≤450mil

之设计实例与建议:

1st ggroup caps

p p

MT6735

VPROC

L5 L4

W≥120mil

MT6735

V OC

VPROC

L6

MT6735

VPROC

L5

W≥240mil

GND

使用1层PWR、1层GND平行走线(L5/L6)、

由于电容在L6,可考虑在 L6将相同电源的 请注意”1st group cap”区至MT6735的摆放原

PWR via用 shape相连 则

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 45

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for CPU Power: VPROC_FB

Bottom Cap

(双面上件: 1uF x 6)

MT6328 L/C 0Ω

MT6735

(PMIC) Network Resistor 1st group cap

(双面上件: 4.7uF x 2, 22uF x 1, 47uF x 2 )

VPROC_FB

(单面上件: 1uF x 6, 4.7uF x 2, 22uF x 1, 47uF x 2 )

VPROC_FB

回馈网络

(VPROC_FB)

MT6328

MT6735会从晶片正下方拉出一對反馈

(VPROC_FB/GND_VPROC_FB)网络回到MT6323 (PMIC),以確保

此對走线为 电压侦测电路,必须

直流損耗可被有效補償。此對走线为一电压侦测电路,必须

直流損耗可被有效補償

减少其他讯号对它的耦合效应。 因此,请在走线或换层via孔

(GND_VPROC_FB)

都做ground shielding的保护。

(VPROC_FB)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 46

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VCORE

Bottom Cap 关键路径

(双面上件 1 F 6)

(双面上件: 1uF x 6) (critical

path) 1st group cap

L2 (双面上件: 4.7uF x 2, 22uF x 2, 47uF x 1 ) L/C MT6328

MT6735 (单面上件: 1uF x 6, 4.7uF x 2, 22uF x 2, 47uF x 1 ) Network (PMIC)

L1

MT6735 VCORE

L/C

MT6328 Network

Close to BB

1. 整个PDN的网络从MT6328 (PMIC ) output pin开始,经过第一级LC低通滤波器, 产生DC直流电源,再流入第一电容群(1st group cap),准备做为电流

抽载的供给来源。双面上件时,可将部分小电容放至芯片下方,可增强电容稳压能力;

2. 从第一电容群(1st group cap)到MT6735的VCORE之走线为关键路径(critical path),此走线均须符合以下描述之PCB layout guideline。

3

3. 双面上件 在”B

双面上件:在”Bottom cap”区间建议放上6颗1uF、2颗4.7uF

”区间建议放上6颗1 F 2颗4 7 F 、 2颗22uF

2颗22 F 、 1颗47uF,放置离VCORE b ll 下方愈近愈好 请依电容值由小而大 由近而

1颗47 F 放置离VCORE balls下方愈近愈好。请依电容值由小而大,由近而

远依序填入电容。

1) L1定义为”正面1st group cap”区至MT6735的VPROC的宽形power trace(“关键路径”),其PCB layout guideline如下:

PWR采用一层走线,L1线长≤ 350mil;L1线宽≥ 100mil 。总共使用1层PWR/1层GND平行走线(请参考下页建议1)。

2)) L2定义为”Bottom cap”区至MT6735之wide power trace的连线,其PCB

p p layout guideline定义如下:

y g

请将这6颗1uF电容置于MT6735的VCORE球正下方附近,并以Via直接串接电容和power trace ,

并使L2愈短愈好。

4. 单面上件:移动背面的6颗1uF至”1st group cap”区。

1) L1定义为”1st group cap”区至MT6735的VPROC的宽形 power trace(“关键路径”),其PCB layout guideline如下:

PWR总共采用1层走线 L1线长≤ 350mil;L

PWR总共采用1层走线,L 线长≤ 350 il;L1线宽≥ 200mil

线宽≥ 200 il (请参考下页建议2)。

(请参考下页建议2)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 47

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VCORE

建议2 (单面上件)

建议1(双面上件)

1. ”1st group cap”区至 MT6735 Length≤350mil L1

L4

VCORE的 power trace VCORE

之设计实例与建议:

1st group caps

W≥100mil

L5

MT6735

VCORE

L4

MT6735

VCORE

W≥200mil

MT6735

L6

VCO

VCORE L5

MT6735

VCORE

GND

由于电容在L6,可考虑在 L6将相同电 使用1层PWR、1层GND平行走线(L3/L4)、

请注意”1st group cap”区至MT6735的摆放

源的PWR via用 shape相连

原则

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 48

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VCORE_FB

Bottom Cap

(双面上件: 1uF x 6)

MT6328 L/C 0Ω

1st group cap MT6735

(PMIC) Network Resistor

(双面上件: 4.7uF x 2, 22uF x 2, 47uF x 1 )

VCORE_FB (单面上件: 1uF x 6, 4.7uF x 2, 22uF x 2, 47uF x 1 )

VCORE_FB

回馈网络

(VCORE_FB)

MT6328

(VCORE_FB)

MT6735会从晶片正下方拉出一對反馈(VCORE_FB/GND_VCORE_FB)

(GND_VCORE_FB)

网络回到MT6323 (PMIC),以確保直流損耗可被有效補償。此對走

线为一电压侦测电路,必须减少其他讯号对它的耦合效应。

线为 电压侦测电路,必须减少其他讯号对它的耦合效应 因此,

请在走线或换层via孔都做ground shielding的保护。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 49

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VLTE

Bottom Cap

(双面上件 1 F 4)

(双面上件: 1uF x 4)

C t ca

Critical

path

L2 1st group cap

MT6735 (双面上件: 4.7uF x 2, 22uF x 3) L/C MT6328

(单面上件: 4.7uF x 2, 1uF x 6, 4.7uF x 2, 22uF x 3 ) Network (PMIC)

L1

MT6735 VLTE

L/C

Network

MT6328

Close to BB

1. 整个PDN的网络从MT6328 (PMIC ) output pin开始,经过第一级LC低通滤波器, 产生DC直流电源,再流入第一电容群(1st group cap),准备做为电流

抽载的供给来源。双面上件时,可将部分小电容放至芯片下方,可增强电容稳压能力;

2. 从第一电容群(1st group cap)到MT6735的VLTE之走线为关键路径(critical path),此走线均须符合以下描述之PCB layout guideline。

3

3. 双面上件 在”B

双面上件:在”Bottom cap”区间建议放上4颗1uF、2颗4.7uF

”区间建议放上4颗1 F 2颗4 7 F 、 2颗22uF

2颗22 F 、 1颗47uF,放置离VLTE b ll 下方愈近愈好 请依电容值由小而大 由近而远

1颗47 F 放置离VLTE balls下方愈近愈好。请依电容值由小而大,由近而远

依序填入电容。

1) L1定义为”正面1st group cap”区至MT6735的VPROC的宽形power trace(“关键路径”),其PCB layout guideline如下:

PWR采用一层走线,L1线长≤ 550mil;L1线宽≥ 80mil 。总共使用1层PWR/1层GND平行走线(请参考下页建议1)。

2)) L2定义为”Bottom cap”区至MT6735之wide power trace的连线,其PCB

p p layout guideline定义如下:

y g

请将这4颗1uF电容置于MT6735的VLTE球正下方附近,并以Via直接串接电容和power trace ,

并使L2愈短愈好。

4. 单面上件:移动背面的6颗1uF至”1st group cap”区。

1) L1定义为”1st group cap”区至MT6735的VLTE的宽形 power trace(“关键路径”),其PCB layout guideline如下:

PWR总共采用1层走线 L1线长≤ 550mil;L

PWR总共采用1层走线,L 线长≤ 550 il;L1线宽≥ 130mil

线宽≥ 130 il (请参考下页建议2)。

(请参考下页建议2)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 50

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VLTE

建议2 (单面上件)

建议1(双面上件)

1. ”1st group cap”区至 MT6735 L1

L4

VLTE的 power trace之 VLTE

设计实例与建议:

1st group caps

W≥80mil

Length≤550mil

L5 MT6735

MT6735

VLTE

L4

VCORE

W≥130mil

L6 MT6735

L5

VCORE

MT6735

VCORE

GND

使用1层PWR、1层GND平行走线

由于电容在L6,可考虑在 L6将相同电 (L3/L4)、

源的PWR via用 shape相连

源的PWR via用 请注意”1

请注意 1st group cap 区至MT6735的摆放

group cap”区至MT6735的摆放

原则

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 51

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Guidelines for Core Power: VLTE_FB

Bottom Cap

Bottom Cap

(2‐sided: 1uF x 4)

1st group cap

MT6328 L/C 0Ω (2‐sided SMT : 4.7uF x 2, 22uF x 3)

MT6735

(PMIC) Network Resistor (1 sided SMT : 4 7uF x 2 1uF x 6 4 7uF x 2 22uF x

(1‐sided SMT : 4.7uF x 2, 1uF x 6, 4.7uF x 2, 22uF x

VLTE_FB 3)

VLTE_FB

回馈网络

(VLTE_FB)

MT6328

MT6735会从晶片正下方拉出一對反馈(VLTE_FB/GND_VLTE_FB)网

络回到MT6323 (PMIC),以確保直流損耗可被有效補償。此對走线

为一电压侦测电路,必须减少其他讯号对它的耦合效应。 因此,

(GND_VLTE_FB) 请在走线或换层via孔都做ground shielding的保护。

(VLTE FB)

(VLTE_FB)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 52

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection

: Via interconnect to PWR

PWR plane/

PWR wide trace

PWR wide trace

GND plane/

GND wide trace

GND wide trace

: Via interconnect to GND

去耦合电容旁之钻孔建议:

1. Via interconnect在PDN掌控跨层之间电流的传递路径, 容易成为各段路径的瓶颈

(短板) 因此要注意l

(短板),因此要注意layout t guideline的建议。

id li 的建议

2. 在PCB背面位置放置电容,注意尽快换层往上连接power plane或power ball。

3. 在去耦合电容旁要在最近位置打PWR和GND via。

4 最好每个去耦合电容(DRAM caps)至少有一对的

4. 最好每个去耦合电容(DRAM )至少有 对的 PWR和GND via

via。在空间足够下,

在空间足够下

建议多打PWR/GND via。电容 pad/via建议比例 Pad : Laser via : PTH via =

1: 1 : 1,并尽可能平均分配PTH & Laser vias ,使其垂直路径为最短 。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 53

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection

VPROC/VCORE/VLTE在PCB上之钻孔建议: (Top view of MT6735 PCB)

1. 在VPROC下方区域放置大、小孔的via数量要足够,以MT6735为例, via数量的最低需求是:6小孔(盲孔)配6大

孔(埋/PTH孔)。

2. 在VCORE下方区域放置大、小孔的via数量要足够,以MT6735为例, via数量的最低需求是:6小孔(盲孔)配6大

孔(埋/PTH孔)。

3. 在VLTE下方区域放置大、小孔的via数量要足够,以MT6735为例, via数量的最低需求是:4小孔(盲孔)配4大孔

(埋/PTH孔)。

4. 小孔(盲孔)尽可能多放,并请直接将这些小孔在出球上做”via on ball”之设计,往下连接wide power trace和大孔

(埋/PTH孔)。另外,在整个power ball的区域范围内平均放置 这些大孔,如右下图示。

5. 除了注意power via的设计, 请同时注意周围ground via安排,将ground via尽量靠近power via,如下一页所示。

适度增加ground via的数量, 可降低via之电感性效应。

大、小孔数量够,

大 小孔数量够 建议!

大、小孔数量不够的! 但分布不均匀!

:VPROC/VCORE/VLTE (PWR balls) :小孔(盲孔) :大孔(埋/PTH孔)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 54

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Via Interconnection

1. 除了注意power via的设计,同时注意周围ground的via安排,以减少via之电感效应,

并缩小“ t

并缩小“return path”,如下图。

th” 如下图

2. GND via之数目和PWR via的比例基本上至少是1:1。

3. GND via距离PWR via愈近愈好,以缩小”return path”。

HDI 1

HDI‐1 双面置件 HDI 2

HDI‐2 单面置件

MT6735 MT6735 MT6735 CAP

CAP CAP

Power GND Signal

2015/2/9 55

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 55

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 56

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169

PCB Layout Guideline

y

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 57

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169芯片外形尺寸图

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 58

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Ball map分布图

RFRX

32K时钟

RF TX

RF TX

32K _EN

26M晶振

LTE TXIQ

LTE BSI LTE RXIQ

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 59

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Placement (1/2)

▪ 针对5M12B,RF RX需要两路接收电路,分别为

DRX(Diversity RX) and PRX(Primary RX)。 RX matching

▪ RX net matching component要尽量靠近MT6169摆放。

et atc g co po e t要尽量靠近 6 69摆放

MT6169

RX net

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 60

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Placement (2/2)

▪ MT6169与PA IC各自需要shielding case隔离,避免de‐sense产生。正反面摆放的情况

下,MT6169和PA必须错开,不能有相交。

▪ RF屏蔽框内表层也要铺GND,屏蔽框下方与内部尽量多打GND via连到主要GND

plane。 PA EPAD 下方尽量多打地孔,以利散热

Top

MT6169 MT6169

PA

PA

Bottom

PA

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 61

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 TX/RX Signals

▪ RF信号线请按照要求做好阻抗控制,TX/PDET(单端50Ω)和RX(单

端50Ω或差分100Ω)。

50 OHM阻

100 OHM阻 抗匹配线

抗匹配线

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 62

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 IQ Signals

▪ I/Q*是差分信号,需两两分开上下左右包GND。

IC Ball

PCB Net Name

Number

LTE_TX_BBIP AK2

IQ LTE TX BBIN

LTE_TX_BBIN AK3

LTE_TX_BBQP AL3

LTE_TX_BBQN AK4

LTE_RX1_BBIP AH7

LTE_RX1_BBIN

_ _ AJ7

LTE_RX1_BBQP AK6

LTE_RX1_BBQN AL6

LTE_RX2_BBIP AK7

LTE_RX2_BBIN AK8

LTE_RX2_BBQP AJ8

LTE_RX2_BBQN AH8

MT6169 IQ

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 63

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Duplexer

▪ 双工器注意事项:

a. 尽量加大双工器GND pin(2,4,5,7,9) L1的铺地范围.

b. b. ANT, RX, TX的出线方向尽量垂直,不要平行出

线。三路信号之间要用GND隔离好,尽量多下

GND via,以达到良好的隔离效果。

cc. L2需要良好的GND plane做为参考。

L2需要良好的GND plane做为参考。

d. 如TX走內層,則表層用GND隔離TX pin與周圍走

線。

RX

绿色plane

L2 GND Ant

GND

TX

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 64

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Crystal

• MT6169 26M晶振L1需要有良好的GND隔离(图一)。

GND GND

• 晶振pin4下方L2需要keepout,L3要有完整的GND plane

作为参考(图二)

作为参考(图二)。 GND

Pin 4 GND

GND

GND GND

L1

L2 L3

图二 图一

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 65

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6169 Others

PCB Net Name IC Ball Number

▪ BSI*信号需要五根合起来上下左右包GND。

LTE_RFIC0_BSI_EN M33

▪ LTE 26MHz(AE10)& APC1(AH10 ball)信号线需要上下左右包

GND。 LTE_RFIC0_BSI_CK L32

▪ AUXADC_REF_RF&THERM_SENSE必须要差分走线,并在下

LTE_RFIC0_BSI_D2 M32

方伴随走一根24MIL的AUXADC_GND。

LTE_RFIC0_BSI_D1 L33

LTE_RFIC0_BSI_D0 L31

MT6169 BSI

MT6169 BSI

26MHz

APC1

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 66

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 67

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158

PCB Layout Guideline

y

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 68

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158芯片外形尺寸图

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 69

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

RF RX MT6158 Ball map分布图

p RF TX

C2K

TX IQ

26M晶振 32K时钟 C2K BSI C2K RXIQ

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 70

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158 Placement

▪ MT6158与PA IC各自需要shielding case隔离,避免de‐sense产生。正反面摆放的情况

下,MT6158和PA必须错开,不能有相交。

▪ RF屏蔽框内表层也要铺GND,屏蔽框下方与内部尽量多打GND via连到主要GND

plane。 PA Epad 下方尽量多打地孔,以利散热。

▪ 元件须与天线开关保 足够好的隔离度

RX 元件须与天线开关保证足够好的隔离度。

▪ TCXO须摆靠近MT6158,下方L2层的地须挖掉。

TOP

TCXO MT6158

BOT PA

MT6158

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 71

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158 TX/RX Signals

▪ RF信号线请按照要求做好阻抗控制, RX差分100Ω和TX单端50Ω。

RX TX 50 OHM

100 OHM

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 72

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158 IQ Signals

▪ I/Q*是差分信号,需两两分开上下左右包GND。

PCB Net IC Ball

Name Number

TX_BBIP_C2K F9

TX_BBIN_C2K G9

TX_BBQP_C2K

_ _ F10

TX_BBQN_C2K E10

RX_BBIP_C2K J8 MT6158 IQ

RX_BBIN_C2K J9

RX BBQP C2K

RX_BBQP_C2K K9

RX_BBQN_C2K K8

DRX_BBIP_C2K K6

DRX_BBIN_C2K J6

DRX BBQP C2K

DRX_BBQP_C2K J7

DRX_BBQN_C2K K7

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 73

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6158 Others

▪ 2组BSI 3 根一起走線並且上下左右包地。

▪ C2K 26M IN需要单独上下左右包地

C2K_26M_IN需要单独上下左右包地。

▪ 双工器处理方式同MT6169。

C2K_26M_IN

TX BSI

IC

PCB

C Net Ball

Name Numb

er

TX_BSI_EN F9

TX_BSI_D0 G9

BSI TX_BSI_CLK F10

BSI_EN E10

BSI_D0 J8

BSI_D0 K8

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 74

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 75

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328

PCB Layout Guideline

y

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 76

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328芯片外形尺寸图

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 77

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Ball map分布图

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 78

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Power Input(1/2)

VSYS Input‐

▪ 22uF电容(C2007)靠近MT6328 VSYS input balls。(图1) 图1

▪ 从22uF电容(C2007)处分星型走线:

input for BUCK ≧50mil

1 VSYS input for BUCK

1.

2.VSYS input for LDO≧ 20mil (图2);

• 进MT6328 VSYS input balls,每一路线宽≧ 20mil,设计

原则请参照 图3.图3

▪ 所有滤波电容靠近MT6328摆放,优先for buck的滤波电

容,其次for LDO. (图4)

LDO 滤波

图2

Buck 滤波电容

电容 图4

图3

MT6328

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 79

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Power Input(2/2) 图3

▪ MT6328 Power Input for Buck GND处理方法

- Buck GND ball以≧20mil trace或 Plane与对应的buck滤波电容

, , , , , 的 脚先连在 起(注意

C2011,C2012,C2013,C2014,C2015,C2043的GND脚先连在一起(注意:

与周边GND trace和plane隔离),再下main GND L3 plane。(图1~图3) 。

尽可能多打一些Via Layer2:BUCK GND与周边

以增加散热,至少6‐

以增加散热,至少6

8个大孔, 25个以上 GND t 和 l 隔离

GND trace和plane隔离

小孔

图1 图2

C2015

5

Layer1

C2014

B3

C

D6

D9

MT6328

C2011

D11

A14

C2012

B16

C2013

C2043

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 80

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Buck Output(1/3)

Buck电路的电感摆放需靠近MT6328(图1),output电流量

请参考以下表格所示。

电感摆放需靠近

MT6328

图1

Output ball

Output Current (A)

name

VPROC 5

MT6328 VLTE 2.8

VCORE1 3.5

VSYS22 1.9

VPA 0.6

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 81

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Buck Output(2/3)

▪ VPROC_PMIC_FB_6328/GND_VPROC_FB_6328,

VLTE_PMIC_FB/GND_VLTE_FB 图1

VCORE_PMIC_FB/GND_VCORE_FB

这三组差分对,需要包地,并避开noise讯号 。(图1)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 82

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Buck Output(3/3)

▪ VSYS22_FB,VPA_FB trace要走4mil,直接接到output bypass CAP上,

并且避开noise讯号 。 (图1 图3)

(图1~图3)

图3

L2008

图1 Ball Number IC Ball Name PCB Net Name

C3 VSYS22_FB VSYS_PMU

B14 VPA_FB VPA_PMU

MT6328

图2

L2009

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 83

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 LDO Output (1/2)

▪ 请参照(表1) 进行电源的走

线宽度设定

LDO Output走线建议 (表1)

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 84

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 LDO Output(2/2)

▪ VREF的电容C2030要靠近MT6325的PIN脚(L4/L3)

C2031/C2057/C2030 摆放

需靠近MT6328 pin 管腳

▪ 电容C2031/C2057要靠近MT6325的PIN脚(T2/T3)

C203

30

30

C2031

C2057

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 85

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Speaker

▪ Speaker走线宽度≥15mil,上下左右都包地。 上下层其他讯号请

与Speaker走线正交

▪ 上下层若有其他讯号请与Speaker走线正交。

上下层若有其他讯号请与Speaker走线正交

线宽度≥15mil

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 86

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Audio Ball

PCB Net Name IC Ball Name

Number

▪ 右边列表的讯号AU_VIN0_P/AU_VIN0_N,

右边列表的讯号AU VIN0 P/AU VIN0 N

M16 AU_VIN0_P AU_VIN0_P

AU_VIN1_P/AU_VIN1_N,AU_VIN2_P/AU_VIN2_N, M15 AU_VIN0_N AU_VIN0_N

AU_HSP/AU_HSN,这四组差分对需要上下左右包地。 K13 AU_VIN1_P AU_VIN1_P

上下层若有其他讯号请与A di 走线正交

上下层若有其他讯号请与Audio走线正交。 L13 AU VIN1 N

AU_VIN1_N AU VIN1 N

AU_VIN1_N

K14 AU_VIN2_P AU_VIN2_P

▪ 右边列表的讯号AU_HPR/AU_HPL需单独分开上下左右包 L14 AU_VIN2_N AU_VIN2_N

地,上下层若有其他讯号请与Audio走线正交。 J14 AU_HSN AU_HSN

K15 AU HSP

AU_HSP AU HSP

AU_HSP

▪ 电容摆放靠近MT6328。(见图1,图2) H16 AU_HPR AU_HPR

H15 AU_HPL AU_HPL

图1

图2

MT6328 MT6328

差分走线

上下层其他讯

号请与

号请与Audio走

走

线正交

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 87

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 32K时钟

32K时钟‐

▪ 32K时钟所有零件要靠近MT6328摆放。

▪ 32K_IN与32K_OUT需(左右、下一层)包地。

▪ RTC32K1V8需包地。

DCXO_32K

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 88

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Others(1/2)

Charger‐

• BATSNS/ISENSE( ball : N3/N4)需按

差分对走线, 旁边避免Noise讯号。

DCXO_32K

差分对走线,旁边避

差分对走线 旁边避

免Noise讯号

差分走线

DCXO_32K

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 89

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6328 Others(2/2)

Gauge‐

• N/CS P( ball : E19/D19)需按差分对走线包地 旁边避免

CS_N/CS_P( ball : E19/D19)需按差分对走线包地,旁边避免

CS

Noise讯号。

DCXO_32K

差分对走线,旁边

差分对走线 旁边

DCXO_32K

避免Noise讯号

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 90

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 91

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625

PCB Layout Guideline

y

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 92

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625 芯片外形尺寸图

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 93

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625 Pin Definition Pin 36: FM 2V8

Pin 37: FM RF_N Pin 34: WiFi 5G RF

Pin 38: FM RF_P Pin 33: WiFi/BT 3V3

Pin39: GPS RF

Pin 31:

Pin40: GPS 1V8 &

MT6625WiFi/BT 2.4G

2 4G RF

6627 core power

Pin 29:

Host reset WiFi/BT

1V8

FM data Package type: QFN 40-lead

WiFi/BT

Package size: 5 x 5mm2

control line

Conn 3-wire

control

System

clock input

Pin 11~14:

11 14: GPS I/Q Pin 15~22: WiFi/BT I/Q

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 94

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

EO

MT6625 vs. MT6735 Placement

US

▪ MT6625距离MT6735最短不低于0.2cm,最长不超过5cm。

MT6625距离MT6735最短不低于0 2cm 最长不超过5cm

• 两者太靠近将造成 短距离微波电路传输灵敏度衰减弱化。

cn

• 两者距离太远也会造成IQ讯号失真 。

m.

.co

tek

MT6625

len MT6625

1@

IQ Side

0.2cm Y 5cm

e0

MT6735

vic

95

ser

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625 IQ Trace

▪ IQ为差分信号,两两走差分,分开左右包GND;

如空间有限,则四根一组,一起上下左右包GND如下面:

Pin22四条trace 组 起 左右包GND

WB RX IP/IN/QP/QN Pin19~Pin22四条trace一组一起

WB_RX_IP/IN/QP/QN Pin19

WB_TX_IP/IN/QP/QN Pin 15~Pin18四条trace一组一起左右包GND

GPS_RX_IP/IN/QP/QN Pin11~Pin14四条trace一组一起 左右包GND

▪ IQ线长需要维持5公分内。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 96

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625 WB Control讯号

• 不可与Power信号及IQ信号重叠。

• 六条trace一起,左右包地。

PCB Net-

Group

name

WB_CTRL WB_CTRL0

WB_CTRL1

WB CTRL2

WB_CTRL2

WB_CTRL

WB_CTRL3

WB_CTRL4

WB CTRL5

WB_CTRL5

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 97

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6625其他控制讯号

▪ 尽可能使用两层走完(L2 or L4),不可与Power信号及IQ信号重叠。

Group PCB Net-name

CONN_SEN

CONN SEN

CONN_SDATA

CONN_SCLK

CONN_CTRL CONN_CTRL

CONN_RSTB

F2W CLK

F2W_CLK

F2W_DATA

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 98

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

RF Trace ‐WiFi /BT/GPS

▪ WiFi /BT共享pin31连到天线。

▪ 需要做到50ohm阻抗和完整的参考平面,走线要远离数字讯号。

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 99

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

RF Trace ‐ FM

▪ FM的走线需为差分走线,以得到较佳的抗噪声能力。

▪ FM RF trace与Audio Jack之间走线会有较长的距离,请务必于一开始即先规

划好FM trace走线的路径 上下左右包GND 左右GND trace尽可能打满GND

划好FM trace走线的路径,上下左右包GND, 左右GND trace尽可能打满GND

VIA 。

▪ 若RF trace无法达到良好的保护,易造成FM假台及FM杂音等问题。

▪ 在包 良好的情形下走内层 可以避免

FM trace在包GND良好的情形下走内层,可以避免ESD干扰。 干扰

4~8mil以上 4~8mil以上

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 100

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

GPS Ext. LNA Placement

▪ GPS的外部 LNA必须放靠

近天线,并且走做好

50ohm阻抗。 close to

antenna

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 101

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Power Trace (1/2)

▪ VCN33_PMU最大电流为200mA,滤波电容须靠近电源pin摆放。

▪ FM_AVDD28最大电流为30mA,滤波电容须靠近电源pin摆放。

VCN33_PMU

C5006

5007

C5

C5008

FM_AVDD28

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 102

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

Power Trace (2/2)

▪ 最大电流为

WB_AVDD18最大电流为50mA ,滤波电容须靠近电源pin摆放。

滤波电容须靠近电源 摆放

▪ GPS_AVDD18最大电流为20mA ,滤波电容须靠近电源pin摆放。

▪ _ 须 先过 ( ) yp 电容

VCN18_PMU Power traces须经先过1uF ( C5015 ) bypass电容,再开始星形走线

分散到WB_AVDD18 &GPS_AVDD18。

C5002

C5005

C5009

C5015

5

经过1uf电容,

经过1uf电容

1_8V星形走线

起点

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 103

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

TCXO摆放规则

1.是TCXO和MT6625之间建议的摆

放位置。

c

2.“a “:隔离GND > 3 mm

c c

c c 3.“b” :隔离GND > 2 mm

a 4. “c” :隔离GND >2 mm

b c

c

• 电流大于>200mA的电路,如PA等,需远离

c TCXO 2cm以上。

MT6625 a

• 其他热源需放至于蓝色框外。

c

c

b c

c b c

a

c c c

c c c

c

c

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 104

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

TCXO走线规则

1. 在布局MT6625模块时必须优先考虑TCXO的位置,

请参考TCXO摆放规则。

2. 右图蓝色区域是TCXO的铺地禁布区,禁布区与 >2mm

TCXO距离,尽量做到>2mm 。

3. TCXO下方GND尽量挖到最远层,让它最大程度避

开所有热源。

4. 不允许有其它信号穿过TCXO的禁布区。

5. TCXO的时钟线在禁布区外必须上下左右包GND。

Keep out

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 105

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

纲目

▪ 概述

▪ 封装

• MT6735芯片外形尺寸

• MT6735 Footprint设计

• MT6735重要信号分布图

▪ 一般设计建议

• 叠构(PCB stack‐up)建议

叠构( )建议

• Common Rules and Via Type

• Placement Notes

• MT6735 fan out

fan out

▪ High‐Speed Digital设计建议

• LPDDR3

• LPDDR2

• PDN design

▪ 其它设计建议

• MT6735 RF interface ‐ MT6169 ‐ MT6158

• MT6328(PMU)

• MT6625 (BT/FM/WiFi/GPS)

• USB/ MIPI/ SIM Card / T‐Card/ eMMC/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 106

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

USB/MIPI/SIM Card

USB/MIPI/SIM C d

/T‐CARD/eMMC

/Differential Pair Layout Suggestion

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved. 2015/2/9 107

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 USB

PCB Net Name IC Ball 阻抗设计

▪ USB_DP/DM差分阻抗为90Ω,需包GND 。

USB_DP_P0 U2

▪ USB_VRT电阻靠近BB。

USB VRT电阻靠近BB USB_DM_P0 V2

90Ω阻抗

CHD_DP T3 不做阻抗

CHD_DM T4 差分走

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 108

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 MIPI

▪ MIPI信号为100Ω差分阻抗设计

TX group: lane‐to‐lane matching ≤60mil 。

RX group: lane‐to‐lane matching ≤100mil 。

▪ 建议做到两两上下左右包GND,若无法达到左右包

GND请保持≧3W rule(如图一) 。

▪ CMMCLK上下左右包GND

CMMCLK上下左右包GND。

▪ MIPI的精密电阻需要放靠近BB

MT6735

MIPI VRT电阻

R122 close

R1227 l to

BB

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 109

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 SIM & T‐CARD

▪ SIM卡的线整组走在一起,SIM1_SCLK/ SIM2_SCLK需单独左右包GND。

▪ T卡的线整组走在一起,SDC1_CLK需单独左右包GND

T卡

SIM1卡

SIM2卡

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 110

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 eMMC (1/2)

▪ MSDC0_CLK & MSDC0_DSL需上下左右包GND 。

MSDC0_DSL

MT6735

MSDC0_CLK

▪ DVDD18_MSDC0电源的电容要尽量靠近MT6735 pin C27放置.滤波

距离控制在150mil范围内

C27

MT6735

CONFIDENTIAL A Copyright © MediaTek Inc. All rights reserved 2015/2/9 111

loginid=eservice01@lentek.com.cn,time=2015-07-03 12:06:38,ip=119.137.35.225,doctitle=MT6735 PCB Design Guidelines-Simplified Chinese--V0_2.pdf,company=Lentek_WCX

MT6735 eMMC (2/2)

▪ MSDC0

MSDC0_RSTB, MSDC0_CMD,

RSTB MSDC0 CMD

MSDC_DAT0~MSDC_DAT7在L1 & L2走线。

▪ L1

L1 & L2走线至少2根1包GND,走线不能重叠,

& L2走线至少2根1包GND,走线不能重叠,

除非是GND

Layer1

建议!

W W W W W W W W W W W W W

L1 (Signal)

W W W W W W W W W W W W W