Академический Документы

Профессиональный Документы

Культура Документы

27 C 256

Загружено:

1webdomainИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

27 C 256

Загружено:

1webdomainАвторское право:

Доступные форматы

27C256

256K (32K x 8) CMOS EPROM

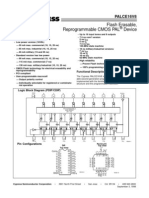

FEATURES PACKAGE TYPES

TSOP

• High speed performance

OE 1 28 A10

- 90 ns access time available A11 2 27 CE

• CMOS Technology for low power consumption A9 3 26 D7

A8 4 25 D6

- 20 mA Active current A13 5 24 D5

A14 6 23

- 100 µA Standby current

D4

27C256

VCC 7 22 D3

• Factory programming available VPP 21

8 VSS

• Auto-insertion-compatible plastic packages A12 9 20 D2

A7 10 19 D1

• Auto ID aids automated programming A6 11 18 D0

A5 12 17 A0

• Separate chip enable and output enable controls A4 13 16 A1

• High speed “express” programming algorithm A3 14 15 A2

• Organized 32K x 8: JEDEC standard pinouts PLCC

A12

A14

A13

Vcc

VPP

NU

A7

- 28-pin Dual-in-line package

32

31

30

- 32-pin PLCC Package A6 5 29 A8

- 28-pin SOIC package A5 6 28 A9

A4 7 27 A11

- 28-pin Thin Small Outline Package (TSOP)

27C256

A3 8 26 NC

A2 9 OE

- 28-pin Very Small Outline Package (VSOP) 25

A1 10 24 A10

- Tape and reel A0 11 23 CE

NC 12 22 O7

• Data Retention > 200 years O0 13 21 O6

• Available for the following temperature ranges:

14

15

16

17

18

19

20

O1

O2

NU

O3

O4

O5

- Commercial: 0˚C to +70˚C VSS

DIP/SOIC

- Industrial: -40˚C to +85˚C

- Automotive: -40˚C to +125˚C

VPP 1 28 VCC

A12 2 27 A14

DESCRIPTION A7 3 26 A13

A6 4 25 A8

A5 5 24 A9

The Microchip Technology Inc. 27C256 is a CMOS A4 6 23 A11

27C256

256K bit electrically Programmable Read Only Memory A3 7 22 OE

(EPROM). The device is organized as 32K words by 8 A2 8 21 A10

A1 9 20 CE

bits (32K bytes). Accessing individual bytes from an A0 10 19 O7

address transition or from power-up (chip enable pin O0 11 18 O6

O1

going low) is accomplished in less than 90 ns. This very 12 17 O5

O2 13 16 O4

high speed device allows the most sophisticated micro- VSS 14 15 O3

processors to run at full speed without the need for

WAIT states. CMOS design and processing enables VSOP

this part to be used in systems where reduced power

consumption and reliability are requirements. OE 22 21 A10

A11 23 20 CE

A complete family of packages is offered to provide the A9 24 19 O7

most flexibility in applications. For surface mount appli- A8 25 18 O6

A13 26 17 O5

cations, PLCC, SOIC, VSOP or TSOP packaging is

27C256

A14 27 16 O4

available. Tape and reel packaging is also available for VCC 28 15 O3

VPP 1 14 VSS

PLCC or SOIC packages.

A12 2 13 O2

A7 3 12 O1

A6 4 11 O0

A5 5 10 A0

A4 6 9 A1

A3 7 8 A2

1996 Microchip Technology Inc. DS11001L-page 1

This document was created with FrameMaker 4 0 4

27C256

1.0 ELECTRICAL CHARACTERISTICS TABLE 1-1: PIN FUNCTION TABLE

1.1 Maximum Ratings* Name Function

VCC and input voltages w.r.t. VSS ........ -0.6V to +7.25V A0-A14 Address Inputs

VPP voltage w.r.t. VSS during CE Chip Enable

programming ....................................... -0.6V to +14.0V

OE Output Enable

Voltage on A9 w.r.t. VSS ...................... -0.6V to +13.5V

Output voltage w.r.t. VSS ............... -0.6V to VCC +1.0V VPP Programming Voltage

Storage temperature .......................... -65˚C to +150˚C O0 - O7 Data Output

Ambient temp. with power applied ..... -65˚C to +125˚C VCC +5V Power Supply

*Notice: Stresses above those listed under “Maximum Ratings” VSS Ground

may cause permanent damage to the device. This is a stress rat-

ing only and functional operation of the device at those or any NC No Connection; No Internal Connec-

other conditions above those indicated in the operation listings of tion

this specification is not implied. Exposure to maximum rating con-

ditions for extended periods may affect device reliability. NU Not Used; No External Connection Is

Allowed

TABLE 1-2: READ OPERATION DC CHARACTERISTICS

VCC = +5V (±10%)

Commercial: Tamb = 0˚C to +70˚C

Industrial: Tamb = -40˚C to +85˚C

Extended (Automotive): Tamb = -40°C to +125°C

Parameter Part* Status Symbol Min. Max. Units Conditions

Input Voltages all Logic "1" VIH 2.0 VCC+1 V

Logic "0" VIL -0.5 0.8 V

Input Leakage all — ILI -10 10 µA VIN = 0 to VCC

Output Voltages all Logic "1" VOH 2.4 V IOH = -400 µA

Logic "0" VOL 0.45 V IOL = 2.1 mA

Output Leakage all — ILO -10 10 µA VOUT = 0V to VCC

Input Capacitance all — CIN — 6 pF VIN = 0V; Tamb = 25°C;

f = 1 MHz

Output Capacitance all — COUT — 12 pF VOUT = 0V; Tamb = 25°C;

f = 1 MHz

Power Supply Current, C TTL input ICC1 — 20 mA VCC = 5.5V; VPP = VCC

Active I,E TTL input ICC2 — 25 mA f = 1 MHz;

OE = CE = VIL;

IOUT = 0 mA;

VIL = -0.1 to 0.8V;

VIH = 2.0 to VCC;

Note 1

Power Supply Current, C TTL input ICC(S) — 2 mA

Standby I, E TTL input 3 mA

all CMOS input 100 µA CE = VCC ± 0.2V

IPP Read Current all Read Mode IPP 100 µA VPP = 5.5V

VPP Read Voltage all Read Mode VPP VCC-0.7 VCC V

* Parts: C=Commercial Temperature Range; I, E=Industrial and Extended Temperature Ranges

Note 1: Typical active current increases .75 mA per MHz up to operating frequency for all temperature ranges.

DS11001L-page 2 1996 Microchip Technology Inc.

27C256

TABLE 1-3: READ OPERATION AC CHARACTERISTICS

AC Testing Waveform: VIH = 2.4V and VIL = 0.45V; VOH = 2.0V VOL = 0.8V

Output Load: 1 TTL Load + 100 pF

Input Rise and Fall Times: 10 ns

Ambient Temperature: Commercial: Tamb = 0˚C to +70˚C

Industrial: Tamb = -40˚C to +85˚C

Automotive: Tamb = -40°C to +125°C

27C256-90* 27C256-10* 27C256-12 27C256-15 27C256-20

Parameter Sym Units Conditions

Min Max Min Max Min Max Min Max Min Max

Address to Output tACC — 90 — 100 — 120 — 150 — 200 ns CE=OE =VIL

Delay

CE to Output Delay tCE — 90 — 100 — 120 — 150 — 200 ns OE = VIL

OE to Output Delay tOE — 40 — 45 — 55 — 65 — 75 ns CE = VIL

CE or OE to O/P tOFF 0 30 0 30 0 35 0 50 0 55 ns

High Impedance

Output Hold from tOH 0 — 0 — 0 — 0 — 0 — ns

Address CE or OE,

whichever goes first

* -10, -90 AC Testing Waveform: VIH = 2.4V and VIL = .45V; VOH = 1.5V and VOL = 1.5V

Output Load: 1 TTL Load + 30pF

FIGURE 1-1: READ WAVEFORMS

VIH

Address Address Valid

VIL

VIH

CE

VIL

t CE(2)

VIH

OE

VIL t OFF(1,3)

t OE(2)

t OH

VOH

Outputs High Z High Z

O0 - O7 Valid Output

VOL

t ACC

Notes: (1) tOFF is specified for OE or CE, whichever occurs first

(2) OE may be delayed up to t CE - t OE after the falling edge of CE without impact on tCE

(3) This parameter is sampled and is not 100% tested.

1996 Microchip Technology Inc. DS11001L-page 3

27C256

TABLE 1-4: PROGRAMMING DC CHARACTERISTICS

Ambient Temperature: Tamb = 25°C ± 5°C

VCC = 6.5V ± 0.25V, VPP = VH = 13.0V ± 0.25V

Parameter Status Symbol Min Max. Units Conditions

Input Voltages Logic”1” VIH 2.0 VCC+1 V

Logic”0” VIL -0.1 0.8 V

Input Leakage — ILI -10 10 µA VIN = 0V to VCC

Output Voltages Logic”1” VOH 2.4 V IOH = -400 µA

Logic”0” VOL 0.45 V IOL = 2.1 mA

VCC Current, program & verify — ICC2 — 20 mA Note 1

VPP Current, program — IPP2 — 25 mA Note 1

A9 Product Identification — VH 11.5 12.5 V

Note 1: VCC must be applied simultaneously or before VPP and removed simultaneously or after VPP

TABLE 1-5: PROGRAMMING AC CHARACTERISTICS

for Program, Program Verify AC Testing Waveform: VIH=2.4V and VIL=0.45V; VOH=2.0V; VOL=0.8V

and Program Inhibit Modes Output Load: 1 TTL Load + 100pF

Ambient Temperature: Tamb=25°C ± 5°C

VCC= 6.5V ± 0.25V, VPP = VH = 13.0V ± 0.25V

Parameter Symbol Min. Max. Units Remarks

Address Set-Up Time tAS 2 — µs

Data Set-Up Time tDS 2 — µs

Data Hold Time tDH 2 — µs

Address Hold Time tAH 0 — µs

Float Delay (2) tDF 0 130 ns

VCC Set-Up Time tVCS 2 — µs

Program Pulse Width (1) tPW 95 105 µs 100 µs typical

CE Set-Up Time tCES 2 — µs

OE Set-Up Time tOES 2 — µs

VPP Set-Up Time tVPS 2 — µs

Data Valid from OE tOE — 100 ns

Note 1: For express algorithm, initial programming width tolerance is 100 µs ±5%.

2: This parameter is only sampled and not 100% tested. Output float is defined as the point where data is no

longer driven (see timing diagram).

DS11001L-page 4 1996 Microchip Technology Inc.

27C256

FIGURE 1-2: PROGRAMMING WAVEFORMS

Program Verify

VIH

Address Address Stable

VIL

t AS

VIH t AH

High Z

Data Data Stable Data Out Valid

VIL

t DS t DH t DF

(1)

13.0V(2)

VPP

5.0V tVPS

6.5V(2)

VCC

5.0V tVCS

VIH

CE

VIL

t PW t OES

VIH t OE

OE (1)

VIL

Notes: (1) t DF and tOE are characteristics of the device but must be accommodated by the programmer

(2) VCC = 6.5 V ±0.25V, VPP = V H = 13.0V ±0.25V for express algorithm

TABLE 1-6: MODES

Operation Mode CE OE VPP A9 O0 - O7

Read VIL VIL VCC X DOUT

Program VIL VIH VH X DIN

Program Verify VIH VIL VH X DOUT

Program Inhibit VIH VIH VH X High Z

Standby VIH X VCC X High Z

Output Disable VIL VIH VCC X High Z

Identity VIL VIL VCC VH Identity Code

X = Don’t Care

1.2 Read Mode For Read operations, if the addresses are stable, the

address access time (tACC) is equal to the delay from

(See Timing Diagrams and AC Characteristics) CE to output (tCE). Data is transferred to the output

Read Mode is accessed when: after a delay from the falling edge of OE (tOE).

a) the CE pin is low to power up (enable) the chip

b) the OE pin is low to gate the data to the output

pins

1996 Microchip Technology Inc. DS11001L-page 5

27C256

1.3 Standby Mode 1.7 Verify

The standby mode is defined when the CE pin is high After the array has been programmed it must be veri-

(VIH) and a program mode is not defined. fied to ensure all the bits have been correctly pro-

When these conditions are met, the supply current will grammed. This mode is entered when all the following

drop from 20 mA to 100 µA. conditions are met:

a) VCC is at the proper level,

1.4 Output Enable b) VPP is at the proper VH level,

This feature eliminates bus contention in multiple bus c) the CE line is high, and

microprocessor systems and the outputs go to a high d) the OE line is low.

impedance when the following condition is true:

1.8 Inhibit

• The OE pin is high and the program mode is not

defined. When programming multiple devices in parallel with dif-

ferent data, only CE need be under separate control to

1.5 Erase Mode (U.V. Windowed Versions) each device. By pulsing the CE line low on a particular

Windowed products offer the ability to erase the mem- device, that device will be programmed; all other

ory array. The memory matrix is erased to the all 1’s devices with CE held high will not be programmed with

state when exposed to ultraviolet light. To ensure com- the data, although address and data will be available on

plete erasure, a dose of 15 watt-second/cm2 is their input pins.

required. This means that the device window must be

1.9 Identity Mode

placed within one inch and directly underneath an ultra-

violet lamp with a wavelength of 2537 Angstroms, In this mode specific data is output which identifies the

intensity of 12,000µW/cm2 for approximately 20 min- manufacturer as Microchip Technology Inc. and device

utes. type. This mode is entered when Pin A9 is taken to VH

(11.5V to 12.5V). The CE and OE lines must be at VIL.

1.6 Programming Mode A0 is used to access any of the two non-erasable bytes

The Express Algorithm has been developed to improve whose data appears on O0 through O7.

on the programming throughput times in a production

environment. Up to ten 100-microsecond pulses are

applied until the byte is verified. No overprogramming Pin Input Output

is required. A flowchart of the express algorithm is

shown in Figure 1-3. H

Identity 0 O O O O O O O

A0 e

Programming takes place when: 7 6 5 4 3 2 1 0

x

a) VCC is brought to the proper voltage,

Manufacturer VIL 0 0 1 0 1 0 0 1 29

b) VPP is brought to the proper VH level, Device Type* VIH 1 0 0 0 1 1 0 0 8C

c) the OE pin is high, and * Code subject to change

d) the CE pin is low.

Since the erased state is “1” in the array, programming

of “0” is required. The address to be programmed is set

via pins A0-A14 and the data to be programmed is pre-

sented to pins O0-O7. When data and address are sta-

ble, a low going pulse on the CE line programs that

location.

DS11001L-page 6 1996 Microchip Technology Inc.

27C256

FIGURE 1-3: PROGRAMMING EXPRESS ALGORITHM

Conditions:

Start

Tamb = 25˚C ±5˚C

VCC = 6.5 ±0.25V

VPP = 13.0 ±0.25V ADDR = First Location

VCC = 6.5V

VPP = 13.0V

X=0

Program one 100 µs pulse

Increment X

Verify Pass

Byte

Fail

No Yes Device

X = 10 ? Failed

Last Yes

Address?

No

Increment Address

VCC = VPP = 4.5V, 5.5V

All

Device Yes bytes No Device

Passed = original Failed

data?

1996 Microchip Technology Inc. DS11001L-page 7

27C256

27C256 Product Identification System

To order or to obtain information (e.g., on pricing or delivery), please use listed part numbers, and refer to factory or listed sales offices.

27C256 – 90 I /TS

Package: L = Plastic Leaded Chip Carrier

P = Plastic DIP (Mil 600)

SO = Plastic SOIC (Mil 300)

TS = Thin Small Outline Package (TSOP) 8x20mm

VS = Very Small Outline Package (VSOP) 8x13.4mm

Temperature Blank = 0˚C to +70˚C

Range: I = -40˚C to +85˚C

E = -40˚C to +125˚C

Access 90 = 90 ns

Time: 10 = 100 ns

12 = 120 ns

15 = 150 ns

20 = 200 ns

Device 27C256 256K (32K x 8) CMOS EPROM

1996 Microchip Technology Inc. DS11001L-page 11

Вам также может понравиться

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- GuppY Manual v46Документ65 страницGuppY Manual v46Coti UlОценок пока нет

- FLAT Autoradio 2009Документ1 страницаFLAT Autoradio 20091webdomainОценок пока нет

- Catalog Monitor Touch e NONДокумент2 страницыCatalog Monitor Touch e NON1webdomainОценок пока нет

- Gal 22 V10Документ7 страницGal 22 V101webdomain100% (3)

- 27 C 16Документ8 страниц27 C 161webdomainОценок пока нет

- Pic 18 LF4620Документ391 страницаPic 18 LF46201webdomainОценок пока нет

- Palce 16 V 8Документ12 страницPalce 16 V 81webdomainОценок пока нет

- Pic 16 F877Документ200 страницPic 16 F8771webdomain100% (2)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Rgs00ts65ehr eДокумент12 страницRgs00ts65ehr eRamón MartinezОценок пока нет

- 3.15: Transistors in Forward Active' Mode Common Base CircuitДокумент1 страница3.15: Transistors in Forward Active' Mode Common Base CircuitMaciel Gomes Dos SantosОценок пока нет

- Simstd Q2 2010 A2Документ3 страницыSimstd Q2 2010 A2manurudin2Оценок пока нет

- Abbey Road 80s Drums Manual EnglishДокумент38 страницAbbey Road 80s Drums Manual EnglishBadOrange123Оценок пока нет

- Ald1107/ald1117: A L D IДокумент6 страницAld1107/ald1117: A L D ISantiago Cadena AlvarezОценок пока нет

- ISF2 Catalog PDFДокумент8 страницISF2 Catalog PDFbdikicОценок пока нет

- MTC Test Nescom 14 May, 2019 AM ElectronicsДокумент9 страницMTC Test Nescom 14 May, 2019 AM ElectronicsIsha Hussain86% (14)

- FETДокумент49 страницFETPalak Agrawal100% (2)

- Tda 8425Документ24 страницыTda 8425vali dОценок пока нет

- Trafo TestsДокумент8 страницTrafo TestsRachit KhannaОценок пока нет

- Electronic Products August 2013Документ88 страницElectronic Products August 2013Alin HrițcuОценок пока нет

- Design and Implementation of 2 Bit Loaded Line Phase ShifterДокумент5 страницDesign and Implementation of 2 Bit Loaded Line Phase ShifterdhvbkhnОценок пока нет

- JT15D Ata 74Документ6 страницJT15D Ata 74Egor85Оценок пока нет

- Design For ESD Prevention and FA - Feb 2012Документ64 страницыDesign For ESD Prevention and FA - Feb 2012Adair NettoОценок пока нет

- Programmable Unijunction TransistorДокумент2 страницыProgrammable Unijunction TransistorBaquiran John Paul Baquiran100% (1)

- Airbag FsДокумент2 страницыAirbag FsSanja StošićОценок пока нет

- KTMICROДокумент28 страницKTMICROthiago garofaloОценок пока нет

- Datasheet IC L7107Документ16 страницDatasheet IC L7107Michael HarveyОценок пока нет

- Report - Solar Thermoelectric Refrigeration NewДокумент16 страницReport - Solar Thermoelectric Refrigeration NewsachinОценок пока нет

- MP3724 ManualmainДокумент12 страницMP3724 ManualmainLes BennettОценок пока нет

- Photovoltaic CellДокумент3 страницыPhotovoltaic Cellsuresh270Оценок пока нет

- AE25Документ3 страницыAE25nandyindyОценок пока нет

- Video Display DevicesДокумент66 страницVideo Display DevicesshabanaОценок пока нет

- Comparadores Auto HechoДокумент107 страницComparadores Auto HechoKozmozОценок пока нет

- 1 1 7 Ak DatasheetsДокумент4 страницы1 1 7 Ak Datasheetsapi-290804719Оценок пока нет

- CITIG 1500 DC Rev.00Документ21 страницаCITIG 1500 DC Rev.00jewel1969Оценок пока нет

- Electric Traction SystemДокумент42 страницыElectric Traction SystemBabu YadavОценок пока нет

- Commutation Torque Ripple Reduction in Brushless DC Motor Using Modified SEPIC ConverterДокумент6 страницCommutation Torque Ripple Reduction in Brushless DC Motor Using Modified SEPIC ConverterSrinath VelavanОценок пока нет

- Eletronics Lab Report - TTLДокумент2 страницыEletronics Lab Report - TTLThan Lwin AungОценок пока нет