Академический Документы

Профессиональный Документы

Культура Документы

AP8064 Datasheet V1.2

Загружено:

Oscar Andres Ramirez AmayaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

AP8064 Datasheet V1.2

Загружено:

Oscar Andres Ramirez AmayaАвторское право:

Доступные форматы

MVSILICON AP8064 Audio Application Processor

AP8064 Datasheet

Audio Application Processor

(ARM Cortex-M3 based)

Rev 1.2

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com

MVSILICON AP8064 Audio Application Processor

DISCLAIMER

All information and data contained in this document are without any commitment, are not

to be considered as an offer for conclusion of a contract, nor shall they be construed as to

create any liability. Any new issue of this document invalidates previous issues. Product

availability and delivery are exclusively subject to our respective order confirmation form;

the same applies to orders based on delivered development samples delivered. By this

publication, Shanghai Mountain View Silicon Co., Ltd.(“MVSILICON”) does not assume

responsibility for patent infringements or other rights of third parties that may result from

its use.

No part of this publication may be reproduced, photocopied, stored in a retrieval system, or

translated in any form or by any means, electronic, mechanical, manual, optical, or

otherwise, without the prior written permission of Shanghai Mountain View Silicon Co.,

Ltd.

Shanghai Mountain View Silicon Co., Ltd. assumes no responsibility for any errors

contained herein.

Revision History

Date Revision Description

2014-03-20 V0.9 Change power supply voltage value

2014-04-11 V1.0 Add the pin function table, LDO33O V-I chart

and the store/reflow requirements

2016-01-18 V1.1 Revised the description of chip features

2016-03-20 V1.2 Add the Codec’s functional block

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com ii

MVSILICON AP8064 Audio Application Processor

Contents

1. Overview.............................................................................................................................1

1.1 Features..................................................................................................................... 1

1.2 CODEC Functional Block........................................................................................ 2

2. Pin Description....................................................................................................................3

2.1 Pin Description..........................................................................................................3

3. Package............................................................................................................................... 6

3.1 Package Diagram...................................................................................................... 6

3.2 Package Dimension Parameter................................................................................. 7

4. Electrical Specification....................................................................................................... 8

4.1 Absolute Maximum Ratings (Note 1).......................................................................8

4.2 Recommended Operating Conditions....................................................................... 8

4.3 Electrical Characteristics.......................................................................................... 8

4.4 LDO33O driving capability...................................................................................... 8

4.5 Audio Performance................................................................................................... 9

5. Store and Reflow...............................................................................................................12

Contact Information.............................................................................................................. 13

Figures

Figure 1 CODEC Functional Block...............................................................................2

Figure 2 Package Diagram (LQFP64-7x7mm / TOP View)......................................... 6

Figure 3 LQFP64-7x7mm Package Dimension Parameter............................................7

Figure 4 LDO33O driving capability.............................................................................8

Tables

Table 1 Pin Description................................................................................................. 3

Table 2 GPIO Pin Function............................................................................................4

Table 3 Absolute Maximum Ratings............................................................................. 8

Table 4 Recommended Operating Conditions...............................................................8

Table 5 Electrical Characteristics.................................................................................. 8

Table 6 Audio DAC Performance .................................................................................9

Table 7 DAC LINE-IN (high quality) Channel Characteristics.................................. 10

Table 8 LINE-IN (normal quality) Channel Characteristics........................................11

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com iii

MVSILICON AP8064 Audio Application Processor

Table 9 MIC Channel Characteristics..........................................................................11

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com iv

MVSILICON AP8064 Audio Application Processor

1. Overview

As a highly integrated SoC for audio application processing, AP8064 integrates ARM

Cortex-M3, OTG, SD/MMC card controller, SARADC, audio DAC, audio ADC, segment

LCD display driver, RTC and IR decoder in a single chip. AP8064 supports Bluetooth

stack, various audio decoders,encoders,and effects. In general AP8064 offers low

power consumption, flexible and more powerful wireless audio player solution.

1.1 Features

ARM Cortex-M3, running @ 96MHz, with 128K byte SRAM

Embedded LDO, with 3.3V output

OTG 2.0 full-speed controller

SD/MMC card controller

12-bit SARADC

Low power RTC with NVM to save external RTC & EEPROM

Display driver for Segment LCD

High speed UART with flow control

Multiple PWM outputs

IR (NEC) decoder

Touch key driver

Multiple GPIOs for various purposes

Code encryption mechanism in SPI-flash

Support FAT16/FAT32 file system

Bluetooth stack including A2DP, AVRCP, HFP, SPP, OBEX etc

Audio input and output

Stereo 20-bit high quality Audio DAC, SNR ≥95dB

Stereo 16-bit high quality Sigma Delta ADC, SNR ≥90dB

Programmable preamp gain for input from microphone and line-in

Programmable ALC / Noise Gate

Built-in headphone driver with “capless” option

>40mW output power into 16Ω / 3.3V

THD –80dB at 20mW, SNR 90dB with 16Ω load

Tone generator

I2S digital audio input/output

9 sample rates supported: 8kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24

kHz, 32 kHz, 44.1 kHz, 48kHz

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 1

MVSILICON AP8064 Audio Application Processor

Audio Algorithms

Decoders: MP2/MP3, WMA, FLAC(8/16/24bit), AAC/MP4/M4A,

WAV(IMA-ADPCM and raw PCM), AIF, AIFC

Encoder: MP2/MP3, IMA-ADPCM

Effects:

Echo

Reverb

MV3D

MVBASS

Pitch shifter

Parametric EQ

Dynamic Range Compression (DRC)

Acoustic Echo Cancellation (AEC)

Programmable frequency shifter for howling prevention

Fast and accurate howling detection and suppression

Serial wire debug (SWD) interface

Firmware updatable through SD/USB drive

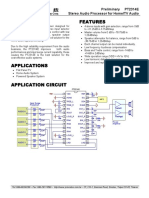

1.2 CODEC Functional Block

Figure 1 CODEC Functional Block

Notes.

1. Adjust the system volume either through DRC pre-gain (DRC on) or mixer gain (DRC off).

2. Direct control of DAC digital volume is NOT recommended.

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 2

MVSILICON AP8064 Audio Application Processor

2. Pin Description

AP8064 is a CMOS device. Floating level on input signals causes unstable device operation

and abnormal current consumption. Pull-up or Pull-down resistors should be used

appropriately for input or bidirectional pins.

Notation Description

I Input

O Output

I/O Bidirectional

PWR Power

GND Ground

2.1 Pin Description

Table 1 Pin Description

Pin Name Pin # Type Description

Audio CODEC interface pins

DAC_R 11 AO audio right channel output

DAC_L 12 AO audio left channel output

DACVMID 10 AI Internal voltage reference

DAC_LINER 14 AI Audio aux right in (high quality)

DAC_LINEL 15 AI Audio aux left in (high quality)

MIC 16 AI MIC input

MICBIAS 17 AI MIC voltage reference

GPIO/MCU IO pins

GPIO_A[0] 26 I/O GPIO PORT, bank A

GPIO_A[10] 27 I/O GPIO PORT, bank A

GPIO_A[16:12] 32:28 I/O GPIO PORT, bank A

GPIO_A[25:17] 42:34 I/O GPIO PORT, bank A

GPIO_B[7:2] 48:43 I/O GPIO PORT, bank B

GPIO_B[31:20] 63:52 I/O GPIO PORT, bank B

GPIO_C[0] 64 I/O GPIO PORT, bank C

GPIO_C[4:1] 4:1 I/O GPIO PORT, bank C

GPIO_C[14:11] 8:5 I/O GPIO PORT, bank C

CLK pins

XIN 19 I 32.768KHz Crystal oscillator input for PLL

XOUT 18 O 32.768KHz Crystal oscillator output for PLL

Power/Ground pins

DVSS 49 GND ground for digital

LDOIN 22 PWR LDO power in

LDO33O 21 PWR LDO 3.3V out

LDO12O 24 PWR LDO 1.2V out

IOVDD 33,51 PWR IO 3.3V

COREVDD 50 PWR power for core

DCOVDD 25 PWR PLL power

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 3

MVSILICON AP8064 Audio Application Processor

DACVDD 13 PWR power for DAC

DACAVSS 9 GND ground for DAC

RTCVDD 20 PWR Power for RTC

MISC pins

POWER_KEY 23 I Power Key

Table 2 GPIO Pin Function

Pin Name Other Function Assignment

GPIO_A[0] PWM0 / UART_TX / CHARGE-LED

GPIO_A[10] IR0 / PWC0 / PWM3 / WAKEUP

GPIO_A[12] 12M_16M_OUT0 / BUART_RTS

GPIO_A[13] FSH_HOLD

GPIO_A[14] FSH_SCK

GPIO_A[15] FSH_SI

GPIO_A[16] FSH_WP

GPIO_A[17] FSH_SO

GPIO_A[18] FSH_CS

GPIO_A[19] SD1_DAT / SPIM1_MISO

GPIO_A[20] SD1_CLK / SPIM1_CLK

GPIO_A[21] SD1_CMD / SPIM1_MOSI

GPIO_A[22] USB2_DP

GPIO_A[23] USB2_DM

GPIO_A[24] BUART_RX / USB1_DP

GPIO_A[25] BUART_TX / USB1_DM

GPIO_B[2] MCLK0_IN / MCLK0_OUT

GPIO_B[3] I2S0_LRCK / PCM0_SYNC / SD2_DAT / SPIM2_MISO

GPIO_B[4] I2S0_BCLK / PCM0_CLK / SD2_CLK / SPIM2_CLK

GPIO_B[5] ADC0 / I2S0_DO / PCM0_DO / SD2_CMD / SPIM2_MOSI / WAKEUP

GPIO_B[6] ADC1 / I2S0_DIN / PCM0_DIN / PWM4 / UART_RX / WAKEUP

GPIO_B[7] ADC2 / IR1 / PWC1 / PWM5 / UART_TX / WAKEUP

GPIO_B[20] LCD0 / PWM7 / SD3_CMD / SPIM3_MOSI / SPIS_MOSI

GPIO_B[21] LCD1 / PWM6 / SD3_CLK / SPIM3_CLK / SPIS_CLK

GPIO_B[22] ADC3 / LCD2 / PWM5 / SD3_DAT / SPIM3_MISO / SPIS_MISO /

WAKEUP

GPIO_B[23] ADC4 / LCD3 / PWM4 / SPIS_CS / WAKEUP

GPIO_B[24] ADC5 / LCD4 / I2S1_LRCK / PCM1_SYNC / PWM3 / WAKEUP

GPIO_B[25] ADC6 / LCD5 / I2S1_BCLK / PCM1_CLK / PWM2 / WAKEUP

GPIO_B[26] LCD6 / I2S1_DO / PCM1_DO / PWM1 / TK0

GPIO_B[27] LCD7 / I2S1_DIN / PCM1_DIN / PWM0 / TK1

GPIO_B[28] BUART_TX / LCD8 / TK2

GPIO_B[29] BUART_RX / LCD9 / TK3

GPIO_B[30] 32K_OUT1 / BUART_CTS / LCD10 / TK4

GPIO_B[31] 12M_16M_OUT1 / BUART_RTS / LCD11 / TK5

GPIO_C[0] 32K_OUT2 / BUART_CTS / LCD12 / TK_CMPOUT

GPIO_C[1] 12M_16M_OUT2 / BUART_RTS / LCD13 / TK6

GPIO_C[2] IR2 / LCD14 / TK7 / WAKEUP

GPIO_C[3] LCD15 / TK8 / UART_TX

GPIO_C[4] LCD16 / TK9 / UART_RX

GPIO_C[11] LINE2_L(normal quality)

GPIO_C[12] LINE2_R(normal quality) / SWV

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 4

MVSILICON AP8064 Audio Application Processor

GPIO_C[13] LINE1_L(normal quality) / SWCLK

GPIO_C[14] LINE1_R(normal quality) / SWD

Notes.

3. ‘TK’ is drive pin for touch key function.

4. ‘CHARGE-LED’ is a function for indicating the charge status of battery even in power down mode.

5. All GPIOs can be used as external interrupt pins.

6. For each of the following modules, only one port group can be activated at any given time, e.g., either

USB1 or USB2 can be activated, but not both at the same time.

Module Port Groups

12M_16M clock 12M_16M_OUT0, 12M_16M_OUT1, 12M_16M_OUT2

32K clock 32K_OUT1, 32K_OUT2

IR IR0, IR1, IR2

I2S I2S0, I2S1

PCM PCM0, PCM1

PWC PWC0, PWC1

SD SD1, SD2, SD3

SPIM SPIM1, SPIM2, SPIM3

USB USB1, USB2

7. For the following modules, there are two scenarios:

Scenario 1, the signal bus can be activated separately, e.g., use UART_TX or UART_RX only;

Scenario 2, only one port can be allocated to the signal bus at any given time, e.g., UART_RX can be

allocated to GPIO_B[6] or GPIO_C[4].

Module Signal Bus Ports

UART_TX GPIO_A[0], GPIO_B[7], GPIO_C[3]

UART

UART_RX GPIO_B[6], GPIO_C[4]

BUART_TX GPIO_A[25], GPIO_B[28]

BUART_RX GPIO_A[24], GPIO_B[29]

BUART

BUART_CTS GPIO_B[30], GPIO_C[0]

BUART_RTS GPIO_A[12], GPIO_B[31], GPIO_C[1]

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 5

MVSILICON AP8064 Audio Application Processor

3. Package

3.1 Package Diagram

Figure 2 Package Diagram (LQFP64-7x7mm / TOP View)

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 6

MVSILICON AP8064 Audio Application Processor

3.2 Package Dimension Parameter

Figure 3 LQFP64-7x7mm Package Dimension Parameter

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 7

MVSILICON AP8064 Audio Application Processor

4. Electrical Specification

4.1 Absolute Maximum Ratings (Note 1)

Table 3 Absolute Maximum Ratings

Parameter Symbol Rating Unit

Storage Temperature TEMP_STG -65 to 150 C

4.2 Recommended Operating Conditions

Table 4 Recommended Operating Conditions

Parameter Symbol Min Typ Max Unit

Power Supply Voltage LDOIN 3.35 5.0 5.5 V

IO Input Voltage VIN 0 3.6 V

Operating Free Air Temperature TEMP_OPR -40 85 C

4.3 Electrical Characteristics

Table 5 Electrical Characteristics

Symbol Parameter Condition Min Typ Max Unit

VIH Input High Voltage 1.6 3.6 V

VIL Input Low Voltage -0.3 1.4 V

VOH Output high voltage @IOH=2mA 3.0 V

VOL Output low voltage @IOL=2mA 0.3 V

IL Input leakage current -10 10 uA

P_PLAY current Current consumption when playing Playing mode 30 mA

RTC current Current consumption for RTC & 16 uA

NVM

4.4 LDO33O driving capability

LDO33O Driving Capability

4

3.5

LDO33O Output Voltage (V)

2.5

1.5

0.5

0

0 50 100 150 200 250 300 350 400

Output Current (mA)

Figure 4 LDO33O driving capability

Note. Not fully tested, characterized only; 2, LDOIN=5V, TA=25℃

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 8

MVSILICON AP8064 Audio Application Processor

4.5 Audio Performance

Table 6 Audio DAC Performance

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

No Filter 93.6/93.6 dB

Dynamic Range

With A-Weighted Filter 95/95 dB

No Filter 95.5/95.6 dB

Signal-to-Noise Ratio

With A-Weighted Filter 98/98 dB

Peak THD+N (@0dBFS) -81/-81 dB

THD+N

0dBFS -75/-75 dB

Frequency Response 0.06 dBV

Output Swing 0.993 Vrms

Inter-channel Gain Mismatch 0.003 dB

Volume Control Step TBD dB

Volume Control Range TBD dB

Group Delay 80 us

Inter-channel Phase Deviation 0.01 degree

Crosstalk -99/-98 dB

The measured output audio spectrum when the output is at -60 dBV

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 9

MVSILICON AP8064 Audio Application Processor

Table 7 DAC LINE-IN (high quality) Channel Characteristics

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

No Filter 88/88 dB

Dynamic Range

With A-Weighted Filter 90/90 dB

No Filter 88/88 dB

Signal-to-Noise Ratio

With A-Weighted Filter 90/90 dB

THD+N Peak THD+N (@-2.4dBFS) -84/-84 dB

Volume Control Step TBD dB

Volume Control Range TBD dB

Group Delay 26 fs

Power Consumption 7.6 mW

Power Supply Rejection Ratio 1kHz, 300mVrms 55 dB

The measured audio spectrum when the analog input is at -2.6 dBV

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 10

MVSILICON AP8064 Audio Application Processor

Table 8 LINE-IN (normal quality) Channel Characteristics

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

No Filter 86 dB

Dynamic Range

With A-Weighted Filter dB

No Filter 85 dB

Signal-to-Noise Ratio

With A-Weighted Filter dB

THD+N Peak THD+N (@-12dBFS) -75 dB

Group Delay 26 fs

Power Consumption 7.6 mW

Power Supply Rejection Ratio 1kHz, 300mVrms 55 dB

Table 9 MIC Channel Characteristics

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

No Filter 87.5/87.5 dB

Dynamic Range

With A-Weighted Filter 90/90 dB

No Filter 85.5/85.5 dB

Signal-to-Noise Ratio

With A-Weighted Filter 88.5/88.5 dB

THD+N Peak THD+N (@-2dBFS) -82/-82 dB

Group Delay 26 fs

Crosstalk TBD dB

Power Consumption 7.6 mW

Power Supply Rejection Ratio 1kHz, 300mVrms 55 dB

Note:

1. “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are

not meant to imply that the device should be operated at these limits.

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 11

MVSILICON AP8064 Audio Application Processor

5. Store and Reflow

AP8064 is a moisture sensitive component. The moisture sensitivity classification is Class 3.

It’s important that the parts are handled under precaution and a proper manner.

The handling, baking and out-of-pack storage conditions of the moisture sensitive components are

described in IPC/JEDC S-STD-033A.

The Technologies recommends utilizing the standard precautions listed below.

1. Calculated shelf life in Sealed Bag: 12 months at <40℃ and <90% relative humidity(RH)

2. Peak Package Body Temperature: 250℃

3. After bag is opened, devices that will be subjected to reflow solder of other high temperature

process must be:

a. Mounted within 168 hours of factory condition ≤30℃ / 60% RH

b. Stored at <10% RH if not used

4. Devices require baking, before mounting if:

a. Humidity indicator card is >10% when read at 23±5℃ immediately after moisture barrier bag is

opened

b. Items 3a or 3b is not met

5. If baking is required, please refer to J-STD-033 standard for low temperature (40℃) baking

requirement in Tape/Reel form.

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 12

MVSILICON AP8064 Audio Application Processor

Contact Information

Shanghai Mountain View Silicon Co Ltd

Shanghai Headquarter:

Suite 4C,Hengyue International Building 3, 1238 Zhangjiang Road,

Shanghai, P.R. China

Zip code: 201203

Tel: 86-21-68549851/68549853/68549857/61630160

Fax: 86-21-61630162

Shenzhen Sales & Technical Support Office:

Suite 6A Olympic Plaza, Shangbao Road, Futian District,

Shenzhen, Guangdong, P.R. China

Zip code: 518034

Tel: 86-755-83522955

Fax: 86-755-83522957

Email: support@mvsilicon.com

Website: http://www.mvsilicon.com

Shanghai Mountain View Silicon Co., Ltd http://www.mvsilicon.com 13

Вам также может понравиться

- General Description Features: Cost Effective LED ControllerДокумент10 страницGeneral Description Features: Cost Effective LED ControlleranilОценок пока нет

- Datasheet CM6802Документ18 страницDatasheet CM6802Gilson3DОценок пока нет

- Si4825 A10 PDFДокумент21 страницаSi4825 A10 PDFTuribio Almeida Barbosa100% (1)

- ET-KA7500: SWITCHMODE Pulse Width Modulation Control CircuitДокумент4 страницыET-KA7500: SWITCHMODE Pulse Width Modulation Control CircuitManutenção FNОценок пока нет

- OB2269Документ12 страницOB2269Juan Ballon100% (1)

- Service Manual: Model: APM200Документ55 страницService Manual: Model: APM200VASILIY GRACHEVОценок пока нет

- CDH l32fd10 Service ManualДокумент42 страницыCDH l32fd10 Service Manualtravieso112Оценок пока нет

- Stormshield SN510: Business Continuity in Complex ArchitecturesДокумент4 страницыStormshield SN510: Business Continuity in Complex ArchitecturesT AnnapooraniОценок пока нет

- LTN140AT07Документ30 страницLTN140AT07JhonSalchichonОценок пока нет

- Samsung+UE32J5000AK CH Ued51Документ56 страницSamsung+UE32J5000AK CH Ued51Miguel Perez Valls100% (1)

- 29TC679FДокумент29 страниц29TC679FGustavo ChavezОценок пока нет

- IC For Samsung UE32D4003BW, LED Driver Control ICДокумент2 страницыIC For Samsung UE32D4003BW, LED Driver Control ICFrancisco ChaoОценок пока нет

- Peavey Pvi-2500 Amplifier SCHДокумент5 страницPeavey Pvi-2500 Amplifier SCHАлексей АндрияшОценок пока нет

- 2576 LДокумент9 страниц2576 LclanonОценок пока нет

- ZS6312 V1.0Документ12 страницZS6312 V1.0Franzua PlasenciaОценок пока нет

- General Description: Multi-Mode Primary Side Regulation (PSR) CV/CC ControllerДокумент11 страницGeneral Description: Multi-Mode Primary Side Regulation (PSR) CV/CC ControllertoolsОценок пока нет

- Silicon PNP Power Transistor: INCHANGE Semiconductor Product SpecificationДокумент2 страницыSilicon PNP Power Transistor: INCHANGE Semiconductor Product SpecificationElton De Souza CouraОценок пока нет

- HX8894CДокумент1 страницаHX8894CTeknisi Kecil0% (1)

- Sony HCD Rv222 Ver 1.1Документ86 страницSony HCD Rv222 Ver 1.1Carlos Raul100% (2)

- Max 17126Документ34 страницыMax 17126918329078250% (2)

- BL1118 Datasheet V1.3.sdcДокумент8 страницBL1118 Datasheet V1.3.sdcrahmat tea100% (1)

- LG Chassis MC 049a RT 29fd15Документ31 страницаLG Chassis MC 049a RT 29fd15Alana Clark100% (2)

- 2 Channel in 4 Channel Out ADAU1701 Sigma DSP Pre-Amplifier With Bluetooth Plug-In ModuleДокумент12 страниц2 Channel in 4 Channel Out ADAU1701 Sigma DSP Pre-Amplifier With Bluetooth Plug-In ModuleNicolae Nechifor100% (1)

- Maida Catalog Specifications Standard SeriesДокумент16 страницMaida Catalog Specifications Standard SeriesRetanaMaferОценок пока нет

- Mini Hi-Fi System: Service ManualДокумент58 страницMini Hi-Fi System: Service ManualJuanCarlosCaballero100% (1)

- BM 81004 MuvДокумент52 страницыBM 81004 MuvHamza Abbasi AbbasiОценок пока нет

- Sharp TV Schematic DiagramДокумент3 страницыSharp TV Schematic Diagramyus11100% (1)

- STK433 070 eДокумент11 страницSTK433 070 evanuzalopeslopes1Оценок пока нет

- Datasheet PDFДокумент26 страницDatasheet PDFHoàng Việt HùngОценок пока нет

- CM6800 Design GuideДокумент34 страницыCM6800 Design GuidedkelicОценок пока нет

- Color TV Horizontal Deflection Output Applications: Data SheetДокумент4 страницыColor TV Horizontal Deflection Output Applications: Data SheetJesus Wladimir RondonОценок пока нет

- Sony HCD Bx3 Dx3Документ66 страницSony HCD Bx3 Dx3videoson100% (2)

- DX 1227Документ11 страницDX 1227Marcos Daniel Muñoz ToledoОценок пока нет

- Integrados 6 TerminalesДокумент9 страницIntegrados 6 TerminalesTitán SotoОценок пока нет

- S 2Документ14 страницS 2Sumit BhatiaОценок пока нет

- HP 2000 Inventec 6050A2498701-MB-A02 AMD SchematicsДокумент45 страницHP 2000 Inventec 6050A2498701-MB-A02 AMD SchematicsMarcos NunfioОценок пока нет

- SOYEA LCD Service Manual PDFДокумент40 страницSOYEA LCD Service Manual PDFraipedriОценок пока нет

- Videocon - Chassis Nano3 CST - Nano4 CSTДокумент29 страницVideocon - Chassis Nano3 CST - Nano4 CSTchanchaldatta0% (1)

- CS11002Документ1 страницаCS11002Rinaldy67% (3)

- Oscilador de TV Plasma Samsung MC34067P - MC33067PДокумент17 страницOscilador de TV Plasma Samsung MC34067P - MC33067PAntonio ChavezОценок пока нет

- Manual de Servicio Sony HCD-NE3Документ44 страницыManual de Servicio Sony HCD-NE3alexОценок пока нет

- MT56E1 Power Blok: MainpowerДокумент12 страницMT56E1 Power Blok: MainpowerNicolas Gandolfo100% (1)

- JVC DXJ 20 Service ManualДокумент101 страницаJVC DXJ 20 Service ManualMuh. Ismail100% (1)

- LCR-0202 Analog Linear CouplingДокумент3 страницыLCR-0202 Analog Linear CouplingJaPan Life100% (1)

- Panasonic TX-40DX600E LA64Документ93 страницыPanasonic TX-40DX600E LA64Marcelo Silvano PenedoОценок пока нет

- Videocon Nano1-Cst Vcn14mbf-CnaДокумент24 страницыVideocon Nano1-Cst Vcn14mbf-CnaRamesh Singh100% (1)

- Manual Service LN40C550J1RДокумент86 страницManual Service LN40C550J1RAngel Luciano Ramon GomezОценок пока нет

- Express Luck Group: Specification PhotoДокумент1 страницаExpress Luck Group: Specification PhotoYesenia Jaime RoaОценок пока нет

- The Specifications of ISL24835IRZДокумент1 страницаThe Specifications of ISL24835IRZFadi100% (1)

- Tps 65148Документ31 страницаTps 65148Jessica Jhon100% (1)

- BN44-00554B PD32GV0Документ3 страницыBN44-00554B PD32GV0Devorador De PecadosОценок пока нет

- Advanced Analog Technology, Inc.: One-Channel Step-Up PWM ControllerДокумент10 страницAdvanced Analog Technology, Inc.: One-Channel Step-Up PWM Controllernestor1209Оценок пока нет

- Regulador 001 A5wДокумент12 страницRegulador 001 A5wvladimirОценок пока нет

- AP8048A Datasheet: Audio Application ProcessorДокумент12 страницAP8048A Datasheet: Audio Application ProcessorEduardoGaleanoОценок пока нет

- Circuito Integrado USB AU6860cДокумент14 страницCircuito Integrado USB AU6860cRonan NolascoОценок пока нет

- AU7860A Datasheet: USB Host MP3/WMA Decoder SOCДокумент14 страницAU7860A Datasheet: USB Host MP3/WMA Decoder SOCsdsОценок пока нет

- Echnical Eference Anual: Version 4.1, January 2020Документ76 страницEchnical Eference Anual: Version 4.1, January 2020Jonathan MendozaОценок пока нет

- AU7843 DatasheetДокумент15 страницAU7843 DatasheetDavid AlfaОценок пока нет

- T260XW02 VGДокумент32 страницыT260XW02 VGOscar Andres Ramirez AmayaОценок пока нет

- T260XW02V5Документ26 страницT260XW02V5Oscar Andres Ramirez AmayaОценок пока нет

- T260XW02 VCДокумент25 страницT260XW02 VCOscar Andres Ramirez AmayaОценок пока нет

- Transistor Sot23 MMBTA92 2DДокумент2 страницыTransistor Sot23 MMBTA92 2DOscar Andres Ramirez AmayaОценок пока нет

- T260XW02SpecVer1 2Документ26 страницT260XW02SpecVer1 2Oscar Andres Ramirez AmayaОценок пока нет

- Leadchip-Lc2127cb5tr C571475Документ6 страницLeadchip-Lc2127cb5tr C571475Oscar Andres Ramirez AmayaОценок пока нет

- Samsung hp-t4254 hp-t5054 (SM)Документ96 страницSamsung hp-t4254 hp-t5054 (SM)Oscar Andres Ramirez AmayaОценок пока нет

- Pegatron Jm50 r3.1 SchematicsДокумент94 страницыPegatron Jm50 r3.1 SchematicsOscar Andres Ramirez AmayaОценок пока нет

- T230XW01 V1Документ28 страницT230XW01 V1Oscar Andres Ramirez AmayaОценок пока нет

- T230XW01Документ28 страницT230XW01Oscar Andres Ramirez AmayaОценок пока нет

- 2Sb595 PNP Epitaxial Silicon Transistor: Low Frequency Power AmplifierДокумент1 страница2Sb595 PNP Epitaxial Silicon Transistor: Low Frequency Power AmplifierOscar Andres Ramirez AmayaОценок пока нет

- Rtl8201e GR RealtekДокумент44 страницыRtl8201e GR RealtekOscar Andres Ramirez AmayaОценок пока нет

- Datasheet PDFДокумент5 страницDatasheet PDFOscar Andres Ramirez AmayaОценок пока нет

- LCD TV: User ManualДокумент125 страницLCD TV: User ManualOscar Andres Ramirez AmayaОценок пока нет

- MMST5401Документ5 страницMMST5401Oscar Andres Ramirez AmayaОценок пока нет

- Ad 28 XMVДокумент20 страницAd 28 XMVcorsini999Оценок пока нет

- Avaya Room System XT7100 DataSheetДокумент8 страницAvaya Room System XT7100 DataSheetPralhad PawarОценок пока нет

- Creator Toolkit TravelAMore-1-vbnjdr 9695 1698840311Документ16 страницCreator Toolkit TravelAMore-1-vbnjdr 9695 1698840311Kunal LalwaniОценок пока нет

- Making Starter Pistol IR'sДокумент6 страницMaking Starter Pistol IR'stshep1100% (1)

- Owners Manual: Two Way Citizens Band Mobile TransceiverДокумент11 страницOwners Manual: Two Way Citizens Band Mobile Transceiverbellscb100% (1)

- User Manual Hardware BIO-PC: Akonic S.AДокумент39 страницUser Manual Hardware BIO-PC: Akonic S.AjumabarrientosОценок пока нет

- Catalogo Runafoto Storeee PDFДокумент52 страницыCatalogo Runafoto Storeee PDFnamapaОценок пока нет

- XAP 800 DatasheetДокумент2 страницыXAP 800 DatasheetPeter FvtОценок пока нет

- Eon210p SS 032111Документ2 страницыEon210p SS 032111Matheus Freitas0% (1)

- Um AM55 AM85 AM105 AM105FX AM125 AM125FX en Es A5Документ32 страницыUm AM55 AM85 AM105 AM105FX AM125 AM125FX en Es A5LittleGaryОценок пока нет

- The Art of Equalization For Custom Home TheatersДокумент3 страницыThe Art of Equalization For Custom Home TheatersArtist RecordingОценок пока нет

- MicrophoneTechniques Vocal 02Документ4 страницыMicrophoneTechniques Vocal 02Ìvan AndonovОценок пока нет

- Akg c1000s SpecДокумент2 страницыAkg c1000s Specevodata5217Оценок пока нет

- APlus Catalog - AC6530MUДокумент1 страницаAPlus Catalog - AC6530MUNgọc TrầnОценок пока нет

- Sound Operated Switch Using A Simple Transistor CircuitДокумент15 страницSound Operated Switch Using A Simple Transistor CircuitIlija Sisoski0% (1)

- The Clap SwitchДокумент10 страницThe Clap SwitchCM-A-12-Aditya BhopalbadeОценок пока нет

- Making The Most of Music With ReSound DFS Ultra II and Music ModeДокумент4 страницыMaking The Most of Music With ReSound DFS Ultra II and Music ModebryankekОценок пока нет

- Micromate Spec SheetДокумент2 страницыMicromate Spec Sheetbagusbp ppmiОценок пока нет

- Numark DM1125Документ16 страницNumark DM1125Henry PalОценок пока нет

- BoschProSound Dealer Price - Jan1 - 2014-2 PDFДокумент64 страницыBoschProSound Dealer Price - Jan1 - 2014-2 PDFJason Brenner100% (1)

- Operation Manual: Digital AmplifierДокумент16 страницOperation Manual: Digital AmplifierAsantha Buddhi HerathОценок пока нет

- Ac '97 and HD Audio Soundmax Codec Ad1986A: Features Enhanced FeaturesДокумент56 страницAc '97 and HD Audio Soundmax Codec Ad1986A: Features Enhanced FeaturesCIACIACIACIACIACIAОценок пока нет

- Transmission Loss in Piping From FisherДокумент8 страницTransmission Loss in Piping From FisheraruatscribdОценок пока нет

- ATH SR5BT DatasheetДокумент1 страницаATH SR5BT DatasheetspeedbeatОценок пока нет

- Icf3003 BrochureДокумент2 страницыIcf3003 BrochureakratorОценок пока нет

- Siddharth Physics IAДокумент7 страницSiddharth Physics IAElement Ender1Оценок пока нет

- 07 VanDyke AerospaceДокумент26 страниц07 VanDyke AerospaceluismcmcОценок пока нет

- 40 Second Message Recorder With Loop OptionДокумент2 страницы40 Second Message Recorder With Loop OptionAnonymous vKD3FG6RkОценок пока нет

- Icom Ic-F7000 OmДокумент68 страницIcom Ic-F7000 OmWimpie DeyselОценок пока нет

- Night Vision Spy Camera Watch Manual Version2 Web ReducedДокумент2 страницыNight Vision Spy Camera Watch Manual Version2 Web ReducedJ.c. MasonОценок пока нет