Академический Документы

Профессиональный Документы

Культура Документы

HT27C020

Загружено:

wardoyoАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

HT27C020

Загружено:

wardoyoАвторское право:

Доступные форматы

HT27C020

CMOS 256K´8-Bit OTP EPROM

Features

· Operating voltage: +5.0V · 256K´8-bit organization

· Programming voltage · Fast read access time: 70ns

- VPP=12.5V±0.2V · Fast programming algorithm

- VCC=6.0V±0.2V · Programming time 75ms typ.

· High-reliability CMOS technology

· Two line controls (OE and CE)

· Latch-up immunity to 100mA from -1.0V to VCC+1.0V

· Standard product identification code

· CMOS and TTL compatible I/O

· Commercial temperature range (0°C to +70°C)

· Low power consumption

· 32-pin DIP/SOP/PLCC package

- Active: 30mA max.

- Standby: 1mA typ.

General Description

The HT27C020 chip family is a low-power, 2048K with respect to Spec. This eliminates the need for WAIT

(2,097,152) bits, +5V electrically one-time programma- states in high-performance microprocessor systems.

ble (OTP) read-only memories (EPROM). Organized The HT27C020 has separate Output Enable (OE) and

into 256K words with 8 bits per word, it features a fast Chip Enable (CE) controls which eliminate bus conten-

single address location programming, typically at 75ms tion issues.

per byte. Any byte can be accessed in less than 70ns

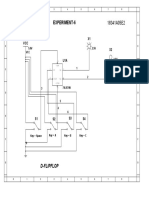

Block Diagram

R o w

X -D e c o d e r C e ll A r r a y

A d d re s s

V C C

C o lu m n V S S

A d d re s s Y -D e c o d e r Y - G a tin g

V P P

C E C E & O E & S A C K T

O E P G M & T E S T & D Q 0 ~ D Q 7

P G M C o n tr o l L o g ic O u tp u t B u ffe r

Rev. 1.10 1 November 21, 2002

HT27C020

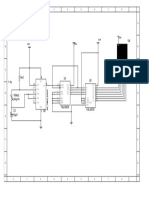

Pin Assignment

V P P 1 3 2 V C C

A 1 6 2 3 1 P G M

P G M

V C C

V P P

A 1 2

A 1 5

A 1 6

A 1 7

A 1 5 3 3 0 A 1 7

3 0

3 2

3 1

A 1 2 4 2 9 A 1 4

4

3

2

1

A 7 5 2 8 A 1 3

A 7 5 2 9 A 1 4

A 6 6 2 7 A 8 2 8

A 6 6 A 1 3

A 5 7 2 6 A 9 A 5 7 2 7 A 8

A 4 8 2 5 A 1 1 A 4 8 2 6 A 9

A 3 9

H T 2 7 C 0 2 0 2 5 A 1 1

A 3 9 2 4 O E

A 2 1 0 3 2 P L C C -A 2 4 O E

A 2 1 0 2 3 A 1 0

A 1 1 1 2 3 A 1 0

A 1 1 1 2 2 C E A 0 1 2 2 2 C E

A 0 1 2 2 1 D Q 7 D Q 0 1 3 2 1 D Q 7

D Q 0 1 3 2 0 D Q 6

1 4

1 5

1 6

1 7

1 8

1 9

2 0

D Q 1 1 4 1 9 D Q 5

V S S

D Q 1

D Q 2

D Q 3

D Q 4

D Q 5

D Q 6

D Q 2 1 5 1 8 D Q 4

V S S 1 6 1 7 D Q 3

H T 2 7 C 0 2 0

3 2 D IP -A /S O P -A

Pin Description

Pin Name I/O/P Description

A0~A17 I Address inputs

DQ0~DQ7 I/O Data inputs/outputs

CE I Chip enable

OE I Output enable

PGM I Program strobe

VPP P Program voltage supply

VCC ¾ Positive power supply

VSS ¾ Negative power supply, ground

Absolute Maximum Rating

Operation Temperature Commercial ..........................................................................................................0°C to +70°C

Storage Temperature.............................................................................................................................-65°C to 125 °C

Applied VCC Voltage with Respect to VSS................................................................................................ -0.6V to 7.0V

Applied Voltage on Input Pin with Respect to VSS..................................................................................... -0.6V to 7.0V

Applied Voltage on Output Pin with Respect to VSS ......................................................................... -0.6V to VCC+0.5V

Applied Voltage on A9 Pin with Respect to VSS ...................................................................................... -0.6V to 13.5V

Applied VPP Voltage with Respect to VSS...............................................................................................-0.6V to 13.5V

Applied READ Voltage (Functionality is guaranteed between these limits) ..............................................+4.5V to +5.5V

Note: These are stress ratings only. Stresses exceeding the range specified under ²Absolute Maximum Ratings² may

cause substantial damage to the device. Functional operation of this device at other conditions beyond those

listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-

ity.

Rev. 1.10 2 November 21, 2002

HT27C020

D.C. Characteristics

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Read operation

VOH Output High Level 5V IOH=-0.4mA 2.4 ¾ ¾ V

VOL Output Low Level 5V IOL=2.1mA ¾ ¾ 0.45 V

VIH Input High Level 5V ¾ 2.0 ¾ VCC+0.5 V

VIL Input Low Level 5V ¾ -0.3 ¾ 0.8 V

ILI Input Leakage Current 5V VIN=0 to 5.5V -5 ¾ 5 mA

ILO Output Leakage Current 5V VOUT=0 to 5.5V -10 ¾ 10 mA

ICC VCC Active Current 5V CE=VIL, f=5MHz, IOUT=0mA ¾ ¾ 30 mA

ISB1 Standby Current (CMOS) 5V CE=VCC±0.3V ¾ 1.0 10 mA

ISB2 Standby Current (TTL) 5V CE=VIH ¾ ¾ 1.0 mA

IPP VPP Read/Standby Current 5V CE=OE=VIL,, VPP=VCC ¾ ¾ 100 mA

Programming operation

VOH Output High Level 6V IOH=-0.4mA 2.4 ¾ ¾ V

VOL Output Low Level 6V IOL=2.1mA ¾ ¾ 0.45 V

VIH Input High Level 6V ¾ 0.7VCC ¾ VCC+0.5 V

VIL Input Low Level 6V ¾ -0.5 ¾ 0.8 V

ILI Input Load Current 6V VIN=VIL, VIH ¾ ¾ 5.0 mA

VH A9 Product ID Voltage 6V ¾ 11.5 ¾ 12.5 V

ICC VCC Supply Current 6V ¾ ¾ ¾ 40 mA

IPP VPP Supply Current 6V CE=VIL ¾ ¾ 10 mA

Capacitance

CIN Input Capacitance 5V VIN=0V ¾ 8 12 pF

COUT Output Capacitance 5V VOUT=0V ¾ 8 12 pF

CVPP VPP Capacitance 5V VPP=0V ¾ 18 25 pF

A.C. Characteristics Ta=25°C±5°C

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Read operation

tACC Address to Output Delay 5V CE=OE=VIL ¾ ¾ 70 ns

tCE Chip Enable to Output Delay 5V OE=VIL ¾ ¾ 70 ns

tOE Output Enable to Output Delay 5V CE=VIL ¾ ¾ 30 ns

CE or OE High to Output Float,

tDF 5V ¾ ¾ ¾ 25 ns

Whichever Occurred First

Output Hold from Address, CE or

tOH 5V ¾ 0 ¾ ¾ ns

OE, Whichever Occurred First

Rev. 1.10 3 November 21, 2002

HT27C020

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Programming operation

tAS Address Setup Time 6V ¾ 2 ¾ ¾ ms

tOES OE Setup Time 6V ¾ 2 ¾ ¾ ms

tDS Data Setup Time 6V ¾ 2 ¾ ¾ ms

tAH Address Hold Time 6V ¾ 0 ¾ ¾ ms

tDH Data Hold Time 6V ¾ 2 ¾ ¾ ms

Output Enable to Output Float

tDFP 6V ¾ 0 ¾ 130 ns

Delay

tVPS VPP Setup Time 6V ¾ 2 ¾ ¾ ms

tPW PGM Program Pulse Width 6V ¾ 30 75 105 ms

tVCS VCC Setup Time 6V ¾ 2 ¾ ¾ ms

tCES CE Setup Time 6V ¾ 2 ¾ ¾ ms

tOE Data Valid from OE 6V ¾ ¾ ¾ 150 ns

VPP Pulse Rise Time During

tPRT 6V ¾ 2 ¾ ¾ ms

Programming

Test waveforms and measurements

2 .4 V

2 .0 V A C

A C D r iv in g M e a s u re m e n t

L e v e ls L e v e l

0 .8 V

0 .4 5 V

tR, tF< 20ns (10% to 90%)

Output test load

1 .3 V

(1 N 9 1 4 )

3 .3 k 9

O u tp u t P in

C L

Note: CL=100pF including jig capacitance

Rev. 1.10 4 November 21, 2002

HT27C020

Functional Description

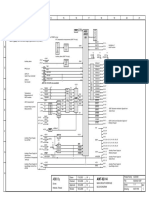

Programming of the HT27C020 To activate this mode, the programming equipment must

When the HT27C020 is delivered, the chip has all force 12.0±0.5V on the address line A9 of the HT27C020.

2048K bits in the ²ONE², or HIGH state. ²ZEROs² are Two identifier bytes may then be sequenced from the de-

loaded into the HT27C020 through programming. vice outputs by toggling address line A0 from VIL to VIH,

when A1=VIH. All other address lines must be held at VIH

The programming mode is entered when 12.5±0.2V is ap- during Auto Product Identification mode.

plied to the VPP pin, OE is at VIH, and CE and PGM are

VIL. For programming, the data to be programmed is ap- Byte 0 (A0=VIL) represents the manufacturer code, and

plied with 8 bits in parallel to the data pins. byte 1 (A0=VIH), the device code. For HT27C020, these

two identifier bytes are given in the Operation mode truth

The programming flowchart in Figure 3 shows the fast table. When A1=VIL, the HT27C020 will read out the bi-

interactive programming algorithm. The interactive al- nary code of 7F, continuation code, to signify the unavail-

gorithm reduces programming time by using 30ms to ability of manufacturer ID codes.

105ms programming pulses and giving each address

only as many pulses as is necessary in order to reliably Read mode

program the data. After each pulse is applied to a given The HT27C020 has two control functions, both of which

address, the data in that address is verified. If the data must be logically satisfied in order to obtain data at out-

is not verified, additional pulses are given until it is veri- puts. Chip Enable (CE) is the power control and should

fied or until the maximum number of pulses is reached be used for device selection. Output Enable (OE) is the

while sequencing through each address of the output control and should be used to gate data to the

HT27C020. This process is repeated while sequencing output pins, independent of device selection. Assuming

through each address of the HT27C020. This part of that addresses are stable, address access time (tACC) is

the programming algorithm is done at VCC=6.0V to as- equal to the delay from CE to output (tCE). Data is avail-

sure that each EPROM bit is programmed to a suffi- able at the outputs (tOE) after the falling edge of OE, as-

ciently high threshold voltage. This ensures that all bits suming the CE has been LOW and addresses have

have sufficient margin. After the final address is com- been stable for at least tACC-tOE.

pleted, the entire EPROM memory is read at

VCC=VPP=5.25±0.25V to verify the entire memory. Standby mode

The HT27C020 has CMOS standby mode which re-

Program inhibit mode

duces the maximum VCC current to 10mA. It is placed in

Programming of multiple HT27C020 in parallel with differ- CMOS standby when CE is at V CC ±0.3V. The

ent data is also easily accomplished by using the Program HT27C020 also has a TTL-standby mode which re-

Inhibit Mode. Except for CE, all like inputs of the parallel duces the maximum VCC current to 1.0mA. It is placed

HT27C020 may be common. A TTL low-level program pulse in TTL-standby when CE is at VIH. When in standby

applied to an HT27C020 CE input with Vpp=12.5±0.2V, mode, the outputs are in a high-impedance state, inde-

PGM LOW, and OE HIGH will program that HT27C020. A pendent of the OE input.

high-level CE input inhibits the HT27C020 from being pro-

grammed. Two-line output control function

Program verify mode To accommodate multiple memory connections, a

Verification should be performed on the programmed two-line control function is provided to allow for:

bits to determine whether they were correctly pro- · Low memory power dissipation

grammed. The verification should be performed with OE · Assurance that output bus contention will not occur

and CE at VIL, PGM at VIH, and VPP at its programming It is recommended that CE be decoded and used as the

voltage. primary device-selection function, while OE be made a

common connection to the READ line from the system

Auto product identification

control bus. This assures that all deselected memory

The Auto Product Identification mode allows the reading devices are in their low-power standby mode and that

out of a binary code from an EPROM that will identify its the output pins are only active when data is desired from

manufacturer and the type. This mode is intended for a particular memory device.

programming to automatically match the device to be

programmed with its corresponding programming algo- System considerations

rithm. This mode is functional in the 25°C±5°C ambient During the switch between active and standby condi-

temperature range that is required when programming tions, transient current peaks are produced on the rising

the HT27C020. and falling edges of Chip Enable. The magnitude of

Rev. 1.10 5 November 21, 2002

HT27C020

these transient current peaks is dependent on the out- effects of the printed circuit board traces on EPROM ar-

put capacitance loading of the device. At a minimum, a rays, a 4.7mF bulk electrolytic capacitor should be used

0.1mF ceramic capacitor (high frequency, low inherent between VCC and VPP for each eight devices. The lo-

inductance) should be used on each device between cation of the capacitor should be close to where the

VCC and VPP to minimize transient effects. In addition, power supply is connected to the array.

to overcome the voltage drop caused by the inductive

Operation mode truth table

All the operation modes are shown in the table following.

Mode CE OE PGM A0 A1 A9 VPP Output

Read VIL VIL X (2) X X X VCC Dout

Output Disable VIL VIH X X X X VCC High Z

Standby (TTL) VIH X X X X X VCC High Z

Standby (CMOS) VCC± 0.3V X X X X X VCC High Z

Program VIL VIH VIL X X X VPP DIN

Program Verify VIL VIL VIH X X X VPP DOUT

Product Inhibit VIH X X X X X VPP High Z

Manufacturer Code (3) VIL VIL X VIL VIH VH (1) VCC 1C

Device Type Code (3) VIL VIL X VIH VIH VH (1) VCC 02

Note: (1) VH = 12.0V ± 0.5V

(2) X=Either VIH or VIL

(3) For Manufacturer Code and Device Code, A1=VIH, When A1=VIL, both codes will read 7F

Product Identification Code

Pins Hex

Code

A0 A1 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 Data

Manufacturer 0 1 0 0 0 1 1 1 0 0 1C

Device Type 1 1 0 0 0 0 0 0 1 0 02

0 0 0 1 1 1 1 1 1 1 7F

Continuation

1 0 0 1 1 1 1 1 1 1 7F

A d d re s s A d d r e s s V a lid

tC E

C E

tD F

tO E

O E

tA C C tO H

O u tp u t O u tp u t V a lid

H IG H Z

Figure 1. A.C. waveforms for read operation

Rev. 1.10 6 November 21, 2002

HT27C020

R e a d

P ro g ra m ( V e r ify )

V IH

A d d re s s A d d r e s s S ta b le

V IL

tA S tO E tA H

V IH

D a ta O u t

D a ta D a ta In V a lid

V IL

tD S tD H

6 .0 V

V C C tD F P

5 .0 V

tV C S

1 2 .5 V tV P S

V P P

5 .0 V

tP R T

V IH

C E

V IL

tC E S

V IH

P G M

V IL

tP W tO E S

V IH

O E

V IL

Figure 2. Programming waveforms

Rev. 1.10 7 November 21, 2002

HT27C020

S T A R T

A d d r e s s = F ir s t L o c a tio n

V C C = 6 .0 V

V P P = 1 2 .5 V

X = 0

P ro g ra m o n e 7 5 m s P u ls e

In te r a c tiv e

S e c tio n

In c re m e n t X

Y e s

X = 2 5 ?

N o

F a il V e r ify

B y te ?

P a s s

N o L a s t F a il

In c re m e n t A d d re s s A d d re s s

Y e s

V C C = V P P = 5 .2 5 V

V e r ify

S e c tio n F a il

V e r ify a ll D e v ic e F a ile d

B y te s ?

P a s s

D e v ic e P a s s e d

N o te : E ith e r 1 0 5 m s o r 3 0 m s p u ls e .

Figure 3. Fast programming flowchart

Rev. 1.10 8 November 21, 2002

HT27C020

Package Information

32-pin DIP (600mil) outline dimensions

3 2 1 7

1 1 6

D

a I

E F G

Dimensions in mil

Symbol

Min. Nom. Max.

A 1635 ¾ 1665

B 535 ¾ 555

C 145 ¾ 155

D 125 ¾ 145

E 16 ¾ 20

F 50 ¾ 70

G ¾ 100 ¾

H 595 ¾ 615

I 635 ¾ 670

a 0° ¾ 15°

Rev. 1.10 9 November 21, 2002

HT27C020

32-pin SOP (450mil) outline dimensions

3 2 1 7

A B

1 1 6

C '

G

D H

a

E F

Dimensions in mil

Symbol

Min. Nom. Max.

A 543 ¾ 557

B 440 ¾ 450

C 14 ¾ 20

C¢ ¾ ¾ 817

D 100 ¾ 112

E ¾ 50 ¾

F 4 ¾ ¾

G 32 ¾ 38

H 4 ¾ 12

a 0° ¾ 10°

Rev. 1.10 10 November 21, 2002

HT27C020

32-pin PLCC outline dimensions

A

B

4 1 3 2 2 9

5 2 8

D C

1 2 2 1

1 3 2 0

K

E F

J G

H

I

Dimensions in mil

Symbol

Min. Nom. Max.

A 485 ¾ 495

B 445 ¾ 455

C 585 ¾ 595

D 545 ¾ 555

E 105 ¾ 115

F ¾ ¾ 140

G 15 ¾ ¾

H ¾ 50 ¾

I 16 ¾ 22

J 24 ¾ 32

K 8 ¾ 12

a 0° ¾ 10°

Rev. 1.10 11 November 21, 2002

HT27C020

Product Tape and Reel Specifications

Reel dimensions

D

T 2

A B C

T 1

SOP 32W

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 100±0.1

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.5

32.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 38.2+0.2

PLCC 32

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 62±1.5

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.5

24.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 30.2±0.2

Rev. 1.10 12 November 21, 2002

HT27C020

Carrier tape dimensions

P 0 P 1 t

D

F

W C B 0

K 1

D 1 P

K 2

A 0

SOP 32W

Symbol Description Dimensions in mm

32.0+0.3

W Carrier Tape Width

-0.1

P Cavity Pitch 16.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 14.2±0.1

D Perforation Diameter 1.55+0.1

D1 Cavity Hole Diameter 2.0+0.25

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 14.7±0.1

B0 Cavity Width 20.9±0.1

K1 Cavity Depth 3.0±0.1

K2 Cavity Depth 3.4±0.1

t Carrier Tape Thickness 0.35±0.05

C Cover Tape Width 25.5

Rev. 1.10 13 November 21, 2002

HT27C020

P 0 P 1

D t

F

W

B 0

C

D 1 P

K 0

A 0

PLCC 32

Symbol Description Dimensions in mm

W Carrier Tape Width 24.0±0.3

P Cavity Pitch 18.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 11.5±0.1

D Perforation Diameter 1.5+0.1

1.55+1.0

D1 Cavity Hole Diameter

-0.05

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 13.1±0.1

B0 Cavity Width 15.5±0.1

K0 Cavity Depth 3.9±0.1

t Carrier Tape Thickness 0.30±0.05

C Cover Tape Width 21.3

Rev. 1.10 14 November 21, 2002

HT27C020

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999

Fax: 886-3-563-1189

http://www.holtek.com.tw

Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635

Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560

Fax: 021-6485-0313

http://www.holtek.com.cn

Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288

Fax: 852-2-742-8657

Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880

Fax: 510-252-9885

http://www.holmate.com

Copyright Ó 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek as-

sumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used

solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable

without further modification, nor recommends the use of its products for application that may present a risk to human life

due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most

up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.10 15 November 21, 2002

Вам также может понравиться

- HT27LC020 Cmos 256K 8-Bit Otp Eprom: FeaturesДокумент16 страницHT27LC020 Cmos 256K 8-Bit Otp Eprom: FeaturesvetchboyОценок пока нет

- 18341A05E2 Experiment-6: VCC X1Документ1 страница18341A05E2 Experiment-6: VCC X1Ashish SrinadhuОценок пока нет

- SchematicsV10 KeysДокумент1 страницаSchematicsV10 KeysGallego OrtizОценок пока нет

- Fire Panel SLD Circuit PLC CompleteДокумент18 страницFire Panel SLD Circuit PLC CompleteASHISH GORAIОценок пока нет

- Terman - Merril: I II III IV X V VI VII Viii IXДокумент1 страницаTerman - Merril: I II III IV X V VI VII Viii IXGabbsMgОценок пока нет

- CircuitДокумент3 страницыCircuitAswathypr KumpalathuОценок пока нет

- Practica 8 ContadoresДокумент1 страницаPractica 8 ContadoresCarlos Francisco Huerta LopezОценок пока нет

- So Do MachДокумент1 страницаSo Do Machxx0a0axxОценок пока нет

- HT23C128 CMOS 16K 8-Bit Mask ROM: FeaturesДокумент12 страницHT23C128 CMOS 16K 8-Bit Mask ROM: FeaturesJoséОценок пока нет

- FMJ A32 - P35 - P35 (3 (SCH)Документ18 страницFMJ A32 - P35 - P35 (3 (SCH)Jory2005Оценок пока нет

- BS62LV1024: Very Low Power/Voltage CMOS SRAM 128K X 8 BitДокумент11 страницBS62LV1024: Very Low Power/Voltage CMOS SRAM 128K X 8 BitDiego SerranoОценок пока нет

- 74AUP1G3208 PhilipsSemiconductorsДокумент16 страниц74AUP1G3208 PhilipsSemiconductorsCer CerОценок пока нет

- ADC0809Документ5 страницADC0809Bhaskar Rao PОценок пока нет

- Controlling Electrical ThinksДокумент11 страницControlling Electrical ThinksGopinathManoharanОценок пока нет

- ADC0809 With CKT, Flow CodeДокумент8 страницADC0809 With CKT, Flow CodeBhaskar Rao PОценок пока нет

- Wio Tracker 1110 v1.0 - SCH - PDF - 20230822Документ4 страницыWio Tracker 1110 v1.0 - SCH - PDF - 20230822marcelu.phdОценок пока нет

- 1 General Description: 4-To-16 Line Decoder/demultiplexer With Input Latches InvertingДокумент14 страниц1 General Description: 4-To-16 Line Decoder/demultiplexer With Input Latches InvertingHeroe APОценок пока нет

- Installation ManualДокумент261 страницаInstallation ManualinkblueОценок пока нет

- Lab 05 2023 2 Hand-OutДокумент3 страницыLab 05 2023 2 Hand-OutNhat Anh NguyenОценок пока нет

- Rits-13 Solution With Answer KeyДокумент7 страницRits-13 Solution With Answer KeyComputer GuyОценок пока нет

- Wire Less Stepper Motor Controll Using MicrocontrollerДокумент51 страницаWire Less Stepper Motor Controll Using MicrocontrollerAnil ReddyОценок пока нет

- Vest3000mkii TurntableДокумент16 страницVest3000mkii TurntableElkin BabiloniaОценок пока нет

- PracticaДокумент1 страницаPracticaJose Refugio Ruiz GarciaОценок пока нет

- 74lvc07apw q100j BufferДокумент14 страниц74lvc07apw q100j BuffersatyamОценок пока нет

- Quiz#08 - 02 - Timer Circuit - To PLCДокумент1 страницаQuiz#08 - 02 - Timer Circuit - To PLC22146015Оценок пока нет

- SIV 2006 - Semester 2, 20192020 Name: Matric No: SIV180011 / 17189250 - C G A - G CДокумент3 страницыSIV 2006 - Semester 2, 20192020 Name: Matric No: SIV180011 / 17189250 - C G A - G CNatashaОценок пока нет

- AQL Chart: Acceptance Quality Levels (Normal Inspection)Документ2 страницыAQL Chart: Acceptance Quality Levels (Normal Inspection)ramnik20098676Оценок пока нет

- El Pala-Pala: Danza Quicha (Trad. Argentin)Документ5 страницEl Pala-Pala: Danza Quicha (Trad. Argentin)Adrian BassiОценок пока нет

- JAW-Chi MaiДокумент3 страницыJAW-Chi MailloreeОценок пока нет

- VSP Lec00 PDFДокумент10 страницVSP Lec00 PDFManish ChavdaОценок пока нет

- Diagrama de RedДокумент5 страницDiagrama de RedLuz Requiz SuloagaОценок пока нет

- DIAGRAMA DE RED - ModДокумент6 страницDIAGRAMA DE RED - ModLuz Requiz SuloagaОценок пока нет

- Diagrama de RedДокумент5 страницDiagrama de RedLuz Requiz SuloagaОценок пока нет

- OptimДокумент2 страницыOptimKaic CangussuОценок пока нет

- Gossip: A Section A 136Документ4 страницыGossip: A Section A 136garyОценок пока нет

- 雪の華Документ2 страницы雪の華iwasawaОценок пока нет

- Accepted Manuscript: Applied Thermal EngineeringДокумент38 страницAccepted Manuscript: Applied Thermal Engineeringlollapalooza109_5725Оценок пока нет

- MK Electronic: Configuration Analyzing (Soft Switch)Документ5 страницMK Electronic: Configuration Analyzing (Soft Switch)Myo KyawОценок пока нет

- Tabla Cuantica de Los Elementos QuimicosДокумент2 страницыTabla Cuantica de Los Elementos QuimicosAntonio AngrisanoОценок пока нет

- Time Division MultiplexingДокумент23 страницыTime Division MultiplexingAshish Ranjan0% (1)

- Schematic - TUGAS 10.2 Fiqri Rahman Suryadi - 2023-05-23Документ1 страницаSchematic - TUGAS 10.2 Fiqri Rahman Suryadi - 2023-05-23FIQRI RAHMAN SURYADIОценок пока нет

- 74LVC1G175-Q100: 1. General DescriptionДокумент13 страниц74LVC1G175-Q100: 1. General DescriptionsamactrangОценок пока нет

- 1920s Printable Escape Room 2Документ8 страниц1920s Printable Escape Room 2patmcgarry100% (1)

- Parcial 2 ProgramacionДокумент6 страницParcial 2 ProgramacionNANTESSОценок пока нет

- AQL Chart: Acceptance Quality Levels (Normal Inspection)Документ2 страницыAQL Chart: Acceptance Quality Levels (Normal Inspection)Meylinda Kartika SariОценок пока нет

- AQLChartДокумент2 страницыAQLChartMIGUEL MARTINGОценок пока нет

- 00233421AINTДокумент1 страница00233421AINTtorbaОценок пока нет

- Bread - IF PDFДокумент2 страницыBread - IF PDFkiemarkОценок пока нет

- Qdoc - Tips Gypsy-UkuleleДокумент10 страницQdoc - Tips Gypsy-UkuleleAndrea FagioniОценок пока нет

- Quiz#08 - 01 - Timer Circuit - To PLCДокумент1 страницаQuiz#08 - 01 - Timer Circuit - To PLC22146015Оценок пока нет

- Examen Final 1Документ132 страницыExamen Final 1Angel GarayОценок пока нет

- Operating Instructions For Desauty'S Bridge: I I JWC JWCДокумент5 страницOperating Instructions For Desauty'S Bridge: I I JWC JWCAnuОценок пока нет

- TheSwan (LoG)Документ7 страницTheSwan (LoG)Nicole AlvaradoОценок пока нет

- Project Management OUM: Critical Path Method - Logic Network Activity Description Duration IPAДокумент3 страницыProject Management OUM: Critical Path Method - Logic Network Activity Description Duration IPAJELSONОценок пока нет

- 74HC86 74HCT86: 1. General DescriptionДокумент13 страниц74HC86 74HCT86: 1. General DescriptionOleg StrashenkoОценок пока нет

- Policy Blues: As Recorded by Blind BlakeДокумент2 страницыPolicy Blues: As Recorded by Blind BlakeTakashiInadaОценок пока нет

- COMP4204: Advanced Data Structure and Algorithms Tutorial 6 (Graphs)Документ3 страницыCOMP4204: Advanced Data Structure and Algorithms Tutorial 6 (Graphs)محمد العبريОценок пока нет

- MachДокумент1 страницаMachhamsterkhinОценок пока нет

- FCC - Element-9 GMDSS Maintainer License: September 2012 Section-A: VHF-DSC Equipment & Operation: Key Topic-1: Frequency and BandwidthДокумент51 страницаFCC - Element-9 GMDSS Maintainer License: September 2012 Section-A: VHF-DSC Equipment & Operation: Key Topic-1: Frequency and BandwidthHrishikesh SinghОценок пока нет

- Experiment No.03: Implementation of Dipole Antenna Using CST Microwave Studio. Objectives: Equipment RequiredДокумент9 страницExperiment No.03: Implementation of Dipole Antenna Using CST Microwave Studio. Objectives: Equipment RequiredM. Ahmad RazaОценок пока нет

- Advance CMOS Cell Design-Book3Документ44 страницыAdvance CMOS Cell Design-Book3Melvic MacalaladОценок пока нет

- Kick Start BoardДокумент52 страницыKick Start BoardHarikrishnakattyОценок пока нет

- Bidirectional 12kV To 1.2kV DC-DC Converter For Renewable Energy ApplicationsДокумент8 страницBidirectional 12kV To 1.2kV DC-DC Converter For Renewable Energy ApplicationsJyothiPunemОценок пока нет

- Analog Servo Drive: Description Power RangeДокумент9 страницAnalog Servo Drive: Description Power RangeElectromateОценок пока нет

- Stator Ground ProtectionДокумент47 страницStator Ground ProtectionAnonymous CO7aaHrОценок пока нет

- Transmission Lines: Electronic Systems and TechnologiesДокумент73 страницыTransmission Lines: Electronic Systems and TechnologiesKier SinghОценок пока нет

- Mxfe Quad, 16-Bit, 12 Gsps RF Dac and Dual, 12-Bit, 6 Gsps RF AdcДокумент34 страницыMxfe Quad, 16-Bit, 12 Gsps RF Dac and Dual, 12-Bit, 6 Gsps RF AdcDanielОценок пока нет

- Schematic Diagram - 1 (Main 1 / 2: Amp)Документ7 страницSchematic Diagram - 1 (Main 1 / 2: Amp)api-3703813Оценок пока нет

- Analog-to-Digital ConverterДокумент21 страницаAnalog-to-Digital ConverterThành TrườngОценок пока нет

- Eee NTДокумент19 страницEee NTvijayalakshmiv VEMURIОценок пока нет

- DSD Unit 1Документ97 страницDSD Unit 1Shivakumar 2108Оценок пока нет

- Silicon Chip 2008.03Документ108 страницSilicon Chip 2008.03David Elias Flores Escalante100% (4)

- Vijeo Citect PDFДокумент14 страницVijeo Citect PDFtiagalОценок пока нет

- YaДокумент134 страницыYaHengkiОценок пока нет

- IR Senor Obstacle Avoidance Keyes KY 032Документ6 страницIR Senor Obstacle Avoidance Keyes KY 032Andy ZhuОценок пока нет

- 1.initial Boot SequenceДокумент94 страницы1.initial Boot SequenceTommaso Mauro TautonicoОценок пока нет

- SRX828S: Key FeaturesДокумент3 страницыSRX828S: Key FeaturesvishnuОценок пока нет

- The History of ARMДокумент1 страницаThe History of ARMmani_vlsiОценок пока нет

- @@D@-@ @@d@-@/na20d@-@: Cp1e-E Cp1e-NДокумент44 страницы@@D@-@ @@d@-@/na20d@-@: Cp1e-E Cp1e-NEDEVALDOОценок пока нет

- Single Electron TransistorДокумент15 страницSingle Electron TransistorAnonymous TZuulYuUlSОценок пока нет

- UP CORE - Carrier Board - Design Guide - 20171116 - A01-2Документ40 страницUP CORE - Carrier Board - Design Guide - 20171116 - A01-2Munawar AliОценок пока нет

- User Manual 2195612Документ2 страницыUser Manual 2195612BCservis BCservisОценок пока нет

- A Designer's Guide To Built-In Self-Test - Charles E. StroudДокумент338 страницA Designer's Guide To Built-In Self-Test - Charles E. StroudPataque1Оценок пока нет

- Speed Command (Frequency) : - Inv034 - Movevelocity: Inv 034 Basic Function SymbolДокумент5 страницSpeed Command (Frequency) : - Inv034 - Movevelocity: Inv 034 Basic Function SymbolJosephОценок пока нет

- Irig-B Decoder Based On Fpga For Synchronization in Pmus by Considering Different Input FormatsДокумент6 страницIrig-B Decoder Based On Fpga For Synchronization in Pmus by Considering Different Input FormatsvitpowerguyОценок пока нет

- DVDR3570H - SB KL Ex Si - 1221814332Документ54 страницыDVDR3570H - SB KL Ex Si - 1221814332olomouc7267Оценок пока нет

- DHI-NVR2104HS-P-S2: Lite MPДокумент3 страницыDHI-NVR2104HS-P-S2: Lite MPLuis Daniel Asbun FriasОценок пока нет

- Diagrama de Fuente BA21F0F0102 - Fuente Philips TV LCDДокумент1 страницаDiagrama de Fuente BA21F0F0102 - Fuente Philips TV LCDneumatraxxx83% (36)