Академический Документы

Профессиональный Документы

Культура Документы

Dr. P.V.V. Rama RaoDr. RAMA RAO P.V.V

Загружено:

HEMANTH BATTULA0 оценок0% нашли этот документ полезным (0 голосов)

55 просмотров1 страницаThis document provides a faculty profile for Dr. RAMA RAO P.V.V from the Department of Electrical & Electronics Engineering at Sri Vasavi Engineering College. It lists his educational qualifications including a Ph.D from JNTU Hyderabad, employment experience in various teaching and administrative roles, current position as Professor and Dean of R&D, achievements and publications, sponsored research projects, patents, and contact details.

Исходное описание:

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThis document provides a faculty profile for Dr. RAMA RAO P.V.V from the Department of Electrical & Electronics Engineering at Sri Vasavi Engineering College. It lists his educational qualifications including a Ph.D from JNTU Hyderabad, employment experience in various teaching and administrative roles, current position as Professor and Dean of R&D, achievements and publications, sponsored research projects, patents, and contact details.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

55 просмотров1 страницаDr. P.V.V. Rama RaoDr. RAMA RAO P.V.V

Загружено:

HEMANTH BATTULAThis document provides a faculty profile for Dr. RAMA RAO P.V.V from the Department of Electrical & Electronics Engineering at Sri Vasavi Engineering College. It lists his educational qualifications including a Ph.D from JNTU Hyderabad, employment experience in various teaching and administrative roles, current position as Professor and Dean of R&D, achievements and publications, sponsored research projects, patents, and contact details.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 1

+91-8818-284355, 284344, 284544 Ext: 337; Fax: +91-8818-284322 Visit us at: www.srivasaviengg.ac.

in

SRI VASAVI ENGINEERING COLLEGE

(Sponsored by Sri Vasavi Educational Society)

Approved by AICTE, New Delhi and Permanently Affiliated to JNTUK, Kakinada

Pedatadepalli, TADEPALLIGUDEM – 534 101, W.G. Dist, (A.P.)

Department of Electrical & Electronics Engineering

FACULTY PROFILE

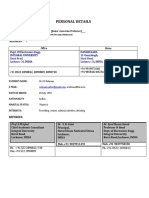

1. Name: Dr. RAMA RAO P.V.V.

2. Date of Birth: 05-06-1975

3. Highest Qualification: Ph.D.

4. Academic Qualifications

S. No. Degree Institution/ University Year % Division/Class

1 Ph.D. (EEE) JNTU Hyderabad 2012 --- Not Applicable

2 M. Tech (EPE) JNTU College of Engineering, Hyderabad 2006 84.33 I (Distinction)

3 B. Tech (EEE) JNTU College of Engineering, Hyderabad 1998 75.96 I (Distinction)

5. Employment Experience

S. No. Period Position & Organization Nature of Job

th

1 7 March 2017 to till Professor in EEE & Dean (R&D), Sri Vasavi Teaching, Administration

date Engineering College, Tadepalligudem & Research

th th

2 6 May 2011 to 6 Professor & HOD, Dept. of EEE, Shri Vishnu Teaching, Administration

March 2017 Engineering College for Women, Bhimavaram & Research

3 1st June 2010 to 30th Professor & HOD of EEE, Arjun College of Teaching &

October 2010 Technology and Sciences, Hyderabad Administration

4 December 2006 to May Professor & HOD of EEE in Tirumala Engineering Teaching &

2010 College, Bogaram, Hyderabad Administration

5 July 2000 to January Assistant Professor of EEE, Sri Venkateswara Teaching

2007 Engineering College, Suryapet

6 October 1999 to August Adhoc-lecturer, EEE Department, Godavari Teaching

2000 Institute of Engineering & Technology,

Rajahmundry

7 September 1998 to Electrical Project Coordinator, M/s. Aster Electrical installations at

October 1999 Teleservices Private Limited, Secunderabad. cellular towers

6. Date of joining in this Institution: 07.03.2017

7. Status as on date of joining : Professor

8. Present Status : Professor and Dean (R&D)

9. Number of promotions since date of joining: Nil

10. Achievements since date of joining:

No. of International Journals 01

No. of Workshops Attended 00

No of International Conferences 01

Memberships MISTE, FIE, MWASET, MIAENG & MIEEE

Others Editor-in-chief of i-Manager’s Journal on Circuits & Systems, reviewer

for few international journals and conferences

Acted as chair for one session in international conferences organized by

Conferences world (ICRTSEM 2016) and KL University (ICSEG 2016),

Organized 3 National conferences, ETE 2014, ETE 2015, ETE 2016

IE INDIA Andhra Pradesh State Electrical Division Member Elected for

2016-18

Total Publications: International Journals = 38, International Conferences = 34, National Conferences = 21

11. Sponsored Research Projects (last five years)

S. No. Title Agency Period Amount Achievements

1 Structured framework for CSI Scheme, November 2013 Rs. 27.89 5 publications, 1

handling the design nonlinearity DST to October 2016 Lakhs M. Tech, 1 Ph.D.

2 FPGA Based Multilevel WOS-A, DST January 2012 to Rs. 25.10 3 Publications,

Inverter March 2015 Lakhs Hardware

12. Filed 2 patents

13. Address: Flat No.: 401, Lekha Vihar Apartment, Besides LIC Office, Tadepalligudem – 534101, Mobile No.:

7569508112, Email: pvvmadhuram@gmail.com

I hereby declare that the above details are true to the best of my knowledge and belief.

Signature

Вам также может понравиться

- Artificial Intelligence for Future Generation RoboticsОт EverandArtificial Intelligence for Future Generation RoboticsRabindra Nath ShawРейтинг: 5 из 5 звезд5/5 (1)

- Action Plan For School CampainДокумент2 страницыAction Plan For School CampainxypherexvvОценок пока нет

- DLL in DIASS WK 1Документ4 страницыDLL in DIASS WK 1MaTeresa Berondo100% (4)

- Project Expo 22 Brochure FinalДокумент2 страницыProject Expo 22 Brochure FinalV MadhuОценок пока нет

- CMT Lab RubricsДокумент1 страницаCMT Lab Rubricsjonilyn florentinoОценок пока нет

- Bio-Chemical Data of DR - Vijayan Gurumurthy Iyer - 21 ST December 2021Документ176 страницBio-Chemical Data of DR - Vijayan Gurumurthy Iyer - 21 ST December 2021Dr.Vijayan Gurumurthy IyerОценок пока нет

- 11 04 2018 Bio Data DR Vijayan GurumurthДокумент67 страниц11 04 2018 Bio Data DR Vijayan GurumurthVikram JaimanОценок пока нет

- DR PSR CVДокумент5 страницDR PSR CVSUDHAKARA REDDY PENUBOLUОценок пока нет

- Dr. Y. Raja Rao: EducationДокумент3 страницыDr. Y. Raja Rao: EducationnavecОценок пока нет

- Dr.M.Venkateshkumar CVДокумент28 страницDr.M.Venkateshkumar CVVenkatesh Kumar100% (1)

- I. Personal Details Name: Official Address:: Glandeva@vjec - Ac.inДокумент21 страницаI. Personal Details Name: Official Address:: Glandeva@vjec - Ac.inGlan DevadhasОценок пока нет

- CV-Soumitra Das-Feb2020 PDFДокумент8 страницCV-Soumitra Das-Feb2020 PDFSoumitra DasОценок пока нет

- Oct2015 ElectSci MridulaДокумент7 страницOct2015 ElectSci MridulaPavitra MurugesanОценок пока нет

- Detailed Bio-Data of DR - Vijayan Gurumurthy Iyer For Job Application As On 19 TH November 2021Документ174 страницыDetailed Bio-Data of DR - Vijayan Gurumurthy Iyer For Job Application As On 19 TH November 2021Dr Vijayan Gurumurthy IyerОценок пока нет

- Bio-Data of DR - Vijayan Gurumurthy Iyer - 23 RD August 2021Документ170 страницBio-Data of DR - Vijayan Gurumurthy Iyer - 23 RD August 2021Dr.Vijayan Gurumurthy IyerОценок пока нет

- Vasumathi D ProfileДокумент6 страницVasumathi D ProfileShreshta PuppamОценок пока нет

- CV GlaДокумент4 страницыCV GlamailmekaranОценок пока нет

- 1 - Bio-Data of DR - Vijayan Gurumurthy Iyer - 28 TH July 2021Документ163 страницы1 - Bio-Data of DR - Vijayan Gurumurthy Iyer - 28 TH July 2021Dr Vijayan Gurumurthy IyerОценок пока нет

- Dr. Mohankumar N Resume - 4jan2023Документ8 страницDr. Mohankumar N Resume - 4jan2023Mohan KumarОценок пока нет

- ANNUAL REPORT - Copy 1Документ102 страницыANNUAL REPORT - Copy 1Dhiraj KumarОценок пока нет

- Udhav Bhosle - July2017Документ8 страницUdhav Bhosle - July2017Yogesh KadamОценок пока нет

- ShashiДокумент3 страницыShashiLKОценок пока нет

- Veda - Faculty ProfileДокумент4 страницыVeda - Faculty ProfileSakthidasan SankaranОценок пока нет

- Updated Bio-Data of DR - Vijayan Gurumurthy IyerДокумент80 страницUpdated Bio-Data of DR - Vijayan Gurumurthy IyerDr.Vijayan Gurumurthy IyerОценок пока нет

- Sanjeev TДокумент4 страницыSanjeev TNaresh KumarОценок пока нет

- Inderdeep Singh Mar 25 PDFДокумент25 страницInderdeep Singh Mar 25 PDFAakashSamaddarОценок пока нет

- RC Soft Compu..5-20 Oct 20 MERGE FILE CompressedДокумент9 страницRC Soft Compu..5-20 Oct 20 MERGE FILE CompressedyrssenoritaОценок пока нет

- Sri Venkateswara University:: Tirupati: Bio-DataДокумент5 страницSri Venkateswara University:: Tirupati: Bio-Data5081 MAKAM SURYA TEJAОценок пока нет

- National Institute of Technology, Tiruchirappalli: Performa For CV of Faculty/ Staff MembersДокумент20 страницNational Institute of Technology, Tiruchirappalli: Performa For CV of Faculty/ Staff MembersGlan DevadhasОценок пока нет

- Curriculam Vitae: National Institute of Technology, Tiruchirappalli: Performa For CV of Faculty/ Staff MembersДокумент20 страницCurriculam Vitae: National Institute of Technology, Tiruchirappalli: Performa For CV of Faculty/ Staff MembersSathya RupanОценок пока нет

- Personal Details: Name: Dr. Saifur RahmanДокумент6 страницPersonal Details: Name: Dr. Saifur Rahmanvenkiscribd444Оценок пока нет

- Faculty CV - DR - Md. Kafiul Islam - Summer - 2020Документ4 страницыFaculty CV - DR - Md. Kafiul Islam - Summer - 2020Md Kafiul IslamОценок пока нет

- Dr. Somashekhar S. HiremathДокумент18 страницDr. Somashekhar S. HiremathdkannanapkОценок пока нет

- Profile of Dr. Prakasha SДокумент3 страницыProfile of Dr. Prakasha SSathish YAОценок пока нет

- Biodata DR D S Deshmukh 03.02.2020Документ27 страницBiodata DR D S Deshmukh 03.02.2020Sheetal DeshmukhОценок пока нет

- Details Regarding Brand TeamДокумент23 страницыDetails Regarding Brand Team5025linuxОценок пока нет

- AICTE Mandatory PDFДокумент26 страницAICTE Mandatory PDFSVCET SVCETОценок пока нет

- Mahesh Resume-ChennaiДокумент66 страницMahesh Resume-ChennaiMahesh KumarОценок пока нет

- Resume MaheshДокумент4 страницыResume MaheshMahesh KumarОценок пока нет

- RESUME MAHESH CompДокумент17 страницRESUME MAHESH CompMahesh KumarОценок пока нет

- HTTPSWWW - Kitsw.ac - Inhomepage PagesKAR CV 15-04-2019 PDFДокумент26 страницHTTPSWWW - Kitsw.ac - Inhomepage PagesKAR CV 15-04-2019 PDFVamshi KeathamОценок пока нет

- RESUMEPHOTOДокумент4 страницыRESUMEPHOTOjulietОценок пока нет

- Resume ECE ProfessorДокумент5 страницResume ECE ProfessorPragya Srivastava AgrawalОценок пока нет

- CV - DrSuyam - Website (Latest)Документ13 страницCV - DrSuyam - Website (Latest)Serge KewouОценок пока нет

- CV JrkumarДокумент20 страницCV JrkumarAnonymous fgrTyKxxsLОценок пока нет

- Faculty Data Tarni Joshi EIДокумент3 страницыFaculty Data Tarni Joshi EISkillytek ServiceОценок пока нет

- FDP - Brochure & ScheduleДокумент2 страницыFDP - Brochure & Scheduleavinash dОценок пока нет

- Syed A Sattar Bio DataДокумент4 страницыSyed A Sattar Bio DatazulkharnainОценок пока нет

- Nba Final Present A Ion Production DeptДокумент77 страницNba Final Present A Ion Production DeptDIPAK VINAYAK SHIRBHATEОценок пока нет

- Curriculum Vitae-Professor 30-05-2018Документ8 страницCurriculum Vitae-Professor 30-05-2018Meer Mustafa AliОценок пока нет

- Resume DR Maneesh K SinghДокумент7 страницResume DR Maneesh K SinghKumar Keshaw ShahiОценок пока нет

- Dr. Rajesh Raut Nagpur 17.02 YrsДокумент6 страницDr. Rajesh Raut Nagpur 17.02 Yrsvenkiscribd444Оценок пока нет

- Curriculam Vitae Dr.M.sujatha 2Документ11 страницCurriculam Vitae Dr.M.sujatha 2SujathaОценок пока нет

- Se Handbook IV SemsДокумент126 страницSe Handbook IV SemsChinmay KulkarniОценок пока нет

- Leaflet - Ic-Quest 2015 - BdceДокумент2 страницыLeaflet - Ic-Quest 2015 - BdceSaurabh PednekarОценок пока нет

- FDP Final PDFДокумент3 страницыFDP Final PDFAlak MajumderОценок пока нет

- BiodataДокумент5 страницBiodataapi-26483995100% (2)

- DR - Srinivas BachuДокумент8 страницDR - Srinivas Bachulifowo6187Оценок пока нет

- S S.No Event Date Event Type Topic of The Event Resource Person InvolvedДокумент3 страницыS S.No Event Date Event Type Topic of The Event Resource Person InvolvedNaveenОценок пока нет

- IT Department NAAC 21-Nov-2014Документ19 страницIT Department NAAC 21-Nov-2014Dr. Gollapalli NareshОценок пока нет

- Profile - GKK - Sept 2011Документ6 страницProfile - GKK - Sept 2011Nilesh GhugeОценок пока нет

- ThirumalaДокумент11 страницThirumaladhruvshinde274Оценок пока нет

- Fundamentals and Innovations in Solar EnergyОт EverandFundamentals and Innovations in Solar EnergySri Niwas SinghОценок пока нет

- History PapermakingДокумент1 страницаHistory PapermakingHEMANTH BATTULAОценок пока нет

- VASAVI GP TRENDS, Nanakramguda: PRICE SHEET For 1st Floor To 7th FloorДокумент1 страницаVASAVI GP TRENDS, Nanakramguda: PRICE SHEET For 1st Floor To 7th FloorHEMANTH BATTULAОценок пока нет

- 1 Oled For StuydentsДокумент9 страниц1 Oled For StuydentsHEMANTH BATTULAОценок пока нет

- User Manual: Question? Contact PhilipsДокумент28 страницUser Manual: Question? Contact PhilipsHEMANTH BATTULAОценок пока нет

- Be I2 A Final Aicte Model Scheme Sallbai 2018 19Документ30 страницBe I2 A Final Aicte Model Scheme Sallbai 2018 19HEMANTH BATTULAОценок пока нет

- Blu Ray Disc Technology A Safe Investment For Next Generation IJERTV2IS70181Документ9 страницBlu Ray Disc Technology A Safe Investment For Next Generation IJERTV2IS70181HEMANTH BATTULAОценок пока нет

- 55pfl8007k 12 Dfu EngДокумент30 страниц55pfl8007k 12 Dfu EngHEMANTH BATTULAОценок пока нет

- Res MethДокумент5 страницRes MethAleli Joyce BucuОценок пока нет

- Proposal KP Chevron (Reservoir Eng)Документ9 страницProposal KP Chevron (Reservoir Eng)Asta Kinan PrayogaОценок пока нет

- UK GAAP and IFRS Standards Similarities and DifferencesДокумент4 страницыUK GAAP and IFRS Standards Similarities and DifferencescidoghaouaОценок пока нет

- Ankit ResumeДокумент3 страницыAnkit ResumeAnkit VyasОценок пока нет

- Veer Surendra Sai University of Technology, Burla: 2 SEMESTER (B.Tech/M.Tech)Документ2 страницыVeer Surendra Sai University of Technology, Burla: 2 SEMESTER (B.Tech/M.Tech)Mkvv MkvvОценок пока нет

- Rahul S: Mambalayil House, Mob: +919048488558 Kakkazhom P.O, Alappuzha 688 005 +918891204200 Kerala. E-MailДокумент2 страницыRahul S: Mambalayil House, Mob: +919048488558 Kakkazhom P.O, Alappuzha 688 005 +918891204200 Kerala. E-MailAbhilash P PaulОценок пока нет

- Corporate Law I-Doctrine of Constructive Notice: Priyamvada YДокумент2 страницыCorporate Law I-Doctrine of Constructive Notice: Priyamvada YHimanshuОценок пока нет

- Promo Mors Smitt enДокумент20 страницPromo Mors Smitt enYigit SarıkayaОценок пока нет

- Electrical Engineering (EE) - GATE Books - GATE 2016 PDFДокумент5 страницElectrical Engineering (EE) - GATE Books - GATE 2016 PDFravik_rkg6775% (4)

- Job Opportunities: National University of Modern Languages Sector H-9, IslamabadДокумент2 страницыJob Opportunities: National University of Modern Languages Sector H-9, IslamabadAasir NaQviОценок пока нет

- (GATE IES PSU) IES MASTER Environmental Engineering - 1 (Water Supply Engineering) Study Material For GATE, PSU, IES, GOVT Exams PDFДокумент194 страницы(GATE IES PSU) IES MASTER Environmental Engineering - 1 (Water Supply Engineering) Study Material For GATE, PSU, IES, GOVT Exams PDFRajeeb SinghОценок пока нет

- M.tech MST - CurriculumДокумент2 страницыM.tech MST - CurriculumMubarak Ali100% (2)

- Who Is Caterpillar?: - Cat Dealers - Cat Business UnitsДокумент17 страницWho Is Caterpillar?: - Cat Dealers - Cat Business UnitsDigitaladda IndiaОценок пока нет

- Form 3. Undergraduate Research Progress Report Form (MAY)Документ2 страницыForm 3. Undergraduate Research Progress Report Form (MAY)Claudine ValdezОценок пока нет

- 1051 - Pet 2016 Cut Off Phase 1Документ28 страниц1051 - Pet 2016 Cut Off Phase 1kamalnitrrОценок пока нет

- AI Based Smart Precision Agriculture Using Embedded IoT For Sustainable EnvironmentДокумент4 страницыAI Based Smart Precision Agriculture Using Embedded IoT For Sustainable EnvironmentThembelanienkosini ChikhambiОценок пока нет

- Teaching and Learning Digital AgeДокумент21 страницаTeaching and Learning Digital Agetummalapalli venkateswara raoОценок пока нет

- EAMCET 2016 Question Papers With SolutionsДокумент17 страницEAMCET 2016 Question Papers With SolutionsShaRukh MohammedОценок пока нет

- Joint Controller of Technical ExaminationsДокумент48 страницJoint Controller of Technical ExaminationsAjil SurendranОценок пока нет

- DefiningtheConceptsofTechnologyandTechnologyTransfer ALiteratureAnalysisДокумент12 страницDefiningtheConceptsofTechnologyandTechnologyTransfer ALiteratureAnalysisJoelОценок пока нет

- Oas Primenjene Informacione TehnologijeДокумент23 страницыOas Primenjene Informacione TehnologijeAleksandra RakicОценок пока нет

- Bits Goa: Stats & RankingДокумент6 страницBits Goa: Stats & RankingdemosvirisОценок пока нет

- 2019 SPISE Acceptance Letter-Leondre Joseph - GrenadaДокумент1 страница2019 SPISE Acceptance Letter-Leondre Joseph - GrenadaLeondreОценок пока нет

- Kurikulum 2010 Program Studi Teknik InformatikaДокумент3 страницыKurikulum 2010 Program Studi Teknik InformatikaAlif FinandhitaОценок пока нет

- Data Base For Further QueriesДокумент5 страницData Base For Further QueriesParveen MittalОценок пока нет

- Presentation - AIMT AdmissionДокумент24 страницыPresentation - AIMT Admissiondeeptiarora86Оценок пока нет

- Activity 4 - Using Database Software (DB) : Turn OverДокумент3 страницыActivity 4 - Using Database Software (DB) : Turn OverantokibaОценок пока нет