Академический Документы

Профессиональный Документы

Культура Документы

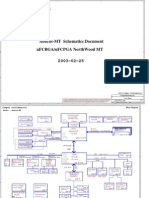

G31M04 Schematic Foxconn Precision Co. Inc.: Fab.A Data: 2007/6/15 Page Index

Загружено:

Leonard GržetićИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

G31M04 Schematic Foxconn Precision Co. Inc.: Fab.A Data: 2007/6/15 Page Index

Загружено:

Leonard GržetićАвторское право:

Доступные форматы

5

www.sp860.com

4 3

QQ:453100829

A-PDF Watermark DEMO: Purchase from www.A-PDF.com to remove the watermark

2 1

Foxconn Precision Co. Inc.

D G31M04 Schematic D

Fab.A

Data: 2007/6/15

Page Index

01. Index Page 25. ICH7 -1

02. Topology 26. ICH7 -2

03. Rest Map 27. ICH7 -3

04. Clock Distribution 28. REAR USB

C

05. Power Delivery Map 29. TPM C

06. Power Sequence 30. PCIE1X

07. BLANK 31. PCI Slot

08. CK505 ClockGen 32. LAN-RTL8101E/RTL8111C

09. Power / MISC Connectors 33. AUDIO 662

10. Voltage Regulator Down 11 34. AUDIO PORT

11. OUTPUT CAP 35. Super I/O ITE8718F/GX

12. 1D25V 1D5V FSB 36. Keyboard / Mouse / Fan

13. STR1D8V 3D3_DUAL 37. Serial / Parallel

14. LGA775 -1 38. FRONT USB

B

15. LGA775 -2 39. changlist B

16. Broadwater -GMCH -1

17. Broadwater -GMCH -2

18. Broadwater -GMCH -3

19. DDR2 Channel A Termination

20. DDR2 Channel A DIMM1, 2

21. DDR2 Channel B Termination

22. DDR2 Channel B DIMM1, 2

23. PCI Express x16 Gfx Slot

A 24. VGA Connector A

FOXCONN PCEG

Title

Index Page

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 1 of 41

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4 3

QQ:453100829 2 1

Cedar Mill, Presler ,

Conroe & Allendale

VRD 11 LGA775 Processor

3 Phase PWM

D

Socket T D

800/1066/1333 FSB

CK-505 Clock

PCI Express x 16 Channel A DDR2

PCI Express x16 Port DDR2 667/800

External Graphics

DIMM1

Card

GMCH DDR2 667/800 Channel B DDR2

VGA Connector

Broadwater DIMM1

C C

Back Panel

PCIe port

USB2.0 Port 7 LAN

4 Lanes

USB2.0 Port 8 Reltek

Direct Media Interface (DMI)

USB2.0 Port 9 Controller Link

USB2.0 Port 10

SPI Flash

PCI Slot 1X2

ICH7

B

Header B

USB2.0 Port 1

Serial ATA ⒑

LPC I/F

USB2.0 Port 2 SATA Connector 1

AHCI, RAID0,1,5,10

USB2.0 Port 3 SATA Connector 2

USB2.0 Port 4 SPI Flash SATA Connector 3

(BIOS) SATA Connector 4

HDA Codec

TPM

TPM(Optional) Realtek ALC662

LPC I/F

Super I/O

IT8718/GX

A A

Floppy

Serial & Parallel

Drive Connector

FOXCONN PCEG

Title

TOPOLOGY

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 2 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4 3

QQ:453100829 2 1

CPU

(Cedar Mill/Presler/Conroe/Allendale)

CPU_PWRGD

LGA775 processor

CPURST#

D D

ATX

Power

Vtt_PwrGd CK505

Translation PWRGD_3V

PWRGD_PS PWROK CPURST#

Circuitry PCI Express x16

PS_ON#

GMCH

Broadwater

C

RSTIN# C

ICH7

ICH_PWRGD

CK_PWRGD

SLP_M#

PCIRST#

PLTRST#

Front Panel PWROK ACZ_RST#

RST# Audio

FR_RST SYS_RESET# LAN_RSTSYNC

B B

SW_ON PWRBTN#

RSMRST#

RCIN#

SLP_S3#

RST#

TPM

RST#

RST#

Power on/off KBRST PCI Slot 1

circuit RSMRST#

Super IO

RST# PCIe Slot

SLP_S3# PCIe LAN

PSOUT

PSIN RST#

A IDE Controller A

PSOUT#

RSMRST circuit FOXCONN PCEG

Title

Reset Map

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 3 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

14.318MHz www.sp860.com4 3

QQ:453100829 2 1

CPU

D

CPU 200/266/333 MHz Diff Pair D

MCH 200/266/333 MHz Diff Pair

PCI Express 100 MHz Diff Pair PCI Express x16 Gfx Channel A DDR2

DIMM1

GMCH

DOT 96 MHz Diff Pair Broadwater

Channel B DDR2

DIMM1

PCI Express/DMI 100 MHz Diff Pair

C C

CK-505

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

SPI Clock SPI

ICH7

Azalia Bit Clock

B

PCI 33 MHz PCI Slot 1 B

TPM 33 MHz TPM

32.768KHz

HD Audio

SIO 33 MHz Super I/O

SATA 100 MHz Diff Pair

PCI Express 100 Mhz Diff Pair

A A

FOXCONN PCEG

Title

Clock Distribution

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 4 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4 3

QQ:453100829 2

3.3V Super I/O

1

ATX P/S 3.3V

Icc(Max)=50mA

Proceessor

Vccp (CPU Vcore)

5V 5VSB VRD 11 Voltage=1.15~1.5V 3.3SBV

12V Switching Icc(Max)=50mA(S0) 5V

Icc(Max)=125A

Three Phase 3-Phases Swithing

5VDUAL 3.3SBV

D

DDR2 Channel A Icc(Max)= Icc(Max)=38mA(S3)

D

1.2V FSB 5VSB

10A Vtt=5.3A

Vdd (Core)=1.8V

Ivdd(Max)=TBD(per channel)

5VDUAL

USB2.0 10 Ports Icc(Max)=

+5V DUAL=5A(S0, S1)

Vtt (Core)

0.9V Single Phase Switch Broadwater GMCH +5V DUAL=20mA(S3) 4.345A(S0,S1)

22mA(S3)

Ivterm(Max)=200mA 5V to 1.8V

(per channel) Ivdd(Max)=TBD FSB_Vtt

Linear 1.8V PS2

LDO 1.2V FSB Vtt

1.8V to 0.9V to 1.2V Icc(Max)=1.3A +5V DUAL=345mA(S0, S1)

Ivterm(Max)=1.2A 6A +5V DUAL=2mA(S3)

DDR2 Channel B

1.8V VCCSM FWH

Vdd (Core)=1.8V 1.8V VCC_SMCLK

Ivdd(Max)=TBD(per channel) 3.3V=107mA(S0, S1)

GMCH 1.25 V Vcore (Core Logic) PCI Express X16

Vtt (Core) 3.3V 21.34A 1.25V

0.9V Switching Icc(Max)=18.8A(Integrated)

slot (1)

Ivterm(Max)=200mA 12V

(per channel) *1.25V (DMI&PCIe) +12V=5.5A

VCCA_EXP 2.5A

C

3.3VSB C

1.25V Icc(Max)=0.375A(wake)

VCC_CL 3.8A

Icc(Max)=0.02A(no wake)

+3.3V=3A

3.3V VCCA_DAC 70mA

3.3V VCC3_3 15.8mA

PCI Express X1

Per slot (1)

+12V=0.5A

HDA Codec

3.3VSB

Vcc LDO Icc(Max)=0.375A(wake)

5V 12V ICH7 Icc(Max)=0.02A(no wake)

Icc(Max)=200mA to 5V

1.25V VCCDMI 40mA

Vcc +3.3V=3A

3.3V Linear 1.25V 1.2V VCC_CPU_IO 14mA

Icc(Max)=40mA to 1.05V

V_1P05V_ICH 1.05V (Core) VCC1_05

2A 1.17A PCI Per Slot (X2)

1.5V (USB &SATA) VCC1_5A -12V

B

1.12A Icc(Max)=0.1A -12V B

Linear 1.8V

to 1.5V 1.5V (PCIe)VCC1_5B

V_1P5V_ICH 0.77A 5V

2.2A 1.5V VCCGLAN1_5 Icc(Max)=5A

5V

74mA

3.3V

RTC Icc(Max)=7.6A

5VSB Battery RTC=5uA

12V

3.3V VccCL3_3 12mA Icc(Max)=0.5A

5V_STBY to 3.3SB 3.3V VccSUS3_3 141mA

1.5A 3.3V VccLAN (10/100) 12mA 3.3VSB

3.3V VccSUSHDA 4mA Icc(Max)=0.375A(wake)

3.3V VCC3_3 310mA Icc(Max)=0.02A(no wake)

3.3V

3.3V VccGLAN3_3 1mA

3.3V VccHDA 4mA

Nineveh GbE Lan

3.3V STBY

A IO LED 15.5nA A

1.8V ANALOG 418.2mA BJT

CK505

1.0V Internal 1.8

to 1.0 VR core Vdd (Core) FOXCONN PCEG

277.2mA 3.3V

Title

Ivdd(Max)=250mA

Power Delivery Map

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 5 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com

4 3

QQ:453100829

2 1

S0->S5

+12V_SYS +12V_SYS

S5->S0

D D

+5V_DUAL +5V_SYS +5V_SYS +5V_DUAL

+3D3V_DUAL +3D3V_SYS +3D3V_SYS +3D3V_DUAL

+1D8V_STR +1D8V_STR

VTT_DDR

VTT_DDR

VTT_VR VTT_VR

Vcc Vcc

1ms to 10ms

Vcc_PWRGD

Vcc_PWRGD

VRM_OUTEN

VRM_OUTEN

VIDPWRGD VIDPWRGD PS_ONJ

C

PS_ONJ C

S0->S3 S3->S0

+12V_SYS +12V_SYS

+5V_SYS +5V_DUAL +5V_DUAL +5V_SYS

+3D3V_SYS +3D3V_DUAL +3D3V_DUAL +3D3V_SYS

B B

+1D8V_STR +1D8V_STR +1D8V_STR +1D8V_STR

VTT_DDR

VTT_DDR

VTT_VR VTT_VR

Vcc Vcc

1ms to 10ms

Vcc_PWRGD

Vcc_PWRGD

VRM_OUTEN

VRM_OUTEN

VIDPWRGD PS_ONJ VIDPWRGD

PS_ONJ

A A

FOXCONN PCEG

Title

Power Sequence

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 6 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com4 3

QQ:453100829 2 1

D D

C C

B B

A FOXCONN PCEG A

Title

BLANK

Size Document Number Rev

A G31M04 A

Date: Wednesday, September 12, 2007 Sheet 7 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 3D3V_SYS

4 3

QQ:453100829 3D3V_SYS

FB17

2

0 Dummy

1

+/-5% r0805h6

FB18 0 Dummy 3D3V_CLK CP7 X_COPPER 3D3V_CLK_SATA_25M

4.7uFC105

10nFC108

10nFC111

6.3V, X5R, +/-10%

25V, X7R, +/-10%

16V, Y5V, +80%/-20%

+/-5% r0805h6

CP8 X_COPPER 3D3V_CLK

1

25V, X7R, +/-10%

25V, X7R, +/-10%

25V, X7R, +/-10%

25V, X7R, +/-10%

25V, X7R, +/-10%

4.7uFC101

10nFC128

10nFC107

10nFC140

10nFC134

10nFC112

6.3V, X5R, +/-10%

Dummy

* * *

2

D

* * * * * * D

3D3V_SYS

2

Change to 0Ohm RES or not

FB19 0 Dummy

+/-5% r0805h6

CP11 X_COPPER 3D3V_CLK_REF_A

10nFC136

10nFC119

25V, X7R, +/-10%

16V, Y5V, +80%/-20%

C138

1

4.7uF

3D3V_CLK_48M * 6.3V, X5R, +/-10% * *

25V, X7R, +/-10%

10nFC121

2

1

3D3V_CLK * Dummy

TBD

2

3D3V_CLK

R83

4.7K

* +/-5%

r0402h4

Reserved U8

1 64

**RLATCH 25Mhz_0F_2x

2 63

3D3V_CLK 3 GND GND 62 3D3V_CLK_SATA_25M

*

R89 4.7K +/-5% r0402h4 24M_1394 VDD VDD25Mhz_STB 3D3V_CLK_SATA_25M

4 61

**GSEL/24.576Mhz VDDSATA_STB

31

35

CK_33M_PCI2

CK_33M_SIO

CK_33M_PCI2

CK_33M_SIO

*1 2 33

RN12 3D3V_CLK 5

6 VDDPCI SATACLKT_LR

60

59

SATA_100M_P_ICH

SATA_100M_N_ICH

CK_SATA_100M_P_ICH

CK_SATA_100M_N_ICH

26

26

*

3 4 +/-5% R91 4.7K Dummy GND SATACLKC_LR

7 58

*

CK_33M_ICH 5 6 8p4r0603h7 +/-5% r0402h4 **DOC1 GND R93 33 +/-5% r0402h4

27 CK_33M_ICH 8 57 CK_14M_ICH 25

7 8 PCICLK0 REF0_2x/FSLC ICS_FSBSEL2

9 56 ?

*

CK_33M_TPM R94 33 +/-5% @TF ICS_FSBSEL1 10 *Freerun/PCICLK1_2x GND 55 X2

29 CK_33M_TPM FSLB/PCICLK2_2x X1

*1 RN16

9,14,25 ICH_SYS_RSTJ 11

12

SELRSET/RESET#/PCICLK32 X2

54

53 3D3V_CLK_REF_A *

**

C CK_33M_PCI1 2 33 R96 4.7K Dummy 13 PCICLK4 VDDREF_STB 52 R97 0 +/-5% r0402h4 Reserved C102 XTAL 14.318MHz C103 C

ICS9LPRS511

31 CK_33M_PCI1 3 4 +/-5% **DOC0 SDATA SMB_DATA_MAIN 20,22,29,36

CK_48M_ICH +/-5% r0402h4 3D3V_CLK_48M R99 0 +/-5% r0402h4 Reserved 27pF 27pF

25 CK_48M_ICH

35 CK_48M_SIO

CK_48M_SIO 5

7

6 8p4r0603h7

8

ICS_FSBSEL0

14

15

VDD48

FSLA/USB_48MHz

SCLK

GND

51

50

SMB_CLK_MAIN 20,22,29,36 * +/-5% * +/-5%

16 49 200M_P_CPU c0402h6 c0402h6

CK_200M_P_CPU 14

*

R1014.7K +/-5% r0402h4 *SEL24_48#/24_48Mhz CPUT_LR0 200M_N_CPU

17 48

GND CPUC_LR0 CK_200M_N_CPU 14

VRMPWRGD 18 47 3D3V_CLK

96M_P_GMCH Vtt_PwrGd/WOL_STOP# VDDCPU 200M_P_GMCH

16 CK_96M_P_GMCH 19 46 CK_200M_P_GMCH 16

96M_N_GMCH DOT96T_LR/PCIeT_LR0 CPUT_LR1 200M_N_GMCH

20 45

16 CK_96M_N_GMCH DOT96C_LR/PCIeC_LR0 CPUC_LR1 CK_200M_N_GMCH 16

21 44 3D3V_CLK

GND VDDI/O

32 CK_PE_100M_P_LAN 22 43

PCIeT_LR1 GNDA 3D3V_CLK_REF_A

32 CK_PE_100M_N_LAN 23 42

24 PCIeC_LR1 VDDA_STB 41

30 CK_PE_100M_P_1PORT_2 PCIeT_LR2 PCIeT_LR8

25 40

30 CK_PE_100M_N_1PORT_2

26 PCIeC_LR2 PCIeC_LR8 39 PE_100M_P_GMCH

GND PCIeT_LR7 CK_PE_100M_P_GMCH 16

PE_100M_P_16PORT 27 38 PE_100M_N_GMCH

23 CK_PE_100M_P_16PORT PCIeT_LR3 PCIeC_LR7 CK_PE_100M_N_GMCH 16

PE_100M_N_16PORT 28 37

23 CK_PE_100M_N_16PORT PCIeC_LR3 GND

29 36

PCIeT_LR4 PCIeT_LR6

30 35

PCIeC_LR4 PCIeC_LR6 PE_100M_P_ICH

31 34 CK_PE_100M_P_ICH 25

3D3V_CLK 32 GND PCIeT_LR5 33 PE_100M_N_ICH

VDDPCIEX PCIeC_LR5 CK_PE_100M_N_ICH 25

ICS9LPRS511EGLF-T

CK_33M_PCI1

3D3V_CLK

CK_33M_PCI2

*R103

8.2K

50V, NPO, +/-5%

50V, NPO, +/-5%

+/-5%

B

C120 C106 r0402h4 B

10pF 10pF VRMPWRGD

* * VRMPWRGD 10,14,25

Dummy Dummy

FSB SELECT

Host Clock

FSBSEL2 FSBSEL1 FSBSEL0 Frequency

1 0 0 333MHz

0 0 0 266MHz

0 1 0 200MHz

* * *

ICS_FSBSEL0 R1002.2K +/-5% r0402h4 FSBSEL0

0 0 1 133MHz

CK_48M_SIO

ICS_FSBSEL1 R90 +/-5% FSBSEL1

CK_48M_ICH 2.2K r0402h4

CK_33M_SIO ICS_FSBSEL2 R95 2.2K +/-5% r0402h4 FSBSEL2

Reserved

CK_33M_ICH

CK_14M_ICH

CK_33M_TPM

50V, NPO, +/-5%

50V, NPO, +/-5%

FSB_VTT

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

C126 C124 C110 C104 C116 C115

10pF 10pF 10pF 10pF 10pF 10pF

* * * * * *

A Dummy Dummy Dummy Dummy Dummy Dummy A

RN11

*1 2 FSBSEL0

FSBSEL0 14

3 4 FSBSEL1

5 6 FSBSEL1 14

FSBSEL2

7 8 FSBSEL2 14

470

+/-5%

8p4r0603h7 FOXCONN PCEG

Title

CK505 Clock Gen

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 8 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4 3

QQ:453100829 3D3V_SYS

2

3D3V_SYS 5V_SYS

1

5V_SB

C454 C510 C462 C461

5V_SB -12V_SYS 3D3V_SYS 3D3V_SYS 12V_SYS 5V_SB * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

5V_SYS

5V_SYS

*R350

4.7K 13

+3.3V3 +3.3V1

PWR1

1

D +/-5% 14 2 D

r0402h4 -12V +3.3V2 12V_SYS

15 3

GND4 GND1 -12V_SYS 12V_SYS

35 PS_ONJ 16 4

PSON +5V1

17 5

C463 GND5 GND2

18 6

GND6 +5V2

1

Del R32, R33, Q3

* 0.1uF

16V, Y5V, +80%/-20%

19

20

GND7 GND3

RSVD PWR0K

7

8 PWRG_ATX

PWRG_ATX 13,35

* C464 * C496 * C425

21 9 0.1uF 0.1uF 0.1uF

2

+5V3 +5V_AUX C465

22 10

+5V4 +12V_1

23

24

+5V5

GND8

+12V_2

+3.3V4

11

12

* 0.1uF

16V, Y5V, +80%/-20% 25V, X7R, +/-10% 25V, X7R, +/-10% 25V, X7R, +/-10%

HM1512E-EP1 Dummy

3D3V_SYS 3D3V_SYS

C141 C251

* 10nF

25V, X7R, +/-10% * 10nF

25V, X7R, +/-10%

Dummy Dummy

5V_SYS 3D3V_SB 5V_SYS

VCC_DUAL

R348 R361

C 330 * 8.2K

*R352 C

+-5% +/-5% R349 4.7K

r0402h4 330 +/-5%

FP1 +-5% r0402h4 3D3V_SYS 1D25V_MCH

1 2

HDD_LEDJ 3 4 C329 C208

*

26 HDD_LEDJ

8,14,25 ICH_SYS_RSTJ

5

7

6

8

R371

33 +/-5%

PBTNJ_SIO 35 * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

9 X C460 C497 C501

1

Header_2X5_K10 * 220pF

Dummy * 220pF

Dummy * 10nF

C459 C483 25V, X7R, +/-10%

2

* 220pF 220pF

50V, NPO, +/-5% 50V, NPO, +/-5% *

Dummy Dummy TBD 3D3V_SYS 5V_SYS 5V_SYS

C284 C285

* R347

10K * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

+/-5%

r0402h4

C

Reserved

Front Panel Switch/LED

*

B R346 1K PWR_LED 25

+/-1% r0402h4

HD_LED+ 1 2 Power MMBT3904_NL Reserved

E

HD_LED- 3 4 Power LED(Green) Change to 5% or not

Q37

B

GND 5 6 Power button B

Reset button 7 8 Power

NC 9 10 Key

SPEAKER HEADER

SPEAKER

1

5V_SYS 1

3

Confirm must use or not

3

4

5V_SYS RN48 4

*1 2

Header_1X4_K2

Reserved

3 4 BUZ

5 6

+

7 8

*R369

4.7K 100 Ohm BUZZER

+/-5% +/-5% -

r0402h4 8p4r0603h7

Buzzer

D43

C

1 Dummy

*

25 SPKR

3 R364 2.2K B Q44 C469

MMBT3904_NL

35 SIO_BEEP 2 +/-5% r0402h4

* 0.1uF

16V, Y5V, +80%/-20%

E

A A

BAT54C

33 BEEP_PC

FOXCONN PCEG

Title

Power/MISC Connectors

Size Document Number Rev

Custom G31M04 A

Date: Wednesday, September 12, 2007 Sheet 9 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4

C245

R167 r0402h4

3

QQ:453100829 2 1

*

Dummy 1K

*

+/-1%

Dummy

1nF

50V, X7R, +/-10% R160

C246 2.2K

1

4.7nF * +/-1%

*

50V, X7R, +/-10% RT1

D T D

2

Del R60 10K

R159 +/-1%

* 0 Dummy

+/-5%

R161

1

120pF

*

*

C247 VIN

1

R162

2

15K50V, NPO, +/-5%

+/-1% 2.43K

14

15

16

r0402h4 U13 +/-1% Q6 C87

1

2 Dummy AOD452

* 4.7uF

FB

IDROOP

VDIFF

13 25V, Y5V, +80%/-20% PHASE1

COMP R173 2.2 R176

2

*

VCCP R158 100 31 C2631 225V, X7R, +/-10% G 6.2k Ohm

*

BOOT1

1

14 VCC_SENSE

+/-1% r0402h4

Dummy C244 18 32

+/-5%

r0805h6

0.22uF R79

2.2 *R80

10K

+/-1%

r0402h4 * 25V, X7R, +/-10%

C274

S

VSEN UGATE1 L17

1

* 10nF +/-5% +/-5% 0.1uF

2

25V, X7R, +/-10% 33 r0805h6 r0402h4 2 1

PHASE1

*

14 VSS_SENSE Dummy 17

D

2

RGND R72

*

R157 100 Dummy 30 Q12 Q7 2.2 Choke 400nH

+/-1% r0402h4 LGATE1 +/-5%

5V_SYS R177 2.2 C262 10 12V_VRM G G r0805h6

1 VCC

+/-5% r0805h6

* 0.1uF

ISEN1-

34 R179

PHASE1 AOD472 AOD472

1

* C97

S

R169 R166

25V, X7R, +/-10% 35 VCCP 1nF

2

*

ISEN1+

1

2.2

C 5V_SYS 12

* C273 50V, X7R, +/-10% C

2

OFS 0.1uF +/-5%

R183 100

r0805h6 VIN

2

* *

68K R168 +/-1% 25V, X7R, +/-10% C250

45 29

+/-1% FS PVCC1_2

30K

+/-1% C2541

Dareen 1/27/07

2 10nF 11

* 1uF

16V, X7R, +/-10% Q25

D

Dummy 120K REF R170 2.2 AOD452 C137

1

+/-1%25V, X7R, +/-10% 27 C2401 225V, X7R, +/-10%

* 4.7uF PHASE2

*

BOOT2 +/-5% 0.22uF R117 25V, Y5V, +80%/-20% R165 VCCP

26 r0805h6 2.2 G 6.2k Ohm

2

*

UGATE2

1

R174

+/-1%

100KOhm

r0402h4

9

SS

25

+/-5%

r0805h6 *R119

10K

+/-1%

r0402h4 * 25V, X7R, +/-10%

C243

S

PHASE2 L24

+/-5% 0.1uF

2

r0402h4 2 1

*

5V_SYS 8 28

D

OVPSEL LGATE2 R149

Del R196 12V_VRM Q28 Q29 2.2 Choke 400nH

+/-5%

46 G G r0805h6

35 PVID7 VID7 R164

35 PVID6 47 20 PHASE2 R193 AOD472 AOD472

VID6 ISEN2-

1

35 PVID5 48 19 VCCP 2.2

* C199

S

VID5 ISEN2+

1

35

35

PVID4

PVID3

1

2

VID4 * C238

0.1uF

+/-5% 1nF

50V, X7R, +/-10%

2

VID3 100 r0805h6 VIN

35 PVID2 3

2

VID2 +/-1% 25V, X7R, +/-10% C286

35 PVID1 4 42

VID1 PVCC3

5

* 1uF Q5

D

35 PVID0 VID0 R186 2.2 16V, X7R, +/-10% AOD452 C81

1

B 40 C2821 225V, X7R, +/-10%

* 4.7uF PHASE3 B

*

VID_SELECT:VR10.1<0.6V; 0.6<VR11<3.0V BOOT3 +/-5% 0.22uF R77 25V, Y5V, +80%/-20% R192

14,25 VID_SELECT 6 39 r0805h6 2.2 G 6.2k Ohm

2

VRSEL UGATE3

1

PGOOD is Open-Drain 38

+/-5%

r0805h6 * R81

10K

+/-1%

r0402h4 * 25V, X7R, +/-10%

C283

S

PHASE3 L16

37 +/-5% 0.1uF

2

8,14,25 VRMPWRGD PGOOD r0402h4 2 1

*

D

D

41 R71

LGATE3 Q13 Q8 2.2 Choke 400nH

+/-5%

R182

43 PHASE3 G G r0805h6

ISEN3- AOD472 AOD472

44 VCCP

ISEN3+

1

1

11 VRM_EN 36

* C290

* C95

S

EN 0.1uF 1nF

EN voltage must 100 50V, X7R, +/-10%

2

2

higher than 0.850V +/-1% 25V, X7R, +/-10%

23 5V_SYS

EN_PH4

7 24

DRSEL PWM4

22

ISEN4-

49

GND

A 21 A

ISEN4+

ISL6312CRZ

FOXCONN PCEG

Title

Voltage Regulator Down 11

Size Document Number Rev

Custom G31M04 A

Date: Thursday, September 27, 2007 Sheet 10 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4

VCCP

3

QQ:453100829 2 1

EC20

* 1800uF

6.3V, +/-20%

Dummy

12V_VRM

D D

EC21

4

* 1800uF

6.3V, +/-20%

PWR2

Dummy Input LC circuit

3

EC30 EC45 EC44 EC42 HM3502E-P1 VIN

L14

* 680uF * 680uF * 680uF * 680uF 1.2uH@100KHz Dareen 1/27/07

*

4V,+/-20% 4V,+/-20% 4V,+/-20% 4V,+/-20%

ce35d80h90 ce35d80h90 ce35d80h90 ce35d80h90 C89 EC18 EC15 EC13 EC24

1

Reserved Reserved Reserved Reserved

* 0.1uF

25V, Y5V, +80%/-20%

* 1000uF

+/-20%

* 1000uF

+/-20%

* 1000uF

+/-20%

* 1000uF

+/-20%

2

Dummy

EC34 EC33 EC31 EC32

* 680uF

4V,+/-20%

* 680uF

4V,+/-20%

* 680uF

4V,+/-20%

* 680uF

4V,+/-20%

ce35d80h90 ce35d80h90 ce35d80h90 ce35d80h90

Reserved

C C

VTT_OUT_RIGHT

TC2 TC1 *R256

1K

* 100uF

2V,+30/-20%

* 100uF

2V,+30/-20%

VTT_OUT_RIGHT VCC_DUAL +/-5%

r0402h4

ctxh15 ctxh15 VTT_PWRGD 14

Dummy Dummy

*R226

D

20K

*R253

4.12K

+/-1% Q33

+/-1% G

2N7002-7-F

S

R248

*

*

R235 100KOhm B Q32 0 CP17

C197 C203 C211 C217 C196 C195 +/-1% r0402h4 MMBT3904_NL +/-5% X_COPPER

* 10uF

* 10uF

* 10uF

* 10uF

* 10uF

* 10uF Dummy Dummy

E

6.3V, X5R, +/-10% 6.3V, X5R, +/-10% 6.3V, X5R, +/-10% 6.3V, X5R, +/-10% 6.3V, X5R, +/-10% 6.3V, X5R, +/-10%

C316

*

B 2.2uF VRM_EN 10 B

6.3V, Y5V, +80%/-20%

* C280

2.2uF

C201 C228 C223 C202 C226 C221 6.3V, Y5V, +80%/-20%

* 10uF

* 10uF

6.3V, X5R, +/-10%6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10%

Dummy Reserved Reserved Dummy Dummy Dummy

C215 C209 C227 C222 C216 C210

* 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10% * 10uF

6.3V, X5R, +/-10%

Dummy Dummy Dummy Dummy Dummy Dummy

A A

FOXCONN PCEG

Title

OUTPUT CAP

Size Document Number Rev

Custom G31M04 A

Date: Wednesday, September 12, 2007 Sheet 11 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com D26

4

C296

12V_SYS

3

QQ:453100829 2 1

A C 125V_PHASE

*

*

L25

*

12V_SYS R198 10 1N4148W 1uH@1KHz

+/-5% 1uF

16V, X7R, +/-10%

close to Q61 Drain

C293 1uF 16V, X7R, +/-10%

*

R224 C267 EC68 C271

1

14.3K

* 0.1uF

* 330uF

* 4.7uF

D

D D

5

+/-1% U14 25V, X7R, +/-10% +/-20% 25V, Y5V, +80%/-20%

1 Q30

VCC

2

Rocset BOOT

7 2 R184 0 +/-5% G

COMP/OCSET UGATE AOD452 1D25V_MCH

L26 Need to change to RUBYCON 16MBZ470MEFC8X11.5

*

S

6 8 125V_PHASE 1D25V_MCH

FB PHASE

GND

4

LGATE R190 2.5uH@100KHz

D

*R200 APW7120KE-TRL 2.2

1

200 Q31 +/-5% C294 EC50 EC49 C292

* * *

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

+/-1% 1000uF 1000uF 10uF

* 0.1uF

2.2uF C224

2.2uF C231

2.2uF C239

1uF C252

1uF C234

1uF C198

10V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

r0402h4 R188 0 +/-5% G C289 6.3V, +/-20%

16V, Y5V, +80%/-20% 6.3V, +/-20%

1

AOD472 2.2nF

* 50V, X7R, +/-10% * * * * * *

S

Near MOSFET

2

VOUT= 0.8V(1+R638 / R658)

R638,R658 must less than 1k

Pull FB trace out after Cout

*

R223 115 Ohm +/-1% r0402h4

R203 C308

*

220 18nF

+/-1% 50V, Y5V, +80%/-20%

Dummy Dummy

1D25V FOR CHIP

C C

12V_SYS

2D5V_REF 12V_SYS

1D8V_STR

3D3V_SB 2D5V_REF

50 mils

1

R112 C158

* U10D

4

*R111

33 Ohm

910

+/-1%

0.1uF

12

2

+

+/-1% 25V, X7R, +/-10% 14

D

U10A 1D5V_CORE 13

4

-

Q36

@1.5V 1D5V_REF 3 LM324DR2G

2

11

+

Q24

C146 1 2

1 G

AP15N03H

1A

1

-

1uF R400 TL431NSL

* 50 mils

S

10V, Y5V, +80%/-20% 100 Dummy LM324DR2G R303

11

Dummy +/-1%

*R113 C153 1K

2

+/-1% *

Reserved 1.5K 0.1uF +/-1%

16V, Y5V, +80%/-20%

Can change to 0402 or not

Dummy EC57 C411

* 1000uF

6.3V, +/-20% * 0.1uF

16V, Y5V, +80%/-20%

B B

Check to dummy or not

1D5V_SYS

2D5V_REF

1D8V_STR

12V_SYS

50 mils

2D5V_REF R121

1D8V_STR * 1K

+/-1%

50 mils r0402h4

D

3D3V_SB 12V_SYS

*R116 FSB_VTT 1D5V_CORE U10B 1D05V_SYS

4

10K Q34

+/-1% @1.05V 1.8V 5

+

R110 r0402h4

* 7 G

1A

D

1K U10C 6 AP15N03H

C

4

-

+/-5% Q27 D24 50 mils

S

1D5V_CORE Reserved VREF1D2 @1.2V 1.8V 10 LM324DR2G R127

11

+

r0402h4 8 G R124 C163 1K

9 AP15N03H 1N4148W * 750

* 0.1uF +/-1%

C

-

*R114 +/-1% 16V, Y5V, +80%/-20%

S

470 B Q26 LM324DR2G R125 Can change to 0402 or not

Dummy EC55 C166

11

+/-5% MMBT3904_NL

*R118 C160 1K

* 680uF

* C362

* 0.1uF

+/-1% *

Reserved 10K 1uF +/-1% 4V,+/-20% 10uF 16V, Y5V, +80%/-20%

6.3A 50 mils

C

10V, Y5V, +80%/-20% ce35d80h90

B Q23 r0402h4 Can change to 0402 or not

Dummy EC37 C154 C164 6.3V, Y5V, +80%/-20%

C147

MMBT3904_NL

Reserved

* 1000uF

6.3V, +/-20% * 10uF

* 0.1uF

6.3V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy Dummy

Need to Check Change to Dummy

E

1uF

A * 10V, Y5V, +80%/-20% Dummy A

Reserved

1D05V_SYS

TBD

FSB_VTT FSB_VTT

C156 C155 FOXCONN PCEG

0.1uF 0.1uF

* 16V, Y5V, +80%/-20% * 16V, Y5V, +80%/-20% Title

1D25V 1D5V FSB

FSB_VTT Size

C

Document Number

G31M04

Rev

A

Date: Wednesday, September 12, 2007 Sheet 12 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com 4 3

QQ:453100829 2 1

DDR_VTT

D D

VCC_DUAL

D41 D40

12V_SYS 1 1

3 3 C466 18V_PHASE

*

1.8V Voltage

*

5V_SB 2 2 1uF L38

16V, X7R, +/-10% 1uH@1KHz

*

R328 10 1D8V_STR 3D3V_SYS

BAT54C BAT54C

1.8V Power requires

+/-5%

17A maximum current

close to Q61 Drain

5V_SB C456 EC60

*

R339

1uF

16V, X7R, +/-10% EC69

* 1000uF

6.3V, +/-20% U22

1

*R360 Open 14.3K

* C482 * 470uF

* C487 1 8 VTT_DDR

D

5

4.7K +/-1% U20 0.1uF +/-20% Dummy VIN VCNTL 7

10uF VCNTL

+/-5% L 1 Q45 c0805h14 R362 6

*

VCC

2

L r0402h4 Rocset BOOT 25V, X7R, +/-10% 10V, Y5V, +80%/-20% 100KOhm VCNTL 5

Open R368 0 +/-5% +/-1% VCNTL

7 2 G

H COMP/OCSET UGATE AOD452 1D8V_STR r0402h4 4

C

L37 VOUT

16V, Y5V, +80%/-20%

Open

*

S

L B Q43 6 8 18V_PHASE 3 2

1

MMBT3904_NL FB PHASE C499 C477 REFEN GND

* *

GND

L 4 10uF 10uF RT9173 C467 EC59 C458

E

1

LGATE 2.5uH@100KHz

R359 c0805h14 c0805h14

*R358 C468

* 0.1uF * 1000uF

* 4.7uF

C

2

First H R335 Need to Apply 2.2 10V, Y5V, +80%/-20% 10V, Y5V, +80%/-20% 100KOhm 0.1uF 6.3V, +/-20% Dummy

* APW7120KE-TRL

*

3

*

R354 1K B Q42 91 Ohm Q38 +/-5% C439 EC61 EC62 +/-1% 16V, Y5V, +80%/-20%

2

25 SLP_S4J

S5

+/-5%

L

r0402h4 MMBT3904_NL +/-1%

R327 0 +/-5% G C486 * 0.1uF * 1000uF

6.3V, +/-20%

16V, Y5V, +80%/-20%

* 1000uF

6.3V, +/-20%

r0402h4

E

1

AOD472 2.2nF

S0 H Don't in CIS * 50V, X7R, +/-10%

S

Near MOSFET Need to Check Change to Dummy

2

S3 H

VOUT= 0.8V(1+R638 / R658)

R638,R658 must less than 1k

Pull FB trace out after Cout

*

R337 115 Ohm

C +/-1% C

*

R336 220 +/-1% C453 18nF

*

Dummy Dummy 50V, Y5V, +80%/-20%

R334 R333

442 Ohm 1.02KOhm

+/-1% +/-1%

Reserved r0402h4

35 SIO_GP10_DDR_VOL_3

35 SIO_GP41_DDR_VOL_5

1D8V_STR

VCC_DUAL

U19

B

3D3V_SB B

3

Vin

2 Max. output current = 3A

Vout

1

ADJ

AZ1084D-ADJTRE1 *R340

301

12V_SYS 5V_SB

+/-1%

3D3VADJ 5V_SB * R353

EC63 C478 EC58 1K

* 1000uF

6.3V, +/-20% * 1uF

10V, Y5V, +80%/-20% R341

* 1000uF

6.3V, +/-20%

915 series failure issue L

+/-5%

* 499 H PWOK+ r0402h4

* R357

S

+/-1%

D

PWOK+ G APM2301AAC-TRL 1K

Q41 +/-5%

A

5V_SYS

Q39 PWOKJ r0402h4

G

D39 2N7002-7-F

D

B120-13-F

S

G

D

C

Q40

Q46

AP15N03H G PWRG_ATX

D

PWRG_ATX 9,35

2N7002-7-F

Vout=Vref(1+R2/R1)+IadjR2 VCC_DUAL

S

R1 is Up Resistor.

Iadj=50uA

Vref=1.25V

A A

3D3V_DUAL 5V_DUAL

FOXCONN PCEG

Title

STR 1D8V 3D3V_DUAL 5V_DUAL

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 13 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

5

www.sp860.com HDJ[63..0]

4

HDJ[63..0] 16

16 HAJ[35..3]

HAJ[35..3]

HAJ3

3

U11A

QQ:453100829 2

3 OF 7

1

L5 D2

HAJ4 P6 A03# ADS# C2 HADSJ 16 U11C

2 OF 7 HAJ5 A04# BNR# HBNRJ 16 TESTHI_0

M5 D4 P2 F26

U11B A05# HIT# HITJ 16 26 SMIJ SMI# TESTHI00

HAJ6 L4 H4 TP_RSPJ K3 W3 TESTHI_1

A06# RSP# TP1 26 A20MJ A20M# TESTHI01

HAJ7 M4 G8 R3 P1 TESTHI_11

A07# BPRI# HBPRIJ 16 26 FERRJ FERR#/PBE# TESTHI11

HDJ0 B4 G16 HDJ32 HAJ8 R4 B2 K1 W2 TESTHI_12

D00# D32# A08# DBSY# HDBSYJ 16 26 INTR LINT0 TESTHI12

HDJ1 C5 E15 HDJ33 HAJ9 T5 C1 L1 F25

D01# D33# A09# DRDY# HDRDYJ 16 26 NMI LINT1 TESTHI02

HDJ2 A4 E16 HDJ34 HAJ10 U6 E4 N2 G25

D02# D34# A10# HITM# HITMJ 16 26 IGNNEJ IGNNE# TESTHI03

HDJ3 C6 G18 HDJ35 HAJ11 T4 AB2 HIERRJ M3 G27

D03# D35# A11# IERR# 26 STPCLKJ STPCLK# TESTHI04

HDJ4 A5 G17 HDJ36 HAJ12 U5 P3 G26

HDJ5 D04# D36# HDJ37 HAJ13 A12# INIT# INITJ 26 TESTHI05

D B6 F17 U4 C3 15 HVCCA A23 G24 D

HDJ6 D05# D37# HDJ38 HAJ14 A13# LOCK# HLOCKJ 16 VCCA TESTHI06 TESTHI_2_7

B7 F18 V5 E3 15 HVSSA B23 F24

HDJ7 A7 D06# D38# E18 HDJ39 HAJ15 V4 A14# TRDY# AD3 TP_BINITJ HTRDYJ 16 VCC_PLL D23 VSSA TESTHI07 AK6 FORCEPHJ

D07# D39# A15# BINIT# TP2 RSVD5 FORCEPH

HDJ8 A10 E19 HDJ40 HAJ16 W5 G7 C23 G6

D08# D40# A16# DEFER# HDEFERJ 16 15 HVCCIOPLL VCCIOPLL RSVD11

HDJ9 A11 F20 HDJ41 N4 F2 HGTLREF_1

HDJ10 B10 D09# D41# E21 HDJ42 P5 RSVD1 EDRDY# AB3 TP_MCERRJ L2 TESTHI_13

D10# D42# 16 HREQJ[4..0] RSVD2 MCERR# TP3 TESTHI13 TESTHI_13 26

HDJ11 C11 F21 HDJ43 HREQJ0 K4 VID0 AM2 AH2

D11# D43# REQ0# 35 VID0 VID0 RSVD12

HDJ12 D8 G21 HDJ44 HREQJ1 J5 U2 TP_APJ0 VID1 AL5 N1

D12# D44# REQ1# AP0# TP4 35 VID1 VID1 PWRGOOD CPU_PWRG 25

HDJ13 B12 E22 HDJ45 HREQJ2 M6 U3 TP_APJ1 VID2 AM3 AL2 PROCHOTJ

D13# D45# REQ2# AP1# TP5 35 VID2 VID2 PROCHOT#

HDJ14 C12 D22 HDJ46 HREQJ3 K6 VID3 AL6 M2

D14# D46# REQ3# 35 VID3 VID3 THERMTRIP# THERMTRIPJ 26

HDJ15 D11 G22 HDJ47 HREQJ4 J6 F3 HBR0J VID4 AK4

D15# D47# HAJ[35..3] REQ4# BR0# HBR0J 16 35 VID4 VID4

HDBIJ0 A8 D19 HDBIJ2 R6 G3 TESTHI_8 VID5 AL4

16 HDBIJ0 DBI0# DBI2# HDBIJ2 16 16 HAJ[35..3] 16 HADSTBJ0 ADSTB0# TESTHI08 35 VID5 VID5

C8 G20 G5 G4 TESTHI_9 VID6 AM5 A13 HCOMP0

16 HDSTBNJ0 DSTBN0# DSTBN2# HDSTBNJ2 16 35 PECI PCREQ# TESTHI09 35 VID6 FC11 COMP0

B9 G19 H5 TESTHI_10 VID7 AM7 T1 HCOMP1

16 HDSTBPJ0 DSTBP0# DSTBP2# HDSTBPJ2 16 TESTHI10 35 VID7 FC12 COMP1

HAJ17 AB6 VID_SELECT AN7 G2 HCOMP2

A17# 10,25 VID_SELECT FC16 COMP2

HDJ16 G9 D20 HDJ48 HAJ18 W6 J16 TP_DPJ0 F28 R1 HCOMP3

D16# D48# A18# DP0# TP6 8 CK_200M_P_CPU BCLK0 COMP3

HDJ17 F8 D17 HDJ49 HAJ19 Y6 H15 TP_DPJ1 G28 J2 HCOMP4

D17# D49# A19# DP1# TP8 8 CK_200M_N_CPU BCLK1 COMP4

HDJ18 F9 A14 HDJ50 HAJ20 Y4 H16 TP_DPJ2 T2 HCOMP5

D18# D50# A20# DP2# TP9 COMP5

HDJ19 E9 C15 HDJ51 4 mils width, 10 mils spacing HAJ21 AA4 J17 TP_DPJ3 AE8

D19# D51# A21# DP3# TP10 TP11 SKTOCC#

HDJ20 D7 C14 HDJ52 HAJ22 AD6 N5

HDJ21 D20# D52# HDJ53 HAJ23 A22# HGTLREF_1 RSVD13

E10 B15 AA5 H2 AE6

HDJ22 D21# D53# HDJ54 HAJ24 A23# GTLREF1 HGTLREF_0 RSVD14 H_TEST

D10 C18 AB5 H1 35 THERMDA AL1 C9

HDJ23 D22# D54# HDJ55 HAJ25 A24# GTLREF0 MCH_GTLREF_CPU THERMDA RSVD15 HGTLREF_0

F11 B16 AC5 E24 AK1 G10

D23# D55# A25# CS_GTLREF MCH_GTLREF_CPU 16 35 THERMDC THERMDC RSVD16

HDJ24 F12 A17 HDJ56 HAJ26 AB4 D16

HDJ25 D24# D56# HDJ57 HAJ27 A26# RSVD17

D13 B18 AF5 AN3 A20

HDJ26 D25# D57# HDJ58 HAJ28 A27# VCCSENSE RSVD18

E13 C21 AF4 G23 AN4 E23

HDJ27 D26# D58# HDJ59 HAJ29 A28# RESET# HCPURSTJ 16 VSSSENSE RSVD19

G13 B21 AG6 10 VCC_SENSE AN5 F23

HDJ28 D27# D59# HDJ60 HAJ30 A29# VCC_MB_REG RSVD21

F14 B19 AG4 B3 10 VSS_SENSE AN6 J3

HDJ29 G14 D28# D60# A19 HDJ61 HAJ31 AG5 A30# RS0# F5 HRSJ0 16 VSS_MB_REG RSVD24

HDJ30 D29# D61# HDJ62 HAJ32 A31# RS1# HRSJ1 16 Changed pin name MS_ID1

F15 A22 AH4 A3 V1

HDJ31 D30# D62# HDJ63 HAJ33 A32# RS2# HRSJ2 16 MSID1 MS_ID0

G15 B22 AH5 F29 from RSV W1

HDBIJ1 G11 D31# D63# C20 HDBIJ3 HAJ34 AJ5 A33# RSVD9 MSID0

16 HDBIJ1 DBI1# DBI3# HDBIJ3 16 A34#

G12 A16 HAJ35 AJ6

16 HDSTBNJ1 DSTBN1# DSTBN3# HDSTBNJ3 16 A35#

E12 C17 AC4 THERMDA/THERMDC Y1 CPU_BOOT

16 HDSTBPJ1 DSTBP1# DSTBP3# HDSTBPJ3 16 RSVD3 BOOTSELECT TP12

AE4 1. width=10 mils, spacing=10 mils. V2 TP_CPU_V2

RSVD4 LL_ID0 TP13

AD5 2. route the lines in parallel AA2 TP_CPU_AA2

16 HADSTBJ1 ADSTB1# LL_ID1 TP14

Socket-IntelPrescottCPU

Socket-IntelPrescottCPU

C 1 OF 7 C

Socket-IntelPrescottCPU

* *

R228 62 HTCK

VTT_OUT_LEFT VTT_OUT_RIGHT +/-5% r0402h4

R215 1D5V_CORE

51 Ohm R227 62 HTRSTJ

*

R232 62 HTDO +/-5% r0402h4

VTT_OUT_LEFT * +/-5%

r0402h4

+/-5% r0402h4 Dummy

CP13

Dummy X_COPPER In Design Guide is NC

Place at CPU end of route

*

R204 62 +/-5% r0402h4 HBR0J U11D 4 OF 7 FSB_VTT

* *

MS_ID0 R216 51 Ohm +/-5% r0402h4 VCC_PLL HTCK AE1 A29

Place at CPU end of route VTT_OUT_RIGHT HTDI AD1 TCK VTT1 B25

C149 C150 HTDO TDI VTT2

AF1 B29

1

MS_ID1 R214 51 Ohm +/-5% r0402h4 10uF 10nF HTMS TDO VTT3

* * 25V, X7R, +/-10% HTRSTJ

AC1

AG1

TMS

TRST#

VTT4

VTT5

B30

C29

RN23 TESTHI_9 R246 130 +/-1% r0402h4 FORCEPHJ 10V, Y5V, +80%/-20% Reserved A26

2

51 7 8 TESTHI_8 MSID0: NC = 2005 Mainstream / Value, 2006 65W FMB VTT6

B27

+/-5% 5 6 TESTHI_10 Vss = 2005 Performance FMB R245 130 +/-1% r0402h4 PROCHOTJ HBPM0J VTT7

AJ2 C28

8p4r0603h7 * 3 4 H_TEST MSID1: Vss = 2005 Performance,2005 Mainstream/Value,2006 65W FMB HBPM1J AJ1 BPM0# VTT8 A25

1 2 VTT_OUT_RIGHT HBPM2J BPM1# VTT9

placed near pin D23, within 500 mils AD2 A28

HBPM3J BPM2# VTT10

AG2 A27

RN32 VID2 VTT_OUT_RIGHT HBPM4J BPM3# VTT11

AF2 C30

7 8 680 VID4 HBPM5J BPM4# VTT12

AG3 A30

RN31 TESTHI_12 5 6 +/-5% VID5 BPM5# VTT13

C25

* **

51 7 8 TESTHI_11 *3 4 8p4r0603h7 VID0 R219 62 +/-5% r0402h4 HIERRJ ICH_SYS_RSTJ AC2

VTT14

C26

8,9,25 ICH_SYS_RSTJ

+/-5% 5 6 TESTHI_1 1 2 DBR# VTT15 C27 VRMPWRGD 8,10,25

8p4r0603h7 3 4 TESTHI_13 R217 62 +/-5% r0402h4 HCPURSTJ VTT16

AK3 B26

*R254

* 1 2 ITPCLKOUT0 VTT17

RN33 VID3 Place at CPU end of route AJ3 D27 0

*

7 8 680 VID6 PROCHOTJ R244 0 +/-5% ITPCLKOUT1 VTT18 +/-5%

D28

*

R208 49.9 +/-1% r0402h4 HCOMP4 5 6 +/-5% VID7 R247 1K +/-1% r0402h4 VID_SELECT r0402h4 Dummy ICH_THRM_UP 25,35 FSBSEL0 G29 VTT19 D25 Dummy

B 3 4 8 FSBSEL0 BSEL0 VTT20 B

Reserved 10 mils width * 8p4r0603h7 VID1 FSBSEL1 H30 D26 r0402h4

1 2 8 FSBSEL1 FSBSEL2 BSEL1 VTT21

7 mils spacing to low speed signals Stuff to enable Thermal event G30 B28

8 FSBSEL2 BSEL2 VTT22 VTT_PWRGD 11

14mils spacing to high speed signals D29

VTT23

max. 1200mils D30

FSB_VTT VTT_OUT_RIGHT VTT24 VTT_OUT_RIGHT VTT_OUT_LEFT

AM6

**

R207 49.9 +/-1% r0402h4 HCOMP2 VTTPWRGD

AA1 VTT_OUT_RIGHT

* *

R156 49.9 +/-1% r0402h4 HCOMP0 R123 51 Ohm +/-5% r0402h4 TESTHI_0 VTT_OUT1 VTT_OUT_LEFT

J1

VTT_OUT2 F27

VTT_OUT_LEFT VTT_SEL TP21

10 mils width R122 51 Ohm +/-5% r0402h4 TESTHI_2_7 Socket-IntelPrescottCPU

7 mils spacing to low speed signals RN24 HBPM2J

14mils spacing to high speed signals 7 8 51 HBPM3J

max. 1200mils

5 6 +/-5% HTDI R206

*3 4 8p4r0603h7 HTMS 51 Ohm

1 2 * +/-5%

***

R209 49.9 +/-1% r0402h4 HCOMP3 r0402h4 VTT_OUT_RIGHT VTT_OUT_LEFT

R210 49.9 +/-1% r0402h4 HCOMP1 RN25 HBPM1J

R211 49.9 +/-1% r0402h4 HCOMP5 7 8 51 HBPM0J TP_CPU_G1 C335 C313

VTT_OUT_LEFT 5 6 TP_CPU_G1 15

Dummy +/-5% HBPM5J 0.1uF 0.1uF

*3

1

4

2

8p4r0603h7 HBPM4J * *

16V, Y5V, +80%/-20% 16V, Y5V, +80%/-20%

Place BPM termination near CPU reserve for Kentsfield CPU support Dummy Dummy

VTT_OUT_RIGHT VTT_OUT_RIGHT

GTLREF voltage should be 0.63*VTT

R251

* 115 Ohm *R255

115 Ohm

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

+/-1% +/-1% 0.22nF caps should be placed near CPU pin

A place series resistor as close to divider A

*

*

R231 10 HGTLREF_0 R230 10 HGTLREF_1

+/-1% +/-1%

C300

C325

* *R250

200

*

C301

220pF

C312

1uF * *R249

200 * 220pF

50V, NPO, +/-5%

1uF +/-1% 50V, NPO, +/-5% 10V, Y5V, +80%/-20% +/-1%

10V, Y5V, +80%/-20%

FOXCONN PCEG

Title

LGA775-1

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 14 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

VCCP

AG22

5

U11E 5 OF 7

AK12

www.sp860.com

VCCP VCCP

4

AF9

U11F 6 OF 7

AL23

3

H22

QQ:453100829

U11G 7 OF 7

D5

2 1

FSB_VTT

VCCP1 VCCP93 VCCP185 VSS41 VSS126 VSS211

K29 AH22 AF22 A12 H21 A9

VCCP2 VCCP94 VCCP186 VSS42 VSS127 VSS212

AM26

VCCP3 VCCP95

T29 AH11

VCCP187 VSS43

L25 H20

VSS128 VSS213

D3 PLL Supply Filter

AL8 AM14 AJ14 J7 H19 B1

VCCP4 VCCP96 VCCP188 VSS44 VSS129 VSS214 R120

AE12 AM25 AH19 AE28 H18 B5

VCCP5 VCCP97 VCCP189 VSS45 VSS130 VSS215 0

AE11 AE9 AH29 AE29 AB7 B8

VCCP6 VCCP98 VCCP190 VSS46 VSS131 VSS216 +/-5%

W23 Y29 AH27 K5 H17 AJ4

VCCP7 VCCP99 VCCP191 VSS47 VSS132 VSS217

W24 AK25 AG28 J4 AJ24 AE26

VCCP8 VCCP100 VCCP192 VSS48 VSS133 VSS218

D W25 AK19 AL26 AE30 AM17 AH1 D

VCCP9 VCCP101 VCCP193 VSS49 VSS134 VSS219 TP_CPU_E29

T25 AG15 AM12 AN20 AC3 E29 TP15

VCCP10 VCCP102 VCCP194 VSS50 VSS135 VSS220

Y28 J22 J24 AF10 H14 V7

VCCP11 VCCP103 VCCP195 VSS51 VSS136 VSS221

AL18 T24 J13 AE24 P28 C13

VCCP12 VCCP104 VCCP196 VSS52 VSS137 VSS222

AC25 AG21 T28 AM24 V6 AK24

VCCP13 VCCP105 VCCP197 VSS53 VSS138 VSS223 HVCCIOPLL

W30 AM21 W28 AN23 AK2 AB30 14 HVCCIOPLL

VCCP14 VCCP106 VCCP198 VSS54 VSS139 VSS224

Y30 J25 J12 H9 P27 L6

VCCP15 VCCP107 VCCP199 VSS55 VSS140 VSS225

AN14 U30 J27 H8 P26 L7

VCCP16 VCCP108 VCCP200 VSS56 VSS141 VSS226 HVCCA

AD28 AL21 AG19 H13 AM28 AB29 14 HVCCA

VCCP17 VCCP109 VCCP201 VSS57 VSS142 VSS227

Y26 AG25 AL9 AC6 AJ13 M1

VCCP18 VCCP110 VCCP202 VSS58 VSS143 VSS228

AC29 AJ18 AD30 AC7 W4 AB28

VCCP19 VCCP111 VCCP203 VSS59 VSS144 VSS229 EC36

M29 J19 AF21 AH6 P25 E8

VCCP20 VCCP112 VCCP204 VSS60 VSS145 VSS230

U24

J23

VCCP21 VCCP113

AH30

J15

Y24

AK14

VCCP205 VSS61

C16

AM16

AJ20

W7

VSS146 VSS231

AG20

AN17

* 100uF

+/-20%

VCCP22 VCCP114 VCCP206 VSS62 VSS147 VSS232

AC27 AG12 J9 AE25 P23 AB27

VCCP23 VCCP115 VCCP207 VSS63 VSS148 VSS233

AM18 AJ22 M27 AE27 AG13 AB26

VCCP24 VCCP116 VCCP208 VSS64 VSS149 VSS234

AM19 J20 AF14 AJ28 AG16 AN16

VCCP25 VCCP117 VCCP209 VSS65 VSS150 VSS235

AB8 AH18 J30 AJ7 AG17 M7

VCCP26 VCCP118 VCCP210 VSS66 VSS151 VSS236 HVSSA

AC26 AH26 AG18 F19 C7 AB25 14 HVSSA

VCCP27 VCCP119 VCCP211 VSS67 VSS152 VSS237

J8 W27 AA8 AH13 Y2 AB24

VCCP28 VCCP120 VCCP212 VSS68 VSS153 VSS238 Notes:

J28 AL25 AG8 AD7 L30 AB23

VCCP29 VCCP121 VCCP213 VSS69 VSS154 VSS239 1. Cap. should be within 1.5" mils of the VCCA and VSSA pins

T30 AN8 AL29 AH16 L29 N3

VCCP30 VCCP122 VCCP214 VSS70 VSS155 VSS240 2. VCCA route should be parallel and next to VSSA route to

AM9 AH14 AD29 AK17 D15 AA30

VCCP31 VCCP123 VCCP215 VSS71 VSS156 VSS241 minimize loop area

AF15 U27 W8 E17 AL27 F4

VCCP32 VCCP124 VCCP216 VSS72 VSS157 VSS242 3. VCCIOPLL route should be parallel and next to VSSA route

AC8 T23 AH8 AH17 Y7 AG10

VCCP33 VCCP125 VCCP217 VSS73 VSS158 VSS243 to minimize loop area

AE14 R8 N24 AH20 L27 AE13

VCCP34 VCCP126 VCCP218 VSS74 VSS159 VSS244 3. Min. 12 mils trace from the filter to the processor pins

N23 AK22 AN22 AE5 AA29 AF30

VCCP35 VCCP127 VCCP219 VSS75 VSS160 VSS245 4. The inductors should be close to the cap.

C W29 AN29 J14 AH23 N6 H28 C

VCCP36 VCCP128 VCCP220 VSS76 VSS161 VSS246

U29 AG11 K26 AE7 N7 F7

VCCP37 VCCP129 VCCP221 VSS77 VSS162 VSS247

AC24 AK26 AF19 AM13 AA28 AF29

VCCP38 VCCP130 VCCP222 VSS78 VSS163 VSS248

AC23 J10 N8 AH24 AN13 AF28

VCCP39 VCCP131 VCCP223 VSS79 VSS164 VSS249

Y23 AJ15 AF12 AJ30 AA27 G1 TP_CPU_G1 14

VCCP40 VCCP132 VCCP224 VSS80 VSS165 VSS250

AN26 AG26 M28 AJ10 AA26 AF27

VCCP41 VCCP133 VCCP225 VSS81 VSS166 VSS251

AN25 AN9 AK9 AF3 P4 AF26

VCCP42 VCCP134 VCCP226 VSS82 VSS167 VSS252

AN11 AH15 AK5 AA25 AF25

VCCP43 VCCP135 VSS83 VSS168 VSS253

AN18 AF18 AJ16 AA24 AN28

VCCP44 VCCP136 VSS84 VSS169 VSS254

Y27 AL15 C10 AF6 P7 AN27

VCCP45 VCCP137 VSS1 VSS85 VSS170 VSS255

Y25 J26 D12 AK29 E26 AF24

VCCP46 VCCP138 VSS2 VSS86 VSS171 VSS256 VTT_OUT_RIGHT

AD24 J18 AJ17 V30 AF23

VCCP47 VCCP139 VSS87 VSS172 VSS257

AE23 J21 C24 F22 R2 AG24

VCCP48 VCCP140 VSS4 VSS88 VSS173 VSS258

AE22 AG27 K2 AH3 V29 AF17

VCCP49 VCCP141 VSS5 VSS89 VSS174 VSS259

AN19 AK15 C22 AK10 V28 AN24

VCCP50 VCCP142 VSS6 VSS90 VSS175 VSS260

V8 AF11 AN1 AM10 R5 H3

VCCP51 VCCP143 VSS7 VSS91 VSS176 VSS261

K8 AD23 B14 F16 V27

**

VCCP52 VCCP144 VSS8 VSS92 VSS177 R218 49.9 +/-1% r0402h4 HCOMP6

AE21 AM15 K7 AJ23 R7 P24

VCCP53 VCCP145 VSS9 VSS93 VSS178 VSS263 Dummy

AM30 AF8 AE16 F13 E20 AE20

VCCP54 VCCP146 VSS10 VSS94 VTT_OUT_LEFT VSS179 VSS264 R220 49.9 +/-1% r0402h4 HCOMP7

AE19 AK21 B11 AG7 AN10 AE17

VCCP55 VCCP147 VSS11 VSS95 VSS180 VSS265 Reserved

AC30 AG30 AL10 F10 V25 E27

VCCP56 VCCP148 VSS12 VSS96 VSS181 VSS266

AE15 AJ21 AK23 L26 T3 T7

VCCP57 VCCP149 VSS13 VSS97 R213 VSS182 VSS267 10 mils width

M30 AM11 H12 AD4 V24 R30

K27

VCCP58

VCCP59

VCCP150

VCCP151

AL11 AF7

VSS14

VSS15

VSS98

VSS99

H11 *

51 Ohm V23

VSS183

VSS184

VSS268

VSS269

AJ27 7 mils spacing to low speed signals

14mils spacing to high speed signals

M24 AJ11 AK7 L24 +/-5% T6 AB1

VCCP60 VCCP152 VSS16 VSS100 r0402h4 VSS185 VSS270 max. 1200mils

AN21 K30 H7 L23 AL7 AM4

VCCP61 VCCP153 VSS17 VSS101 VSS186 VSS271

T8 AL14 E14 AM23 E25 V26

VCCP62 VCCP154 VSS18 VSS102 VSS187 VSS272

B AC28 AN30 L28 A15 U1 AA23 B

VCCP63 VCCP155 VSS19 VSS103 VSS188 VSS273

N25 AH25 Y5 AH10 R29 AL28

VCCP64 VCCP156 VSS20 VSS104 VSS189 VSS274

AE18 AL12 E11 H29 TP17 R28 AF20

VCCP65 VCCP157 VSS21 VSS105 VSS190 VSS275 R155 24.9 HCOMP8

W26 AJ9 AL16 B24 R27 AG23

VCCP66 VCCP158 VSS22 VSS106 VSS191 VSS276 +/-1%

AD25 AK11 AL24 L3 R26

VCCP67 VCCP159 VSS23 VSS107 VSS192

M8 AG14 AK13 H27 R25

VCCP68 VCCP160 VSS24 VSS108 VSS193

N30 N29 TP68 AL3 A21 U7

VCCP69 VCCP161 VSS25 VSS109 VSS194

AD26 AL30 D21 AE2 R24

VCCP70 VCCP162 VSS26 VSS110 VSS195 15 mils width

AJ26 AJ25 AL20 AJ29 R23

*

VCCP71 VCCP163 VSS27 VSS111 VSS196 7 mils spacing to low speed signals

AM29 AH9 D18 A24 P30

VCCP72 VCCP164 VSS28 VSS112 VSS197 14mils spacing to high speed signals

M25 J29 AN2 AK27 V3

VCCP73 VCCP165 VRDSEL VSS29 VSS113 R115 VSS198 max. 1200mils

M26 J11 AK16 AK28 P29

VCCP74 VCCP166 VSS30 VSS114 1K VSS199 IMPSEL

L8 K25 AK20 B20 AF16 F6

VCCP75 VCCP167 VSS31 VSS115 +/-5% VSS200 RSVD26

U25 P8 AM27 AM20 AE10

VCCP76 VCCP168 VSS32 VSS116 r0402h4 VSS201 HCOMP6

Y8 K23 AM1 H26 AF13 Y3

VCCP77 VCCP169 VSS33 VSS117 Dummy VSS202 RSVD28 HCOMP7

AJ12 AL19 AL13 B17 H6 AE3

VCCP78 VCCP170 VSS34 VSS118 VSS203 RSVD29

AD27 AM8 AL17 H25 A18

*

VCCP79 VCCP171 VSS35 VSS119 VSS204 R205 51 Ohm IMPSEL

U23 T26 C19 H24 A2 E7

VCCP80 VCCP172 VSS36 VSS120 VSS205 RSVD31 HCOMP8 +/-5% r0402h4

M23 N28 E28 AA3 E2 B13

VCCP81 VCCP173 VSS37 VSS121 VSS206 RSVD32

AG29 AH12 AH7 AA7 D9 D14

VCCP82 VCCP174 VSS38 VSS122 VSS207 RSVD33

N27 AL22 AK30 H23 C4 E6

VCCP83 VCCP175 VSS39 VSS123 VSS208 RSVD34

AM22 AN15 D24 AA6 A6 D1

VCCP84 VCCP176 VSS40 VSS124 VSS209 RSVD35

U28 AJ8 H10 D6 E5

VCCP85 VCCP177 VSS125 VSS210 RSVD36

K28 U26

VCCP86 VCCP178

U8 AJ19 Socket-IntelPrescottCPU Socket-IntelPrescottCPU

VCCP87 VCCP179

AK18 T27

VCCP88 VCCP180

AD8 AK8

VCCP89 VCCP181

A K24 AN12 A

VCCP90 VCCP182

AH28 AG9

VCCP91 VCCP183

AH21 N26

VCCP92 VCCP184

Socket-IntelPrescottCPU FOXCONN PCEG

Title

LGA775-2

Size Document Number Rev

Custom G31M04 A

Date: Wednesday, September 12, 2007 Sheet 15 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

14 HAJ[35..3]

5

HAJ3

HAJ4

J42

HA3#

U1MCH

U12B

HD0#

www.sp860.com

R40 HDJ0

HDJ1

HDJ[63..0]

4

HDJ[63..0] 14

3

QQ:453100829 2

U12E

1

Placed both Resistors close to GMCH

Within 750 mils

L39 P41 W=4 mils, S=10 mils from GMCH to connector

HAJ5 J40 HA4# HD1# R41 HDJ2

**

HAJ6 HA5# HD2# HDJ3 U1MCH BSEL0 HSYNC_P R139 39 +/-1%

L37 N40 G20 C15

HA6# HD3# U12A BSEL0 HSYNC HSYNC 24

HAJ7 L36 R42 HDJ4 BSEL1 J20 D15 VSYNC_P R140 39 +/-1%

HA7# HD4# BSEL1 VSYNC VSYNC 24

HAJ8 K42 M39 HDJ5 EXP_RXP0 F15 D11 EXP_TXP0 BSEL2 J18 Modify by Steven 051707 Apply 0402 or not

HA8# HD5# 23 EXP_RXP0 EXP_RXP0 EXP_TXP0 EXP_TXP0 23 BSEL2

HAJ9 N32 N41 HDJ6 EXP_RXN0 G15 D12 EXP_TXN0 TP16 TP_ALLZTEST K20 B18

HA9# HD6# 23 EXP_RXN0 EXP_RXN0* EXP_TXN0* EXP_TXN0 23 ALLZTEST RED RED 24

HAJ10 N34 N42 HDJ7 EXP_RXP1 K15 B11 EXP_TXP1 F20 C19

HA10# HD7# 23 EXP_RXP1 EXP_RXP1 EXP_TXP1 EXP_TXP1 23 XORTEST GREEN GREEN 24

HAJ11 M38 L41 HDJ8 EXP_RXN1 J15 A10 EXP_TXN1 G18 B20

FSB

HA11# HD8# 23 EXP_RXN1 EXP_RXN1* EXP_TXN1* EXP_TXN1 23 RESERVED_24 BLUE BLUE 24

HAJ12 N37 J39 HDJ9 EXP_RXP2 F12 C10 EXP_TXP2 GMCH_EXP_SLR E18 C18 R152 R153 R151

HA12# HD9# 23 EXP_RXP2 EXP_RXP2 EXP_TXP2 EXP_TXP2 23 EXP_SLR RED#

HAJ13 M36 L42 HDJ10 EXP_RXN2 E12 D9 EXP_TXN2 K17 D19 150 150 150

HA13# HD10# 23 EXP_RXN2 EXP_RXN2* EXP_TXN2* EXP_TXN2 23 RESERVED_25 GREEN# * * *

VGA

HAJ14 R34 J41 HDJ11 EXP_RXP3 J12 B9 EXP_TXP3 GMCH_EXP_EN_HDR J17 D20 +/ -1% +/ -1% +/ -1%

D HA14# HD11# 23 EXP_RXP3 EXP_RXP3 EXP_TXP3 EXP_TXP3 23 EXP_EN BLUE# D

HAJ15 N35 K41 HDJ12 EXP_RXN3 H12 B7 EXP_TXN3 H18 r0402h4 r0402h4 r0402h4

HA15# HD12# 23 EXP_RXN3 EXP_RXN3* EXP_TXN3* EXP_TXN3 23 RESERVED

HAJ16 N38 G40 HDJ13 EXP_RXP4 J11 D7 EXP_TXP4 L13 DDCA_DATA

HA16# HD13# 23 EXP_RXP4 EXP_RXP4 EXP_TXP4 EXP_TXP4 23 DDC_DATA DDCA_DATA 24

HAJ17 U37 F41 HDJ14 EXP_RXN4 H11 D6 EXP_TXN4 L17 M13 DDCA_CLK

HA17# HD14# 23 EXP_RXN4 EXP_RXN4* EXP_TXN4* EXP_TXN4 23 RESERVED_1 DDC_CLK DDCA_CLK 24

HAJ18 N39 F42 HDJ15 EXP_RXP5 F7 B5 EXP_TXP5 N17 Placed close to

HA18# HD15# 23 EXP_RXP5 EXP_RXP5 EXP_TXP5 EXP_TXP5 23 RESERVED_2

HAJ19 R37 C42 HDJ16 EXP_RXN5 E7 B6 EXP_TXN5 N18 A20 REFSET GMCH within

HA19# HD16# 23 EXP_RXN5 EXP_RXN5* EXP_TXN5* EXP_TXN5 23 RESERVED_3 REFSET

HAJ20 P42 D41 HDJ17 EXP_RXP6 E5 B3 EXP_TXP6 N15 300 mils

HA20# HD17# 23 EXP_RXP6 EXP_RXP6 EXP_TXP6 EXP_TXP6 23 RESERVED_4

HAJ21 R39 F38 HDJ18 EXP_RXN6 F6 B4 EXP_TXN6 M20 C14 CK_96M_P_GMCH

HA21# HD18# 23 EXP_RXN6 EXP_RXN6* EXP_TXN6* EXP_TXN6 23 RESERVED_5 DREFCLKP CK_96M_P_GMCH 8

HAJ22 V36 G37 HDJ19 EXP_RXP7 C2 F2 EXP_TXP7 L15 D13 CK_96M_N_GMCH

HA22# HD19# 23 EXP_RXP7 EXP_RXP7 EXP_TXP7 EXP_TXP7 23 RESERVED_6 DREFCLKN CK_96M_N_GMCH 8

HAJ23 R38 E42 HDJ20 EXP_RXN7 D2 E2 EXP_TXN7 Controller Link Routing L18 L12

HA23# HD20# 23 EXP_RXN7 EXP_RXN7* EXP_TXN7* EXP_TXN7 23 RESERVED_7 VCC 1D25V_MCH

HAJ24 U36 E39 HDJ21 EXP_RXP8 G6 F4 EXP_TXP8 1. width=4 mils, Spacing=7 mils M18 M11

PCIE

HA24# HD21# 23 EXP_RXP8 EXP_RXP8 EXP_TXP8 EXP_TXP8 23 RESERVED_8 VSS

HAJ25 U33 E37 HDJ22 EXP_RXN8 G5 G4 EXP_TXN8 2. CL_CLK and CL_DATA should be length

HA25# HD22# 23 EXP_RXN8 EXP_RXN8* EXP_TXN8* EXP_TXN8 23

HAJ26 R35 C39 HDJ23 EXP_RXP9 L9 J4 EXP_TXP9 matched to within 100 mils

HA26# HD23# 23 EXP_RXP9 EXP_RXP9 EXP_TXP9 EXP_TXP9 23

HAJ27 V33 B39 HDJ24 EXP_RXN9 L8 K3 EXP_TXN9

HA27# HD24# 23 EXP_RXN9 EXP_RXN9* EXP_TXN9* EXP_TXN9 23

HAJ28 V35 G33 HDJ25 EXP_RXP10 M8 L2 EXP_TXP10 TP19 AD12 F13 TP_MCH_F13

HA28# HD25# 23 EXP_RXP10 EXP_RXP10 EXP_TXP10 EXP_TXP10 23 CL_DATA RESERVED_001 TP20

HAJ29 Y34 A37 HDJ26 EXP_RXN10 M9 K1 EXP_TXN10 TP18 AD13 F17

HA29# HD26# 23 EXP_RXN10 EXP_RXN10* EXP_TXN10* EXP_TXN10 23 CL_CLK RESERVED_23

HAJ30 V42 F33 HDJ27 EXP_RXP11 M4 N2 EXP_TXP11 CL_VREF_MCH AM5 A14 TP_MCH_A14

23 EXP_RXP11 EXP_TXP11 23 TP22

MISC

HAJ31 V38 HA30# HD27# E35 HDJ28 EXP_RXN11 L4 EXP_RXP11 EXP_TXP11 M2 EXP_TXN11 PLTRSTJ R199 1.65KOhm CL_RST AA12 CL_VREF RESERVED_26 AM18 ICH_PLTRSTJ

HA31# HD28# 23 EXP_RXN11 EXP_RXN11* EXP_TXN11* EXP_TXN11 23 CL_RST# RSTIN# PLTRSTJ 25,29,35

HAJ32 Y36 K32 HDJ29 EXP_RXP12 M5 P3 EXP_TXP12 +/-1% r0402h4 AM15 AM17 PWRGD_3V

EXP_TXP12 23 PWRGD_3V 25,35

*

HAJ33 HA32# HD29# HDJ30 23 EXP_RXP12 EXP_RXN12 EXP_RXP12 EXP_TXP12 EXP_TXN12 R197 1K CL_PWROK PWROK ICH_SYNCJ

Y38 H32 M6 N4 J13

HA33# HD30# 23 EXP_RXN12 EXP_RXN12* EXP_TXN12* EXP_TXN12 23 ICH_SYNC# ICH_SYNCJ 25

HAJ34 Y39 B34 HDJ31 EXP_RXP13 R9 R2 EXP_TXP13 +/-1% r0402h4

HA34# HD31# 23 EXP_RXP13 EXP_RXP13 EXP_TXP13 EXP_TXP13 23

HAJ35 AA37 J31 HDJ32 EXP_RXN13 R10 P1 EXP_TXN13 A42 TP_MCH_DET_N

HA35# HD32# 23 EXP_RXN13 EXP_RXN13* EXP_TXN13* EXP_TXN13 23 NC TP23

F32 HDJ33 EXP_RXP14 T4 U2 EXP_TXP14 PWRGD_3V

HD33# 23 EXP_RXP14 EXP_RXP14 EXP_TXP14 EXP_TXP14 23

M31 HDJ34 EXP_RXN14 R4 T2 EXP_TXN14 AA10

14 HREQJ[4..0] HD34# 23 EXP_RXN14 EXP_RXN14* EXP_TXN14* EXP_TXN14 23 RESERVED_9

HREQJ0 F40 E31 HDJ35 EXP_RXP15 R6 V3 EXP_TXP15 AA9 BC43 TP_MCH_CGC_1

HREQ0# HD35# 23 EXP_RXP15 EXP_RXP15 EXP_TXP15 EXP_TXP15 23 RESERVED_10 TEST0 TP24

HREQJ1 L35 K31 HDJ36 EXP_RXN15 R7 U4 EXP_TXN15 AA11 BC1 TP_MCH_CGC_2

HREQ1# HD36# 23 EXP_RXN15 EXP_RXN15* EXP_TXN15* EXP_TXN15 23 RESERVED_11 TEST1 TP26

HREQJ2 L38 G31 HDJ37 Y12 A43 TP_MCH_CGC_3

HREQ2# HD37# RESERVED_12 TEST2 TP25

HREQJ3 G43 K29 HDJ38 DMI_RXP0 W2 V7 C2590.1uF 16V, X7R, +/-10% DMI_TXP0

DMI_TXP0 25

********

HREQJ4 J37 HREQ3# HD38# F31 HDJ39 25 DMI_RXP0 DMI_RXN0 V1 DMI_RXP0 DMI_TXP0 V6 C2580.1uF 16V, X7R, +/-10% DMI_TXN0 U30

HREQ4# HD39# 25 DMI_RXN0 DMI_RXN0* DMI_TXN0* DMI_TXN0 25 RESERVED_13

J29 HDJ40 DMI_RXP1 Y8 W4 C2480.1uF 16V, X7R, +/-10% DMI_TXP1 U31 N20

HD40# 25 DMI_RXP1 DMI_RXP1 DMI_TXP1 DMI_TXP1 25 RESERVED_14 NC_1

M34 F29 HDJ41 DMI_RXN1 Y9 Y4 C2530.1uF 16V, X7R, +/-10% DMI_TXN1 R29 BC42

14 HADSTBJ0 HADSTB0# HD41# 25 DMI_RXN1 DMI_RXN1* DMI_TXN1* DMI_TXN1 25 RESERVED_15 NC_2

DMI

U34 L27 HDJ42 DMI_RXP2 AA7 AC8 C2610.1uF 16V, X7R, +/-10% DMI_TXP2 R30 BC2

14 HADSTBJ1 HADSTB1# HD42# 25 DMI_RXP2 DMI_RXP2 DMI_TXP2 DMI_TXP2 25 RESERVED_16 NC_3

K27 HDJ43 DMI_RXN2 AA6 AC9 C2660.1uF 16V, X7R, +/-10% DMI_TXN2 BB43

HD43# 25 DMI_RXN2 DMI_RXN2* DMI_TXN2* DMI_TXN2 25 NC_4

L40 H26 HDJ44 DMI_RXP3 AB3 Y2 C2570.1uF 16V, X7R, +/-10% DMI_TXP3 U12 BB1

14 HDSTBPJ0 HDSTBP0# HD44# 25 DMI_RXP3 DMI_RXP3 DMI_TXP3 DMI_TXP3 25 RESERVED_17 NC_5

M43 L26 HDJ45 DMI_RXN3 AA4 AA2 C2640.1uF 16V, X7R, +/-10% DMI_TXN3 U11 B43

14 HDSTBNJ0 HDSTBN0# HD45# 25 DMI_RXN3 DMI_RXN3* DMI_TXN3* DMI_TXN3 25 RESERVED_18 NC_6

HDBIJ0 M40 J26 HDJ46 R12 B42 3D3V_SYS

14 HDBIJ0 HDINV0# HD46# RESERVED_19 NC_7

G35 M26 HDJ47 R13 B2

14 HDSTBPJ1 HDSTBP1# HD47# RESERVED_20 NC_8

H33 C33 HDJ48 CK_PE_100M_P_GMCH B12 R178 5 OF 7

14 HDSTBNJ1 HDSTBN1# HD48# 8 CK_PE_100M_P_GMCH GCLKP

C HDBIJ1 J33 C35 HDJ49 CK_PE_100M_N_GMCH B13 AC11 GMCH_EXP_COMP 24.9 C

14 HDBIJ1 HDINV1# LE82G31 HD49# 8 CK_PE_100M_N_GMCH GCLKN* EXP_COMPO 1D25V_MCH

G27 E41 HDJ50 AC12 +/-1%

14 HDSTBPJ2 HDSTBP2# HD50# HDJ51 EXP_COMPI

14 HDSTBNJ2 H27 B41 G17 LE82G31

HDBIJ2 G29 HDSTBN2# HD51# D42 HDJ52 23 SDVO_CTRLDATA

E17 SDVO_CTRLDATA width 10 mils, spacing 6 mils at breakout

14 HDBIJ2

*

HDINV2# HD52# HDJ53 23 SDVO_CTRLCLK SDVO_CTRLCLK 2 OF 7 bga1226_1h25 ICH_SYNCJ R148 1K

B38 C40 10 mils after that

14 HDSTBPJ3 HDSTBP3# HD53# HDJ54 Del R934,R935 0Ohm RES +/-5% r0402h4

D38 D35 LE82G31

14 HDSTBNJ3 HDBIJ3 HDSTBN3# HD54# HDJ55

14 HDBIJ3 E33 B40

HDINV3# HD55# HDJ56 bga1226_1h25 R200,R201,R205,R208,R209,R210 USE 0 OHM FOR 946PL.

C38

HD56# HDJ57 DUMMY R192,R194.

W40 D37

*

14 HADSJ HADS# HD57# HDJ58 PWRGD_3V

Y40 B33 R323 10K

14 HTRDYJ HTRDY# HD58# HDJ59 +/-5% Dummy

W41 D33

14 HDRDYJ

T43 HDRDY# HD59# C34 HDJ60

14 HDEFERJ HDEFER# HD60# HDJ61

Y43 B35

14 HITMJ

U42 HHITM# HD61# A32 HDJ62 1D25V_MCH

14 HITJ HHIT# HD62# HDJ63

V41 D32

14 HLOCKJ HLOCK# HD63#

AA42

****

14 HBR0J HBREQ0# HSWING DMI_RXP0

W42 B25 R163 4.7K +/-5%

14 HBNRJ HBNR# HSWING HRCOMP R150 1.3K REFSET

G39 D23

14 HBPRIJ HBPRI# HRCOMP HSCOMP DMI_RXP1 R171 4.7K +/-5% +/-1%

14 HDBSYJ

U40 C25

U41 HDBSY# HSCOMP D25 HSCOMPJ

14 HRSJ0 HRS0# HSCOMP# MCH_GTLREF DMI_RXP2 R172 4.7K +/-5%

AA41 D24

14 HRSJ1

U39 HRS1# HDVREF B24 placed close to GMCH within 500 mils

14 HRSJ2 HRS2# HACCVREF DMI_RXP3 R175 4.7K +/-5% 4 mils width

C31 R32 CK_200M_P_GMCH 8

14 HCPURSTJ HCPURST# HCLKP U32 6 mils spacing to static signals

HCLKN CK_200M_N_GMCH 8

12 mils spacing to toppling signals

1 OF 7

bga1226_1h25

FSB_VTT FSB_VTT COMP SIGNAL TERMINATION

*

R136 R138 49.9 HSCOMPJ

* 301 Resistor and Capacitor +/-1% r0402h4 C186

+/-1% next to each other. 2.7pF

B

* 50V, NPO, +/-0.25pF B

Dummy

*

R145 49.9 HSWING

*

+/-1% r0402h4 FSBSEL0 R401 10K BSEL0

*

R137 49.9 HSCOMP +/-5% 1D25V_MCH

*R135

100 Ohm

*

C178

10nF

+/-1% r0402h4

*

C185

2.7pF

+/-1% 25V, X7R, +/-10% 50V, NPO, +/-0.25pF FSB_VTT

Dummy

23 GMCH_EXP_EN_HDR

GMCH_EXP_EN_HDR *R194

1K

HSWING voltage should be 0.25*FSB_VTT +/-1%

10 mils width, 10 mils spacing R404 r0402h4

max. 3 inches long * 470 CL_VREF_MCH

4 mils width, 6 mils spacing in the breakout FSBSEL0 +/-5% JP1(P1 & P2)

8 FSBSEL0

4 mils width, 14 mils spacing after the breakout

max. 750 mils

JP1

*R196

392

*

C288

0.1uF

0.349V

routed on a single layer and matched within 50mils FSBSEL1 3 +/-1% 16V, Y5V, +80%/-20%

*

8 FSBSEL1 3 R402 10K BSEL1 r0402h4

2

HRCOMP R154 2 +/-5% FSBSEL1

1 Place close to VREF Pin

16.5 Ohm +/-1% FSBSEL2 1 Jumper

8 FSBSEL2

Reserved

Header_1X3

10 mils width, 7 mils spacing min. 4 mils width

max. 500 mils 10 mils spacing

*

GMCH_EXP_SLR

5 on 5 mils in breakout, max 250 mils 1D25V_MCH R132 1K 5 mils min. for max. of 300 mils in breakout

+/-5% r0402h4 JP2(P1 & P2)

ATX: 1 JP2

BTX: 0 3

*

3 2 R403 10K BSEL2

2 +/-5%FSBSEL2

1

1

FSB_VTT Jumper

Not used for CoreTM2 Duo and Wolfdale with G31 Chipset Header_1X3 Reserved

Del or not in G31

*

*R134 R131

100 Ohm +/-5%

+/-1%

0

MCH_GTLREF_CPU 14

*

A R144 MCH_GTLREF A

C171 10

* 1uF *R130

200 +/-1%

*

C187

220pF

+/-1% 50V, NPO, +/-5%

10V, Y5V, +80%/-20%

GTLREF voltage should be 0.63*VTT = 0.75V FOXCONN PCEG

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin Title

220pF caps should be placed near MCH pin BearLake-GMCH-1

place series resistor as close to divider

Size Document Number Rev

Resistor and Capacitor next to each other

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 16 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

19,20 M_MAA_A[14..0]

5

M_MAA_A0

M_MAA_A1

www.sp860.com

BA31

U12C

SMA_A0

U1MCH

4

SDQS_A0

AU4 M_DQS_A0

M_DQS_AJ0

M_DQS_A[7..0] 20

M_DQS_AJ[7..0] 20

3

QQ:453100829

21,22 M_MAA_B[14..0] M_MAA_B0

M_MAA_B1

M_MAA_B2

2

BB17

AY17

U12D

SMA_B0

SMA_B1

U1MCH

SDQS_B0

SDQS_B0#

AV6

AU5

M_DQS_B0

M_DQS_BJ0

M_DQM_B0

1

M_DQS_B[7..0] 22

M_DQS_BJ[7..0] 22

M_DQM_B[7..0] 22

BB25 AR3 M_DQM_A[7..0] 20 BA17 AR7 M_DATA_B[63..0] 22

M_MAA_A2 BA26 SMA_A1 SDQS_A0# AR2 M_DQM_A0 M_MAA_B3 BC16 SMA_B2 SDM_B0

SMA_A2 SDM_A0 M_DATA_A[63..0] 20 SMA_B3

M_MAA_A3 BA25 M_MAA_B4 AW15 AN7 M_DATA_B0

M_MAA_A4 SMA_A3 M_DATA_A0 M_MAA_B5 SMA_B4 SDQ_B0 M_DATA_B1

AY25 AR5 BA15 AN8

M_MAA_A5 SMA_A4 SDQ_A0 M_DATA_A1 M_MAA_B6 SMA_B5 SDQ_B1 M_DATA_B2

BA23 AR4 BB15 AW5

M_MAA_A6 SMA_A5 SDQ_A1 M_DATA_A2 M_MAA_B7 SMA_B6 SDQ_B2 M_DATA_B3

AY24 AV3 BA14 AW7

M_MAA_A7 SMA_A6 SDQ_A2 M_DATA_A3 M_MAA_B8 SMA_B7 SDQ_B3 M_DATA_B4

AY23 AV2 AY15 AN5

M_MAA_A8 SMA_A7 SDQ_A3 M_DATA_A4 M_MAA_B9 SMA_B8 SDQ_B4 M_DATA_B5

BB23 AP3 BB14 AN6

M_MAA_A9 SMA_A8 SDQ_A4 M_DATA_A5 M_MAA_B10 SMA_B9 SDQ_B5 M_DATA_B6

BA22 AP2 AW18 AN9

M_MAA_A10 SMA_A9 SDQ_A5 M_DATA_A6 M_MAA_B11 SMA_B10 SDQ_B6 M_DATA_B7

AY33 AU1 BB13 AU7

M_MAA_A11 SMA_A10 SDQ_A6 M_DATA_A7 M_MAA_B12 SMA_B11 SDQ_B7

D BB22 AV4 BA13 M_DQS_B[7..0] 22 D

M_MAA_A12 SMA_A11 SDQ_A7 M_MAA_B13 SMA_B12 M_DQS_B1

AW21 M_DQS_A[7..0] 20 AY29 AR12 M_DQS_BJ[7..0] 22

M_MAA_A13 AY38 SMA_A12 BB3 M_DQS_A1 M_MAA_B14 AY13 SMA_B13 SDQS_B1 AP12 M_DQS_BJ1

SMA_A13 SDQS_A1 M_DQS_AJ[7..0] 20 SMA_B14 SDQS_B1# M_DQM_B[7..0] 22

M_MAA_A14 BA21 BA4 M_DQS_AJ1 AW9 M_DQM_B1

SMA_A14 SDQS_A1# M_DQM_A[7..0] 20 SDM_B1 M_DATA_B[63..0] 22

BA2 M_DQM_A1 BA27

SDM_A1 M_DATA_A[63..0] 20 21,22 M_WE_BJ SWE_B#

BB34 AW29 AT11 M_DATA_B8

19,20 M_WE_AJ SWE_A# M_DATA_A8 21,22 M_CAS_BJ SCAS_B# SDQ_B8 M_DATA_B9

AY35 AY2 AW26 AU11

19,20 M_CAS_AJ SCAS_A# SDQ_A8 M_DATA_A9 21,22 M_RAS_BJ SRAS_B# SDQ_B9 M_DATA_B10

BB33 AY3 AP13

19,20 M_RAS_AJ SRAS_A# SDQ_A9 BB5 M_DATA_A10 21,22 M_BS_B[2..0] M_BS_B0 AY19 SDQ_B10 AR13 M_DATA_B11

M_BS_A0 SDQ_A10 M_DATA_A11 M_BS_B1 SBS_B0 SDQ_B11 M_DATA_B12

BA33 AY6 BA18 AR11

M_BS_A1 SBS_A0 SDQ_A11 M_DATA_A12 M_BS_B2 SBS_B1 SDQ_B12 M_DATA_B13

AW32 AW2 BC12 AU9

M_BS_A2 SBS_A1 SDQ_A12 M_DATA_A13 SBS_B2 SDQ_B13 M_DATA_B14

BB21 AW3 AV12

SBS_A2 SDQ_A13 BA5 M_DATA_A14 BB27 SDQ_B14 AU12 M_DATA_B15

19,20 M_BS_A[2..0] SDQ_A14 M_DATA_A15 21,22 M_SCS_B0J SCS_B0# SDQ_B15

AW35 BB4 BB30 M_DQS_B[7..0] 22

19,20 M_SCS_A0J SCS_A0# SDQ_A15 21,22 M_SCS_B1J SCS_B1# M_DQS_B2

BA35 M_DQS_A[7..0] 20 AY27 AP15 M_DQS_BJ[7..0] 22

19,20 M_SCS_A1J

BA34 SCS_A1# BB9 M_DQS_A2 AY31 SCS_B2# SDQS_B2 AR15 M_DQS_BJ2

SCS_A2# SDQS_A2 M_DQS_AJ[7..0] 20 SCS_B3# SDQS_B2# M_DQM_B[7..0] 22

BB38 BA9 M_DQS_AJ2 AW13 M_DQM_B2

SCS_A3# SDQS_A2# M_DQM_A[7..0] 20 21,22 M_SCKE_B[1..0] SDM_B2 M_DATA_B[63..0] 22

AY9 M_DQM_A2 M_SCKE_B0 AY12

19,20 M_SCKE_A[1..0] SDM_A2 M_DATA_A[63..0] 20 SCKE_B0

M_SCKE_A0 BC20 M_SCKE_B1 AW12 AU15 M_DATA_B16

M_SCKE_A1 SCKE_A0 M_DATA_A16 SCKE_B1 SDQ_B16 M_DATA_B17

AY20 AY7 BB11 AV13

SCKE_A1 SDQ_A16 M_DATA_A17 SCKE_B2 SDQ_B17 M_DATA_B18

AY21 BC7 BA11 AU17

SCKE_A2 SDQ_A17 M_DATA_A18 21,22 M_ODT_B[1..0] M_ODT_B0 SCKE_B3 SDQ_B18 M_DATA_B19

BA19 AW11 BA29 AT17

SCKE_A3 SDQ_A18 M_DATA_A19 M_ODT_B1 SODT_B0 SDQ_B19 M_DATA_B20

AY11 BA30 AU13

19,20 M_ODT_A[1..0] M_ODT_A0 SDQ_A19 M_DATA_A20 SODT_B1 SDQ_B20 M_DATA_B21

AY37 BB6 BB29 AM13

M_ODT_A1 SODT_A0 SDQ_A20 M_DATA_A21 SODT_B2 SDQ_B21 M_DATA_B22

BA38 BA6 BB31 AV15

SODT_A1 SDQ_A21 M_DATA_A22 SODT_B3 SDQ_B22 M_DATA_B23

BB35 BA10 AW17

SODT_A2 SDQ_A22 M_DATA_A23 SDQ_B23

BA39 BB10 AV31 M_DQS_B[7..0] 22

SODT_A3 SDQ_A23 22 CK_M_200M_P_DDR0_B SCLK_B0 M_DQS_B3

M_DQS_A[7..0] 20 AW31 AT24 M_DQS_BJ[7..0] 22

AU31 AT20 M_DQS_A3 22 CK_M_200M_N_DDR0_B

AU27 SCLK_B0# SDQS_B3 AU26 M_DQS_BJ3

20 CK_M_200M_P_DDR0_A SCLK_A0 SDQS_A3 M_DQS_AJ[7..0] 20 22 CK_M_200M_P_DDR1_B SCLK_B1 SDQS_B3# M_DQM_B[7..0] 22

AR31 AU18 M_DQS_AJ3 AT27 AP23 M_DQM_B3

20 CK_M_200M_N_DDR0_A SCLK_A0# SDQS_A3# M_DQM_A[7..0] 20 22 CK_M_200M_N_DDR1_B SCLK_B1# SDM_B3 M_DATA_B[63..0] 22

AP27 AN18 M_DQM_A3 AV32

20 CK_M_200M_P_DDR1_A SCLK_A1 SDM_A3 M_DATA_A[63..0] 20 22 CK_M_200M_P_DDR2_B SCLK_B2

AN27 AT32 AV24 M_DATA_B24

20 CK_M_200M_N_DDR1_A SCLK_A1# M_DATA_A24 22 CK_M_200M_N_DDR2_B SCLK_B2# SDQ_B24 M_DATA_B25

AV33 AT18 AU29 AT23

20 CK_M_200M_P_DDR2_A SCLK_A2 SDQ_A24 M_DATA_A25 SCLK_B3 SDQ_B25 M_DATA_B26

AW33 AR18 AR29 AT26

20 CK_M_200M_N_DDR2_A SCLK_A2# SDQ_A25 M_DATA_A26 SCLK_B3# SDQ_B26 M_DATA_B27

AP29 AU21 AV29 AP26

AP31 SCLK_A3 SDQ_A26 AT21 M_DATA_A27 AW27 SCLK_B4 SDQ_B27 AU23 M_DATA_B28

SCLK_A3# SDQ_A27 M_DATA_A28 SCLK_B4# SDQ_B28 M_DATA_B29

AM26 AP17 AN33 AW23

SCLK_A4 SDQ_A28 M_DATA_A29 SCLK_B5 SDQ_B29 M_DATA_B30

AM27 AN17 AP32 AR24

C AT33 SCLK_A4# SDQ_A29 AP20 M_DATA_A30 SCLK_B5# SDQ_B30 AN26 M_DATA_B31 C

SCLK_A5 SDQ_A30 M_DATA_A31 SDQ_B31

AU33 AV20

SCLK_A5# SDQ_A31 M_DQS_B[7..0] 22

AW39 M_DQS_B4

M_DQS_A[7..0] 20 SDQS_B4 M_DQS_BJ[7..0] 22

AR41 M_DQS_A4 AU39 M_DQS_BJ4

SDQS_A4 M_DQS_AJ[7..0] 20 SDQS_B4# M_DQM_B[7..0] 22

AR40 M_DQS_AJ4 AU37 M_DQM_B4

SDQS_A4# M_DQM_A[7..0] 20 SDM_B4 M_DATA_B[63..0] 22

AU43 M_DQM_A4

SDM_A4 M_DATA_A[63..0] 20

AW37 M_DATA_B32

M_DATA_A32 SDQ_B32 M_DATA_B33

AV42 AV38

SDQ_A32 M_DATA_A33 SDQ_B33 M_DATA_B34

AU40 BB2 AN36

SDQ_A33 M_DATA_A34 RESERVED_1 SDQ_B34 M_DATA_B35

AP42 AW42 AN37

SDQ_A34 M_DATA_A35 RESERVED_2 SDQ_B35 M_DATA_B36

AN39 AN32 AU35

SDQ_A35 AV40 M_DATA_A36 AM31 RESERVED_3 SDQ_B36 AR35 M_DATA_B37

SDQ_A36 M_DATA_A37 RESERVED_4 SDQ_B37 M_DATA_B38

AV41 AG32 AN35

SDQ_A37 AR42 M_DATA_A38 AF32 RESERVED_5 SDQ_B38 AR37 M_DATA_B39

SDQ_A38 M_DATA_A39 TP_MCH_AP21 RESERVED_6 SDQ_B39

AP41 AP21

SDQ_A39 TP51 SM_SLEWIN0 M_DQS_B[7..0] 22

TP_MCH_AA39 AA39 AL35 M_DQS_B5

M_DQS_A[7..0] 20 TP52 SM_SLEWIN1 SDQS_B5 M_DQS_BJ[7..0] 22

AL41 M_DQS_A5 AL34 M_DQS_BJ5

SDQS_A5 M_DQS_AJ[7..0] 20 SDQS_B5# M_DQM_B[7..0] 22

AL40 M_DQS_AJ5 AM37 M_DQM_B5

SDQS_A5# M_DQM_A[7..0] 20 SDM_B5 M_DATA_B[63..0] 22

AM43 M_DQM_A5

SDM_A5 M_DATA_A[63..0] 20

AM35 M_DATA_B40

M_DATA_A40 SDQ_B40 M_DATA_B41

AN41 AM38

SDQ_A40 AM39 M_DATA_A41 SDQ_B41 AJ34 M_DATA_B42

SDQ_A41 M_DATA_A42 SDQ_B42 M_DATA_B43

AK42 AL38

SDQ_A42 AK41 M_DATA_A43 SDQ_B43 AR39 M_DATA_B44

SDQ_A43 M_DATA_A44 SDQ_B44 M_DATA_B45

AN40 AM34

SDQ_A44 M_DATA_A45 SDQ_B45 M_DATA_B46

AN42 AL37

SDQ_A45 AL42 M_DATA_A46 SDQ_B46 AL32 M_DATA_B47

SDQ_A46 M_DATA_A47 SDQ_B47

AL39

SDQ_A47 M_DQS_B[7..0] 22

AG35 M_DQS_B6

M_DQS_A[7..0] 20 SDQS_B6 M_DQS_BJ[7..0] 22

AG42 M_DQS_A6 AG36 M_DQS_BJ6

SDQS_A6

SDQS_A6#

AG41 M_DQS_AJ6

M_DQM_A6

M_DQS_AJ[7..0] 20

M_DQM_A[7..0] 20

DDR_1 SDQS_B6#

SDM_B6

AG39 M_DQM_B6

M_DQM_B[7..0] 22

M_DATA_B[63..0] 22

AG40

SDM_A6 M_DATA_A[63..0] 20

AG38 M_DATA_B48

AJ40 M_DATA_A48 SDQ_B48 AJ38 M_DATA_B49

SDQ_A48 M_DATA_A49 SDQ_B49 M_DATA_B50

AH43 AF35

SDQ_A49 M_DATA_A50 SDQ_B50 M_DATA_B51

AF39 AF33

SDQ_A50 M_DATA_A51 SDQ_B51 M_DATA_B52

AE40 AJ37

SDQ_A51 AJ42 M_DATA_A52 SDQ_B52 AJ35 M_DATA_B53

B SDQ_A52 SDQ_B53 B

AJ41 M_DATA_A53 TP_MCH_AM21 AM21 AG33 M_DATA_B54

SDQ_A53 TP53 RESERVED_7 SDQ_B54

AF41 M_DATA_A54 AF34 M_DATA_B55

SDQ_A54 M_DATA_A55 DDR_GMCH_VREF SDQ_B55

AF42 AM6 M_DQS_B[7..0] 22

SDQ_A55 SVREF M_DQS_B7

AC36

M_DQS_A[7..0] 20 SDQS_B7 M_DQS_BJ[7..0] 22

AC42 M_DQS_A7 AC37 M_DQS_BJ7

DDR_0 SDQS_A7

SDQS_A7#

AC41 M_DQS_AJ7

M_DQS_AJ[7..0] 20

M_DQM_A[7..0] 20

SDQS_B7#

SDM_B7

AD38 M_DQM_B7

M_DQM_B[7..0] 22

M_DATA_B[63..0] 22

AC40 M_DQM_A7

SDM_A7 M_DATA_A[63..0] 20

AD36 M_DATA_B56

TP_MCH_AN21 AN21 AD40 M_DATA_A56 SRCOMP0 AN2 SDQ_B56 AC33 M_DATA_B57

TP54 RESERVED SDQ_A56 SRCOMP0 SDQ_B57

AD43 M_DATA_A57 SRCOMP1 AN3 AA34 M_DATA_B58

SDQ_A57 M_DATA_A58 SRCOMP2 SRCOMP1 SDQ_B58 M_DATA_B59

AB41 BB40 AA36

SDQ_A58 M_DATA_A59 SRCOMP3 SRCOMP2 SDQ_B59 M_DATA_B60

AA40 BA40 AD34

SDQ_A59 M_DATA_A60 DDR2 Compensation Group Signals SMRCOMPVOL SRCOMP3 SDQ_B60 M_DATA_B61

AE42 AM8 AF38

SDQ_A60 AE41 M_DATA_A61 SMRCOMPVOH AM10 SMRCOMPVOL SDQ_B61 AC34 M_DATA_B62

SDQ_A61 M_DATA_A62 SMRCOMPVOH SDQ_B62 M_DATA_B63

AC39 BB19 AA33

SDQ_A62 M_DATA_A63 R187 20 SRCOMP0 RESERVED SDQ_B63

AB42

SDQ_A63 +/-1% 4 OF 7

3 OF 7

1D8V_STR LE82G31 bga1226_1h25

LE82G31 bga1226_1h25

R181 20 SRCOMP1

C281 +/-1%

0.1uF

* 16V, Y5V, +80%/-20%

1D8V_STR 1D8V_STR 1D8V_STR

R221 20 SRCOMP2

+/-1% 1D8V_STR

C302 C297

* 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% *R180

1K 1D8V_STR

Dummy

+/-1%

r0402h4 R202 20 SRCOMP3

*R191

1K

+/-1%

SMRCOMPVOH +/-1% r0402h4

C279 DDR_GMCH_VREF

A

*R185

3.01K * 10nF

25V, X7R, +/-10%

A

+/-1%

r0402h4

*R195

1K

+/-1% *

C287

0.1uF

16V, Y5V, +80%/-20%

SMRCOMPVOL r0402h4

*R189

1K C275

+/-1% 10nF 5 mils width, 10 mils spacing, max 500 mils length for breakout region

r0402h4 * 25V, X7R, +/-10% Place CAP./RES. within 1" of GMCH package.

1D8V_STR: 10 mils width/10 mils spacing.

width 10 mils, spacing 10 mils

5 mils width/spacing minimum for max. of 300 mils FOXCONN PCEG

SMRCOMPVOH: 0.8 *VCCSM in GMCH break-out area

SMRCOMPVOL: 0.2 *VCCSM Placed close to GMCH pin Title

BearLake-GMCH-2

Size Document Number Rev

C G31M04 A

Date: Wednesday, September 12, 2007 Sheet 17 of 39

5 4 3 2 1

PDF created with pdfFactory trial version www.pdffactory.com

UI1_1

8

7

8

D 7

5

2

1 A

2

1

U12_1

FOXCONN

www.sp860.com D

5

4

1D25V_MCH

AJ12

AJ11

AJ10

3

VCC_1

VCC_2

U12F

VCC_81

VCC_172

VCC_173

VCC_174

VCC_82

AG25

AG24

AG23

AG22

AG21

AG20

1D25V_MCH

QQ:453100829 2

BC37

BC32

BC28

BC24

BC10

VSS_1

VSS_2

VSS_3

VSS_4

U12G

VSS_181

VSS_182

VSS_183

VSS_184

AF5

AF3

AF2

AF1

AD42

1

B 5C 6 AJ9 VCC_3 VCC_83 AG19 BC5 VSS_5 VSS_185 AD39

6 VCC_4 VCC_84 VSS_6 VSS_186

3 AJ8 AG18 BB7 AD37

4 B 3 Heatsink AJ7 VCC_5 VCC_85 AG17 AY41 VSS_7 VSS_187 AD35

4 AJ6 VCC_6 VCC_86 AG15 AY4 VSS_8 VSS_188 AD33

VCC_7 VCC_87 VSS_9 VSS_189

Heatsink AJ5 AG14 AW43 AD25

AJ4 VCC_8 VCC_88 AF26 AW41 VSS_10 VSS_190 AD23

VCC_9 VCC_89 VSS_11 VSS_191

AJ3 AF25 AW1 AD21

VCC_10 VCC_90 VSS_12 VSS_192

CLIP1N AJ2 AF24 AV37 AD19

VCC_11 VCC_91 VSS_13 VSS_193

CLIP2S CLIP4S 1 AH4 AV35 AC38

VCC_12 VSS_14 VSS_194

1 1 AH2 AF22 AV27 AC35

GND

VCC_13 VCC_93 VSS_15 VSS_195

POWER

2 AH1 AF20 AV23 AC24

VCC_14 VCC_94 VSS_16 VSS_196

2 2 AG13 AF18 AV21 AC22

Clip_2P VCC_15 VCC_95 VSS_17 VSS_197

AG12 AF17 AV17 AC20

D VCC_16 VCC_96 VSS_18 VSS_198 D

Clip_2P Clip_2P AG11 AF15 AV11 AC10

VCC_17 VCC_97 VSS_19 VSS_199

This is for ICH7 heatsink hook. For GMCH heatsink hook AG10

VCC_18 VCC_98

AF14 AV9

VSS_20 VSS_200

AC7

AG9 AE27 AV7 AC5

CLIP3N VCC_19 VCC_99 VSS_21 VSS_201

AG8 AE26 AU42 AB43

1 AG7 VCC_20 VCC_100 AE25 AU38 VSS_22 VSS_202 AB25

AG6 VCC_21 VCC_101 AE23 AU32 VSS_23 VSS_203 AB23

VCC_22 VCC_102 VSS_24 VSS_204

2 AG5 AE21 AU24 AB21

AG4 VCC_23 VCC_103 AE19 AU20 VSS_25 VSS_205 AB19

Clip_2P VCC_24 VCC_104 VSS_26 VSS_206

AG3 AE17 AU6 AB2

AG2 VCC_25 VCC_105 AD27 AU2 VSS_27 VSS_207 AB1

VCC_26 VCC_106 VSS_28 VSS_208

AF13 AD26 AT31 AA38

VCC_27 VCC_107 VSS_29 VSS_209

AF12 AD18 AT29 AA35

AF11 VCC_28 VCC_108 AD17 AT15 VSS_30 VSS_210 AA24

VCC_29 VCC_109 VSS_31 VSS_211

AD24 AD15 AT13 AA22

AD22 VCC_30 VCC_110 AD14 AT12 VSS_32 VSS_212 AA20

1D25V_MCH AD20 VCC_31 VCC_111 AC27 AR38 VSS_33 VSS_213 AA8

VCC_32 VCC_112 VSS_34 VSS_214

AC25 AC26 AR33 AA5

AC23 VCC_80 VCC_113 AC17 AR32 VSS_35 VSS_215 Y42

1D25V_MCHPCIE VCC_34 VCC_114 VSS_36 VSS_216

L27 AC21 AC15 AR27 Y37

0 AC19 VCC_35 VCC_115 AC14 AR26 VSS_37 VSS_217 Y35

VCC_36 VCC_116 VSS_38 VSS_218

C272 C268 EC48 1D25V_MCH AC13 AB27 AR23 Y33

1

VCC_37 VCC_117 VSS_39 VSS_219

* 10uF

* 0.1uF

16V, Y5V, +80%/-20%

* 220uF

6.3V, +/-20%

AC6

AB24 VCC_38 VCC_118

AB26

AB18

AR21

AR20 VSS_40 VSS_220

Y25

Y23

VCC_39 VCC_119 VSS_41 VSS_221

10V, Y5V, +80%/-20%

10uF C172

AB22 AB17 AR17 Y21

2

1

VCC_40 VCC_120 VSS_42 VSS_222

* AB20

AA25 VCC_41

VCC_42

VCC_121

VCC_122

AA27

AA26

AR9

AR6 VSS_43

VSS_44

VSS_223

VSS_224

Y19

Y10

AA23 AA17 AP43 Y7

2

AA21 VCC_43 VCC_123 AA15 AP24 VSS_45 VSS_225 Y5

VCC_44 VCC_124 VSS_46 VSS_226

AA19 AA14 AP18 Y1

AA13 VCC_45 VCC_125 Y27 AP1 VSS_47 VSS_227 W3

1D25V_MCH AA3 VCC_46 VCC_126 Y26 AN38 VSS_48 VSS_228 V43

VCC_47 VCC_127 VSS_49 VSS_229

Y24 Y18 AN31 V39

Y22 VCC_48 VCC_128 Y17 AN29 VSS_50 VSS_230 V37

VCC_49 VCC_129 VSS_51 VSS_231

Y20 Y15 AN24 V34

Y13 VCC_50 VCC_130 Y14 AN23 VSS_52 VSS_232 V32

Place in 1D25V_MCH_CL plane Y6 VCC_51 VCC_131 W27 AN20 VSS_53 VSS_233 V11

VCC_52 VCC_132 VSS_54 VSS_234

(less than 100 mils from the package) V13 W26 AN15 V8

VCC_53 VCC_133 VSS_55 VSS_235

V12 W25 AN13 V5

VCC_54 VCC_134 VSS_56 VSS_236

V10 W23 AN12 V2

VCC_55 VCC_135 VSS_57 VSS_237

V9 W21 AN11 U38

*

L22 270nH VCCA_HPLL U13 VCC_56 VCC_136 W19 AN4 VSS_58 VSS_238 U35

+/-20% C176 VCC_57 VCC_137 VSS_59 VSS_239

U10 W18 AM42 U8

1

VCC_58 VCC_138 VSS_60 VSS_240

* 2.2uF

6.3V, Y5V, +80%/-20%

U9

U6

VCC_59

VCC_60

VCC_139

VCC_140

W17

V27

AM40

AM36

VSS_61

VSS_62

VSS_241

VSS_242

U7

U5

U3 V26 AM33 T42

2

N12 VCC_61 VCC_141 V25 AM29 VSS_63 VSS_243 T1

VCC_62 VCC_142 VSS_64 VSS_244

N11 V24 AM24 R36

N9 VCC_63 VCC_143 V23 AM23 VSS_65 VSS_245 R33

VCC_64 VCC_144 VSS_66 VSS_246

1D8V_STR Connect ground sides of caps with traces to GND balls N8 V22 AM20 R31

*

L20 2.2uH VCCA_MPLL (less than 100 mils from the package) N6 VCC_65 VCC_145 V21 AM11 VSS_67 VSS_247 R11

C +/-20% VCC_66 VCC_146 VSS_68 VSS_248 C

N3 V20 AM9 R8

VCC_67 VCC_147 VSS_69 VSS_249

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

R129 1 L6 V19 AM7 R5

VCC_68 VCC_148 VSS_70 VSS_250

+/-5% J6 V18 AM4 R3

VCC_69 VCC_149 VSS_71 VSS_251

C306

C305

C304 J3 V17 AM2 P43

1

VCC_70 VCC_150 VSS_72 VSS_252

C170

* * * J2 V15 AM1 P30

1

VCC_71 VCC_151 VSS_73 VSS_253

R128 1

+/-5% * 10uF

10V, Y5V, +80%/-20%

G2

F11