Академический Документы

Профессиональный Документы

Культура Документы

Tarea 4 Oscar Mercado

Загружено:

javierone xporОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Tarea 4 Oscar Mercado

Загружено:

javierone xporАвторское право:

Доступные форматы

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

PROGRAMA ELECTRONICA DIGITAL

Presentado por :

OSCAR LUIS MERCADO BARRIOS

GRUPO: 243004_29

Tutor:

SANDRA MILENA GARCIA

FASE DE LA ESTRATEGIA:

Tarea 4- Análisis de aplicaciones con ctos combinacionales y secuenciales-1

Cartagena de indias, Colombia 7 de Mayo de 2020

INTRODUCCIÓN

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 1/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

Dentro del siguiente informe encontraremos el desarrollo de la tarea 4 de la

asignatura expuesta en la portada, donde trataremos la temática de diseño de

circuitos combinacionales y secuenciales.

Para diseñar un cronómetro de cuenta regresiva, tendremos que cumplir con las

siguientes fases:

• Investigar conceptos teóricos en el entorno de conocimiento de la Unidad 4.

• Resolver ejercicios con aplicaciones de circuitos digitales combinacionales y

secuenciales.

Al culminar las fases estaremos en la capacidad desarrollar el ejercicio propuesto y

dar por entendido la temática de la unidad 4.

Todas las implementaciones en VHDL se deben hacer utilizando el software Vivado.

La implementación se debe evidenciar en el informe con la impresión de pantalla de

la descripción de VHDL y el resultado de la simulación

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 2/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

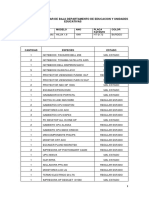

ACTIVIDADES A DESARROLLAR

Diseñar un cronómetro de cuenta regresiva. El valor inicial del contero será la edad

del estudiante. Por ejemplo, si el estudiante tiene 32 años, el cronómetro deberá

contar desde de 32 hasta 0 (32,31, 30,… 2, 1,0).

Se debe tener en cuenta que el reset (R*) del Registro conteo debe reiniciar el

conteo a su valor inicial, es decir, la edad del estudiante. Los otros reset deben poner

la salida a cero.

El funcionamiento del cronómetro es el siguiente:

El cronómetro tendrá un pulsador inicio que permitirá iniciar y detener el

conteo.

El cronómetro también tendrá un pulsador reinicio que llevará el cronómetro

a su conteo inicial, es decir, la edad del estudiante y detener el conteo.

La figura 1, muestra el diagrama de bloques del circuito a implementar.

Se debe hacer la implementación en VHDL del circuito propuesto.

Adicionalmente se debe simular para comprobar que efectivamente el circuito

funciona como se ha descrito

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 3/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

Una impresión de pantalla con la descripción en VHDL

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 4/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

SIMULACION DEL CRONOMETRO

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 5/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

ESTRUCTURA GENERAL

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−¿

−−Nombre :Oscar Luis Mercado

−−Documento :73.196.695

−−Fecha :07/05 /20 20

−−Proyecto :Cronometro

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−¿

library IEEE;

use IEEE . std ¿ ;

use IEEE . numeric std . all ;

use IEEE . std ¿ . all ;

entity Cronometro1 is

Port ¿

Salida: out STD ¿ (4 downto 0)

¿;

end Cronometro1 ;

architecture Behavioral of Cronometro1 is

signal D1 , Q1 , D 2, Q 2 , D 4 ,Q 4 , E 2 , R 3: STD LOGIC ;

signal D3 , Q 3 :STD ¿ (4 downto 0);

begin

process( clk)

begin

if clk ' event∧clk=' 1' then

if R 3=' 1' then

Q 3≤00000 ;

elsif Q 2=' 1 ' then

Q 3≤D 3 ;

end if ;

end if ;

end process ;

D 3≤11100 when Q3=0 else

Q 3−1 ;

process( clk)

begin

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 6/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

if clk ' event∧clk=' 1' then

if R 3=' 1' then

Q 2≤' 0 ' ;

elsif e 2=' 1 ' then

Q 2≤D 2;

end if ;

end if ;

end process ;

D 2≤NOT Q 2 ;

process( clk)

begin

if clk ' event∧clk=' 1' then

if R 3=' 1' then

Q 1≤' 0 ' ;

else

Q 1≤D 1;

end if ;

end if ;

end process ;

D 1≤inicio ;

E 2≤inicio∧(not Q 1) ;

process( clk)

begin

if clk ' event∧clk=' 1' then

if reinicio=' 1 ' then

Q 4≤' 0 ' ;

else

Q 4≤D 4 ;

end if ;

end if ;

end process ;

D 4≤reinicio ;

R 3≤reinicio∧(not Q 4 );

Salida≤Q 3 ;

end Behavioral ;

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 7/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

ENTORNO SIMULACION

library IEEE;

use IEEE . STD ¿ ;

entity Simulacionis

−−¿

end Simulacion ;

architecture Behavioral of Simulacion is

component Cronometro1

Port ¿

Salida: out STD ¿ (4 downto 0)

¿;

end component ;

−−Señales de las entradas

signal clk , inicio ,reinicio : STD LOGIC :=' 0 ' ;

−−Señales de salidas

signal Salida : STD¿ (4 downto 0);

constant PERIOD :time:=10 ns ;

begin

UO :Cronometro1 Port map¿

CLK =¿ CLK ,

INICIO=¿ INICIO ,

REINICIO=¿ REINICIO ,

Salida=¿ Salida

¿;

process begin

clk≤' 0' ;

wait for PERIOD /2 ;

clk≤' 1 ' ;

wait for PERIOD /2 ;

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 8/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

end process ;

process begin

−−−Estímulos de lasimulación wait for 100 ns ;

wait for 50 ns ;

reinicio≤' 1 ' ;

wait for 60 ns ;

reinicio≤' 0 ' ;

wait for 10 ns ;

inicio≤' 1 ' ;

wait for 200 ns ;

inicio≤' 0 ' ;

wait for 50 ns ;

inicio≤' 1 ' ;

wait for 20 ns ;

inicio≤' 0 ' ;

wait for 100 ns ;

inicio≤' 1 ' ;

wait for 20 ns ;

inicio≤' 0 ' ;

wait for 100 ns ;

reinicio≤' 1 ' ;

wait for 30 ns ;

reinicio≤' 0 ' ;

wait for 10 ns ;

wait ;

end process ;

end Behavioral ;

CONCLUSIONES

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 9/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

A través del desarrollo de este trabajo aprendimos aplicar circuitos combinacionales y

secuenciales a partir de un ejercicio planteado por medio del software Eda

PlayGround, adquiriendo la práctica suficiente en base al conocimiento de la unidad 4

para aplicarlos en diferentes ámbitos tanto laborales como estudiantiles.

Un circuito secuencial es en realidad una máquina de estados o maquinas generadora

de estados o etapas, que nos permite seguir con una forma dentro del circuito. Estos

sistemas al unirse con los sistemas combinacionales nos permiten realizar actividades

más complejas como la desarrollada en el trabajo culminado.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 10/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

Escuela de ciencias básicas tecnologías e Ingeniería

Programa Electrónica Digital. 243004_29

REFERENCIAS BIBLOGRAFICAS.

Muñoz, J. (2012). Introducción a los Sistemas Digitales: Un enfoque usando

Lenguajes de Descripción de Hardware. (Capítulos 2 y 3, pp. 19-66). Madrid.

Recuperado de https://openlibra.com/es/book/introduccion-a-los-sistemas-

digitales

Fajardo, C. (2016, diciembre 13), Una visión global al diseño digital. [Archivo de

video], Recuperado de https://youtu.be/Aj0klECFkZ4

Fajardo, C. (2017, julio 12), Introducción a VHDL. [Archivo de video],

Recuperado de https://youtu.be/X53K330jGTk

Fajardo, C. (2017, mayo 17), Instalación de Vivado - Software de Xilinx. [Archivo

de video], Recuperado de https://youtu.be/mkALe1BsKBA

Fajardo, C. (2017, junio 23), Actividad de reconocimiento: Hola mundo en

Vivado. [Archivo de video], Recuperado de https://youtu.be/jdocKPJ1f_g

Fajardo, C. (2017, Julio 13), Diseño de un circuito combi nacional - Suma de

Productos [Archivo de video]. Recuperado de https://youtu.be/ziPj9Yi-suc

Fajardo, C. (2017, Julio 13), Diseño Digital con Vivado: Detección de errores

[Archivo de video]. Recuperado de https://youtu.be/7MnDMs-ObmI

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD – www.unad.edu.co 11/11

PTU: www.unadvirtual.org / Docente diseñador de plantilla: Georffrey Acevedo.

Вам также может понравиться

- Aporte - Hernando - López - Fase 2Документ7 страницAporte - Hernando - López - Fase 2javierone xporОценок пока нет

- Manual de Usuario ODK Collect 5-10-15Документ27 страницManual de Usuario ODK Collect 5-10-15ERICK CHICONCULLOОценок пока нет

- Flowcode Arduino PDFДокумент54 страницыFlowcode Arduino PDFchidomendezОценок пока нет

- Guía de Actividades y Rúbrica de Evaluación - Tarea 1 - Reconocimiento de ConceptosДокумент10 страницGuía de Actividades y Rúbrica de Evaluación - Tarea 1 - Reconocimiento de Conceptosjavierone xporОценок пока нет

- Tarea 2 - Javier - TamaraДокумент7 страницTarea 2 - Javier - Tamarajavierone xporОценок пока нет

- Fase 1 - Javier - TamaraДокумент7 страницFase 1 - Javier - Tamarajavierone xporОценок пока нет

- Ficha Del Plan de Acción SolidariaДокумент1 страницаFicha Del Plan de Acción Solidariajavierone xporОценок пока нет

- Tarea 1 - Conceptos Previos de Control - Javier TamaraДокумент7 страницTarea 1 - Conceptos Previos de Control - Javier Tamarajavierone xporОценок пока нет

- PortadaДокумент2 страницыPortadajavierone xporОценок пока нет

- Javier TamaraДокумент21 страницаJavier Tamarajavierone xporОценок пока нет

- Fase4 Javier Tamara.Документ33 страницыFase4 Javier Tamara.javierone xporОценок пока нет

- Paso1 Grupo5 Javier TamaraДокумент9 страницPaso1 Grupo5 Javier Tamarajavierone xporОценок пока нет

- Ficha de Diagnostico SolidarioДокумент3 страницыFicha de Diagnostico Solidariojavierone xporОценок пока нет

- Javier TamaraДокумент4 страницыJavier Tamarajavierone xporОценок пока нет

- Fase6 Javier TamaraДокумент48 страницFase6 Javier Tamarajavierone xporОценок пока нет

- El Lugar Geométrico de Las Raíces Es Un Poderoso Método de Análisis y Diseño para La Estabilidad y Respuesta Transitoria de Un Sistema de ControlДокумент2 страницыEl Lugar Geométrico de Las Raíces Es Un Poderoso Método de Análisis y Diseño para La Estabilidad y Respuesta Transitoria de Un Sistema de Controljavierone xporОценок пока нет

- Fase 3 - MarcosNievesДокумент4 страницыFase 3 - MarcosNievesjavierone xporОценок пока нет

- Javier Tamara 203050 6 Fase4Документ12 страницJavier Tamara 203050 6 Fase4javierone xporОценок пока нет

- Javier Tamara Tarea3 Grupo11Документ8 страницJavier Tamara Tarea3 Grupo11javierone xporОценок пока нет

- Tarea2 JuanSanchez Grupo11Документ9 страницTarea2 JuanSanchez Grupo11javierone xporОценок пока нет

- Etapa 3 Mateo VargasДокумент5 страницEtapa 3 Mateo Vargasjavierone xporОценок пока нет

- TAREA 2 ROLAND ALARCON G11docxДокумент6 страницTAREA 2 ROLAND ALARCON G11docxjavierone xpor0% (1)

- El Lugar Geométrico de Las Raíces Es Un Poderoso Método de Análisis y Diseño para La Estabilidad y Respuesta Transitoria de Un Sistema de ControlДокумент2 страницыEl Lugar Geométrico de Las Raíces Es Un Poderoso Método de Análisis y Diseño para La Estabilidad y Respuesta Transitoria de Un Sistema de Controljavierone xporОценок пока нет

- Tarea2Modulación AnalogicaДокумент9 страницTarea2Modulación Analogicajavierone xporОценок пока нет

- Diapositivas EcuacionesДокумент2 страницыDiapositivas Ecuacionesjavierone xporОценок пока нет

- Topologias de RedДокумент11 страницTopologias de RedEdgard CAJACHAHUA ROJASОценок пока нет

- IE0308 GuiaExp1Документ3 страницыIE0308 GuiaExp1Bryan MendezОценок пока нет

- Líneas de TransmisiónДокумент5 страницLíneas de Transmisión7978ORIONОценок пока нет

- Trabajo 1lazos de Control PF Y QVДокумент6 страницTrabajo 1lazos de Control PF Y QVwalter illescas100% (2)

- AporteДокумент7 страницAporteJUAN SEBASTIAN RUIZ SUAREZОценок пока нет

- Procedimientos de Diagnóstico de Fallas para El Sistema PLD: Plaza Vargas, KervinДокумент84 страницыProcedimientos de Diagnóstico de Fallas para El Sistema PLD: Plaza Vargas, KervinIsaac Galvez EscuderoОценок пока нет

- User Guide VERTIV - GXT RT+ (REV0 11-2019) (EU Spanish)Документ34 страницыUser Guide VERTIV - GXT RT+ (REV0 11-2019) (EU Spanish)saci.01022023Оценок пока нет

- 2.-Teoría de La Informacion - Chaile Unidad 4Документ18 страниц2.-Teoría de La Informacion - Chaile Unidad 4jose ruizОценок пока нет

- Configuración Punto Acceso EquipoДокумент27 страницConfiguración Punto Acceso EquipoitzelОценок пока нет

- BiosДокумент4 страницыBiosGüero TorresОценок пока нет

- Ejem Progra PLC S5 100UДокумент35 страницEjem Progra PLC S5 100UtoranagasanОценок пока нет

- Lab 1 Circuitos ElectricosДокумент8 страницLab 1 Circuitos ElectricosJuan Carlos Mendoza LimaОценок пока нет

- Repetidor Con DiagnosticoДокумент212 страницRepetidor Con Diagnosticopercu_mwОценок пока нет

- Tic - ThaliaДокумент10 страницTic - ThaliaMaick Baldeon SalazarОценок пока нет

- Testo 816-1 PDFДокумент2 страницыTesto 816-1 PDFronny25Оценок пока нет

- Práctica 1 y 2 Lab MicroondasIДокумент26 страницPráctica 1 y 2 Lab MicroondasIJhonAponteОценок пока нет

- Componentes Basicos 2Документ5 страницComponentes Basicos 2Mauricio CaballeroОценок пока нет

- Ficha Tecnica Toxirae Pro LelДокумент2 страницыFicha Tecnica Toxirae Pro LelJunior TorrejónОценок пока нет

- La Tecnología MMDSДокумент5 страницLa Tecnología MMDSSandy MoralesОценок пока нет

- Tipos Cable de Red y Categorías de Cables de Red - Apuntesjulio PDFДокумент13 страницTipos Cable de Red y Categorías de Cables de Red - Apuntesjulio PDFAlexis Lara MenesesОценок пока нет

- Preguntero Sistemas Informáticos 1Документ14 страницPreguntero Sistemas Informáticos 1Nidia Beatriz SperaОценок пока нет

- Instrumentacion IndustrialДокумент13 страницInstrumentacion Industrialjuli sanchezОценок пока нет

- Bienes Dados de Baja PDFДокумент8 страницBienes Dados de Baja PDFLuis Fernando Cid FrizОценок пока нет

- Manual Booq Avant EsДокумент52 страницыManual Booq Avant EsNuria PinillaОценок пока нет

- CON EL TesterДокумент52 страницыCON EL TesterJimmyОценок пока нет

- La Computadora Hoy en Dia Se Ha Vuelto Una Herramienta Indispensable en Muchas AreasДокумент5 страницLa Computadora Hoy en Dia Se Ha Vuelto Una Herramienta Indispensable en Muchas AreasOmar AboujokhОценок пока нет

- Componentes de Un Equipo de ComputoДокумент3 страницыComponentes de Un Equipo de ComputoAndreycb28Оценок пока нет

- Equipo de Diagnóstico - XPLORE-NEXIQ - HelPCДокумент7 страницEquipo de Diagnóstico - XPLORE-NEXIQ - HelPCJMWIN32Оценок пока нет