Академический Документы

Профессиональный Документы

Культура Документы

University of Technology Computer Engineering Department: Second Class 2018 / 2019 Ass. Lecturer Suhad Haddad

Загружено:

wisamОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

University of Technology Computer Engineering Department: Second Class 2018 / 2019 Ass. Lecturer Suhad Haddad

Загружено:

wisamАвторское право:

Доступные форматы

Second Class / 2018-2019 (First Subject) / Digital Electronics

University of Technology

Computer Engineering Department

Second Class

2018 / 2019

Ass. Lecturer Suhad Haddad

Integrated Circuit Technologies

© Ass. Lecturer // Suhad Haddad Page 1

Second Class / 2018-2019 (First Subject) / Digital Electronics

TTL Characteristics

References:-

1- Digital Design / (4th edition) / Morris Mano & Michael Ciletti.

2- Digital Fundamentals / ( 9th edition ) / Thomas L. Floyd

3- Electronic Devices and Circuit Theory/Robert Boylestad, Louis

Nashelsky.

1-Introduction:-

The growing popularity of digital circuits is due in part to the

availability of inexpensive integrated circuits (ICs). Manufacturers

have developed many families of digital ICs-groups that can be used

together in building a digital system. The ICs in a family are said to be

compatible, and they can be easily connected. Digital ICs can be

categorized as either bipolar or unipolar. Bipolar digital ICs are

fabricated from parts comparable to discrete bipolar transistors, diodes,

and resistors. The TTL (transistor-transistor logic) family is the most

popular of the ICs using the bipolar technology.

Unipolar digital ICs are fabricated from parts comparable to

insulated-gate field-effect transistors (IGFETs). The CMOS

(complementary-metal-oxide semiconductor) family is a widely used

group of ICs based on the metal-oxide semiconductor (MOS)

technology.

A bipolar junction transistor (BIT) can be either an npn or a pnp

junction transistor. In contrast, the field-erect transistor (FET) is said to

be unipolar. The operation of a bipolar transistor depends on the flow

© Ass. Lecturer // Suhad Haddad Page 2

Second Class / 2018-2019 (First Subject) / Digital Electronics

of two types of carriers: electrons and holes. The operation of a

unipolar transistor depends on the flow of only one type of majority

carrier, which may be electrons (in an n-channel transistor) or holes (in

a p-channel transistor).

Main Logic Families

Most digital systems are designed by combining various logic

functions discussed in digital electronics.

All these logic circuits are available in IC modules and are divided

into many families. Each family is classified by abbreviations which

indicate the type of logic circuit used. For example, RTL means

resistor-transistor logic. We will discuss the following seven transistor

logic families although the first two are, at present, of historic interest

only.

1. Resistance-transistor logic (RTL): it was the first family group of

logic circuits to be developed and packaged in IC form in early 1960s;

2. Diode-transistor logic (DLT): It followed RTL in late 1960s;

3. Transistor-transistor logic (TTL) OR (T2L): was introduced in the

early 1970 s;

4. Schottky TTL: was introduced to improve the speed of TTL;

5. Emitter-coupled logic (ECL): It is fastest logic line currently

available;

6. Integrated-injection logic (I2L): It is one of the latest of the bipolar

types of logic;

7. Complementary metal-oxide semiconductor (CMOS): It has the

lowest power dissipation of the currently-available logic circuits.

The various logic families discussed above posses different

characteristics as detailed below.

© Ass. Lecturer // Suhad Haddad Page 3

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (1):- Example of Vcc and ground connection and distribution in an IC

package .Other pin connections are omitted for simplicity.

2- Basic definition:-

Integrated circuits are sometimes grouped by manufacturers as to

their circuit complexity. Circuit complexity of ICs is defined as

follows:

1. SSI (small-scale integration ):

Number of gates: less than 12

Typical digital devices: gates and flip-flops

2. MSI (medium-scale integration):

Number of gates: 12 to 99

© Ass. Lecturer // Suhad Haddad Page 4

Second Class / 2018-2019 (First Subject) / Digital Electronics

Typical digital devices: adders, counters, decoders, encoders,

multiplexers, and demultiplexers, registers

3. LSI (large-scale integration ):

Number of gates: 100 to 9999

Typical digital devices: digital clocks, smaller memory chips,

calculators

4. VLSI ( very -1arge-scale integration ):

Number of gates: 10,000 to 99,999

Typical digital devices: microprocessors, larger memory chips,

advanced calculators

5. ULSI (ultra-large-scale integration):

Number of gates: over 100,000

Typical digital devices: advanced microprocessors

The basic circuit in each IC digital logic family is a NAND or NOR

gate. This basic circuit is the primary building block from which all

other, more complex digital components are obtained. The statement

of NAND gate and NOR gate is shown below:-

© Ass. Lecturer // Suhad Haddad Page 5

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (2):- positive –logic NAND gate

Figure (3):- positive –logic NOR gate

All TTL series are available in SSI components and in more

complex forms, such as MSI and LSI components. The differences in

the TTL series are not in the digital logic that they perform, but rather

in the internal construction of the basic NAND gate. In any case, TTL

gates in all the available series come in three different types of output

configuration:

1. Totem-pole output.

2. Open-collector output.

3. Three-state (or tristate) output

DC Supply Voltage

© Ass. Lecturer // Suhad Haddad Page 6

Second Class / 2018-2019 (First Subject) / Digital Electronics

The voltage used to represent a 1 and a 0 called logic levels. One

voltage level represents a HIGH and another voltage level represents a

LOW. The both can be between a specified minimum and maximum

level. There can be no overlap between the accepted range of HIGH

levels and LOW levels.

Figure (4) illustrates the general range of LOWs and HIGHs for digital

circuit.

Figure (4):- logic level ranges of voltage for digital circuit

The variable VH (max) represents the maximum HIGH voltage value,

and VH (min) represent the minimum HIGH voltage value.

The maximum LOW voltage value is represented by VL (max), and the

minimum LOW voltage value is represented by VL (min). And the

voltage value between VL (max) and VH (min) are unacceptable for proper

operation.

The HIGH values for a certain type of digital circuit called CMOS

may range from 2V to 3.3V and the LOW values may range from

0V to 0.8V.

© Ass. Lecturer // Suhad Haddad Page 7

Second Class / 2018-2019 (First Subject) / Digital Electronics

For example, if a voltage of 2.5 V is applied, the circuit will accept

it as a HIGH or binary 1.

If a voltage of 0.5V is applied, the circuit will accept it as a LOW or

binary 0.

For this type of circuit, voltages between 0.8V and 2V are

unacceptable.

There are four different logic-level: VIL , VIH, VOL and VOH. As shown

below.

Figure (5):- Input and output logic levels for CMOS

© Ass. Lecturer // Suhad Haddad Page 8

Second Class / 2018-2019 (First Subject) / Digital Electronics

The input and output logic levels for TTL are given in figure (6).Just

as for CMOS; there are four different logic level specifications.

Figure (6):- Input and output logic levels for TTL

Basic Operational Characteristics and Parameters:-

When you work with digital ICs, you should be familiar not only

with their logical operation but also with such operational properties as

voltage levels, noise immunity, power dissipation, fan-out, and

propagation delay time. In this section, the practical aspects of these

properties are discussed.

© Ass. Lecturer // Suhad Haddad Page 9

Second Class / 2018-2019 (First Subject) / Digital Electronics

1- Noise immunity: -

Noise is unwanted voltage that is induced in electrical circuits

and can present a threat to the proper operation of the circuit.

Wires and other conductors within a system can pick up stray high-

frequency electromagnetic radiation from adjacent conductors in

which currents are changing rapidly or from many other sources

external to the system, also, power-line voltage fluctuation is a form of

low-frequency noise.

In order not to be adversely affected by noise, a logic circuit must

have a certain amount of noise immunity .this is the ability to tolerate

a certain amount of unwanted voltage fluctuation on its inputs without

changing its output state. For example, if noise voltage causes the

input of a 5V CMOS gate to drop below 3.5V in the HIGH state, the

input is in the un allowed region and operation is unpredictable. thus ,

the gate may interpret the fluctuation below 3.5V as a LOW level, as

shown in figure (7-a) .similarly ,if noise causes a gate input to go

above 1.5V in the LOW state, an uncertain condition is created ,as

shown in (7-B).

Figure (7-a-b):- illustration of the effects of input noise on gate operation

© Ass. Lecturer // Suhad Haddad Page 10

Second Class / 2018-2019 (First Subject) / Digital Electronics

1-2 Noise Margin: -

A measure of a circuit's noise immunity is called the noise margin,

which is expressed in volts. There are two values of noise margin

specified for a given logic circuit ,the HIGH -level noise margin (VNH)

and the LOW-level noise margin (VNL).these parameters are defined by

the following equations:-

VNH = VOH (min) – VIH (min)

VNL = VIL (max) - VOL (max)

Sometimes you will see the noise margin expressed as a percentage of

VCC .from the equation, VNH is the difference between the lowest

possible HIGH output from a driving gate (V OH (min) ) and the lowest

possible HIGH input that the load gate can tolerate (VIH (min) ) .

Noise margin, VNL ,is the difference between the maximum possible

LOW input that a gate can tolerate (V IL (max) ) and the maximum

possible LOW output of the driving gate ( VOL (max) ), noise margin are

illustrated in figure (8) .

Figure (8):- illustration of noise margin, values are for 5V CMOS, but the

principle applies to any logic family

© Ass. Lecturer // Suhad Haddad Page 11

Second Class / 2018-2019 (First Subject) / Digital Electronics

© Ass. Lecturer // Suhad Haddad Page 12

Second Class / 2018-2019 (First Subject) / Digital Electronics

2- Power Dissipation:-

A logic gate draws current from the DC supply voltage source, as

indicated in figure(9) .when the gate is in the HIGH output state ,an

amount of current designated by ICCH is drown, and in the LOW output

state ,a different amount of current,ICCL, is drown.

LOW

Figure (9):- Currents from the dc supply, conventional current direction is shown,

electron flow notation is opposite

As an example, if ICCH is specified as 1.5 mA when VCC is 5V and if the

gate is in a static (no changing) HIGH output state, the power

dissipation (PD) of the gate is

PD = VCC ICCH = (5V) (1.5mA) =7.5 mW

When a gate is pulsed, its output switches back and forth between

HIGH and LOW, and the amount of supply current varies between I CCH

and ICCL. The average power dissipation depends on the duty cycle and

is usually specified for a duty cycle of 50%. When the duty cycle is

50%, the output is HIGH half the time and LOW the other half. The

average supply current is therefore:-

ICCH + ICCL

ICC = 2

© Ass. Lecturer // Suhad Haddad Page 13

Second Class / 2018-2019 (First Subject) / Digital Electronics

The average power dissipation is

PD = VCC ICC

Power dissipation in a TTL circuit is essentially constant over its

range of operating frequencies. Power dissipation in CMOS, however,

is frequency dependent .it is extremely low under static (dc) conditions

and increases as the frequency increases. These characteristic are

shown in the general curves of figure (10).

Figure (10):- Power –versus- frequency curves for TTL and CMOS

© Ass. Lecturer // Suhad Haddad Page 14

Second Class / 2018-2019 (First Subject) / Digital Electronics

3- Propagation Delay Time:-

When a signal passes (propagates) through a logic circuit, it always

experiences a time delay, as illustrated in figure(11) .A change in the

output level always occurs a short time ,called the propagation delay

time, later than the change in the input level that caused it.

Figure (11):- A basic illustration of propagation delay time

There are two propagation delay times specified for logic gates:-

1. tPHL: The time between a designated point on the input pulse and

the corresponding point on the output pulse when the output is

changing from HIGH to LOW.

2. tPLH: The time between a designated point on the input pulse and

the corresponding point on the output pulse when the output is

changing from LOW to HIGH.

These propagation delay times are illustrated in figure (12), with the

50% points on the pulse edges used as references.

© Ass. Lecturer // Suhad Haddad Page 15

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (12):- Propagation delay times

The propagation delay time of a gate limits the frequency at which it

can be operated .The greater the propagation delay time, the lower

the maximum frequency .Thus, a higher-speed circuit is one that has

a smaller propagation delay time .For example, a gate with a delay of

3ns is faster than one with a 10ns delay.

4- Speed-Power Products:-

The speed –power product provides a basis for the comparison of

logic circuits when both propagation delay time and power dissipation

are important consideration in the selection of the type of logic to be

used in a certain application. The lower the speed-power product, the

batter. The unit of speed-power product is the picojoule (pJ).

For example; HCMOS has a speed –power product of 1.2pJ at

100 kHz while LSTTL has a value of 22pJ.

5- Loading and Fan-Out:-

When the output of logic is connected to one more inputs of other

gates, a load on the driving gate is created, as shown in figure (13).

© Ass. Lecturer // Suhad Haddad Page 16

Second Class / 2018-2019 (First Subject) / Digital Electronics

There is a limit to the number of load gate inputs that a given gate

can drive. This limit is called the fan-out of the gate.

Figure (13):- Loading a gate output with gate inputs

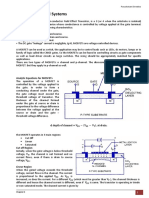

1- CMOS loading: - Loading in CMOS differs from that in TTL,

because the type of transistors used in CMOS logic present a

predominantly capacitive load to the driving gate, as illustrated in

figure (13). In this case, the limitations are the charging and

discharging times associated with the output resistance of the

driving gate and the input capacitance of the load gate .when the

output of the driving gate is HIGH, the input capacitance of the load

gate is charging through the output resistance of the driving gate.

When the output of the driving gate is LOW, the capacitance is

discharging, as shown in figure (14).

Figure (14):- Capacitive loading of a CMOS gate

© Ass. Lecturer // Suhad Haddad Page 17

Second Class / 2018-2019 (First Subject) / Digital Electronics

When more load gate inputs are added to the driving gate output, the

total capacitance increases because the input capacitances effectively

appear in parallel. This increase in capacitance will increase the

charging and discharging times, thus reducing the maximum

frequency at which the gate can be operated.Therefore, the fan-out

of a CMOS gate depends on the frequency of operation. The fewer

the load gate inputs, the greater the maximum frequency.

2- TTL Loading :- A TTL driving gate sources current to a load gate

input in the HIGH state ( IIH ) and sinks current from the load gate in

the LOW state (IIL) .Current sourcing and Current sinking are

illustrated in simplified form in figure(15),where the resistors

represent the internal input and output resistance of the gate for the

two conditions.

Figure (15):- Basic illustration of current sourcing and current sinking in logic

gates

As more load gates are connected to the driving gate, the loading on

the driving gate increases. The total source current increases with each

load input that is added, as illustrated in figure (16) .As this current

increase, the internal voltage drop of the driving gate increases,

causing the output VOH to decrease. If an excessive number of load

© Ass. Lecturer // Suhad Haddad Page 18

Second Class / 2018-2019 (First Subject) / Digital Electronics

gate inputs are connected,VOH drops below VOH(min) , and the HIGH-

level noise margin is reduced, thus compromising the circuit operation.

Also, as the total source current increases, the power dissipation of the

driving gate increases.

Figure (16):- HIGH-state TTL loading

The fan-out is the maximum number of load gate inputs that

can be connected without adversely affecting the specified

operational characteristics of the gate. For example, low-power

Schottky (LS) TTL has a fan-out of 20 unit loads. One input of the

same logic family as the driving gate is called a unit load.

The total sink current also increases with each load gate input that is

added, as shown in figure (17), as this current increase, the internal

voltage drop of the driving gate increases, causing VOL to increase. If

an excessive number of loads are added, VOL exceeds VOL(max) ,and the

Low-level noise margin is reduced.

In TTL, the current-sinking capability (LOW output state) is the

limiting factor in determining the fan-out.

© Ass. Lecturer // Suhad Haddad Page 19

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (17):- LOW-stage TTL loading

IoH

The fan- out of the gate is calculated from the ratio IIH

or

IOL

IIL

, for example, the standard TTL gates have the following

values for the currents:

© Ass. Lecturer // Suhad Haddad Page 20

Second Class / 2018-2019 (First Subject) / Digital Electronics

The TTL (Transistor Transistor Logic) Circuits:-

The bipolar junction transistor (BJT) is the active switching element

used in all TTL circuits. The figure (18) below shows the symbol for

an npn BJT with its three terminals: base, emitter, and collector. A BJT

has two junctions, the base – emitter junction and the base- collector

junction.

Figure (18):- The symbol for a BJT

The basic switching operation is as follows:

1- When the base is approximately (0.7 V) more positive than the

emitter.

2- Sufficient current is provided into the base; the transistor turns

ON and goes into saturation.

3- In saturation, the transistor ideally acts like a closed switch

between the collector and the emitter, as shown in the figure

below (19- a).

4- When the base is less than (0.7V) more positive than the emitter.

© Ass. Lecturer // Suhad Haddad Page 21

Second Class / 2018-2019 (First Subject) / Digital Electronics

5- The transistor turns OFF and becomes an open switch between

the collector and the emitter, as shown in the figure below (19-

b).

6- A HIGH on the base turns the transistor ON and makes it a

closed switch.

7- A LOW on the base turns the transistor OFF and makes it an

open switch.

Figure (19-a-b):- The ideal switching action of the BJT

Figure (20):- Typical npn Silicon Transistor Parameters

© Ass. Lecturer // Suhad Haddad Page 22

Second Class / 2018-2019 (First Subject) / Digital Electronics

1-TTL Inverter:-

The logic function of an inverter or any type of gate is always the

same, regardless of the type of circuit technology that is used. The

figure (21) below shows a standard TTL circuits for an inverter, which

is working as shown below:-

Figure (21):- Standard Symbol of TTL Inverter

1- Q1 is the input coupling transistor, and D1 is the input clamp

diode.

2- The combination of Q3 and Q4 forms the output circuit often

referred to as (a totem- pole) arrangement.

3- The Q2 is called a phase splitter transistor.

What is totem pole?

a. Addition of an active pull up circuit in the output of a

gate is called totem pole. Using Q3 and Q4 to achieve

this purpose

Why totem pole?

b. To increase the switching speed of the gate.

© Ass. Lecturer // Suhad Haddad Page 23

Second Class / 2018-2019 (First Subject) / Digital Electronics

Operation of the inverter:-

When the input is HIGH.

1- The base-emitter junction of Q1 is reversed biased. The base-

collector junction is forward biased.

2- This condition will permits current through R 1 and the base-

collector junction of Q1 into the base of Q2.

3- Thus driving Q2 into saturation.

4- As a result Q3 is turned ON by Q2, and its collector voltage,

which is the output, is near ground potential.

5- So there will be LOW output for a HIGH input.

6- The collector of Q2 is at a sufficiently low voltage level to keep

Q4 OFF.

When the input is LOW:-

1- The base –emitter junction of Q1 is forward biased, and the

base-collector junction is reverse biased.

2- There is current through R1 and the base-emitter junction of Q1

to the LOW input.

3- A LOW provides a path to ground for the current.

4- There is no current into the base of Q2, so it is OFF.

5- The collector of Q2 is HIGH thus turning Q4 ON.

6- A saturated Q4 provides a low –resistance path from VCC to the

output.

7- So there will be a HIGH on the output for a LOW on the input.

8- The emitter of Q2 is at ground potential, this will keep Q3 OFF.

9- Diode D1 in the Totem-pole TTL circuit prevents negative

spikes of voltage on the input from damaging Q1.

10- Diode D2 ensures that Q4 will turn off when Q2 is on (HIGH

input).

The operation of the TTL inverter for the two input states is

shown below figure (22).

© Ass. Lecturer // Suhad Haddad Page 24

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (22):-Operation of a TTL inverter

2- TTL NAND Gate:-

© Ass. Lecturer // Suhad Haddad Page 25

Second Class / 2018-2019 (First Subject) / Digital Electronics

In TTL some BJTs have multiple emitters. A 2-input TTL NAND

gate is shown in figure (23) below. Basically, it is the same as the

inverter circuit except for the additional input emitter of Q1.

Figure (23):- A TTL NAND gate circuit

In TTL technology multiple-emitter transistors are used for the input

devices. These multiple - emitter transistors can be compared to the

diode arrangement, as shown in figure (24) below:

Figure (24):-Diode equivalent of a TTL multiple-emitter transistor

Operation of TTL NAND gate:-

© Ass. Lecturer // Suhad Haddad Page 26

Second Class / 2018-2019 (First Subject) / Digital Electronics

1- A LOW an either input A or input B forward-biases the

respective diode and reverse-biases D3 (Q1 base-collector

junction).

2- This action keeps Q2 OFF and results in a HIGH output in the

same way as described for the TTL inverter.

3- A LOW on both inputs will do the same thing.

4- A HIGH on both inputs reverse-biases both input diodes and

forward-biases D3 (Q1 base-collector junction).

5- This action turns Q2 ON and results in a LOW output in the

same way as described for the TTL inverter.

6- The output is LOW only if all inputs are HIGH.

3-Open – Collector Gates:

The TTL gates described in the previous section all had the totem-

pole output circuits. Another type of output available in TTL integrated

circuits is the Open – Collector output .a standard TTL inverter with

an open-collector is shown below (25-a-b) .the other types of gates are

also available with open-collector outputs.

Figure (25-a-b):- TTL inverter with open-collector output

1- Notice that the output is the collector of transistor Q 3 with

nothing connected to it. Hence the name open collector.

2- In order to get proper HIGH and LOW logic levels out of the

circuit.

© Ass. Lecturer // Suhad Haddad Page 27

Second Class / 2018-2019 (First Subject) / Digital Electronics

3- An external pull-up resistor must be connected to VCC from the

collector of Q3, as shown in (b).

4- When Q3 is OFF, the output is pulled up to VCC through the

external resistor.

5- When Q3 is ON, the output is connected to near-ground through

the saturated transistor.

4-Tristate TTL Gates:-

The third type of TTL circuits is tristate TTL gate as shown in the

figure below:

Figure (26):-Basic Tristate inverter circuit

1- When the enable input is LOW.

2- So Q2 is OFF, and the output circuit operates as a normal

totem-pole configuration, in which the output state depends on

the input state.

3- When the enable input is HIGH, Q2 is ON.

4- There is thus a LOW on the second emitter of Q1, causing Q3

and Q5 to turn OFF.

5- Diode D1 is forward biased, casuing Q4 also to turn OFF.

6- When both totem-pole transistors are OFF, they are effectively

open.

© Ass. Lecturer // Suhad Haddad Page 28

Second Class / 2018-2019 (First Subject) / Digital Electronics

7- The output is completely disconnected from the internal

circuitry, as shown in figure (27) below.

Figure (27):-An equivalent circuit for tristate in the output in the high -2 state

5-Schottky TTL:-

Most TTL logic used today is some form of Schottky TTL, which

provides a faster switching time by incorporating Schottky diodes to

prevent the transistors from going into saturation, thereby decreasing

the time for a transistor to turn on or off. Figure (28) shows the

Schottky TTL NAND gate.

Figure (28):- Schottky TTL NAND gate

© Ass. Lecturer // Suhad Haddad Page 29

Second Class / 2018-2019 (First Subject) / Digital Electronics

CMOS Logic Family

It does not use bipolar transistors but just Enhancement- only

MOSFETs .there are two kinds of digital MOS circuits.

a) One which uses MOSFETs of one polarity either all of N-type

called NMOS or all of P-type called PMOS but not both on the

same chip.

b) The other which employs both N-type and P-type MOSFETs on

the same chip .it is called complementary MOS (CMOS).

The MOS family may be subdivided as under:-

Since FET requires small area, it is possible to fabricate a large

number of MOS circuits on a single small chip. Gating arrays with

thousands of gates and flip-flops are manufactured in standard

containers and are often used in IC memories and microprocessors.

Following are some of the advantages of MOS ICs over the bipolar

ICs (i.e. TTL).

1. The MOS IC is relatively simple and inexpensive to fabricate.

2. The MOS device size is small and it consumers less power.

Because of the small size, the MOS ICs can accommodate a

much large number of circuit elements on a single chip than

bipolar IC in the area of large scale integration. This makes

them especially well-suited for complex ICs such as

microprocessor, memory chips etc.

© Ass. Lecturer // Suhad Haddad Page 30

Second Class / 2018-2019 (First Subject) / Digital Electronics

3. MOS digital ICs normally do not use the IC resistor elements

that take up so much of the chip area or bipolar ICs.

4. The continuous improvement in MOS IC technology has led to

the devices that are faster than TTL device.

5. Consequently MOS devices (especially CMOS) have become

dominant in the SSI (small –scale integration) and MSI

(medium-scale integration) market.

6. The major disadvantage of MOS device is that they are

susceptible to static-electricity damage. Although we can

minimize it by adopting proper handling procedures, yet TTL is

still more durable for laboratory experimentation.

7. Field –effect transistor amplifiers provide an excellent voltage

gain with the added feature of high input impedance.

8. They are also considered low-power consumption

configurations with good frequency range and minimal size and

weight.

9. Both JFET and depletion MOSFET devices can be used to

design amplifiers having similar voltage gains.

10.The BJT is a current-controlled device and the FET is a

voltage –controlled device.

11.While the BJT had an amplification factor β (beta), the FET has

a transconductance factor, gm.

12.The FET can be used as a linear amplifier or as a digital device

in logic circuits.

13.The enhancement MOSFET is quite popular in digital

circuitry, especially in CMOS circuits that require very low

power consumption.

The field-effect transistor (FET) is a unipolar transistor, since its

operation depends on the flow of only one type of carrier. There are

two types of FETs: the junction field-effect transistor (JFET) and the

metal-oxide semiconductor (MOS). The former is used in linear

© Ass. Lecturer // Suhad Haddad Page 31

Second Class / 2018-2019 (First Subject) / Digital Electronics

circuits and the latter in digital circuits. MOS transistors can be

fabricated in less area than bipolar transistors.

The basic structure of the MOS transistor is shown in figure (29).

The p-channel MOS consists of a lightly doped substrate of n-type

silicon material. Two regions are heavily doped by diffusion with p-

type impurities to form the source and drain .The region between the

two p-type sections serves as the channel .The gate is a metal plate

separated from the channel by an insulated dielectric of silicon

dioxide. A negative voltage (with respect to the substrate) at the gate

terminal causes an induced electric field in the channel that attracts p-

type carriers (holes) from the substrate. As the magnitude of the

negative voltage on the gate increases, the region below the gate

accumulates more positive carriers, the conductivity increases, and

current can flow from source to drain, provided that a voltage

difference is maintained between these two terminals.

Figure (29) :- The basic structure of the MOS transistor

© Ass. Lecturer // Suhad Haddad Page 32

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (30-a-b-c):- Basic symbols and switching action of MOSFETs

© Ass. Lecturer // Suhad Haddad Page 33

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (31):- MOSFET structure

Complementary MOS:-

Complementary MOS (CMOS) circuits take advantage of the fact

that both n-channel and p-channel devices can be fabricated on the

same substrate. CMOS circuits consist of both types of MOS devices,

interconnected to form logic functions.

The basic circuit is the inverter, which consists of one p-channel

transistor and one n-channel transistor.

CMOS Inverter:-

Complementary MOS (CMOS) logic uses the MOSFET in

complementary pairs as its basic element .A complementary pairs

uses both p-channel and n-channel enhancement MOSFETs, as

shown in figure (32) which is the inverter circuit.

© Ass. Lecturer // Suhad Haddad Page 34

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (32):- A CMOS inverter circuit

The operation of inverter:-

1- When a HIGH is applied to the input, as shown in figure (33-a),

the p-channel MOSFET Q1 is OFF and the n-channel MOSFET

Q2 is ON.

2- This condition connects the output to ground through the ON

resistance of Q2, resulting in a LOW output.

3- When a LOW is applied to the input, as shown in (33-b).

4- Q1 is ON and Q2 is OFF.

5- This condition connects the output to ( +VDD ) ( dc supply

voltage ) through the ON resistance of Q1 , which resulting in a

HIGH output

© Ass. Lecturer // Suhad Haddad Page 35

Second Class / 2018-2019 (First Subject) / Digital Electronics

-:Operation of a CMOS inverter Figure (33-a-b)

CMOS NAND Gate:-

Figure (34) shows a CMOS NAND gate with two inputs. And the

operation of it is as follow:-

The operation of CMOS NAND:-

1- When both inputs are LOW Q1 and Q2 are ON, and Q3 and Q4

are OFF. The output is pulled HIGH through the on resistance

of Q1 and Q2 in parallel.

2- When input A is LOW and input B is HIGH Q1 and Q4 are ON,

and Q2 and Q3 are OFF. The output is pulled HIGH through the

low on resistance of Q1.

3- When input A is HIGH and input B is LOW, Q1 and Q4 are

OFF, and Q2 and Q3 are ON. The output is pulled HIGH

through the low on resistance of Q2.

4- Finally, when both inputs are HIGH, Q1 and Q2 are OFF, and

Q4 are ON. In this case, the output is pulled LOW through the

on resistance of Q3 and Q4 in series to ground.

© Ass. Lecturer // Suhad Haddad Page 36

Second Class / 2018-2019 (First Subject) / Digital Electronics

Figure (34):- A CMOS NAND gate circuit

CMOS NOR Gate:-

Figure (35) illustrated a CMOS NOR gate with two inputs .the

operation of it is as follow:-

1- When both inputs are LOW, Q1 and Q2 are ON, and Q3 and

Q4 are OFF, as a result, the output is pulled HIGH through

the on resistance of Q1 and Q2 in series.

2- When input A is LOW and input B is HIGH, Q1 and Q4 are

ON, and Q2 and Q3 are OFF. The output is pulled LOW

through the low on resistance of Q4 to ground.

3- When input A is HIGH and input B is LOW, Q1 and Q4 are

OFF, and Q2 and Q3 are ON. The output is pulled LOW

through the on resistance of Q3 to ground.

4- When both inputs are HIGH, Q1 and Q2 are OFF, and Q3 and

Q4 are ON. The output is pulled LOW through the on

resistance of Q3 and Q4 in parallel to ground

Figure (35):- A CMOS NOR gate circuit

Open –Drain Gates:-

1- The term open –drain means that the drain terminal of the output

transistor is unconnected and must be connected externally to

VDD through a load.

© Ass. Lecturer // Suhad Haddad Page 37

Second Class / 2018-2019 (First Subject) / Digital Electronics

2- An open –drain output circuit is a single n-channel MOSFET as

shown in figure (36).

3- An external pull-up resistor must be used. As shown in (b).In

order to produce a HIGH output state.

Figure (36):- Open –drain CMOS gates

Tristate CMOS Gates:-

Tristate output is available in both CMOS and TTL logic .The tristate

output combines the advantages of the totem-pole and open-collector

circuits. Its operation is as follow:-

1- The three output states are HIGH, LOW, and high-impedance

(high-Z).

2- When selected for normal logic level operation, as determined

by the state of the enable input, a tristate circuit operates in the

same way as a regular gate.

3- When a tristate circuit is selected for high-Z operation, the

output is effectively disconnected from the rest of the circuit by

internal circuitry .figure (37) illustrates the operation of a tristate

circuit.

4- The circuitry in tristate CMOS gate , shown in figure (38) ,

allow each of the output transistors Q 1 and Q2 to be turned OFF

at the same time ,thus disconnecting the output from the rest of

the circuit.

© Ass. Lecturer // Suhad Haddad Page 38

Second Class / 2018-2019 (First Subject) / Digital Electronics

5- When the enable input is LOW, the device is enabled for

normal logic operation.

6- When the enable input is HIGH, both Q1 and Q2 are OFF and

the circuit is in the high-Z state.

Figure (37):- The three states of a tristate circuit

Figure (38):- Atristate CMOS inverter

TTL Sub-families

The standard TTL family has the following advantages:-

1. Greater speed then DTL, and RTL.

2. Less noise immunity (0.4 V).

3. Average propagation delay per gate of 9ns.

4. Average power dissipation of 10mw.

5. A fan-out of 10 meaning one output can drive 10 other TTL inputs.

© Ass. Lecturer // Suhad Haddad Page 39

Second Class / 2018-2019 (First Subject) / Digital Electronics

Sub-families TTL have several sub-families having different speed

and lower dissipation characteristics as detailed below:

1. 74L00 series - the letter L standing for low power consumption. It

has an average power dissipation of 1 mW per gate but an average

propagation delay of 33 ns.

2. 74H00 series - the letter H standing for higher speed. It has a

propagation delay of 6 ns but average power dissipation of +23

mW/gate.

3. 74S00 - the letter S representing Schottky. It has the highest speed

because its average propagation delay is just 3 ns per gate. However,

its average power dissipation is 23 mW/ gate.

4. 74LS00 - It is called low-power Schottky TTL. It has an average

propagation delay of 9.5 ns and an average power dissipation of 2 mW.

5. 74AS00 series - the letter A representing advanced and S standing

for schottky. It is called advanced schottky TTL series. It is the fastest

TTL series.

6. 74ALS00 series - It is called Advanced Low-power Schottky TTL

series. The 74ALS series has the lower speed-power product and the

lowest gate power dissipation of all the TTL series.

7. 74F00 series - the letter F standing for Fast. This logic family uses

a new IC fabrication technique to reduce inter device capacitances to

achieve reduced propagation delays. It has a propagation delay of 3 ns

and a power consumption of 6 mW.

© Ass. Lecturer // Suhad Haddad Page 40

Second Class / 2018-2019 (First Subject) / Digital Electronics

.The table summarizes the important characteristics of the each of the TTL sub-families

© Ass. Lecturer // Suhad Haddad Page 41

Вам также может понравиться

- Digital Logic Families - Electronics TutorialДокумент7 страницDigital Logic Families - Electronics TutorialrakeluvОценок пока нет

- Digital Logic Families PDFДокумент49 страницDigital Logic Families PDFdineep90% (10)

- Experiment 1 Basic Logic Gates: ObjectivesДокумент10 страницExperiment 1 Basic Logic Gates: Objectivesasdf lkjОценок пока нет

- IC Logic FamilyДокумент4 страницыIC Logic FamilyAsheque IqbalОценок пока нет

- Ec1203 Digital ElectronicsДокумент20 страницEc1203 Digital ElectronicsSiva Prasad PadilamОценок пока нет

- Logic FamiliesДокумент49 страницLogic Familiesnour hijaziОценок пока нет

- Unit 3Документ46 страницUnit 3jana kОценок пока нет

- DEL Lab ManualДокумент68 страницDEL Lab ManualMohini AvatadeОценок пока нет

- IC Logic FamiliesДокумент5 страницIC Logic FamiliesAdarsha BhattaraiОценок пока нет

- Digital Integrared CircuitsДокумент27 страницDigital Integrared CircuitsDeepa RangasamyОценок пока нет

- TTL and CMOS FamiliesДокумент7 страницTTL and CMOS FamiliesFabian AvilaОценок пока нет

- Logic Families: Ics, Logical Operation Operational PropertiesДокумент33 страницыLogic Families: Ics, Logical Operation Operational Propertiesملكه الاحساسОценок пока нет

- Sonali Manual - 2nd August 2007Документ78 страницSonali Manual - 2nd August 2007sonalibhagwatkarОценок пока нет

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersДокумент20 страницGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuОценок пока нет

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersДокумент17 страницGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuОценок пока нет

- LOGIC GATES USING TRANSISTORS Digital TechniquesДокумент19 страницLOGIC GATES USING TRANSISTORS Digital Techniquesmohit moreОценок пока нет

- Digital Electronics Question BankДокумент34 страницыDigital Electronics Question Banksujithaa13100% (1)

- DEL ManualДокумент94 страницыDEL ManualAnand BongirОценок пока нет

- Electronic Digital CircuitsДокумент33 страницыElectronic Digital Circuitskathrin_jazz26Оценок пока нет

- Physics ProjectДокумент6 страницPhysics ProjectAdhithyaОценок пока нет

- Introduction To Integrated Digital Electron Nic SДокумент6 страницIntroduction To Integrated Digital Electron Nic SKarajá PtahОценок пока нет

- Chap. 8 Integrated-Circuit Logic Families: Digital IC Technology Has Advanced RapidlyДокумент45 страницChap. 8 Integrated-Circuit Logic Families: Digital IC Technology Has Advanced RapidlyAdimoolam MalayalathanОценок пока нет

- Logic Families in Digital Electronics - TTL, Cmos, and EclДокумент35 страницLogic Families in Digital Electronics - TTL, Cmos, and EclSameer A.AОценок пока нет

- 2 Marks ADICДокумент21 страница2 Marks ADICRavi TejaОценок пока нет

- Chapter 2Документ46 страницChapter 2roza.hemin1993Оценок пока нет

- Chapter 7 - IC Logic FamilyДокумент33 страницыChapter 7 - IC Logic Familyswathich6Оценок пока нет

- Verify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)Документ8 страницVerify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)sonalibhagwatkar100% (1)

- 4 Channel RF Remote Control DeviceДокумент90 страниц4 Channel RF Remote Control Devicepinku3Оценок пока нет

- IC ApplicationsДокумент164 страницыIC ApplicationsSam SelinОценок пока нет

- EI2353 DSDQbankДокумент24 страницыEI2353 DSDQbankRaja RockОценок пока нет

- Tutorial 4 PHY 340Документ3 страницыTutorial 4 PHY 340ammirulhafiz03Оценок пока нет

- Digital Systems: Digital IC Characteristics: Wen-Hung Liao, PH.DДокумент23 страницыDigital Systems: Digital IC Characteristics: Wen-Hung Liao, PH.DRohit jadhavОценок пока нет

- DLD Assignment PDFДокумент3 страницыDLD Assignment PDFMuhammad AliОценок пока нет

- Digital Logic FamiliesДокумент7 страницDigital Logic FamiliesGirdhar GopalОценок пока нет

- Logic Gate - Wikipedia The Free EncyclopediaДокумент11 страницLogic Gate - Wikipedia The Free EncyclopediaAkhil GargОценок пока нет

- Digital Logic FamiliesДокумент19 страницDigital Logic FamiliesThairu Muiruri100% (1)

- EEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsДокумент27 страницEEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsAlaa MalekОценок пока нет

- Logic Family Introduction and OverviewДокумент96 страницLogic Family Introduction and OverviewNikhil DattaОценок пока нет

- Unit 2Документ16 страницUnit 2Kavitha SelvarajОценок пока нет

- Digital Logic GatesДокумент57 страницDigital Logic GatesAbdullah Al AsikОценок пока нет

- Characteristics of Logic Gates: A. ObjectivesДокумент10 страницCharacteristics of Logic Gates: A. ObjectivesManish KumarОценок пока нет

- Tutorials Inlogic GatesДокумент8 страницTutorials Inlogic GatesAbdullah Al AsikОценок пока нет

- TTL and CДокумент2 страницыTTL and CManas NagОценок пока нет

- DD - Lecture 1 - PCДокумент31 страницаDD - Lecture 1 - PCRaju ReddyОценок пока нет

- Unit 4 Logic FamiliesДокумент10 страницUnit 4 Logic FamiliesJagat SinghОценок пока нет

- Unit-2 DE TOTALДокумент35 страницUnit-2 DE TOTALParameshwar ReddyОценок пока нет

- Logic Circuit DesignДокумент15 страницLogic Circuit Designajas777BОценок пока нет

- Two Mark Questions For DSDДокумент17 страницTwo Mark Questions For DSDvnirmalacseОценок пока нет

- Logic Families: ElectronicsДокумент40 страницLogic Families: ElectronicsPawan DubeyОценок пока нет

- What Is SimulinkДокумент12 страницWhat Is SimulinkSaiful IslamОценок пока нет

- UntitledДокумент202 страницыUntitledSidharth KapoorОценок пока нет

- DR K B Singh Lecture Notes PG III Sem TTLДокумент3 страницыDR K B Singh Lecture Notes PG III Sem TTLAbhijith PrabhaОценок пока нет

- Digital Concepts: 1.1 Definition of An Analogue QuantityДокумент6 страницDigital Concepts: 1.1 Definition of An Analogue QuantityAuMit GuptaОценок пока нет

- Experiment No: 1: Title: Relevant TheoryДокумент25 страницExperiment No: 1: Title: Relevant TheorysonalibhagwatkarОценок пока нет

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsОт EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercОценок пока нет

- Multiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationsДокумент8 страницMultiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationssunilОценок пока нет

- 2.differential EquationsДокумент6 страниц2.differential EquationswisamОценок пока нет

- Solving A System of Linear Equations: y X y XДокумент6 страницSolving A System of Linear Equations: y X y XwisamОценок пока нет

- 3.differential Equations IIДокумент8 страниц3.differential Equations IIwisamОценок пока нет

- 4.differential Equations IIIДокумент4 страницы4.differential Equations IIIwisamОценок пока нет

- 2.differential EquationsДокумент6 страниц2.differential EquationswisamОценок пока нет

- Fourier Series:: Periodic FunctionsДокумент8 страницFourier Series:: Periodic FunctionswisamОценок пока нет

- Basic Operation Circuits: 1-Integrators and DifferentiatorsДокумент17 страницBasic Operation Circuits: 1-Integrators and DifferentiatorswisamОценок пока нет

- University of Technology: Computer Engineering DepartmentДокумент29 страницUniversity of Technology: Computer Engineering DepartmentwisamОценок пока нет

- Matrices:: M N A A A AДокумент4 страницыMatrices:: M N A A A AwisamОценок пока нет

- Transistor - Transistor Logic (TTL) : I LowДокумент17 страницTransistor - Transistor Logic (TTL) : I LowwisamОценок пока нет

- Course Title: Instructor:: Fundamentals of Communication Dr. Aymen Dawood SalmanДокумент13 страницCourse Title: Instructor:: Fundamentals of Communication Dr. Aymen Dawood SalmanwisamОценок пока нет

- Example1: (Using Friend Function With Class)Документ15 страницExample1: (Using Friend Function With Class)wisamОценок пока нет

- Slide02 - Communication SystemДокумент14 страницSlide02 - Communication SystemwisamОценок пока нет

- Lecture 5Документ12 страницLecture 5wisamОценок пока нет

- Templates:: Int Float Int Float DoubleДокумент15 страницTemplates:: Int Float Int Float DoublewisamОценок пока нет

- Slide04 - Modulation IДокумент17 страницSlide04 - Modulation IwisamОценок пока нет

- Returning ObjectsДокумент15 страницReturning ObjectswisamОценок пока нет

- Adv Math II - ch2 - Lec5 - 3rdДокумент5 страницAdv Math II - ch2 - Lec5 - 3rdwisamОценок пока нет

- Firstly, Functions Have Unrestricted Access To Global Data. This Causes A Program's StructureДокумент19 страницFirstly, Functions Have Unrestricted Access To Global Data. This Causes A Program's StructurewisamОценок пока нет

- Adv Math II - ch2 - Lec3 - 3rdДокумент7 страницAdv Math II - ch2 - Lec3 - 3rdwisamОценок пока нет

- Adv Math II - ch2 - Lec4 - 3rdДокумент7 страницAdv Math II - ch2 - Lec4 - 3rdwisamОценок пока нет

- Adv Math II - ch1 - Lec2 - 3rdДокумент13 страницAdv Math II - ch1 - Lec2 - 3rdwisamОценок пока нет

- Adv Math II - ch1 - Lec1 - 3rdДокумент12 страницAdv Math II - ch1 - Lec1 - 3rdwisamОценок пока нет

- DSD Module 1 - Notes 1Документ95 страницDSD Module 1 - Notes 1Abinesh RОценок пока нет

- Cmos Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions ManualДокумент31 страницаCmos Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manualalbertchavezwbkafcgrns100% (22)

- Telecommunications - WikipediaДокумент29 страницTelecommunications - WikipediaSebastian GhermanОценок пока нет

- Sad Raf Shari 2016Документ9 страницSad Raf Shari 2016mhmedОценок пока нет

- Assignment #02: Name: - Ahmad Raza 20-ARID-1665 Section: - BSCS 2 (A) Course: - Digital Logic & DesignДокумент28 страницAssignment #02: Name: - Ahmad Raza 20-ARID-1665 Section: - BSCS 2 (A) Course: - Digital Logic & DesignAhmad RazaОценок пока нет

- Report On Ultrasonic Distance MeterДокумент56 страницReport On Ultrasonic Distance MeterMahesh Jadhav80% (5)

- SDPДокумент6 страницSDPJay SuguitanОценок пока нет

- CMOS Question FN-3Документ3 страницыCMOS Question FN-3alokjadhavОценок пока нет

- Mediatek Mt6169V RF Transceiver Partial Circuit Analysis of The Input CircuitsДокумент42 страницыMediatek Mt6169V RF Transceiver Partial Circuit Analysis of The Input CircuitsMario Negro Jimarez0% (1)

- Lab 2 NAND Gate Layout ECE334S: MAX TutorialДокумент6 страницLab 2 NAND Gate Layout ECE334S: MAX TutorialAnkur ThakurОценок пока нет

- EEPROM 28C16 DatasheetДокумент18 страницEEPROM 28C16 DatasheetCesarОценок пока нет

- Chapter 6 Control SystemsДокумент7 страницChapter 6 Control SystemspurushresthaОценок пока нет

- Nand 2 Nor 2Документ19 страницNand 2 Nor 2Nagendra BoyellaОценок пока нет

- UG 3-2 ECE R16-SyllabusДокумент26 страницUG 3-2 ECE R16-Syllabuschandra kiranОценок пока нет

- LD7523 DS 00Документ18 страницLD7523 DS 00Eduardo LaloОценок пока нет

- TLC 5615Документ25 страницTLC 5615Muhammad Ahsan AkramОценок пока нет

- ITRS 2011 International Technology Roadmap For SemiconductorsДокумент41 страницаITRS 2011 International Technology Roadmap For SemiconductorsFaisal AmirОценок пока нет

- SEMINAR REPORT - Image ProcessingДокумент25 страницSEMINAR REPORT - Image ProcessingRavi Kumar VermaОценок пока нет

- Cmos Process TechnologyДокумент23 страницыCmos Process TechnologyDikshaОценок пока нет

- Vlsi InternshipДокумент38 страницVlsi Internship20l31a04b1Оценок пока нет

- LДокумент16 страницLMa SeenivasanОценок пока нет

- M.tech Ece Vlsi System Design 1Документ46 страницM.tech Ece Vlsi System Design 1Mohan DasОценок пока нет

- Ams Lec 04 Mos v01Документ69 страницAms Lec 04 Mos v01Ahmed AtefОценок пока нет

- Voltage References and BiasingДокумент15 страницVoltage References and BiasingSintherОценок пока нет

- Design of XOR Gates in VLSI Implementation: November 2010Документ6 страницDesign of XOR Gates in VLSI Implementation: November 2010Perumal NamasivayamОценок пока нет

- National Semiconductor CD40106BCN DatasheetДокумент7 страницNational Semiconductor CD40106BCN DatasheetAlan CienfuegosОценок пока нет

- Adld l6Документ117 страницAdld l6prasanna prasannaОценок пока нет

- 2.5, Quad, SPST, CMOS Analog Switches: General Description FeaturesДокумент12 страниц2.5, Quad, SPST, CMOS Analog Switches: General Description FeaturesAlekseyyyОценок пока нет

- Chapter 5 MOSFET - 1 PDFДокумент31 страницаChapter 5 MOSFET - 1 PDFBanupriya-Оценок пока нет

- Professional Radio: GM300 SeriesДокумент46 страницProfessional Radio: GM300 SeriesUMA AKANDU UCHEОценок пока нет