Академический Документы

Профессиональный Документы

Культура Документы

NOT Recommended For New Designs Refer TO MP1477

Загружено:

Yuber RaptorazorОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

NOT Recommended For New Designs Refer TO MP1477

Загружено:

Yuber RaptorazorАвторское право:

Доступные форматы

MP1471

High-Efficiency, 3A Peak,

16V, 500kHz Synchronous,

Step-Down Converter In a 6-Pin TSOT 23

The Future of Analog IC Technology

R

DESCRIPTION FEATURES

P1 S FO

The MP1471 is a high-frequency, synchronous, • Wide 4.7V-to-16V Operating Input Range

rectified, step-down, switch-mode converter • 150mΩ/70mΩ Low-RDS(ON) Internal Power

with internal power MOSFETs. It offers a very MOSFETs

compact solution to achieve a 3A peak output • Proprietary Switching-Loss–Reduction

current over a wide input supply range, with

ED

Technology

excellent load and line regulation. The MP1471 • High-Efficiency Synchronous-Mode

has synchronous-mode operation for higher Operation

efficiency over the output current-load range. • Fixed 500kHz Switching Frequency

TO SI D

Current-mode operation provides fast transient • Internal AAM Power-Save Mode for High

response and eases loop stabilization. Efficiency at Light Load

•

7

Internal Soft-Start

N

Protection features include over-current

•

M N

Over-Current Protection and Hiccup

protection and thermal shutdown.

47

• Thermal Shutdown

ER D ME

The MP1471 requires a minimal number of • Output Adjustable from 0.8V

G

readily-available, standard, external • Available in a 6-pin TSOT-23 package

components and is available in a space-saving

6-pin TSOT23 package. APPLICATIONS

EF W M

• Game Consoles

• Digital Set-Top Boxes

E

•

R NE O

Flat-Panel Television and Monitors

• General Purposes

EC

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Products, Quality Assurance page.

“MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

R

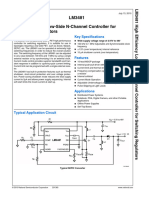

TYPICAL APPLICATION

T

VIN

3 6

IN BST

O

U1 100

3.3V 95

GND SW 2 VOUT 90

N

MP1471 R1 85

40.2k 80

5 R3

EN EN FB 4 75

40.2k 70

GND R2

65

1 13k

60

55

50

0.01 0.1 1 10

MP1471 Rev. 1.01 www.MonolithicPower.com 1

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

ORDERING INFORMATION

Part Number* Package Top Marking

MP1471GJ TSOT23-6 AEJ

R

* For Tape & Reel, add suffix –Z (e.g. MP1471GJ–Z);

P1 S FO

PACKAGE REFERENCE

TOP VIEW

ED

GND 1 6 BST

MP1471

TO SI D

SW 2 5 EN

7

N

M N

IN 3 4 FB

47

ER D ME

G

EF W M

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance

(4)

θJA θJC

E

VIN ..................................................-0.3V to 17V TSOT-23-6............................. 100 ..... 55... °C/W

R NE O

VSW ...................................................................... Notes:

-0.3V (-5V for <10ns) to 17V (19V for <10ns) 1) Exceeding these ratings may damage the device.

EC

VBS ......................................................... VSW+6V 2) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-to-

All Other Pins ...................................–0.3V to 6V ambient thermal resistance θJA, and the ambient temperature

(2)

Continuous Power Dissipation (TA = +25°C) TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ

........................................................... 1.25W (MAX)-TA)/θJA. Exceeding the maximum allowable power

R

Junction Temperature ...............................150°C dissipation will cause excessive die temperature, and the

regulator will go into thermal shutdown. Internal thermal

Lead Temperature ....................................260°C shutdown circuitry protects the device from permanent

Storage Temperature................. -65°C to 150°C damage.

T

3) The device is not guaranteed to function outside of its

(3)

Recommended Operating Conditions operating conditions.

4) Measured on JESD51-7, 4-layer PCB.

Supply Voltage VIN ...........................4.7V to 16V

O

Output Voltage VOUT ......................0.8V to 0.9VIN

Operating Junction Temp. (TJ). -40°C to +125°C

N

MP1471 Rev. 1.01 www.MonolithicPower.com 2

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

ELECTRICAL CHARACTERISTICS (5)

VIN = 12V, TA = 25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

R

Supply Current (Shutdown) IIN VEN = 0V 1 μA

Supply Current (Quiescent) Iq VEN = 2V, VFB = 1V 0.83 mA

P1 S FO

HS Switch-On Resistance HSRDS-ON VBST-SW=5V 150 mΩ

LS Switch-On Resistance LSRDS-ON Vcc=5V 70 mΩ

Switch Leakage SWLKG VEN = 0V, VSW =12V 1 μA

Current Limit (5) ILIMIT 3.5 4.2 A

ED

Oscillator Frequency fSW VFB=0.75V 400 490 580 kHz

Maximum Duty Cycle DMAX VFB=700mV 88 92 %

Minimum On Time(5) τON_MIN 90 ns

Feedback Voltage VFB 776 800 824 mV

TO SI D

EN Rising Threshold VEN_RISING 1.4 1.5 1.6 V

7

N

EN Falling Threshold VEN_FALLING 1.23 1.32 1.41 V

M N

VEN=2V 1.6 μA

47

ER D ME

EN Input Current IEN

G

VEN=0 0 μA

VIN Under-Voltage Lockout

INUVVth 3.85 4.2 4.55 V

Threshold, Rising

VIN Under-Voltage Lockout

EF W M

INUVHYS 340 mV

Threshold Hysteresis

E

Soft-Start Period τSS 1 ms

R NE O

Thermal Shutdown(5) 150 °C

Thermal Hysteresis(5) 20 °C

EC

Notes:

5) Guaranteed by design.

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 3

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 6.5µH, TA = +25°C, unless otherwise noted.

R

P1 S FO

100 100 100

95 95 95

90 90

90

85 85

85 80 80

80 75 75

ED

75 70 70

65 65

70

60 60

65 55 55

TO SI D

60 50 50

0.01 0.1 1 10 0.01 0.1 1 10 0.01 0.1 1 10

7

N

M N

47

ER D ME

G

100 5.0 50

45

90 4.5

EF W M

40

PEAK CURRENT (A)

4.0 35

80

E

30

R NE O

70 3.5 25

20

60 3.0 15

EC

10

50 2.5

5

40 2.0 0

0.01 0.1 1 10 0% 20% 40% 60% 80% 100% 0.0 0.5 1.0 1.5 2.0 2.5

R

T

O

870 50 2.9

45

860 2.7

N

40

850 35 2.5

30

840 2.3

25

830 20 2.1

820 15

1.9

10

810 1.7

5

800 0 1.5

4 6 8 10 12 14 16 4 6 8 10 12 14 16 0 1.0 2.0 3.0 4.0 5.0

MP1471 Rev. 1.01 www.MonolithicPower.com 4

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 12V, VOUT = 3.3V, L = 6.5µH, TA = +25°C, unless otherwise noted.

R

1 1

P1 S FO

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0 0

ED

-0.2 -0.2

-0.4 -0.4

-0.6 -0.6

-0.8 -0.8

TO SI D

-1 -1

0 0.5 1 1.5 2 2.5 4 6 8 10 12 14 16

7

N

M N

47

ER D ME

G

EF W M

E

R NE O

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 5

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 12V, VOUT = 3.3V, L = 6.5µH, TA = +25°C, unless otherwise noted.

Startup through Shutdown through Startup through

R

Input Voltage Input Voltage Input Voltage

IOUT = 0A IOUT = 0A IOUT = 3A

P1 S FO

VOUT VOUT VOUT

2V/div. 2V/div. 2V/div.

VIN VIN VIN

10V/div. 10V/div. 10V/div.

ED

VSW VSW VSW

5V/div. 5V/div. 5V/div.

IL IL

500mA/div. 200mA/div. IL

TO SI D

2A/div.

7

N

M N

47

Shutdown through Startup through Enable Shutdown through Enable

ER D ME

Input Voltage IOUT = 0A IOUT = 0A

G

IOUT = 3A

EF W M

VOUT VOUT VOUT

2V/div. 2V/div. 2V/div.

VIN

E

10V/div.

R NE O

VEN VEN

2V/div. 2V/div.

VSW VSW VSW

5V/div. 10V/div. 10V/div.

EC

IL IL

IL 500mA/div. 500mA/div.

2A/div.

R

Startup through Enable Shutdown through Enable Input/Output Ripple

T

IOUT = 3A IOUT = 3A IOUT = 3A

O

VOUT/AC

20mV/div.

VOUT VOUT

N

2V/div. 2V/div.

VIN/AC

500mV/div.

VEN VEN

5V/div. 5V/div.

VSW VSW VSW

10V/div. 10V/div. 10V/div.

IL IL IL

2A/div. 2A/div. 2A/div.

MP1471 Rev. 1.01 www.MonolithicPower.com 6

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 6.5µH, TA = +25°C, unless otherwise noted.

R

P1 S FO

ED

TO SI D

7

N

M N

47

ER D ME

G

EF W M

E

R NE O

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 7

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

PIN FUNCTIONS

Package

Name Description

R

Pin #

System Ground. Reference ground of the regulated output voltage: requires extra care

1 GND

P1 S FO

during PCB layout. Connect to GND with copper traces and vias.

2 SW Switch Output. Connect using wide a PCB trace.

Supply Voltage. The MP1471 operates from a 4.7V-to-16V input rail. Requires C1 to

3 IN

decouple the input rail. Connect using a wide PCB trace.

Feedback. Connect to the tap of an external resistor divider from the output to GND to set

ED

the output voltage. The frequency fold-back comparator lowers the oscillator frequency

4 FB

when the FB voltage drops below 140mV to prevent current-limit runaway during a short

circuit fault.

EN=HIGH to enable the MP1471. For automatic start-up, connect EN to VIN using a 100kΩ

5 EN

TO SI D

resistor.

Bootstrap. Connect a capacitor and a resistor between SW and BS pins to form a floating

6 BST

7

supply across the high-side switch driver. Use a 1µF BST capacitor.

N

M N

47

ER D ME

G

EF W M

E

R NE O

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 8

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

BLOCK DIAGRAM

R

IN

+

-

P1 S FO

VCC RSEN

Currrent Sense

Regulator

Amplifer

Bootstrap

Regulator BST

Oscillator HS

ED

Driver

+

SW

- Comparator

1.2pF On Time Control VCC

Current Limit Logic Control

TO SI D

47pF

Comparator

EN Reference 500k

LS

1MEG

7

N

6.5V Driver

+

+

M N

20k

FB -

47

ER D ME

Error Amplifier GND

G Figure 1: Functional Block Diagram

EF W M

E

R NE O

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 9

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

OPERATION

The MP1471 is a high-frequency, synchronous, In light-load condition, the value of VCOMP is low.

rectified, step-down, switch-mode converter When VCOMP is less than VAAM and VFB is less

R

with internal power MOSFETs. It offers a very than VREF, VCOMP ramps up until it exceeds VAAM.

compact solution to achieve a 3A peak output During this time, the internal clock is blocked,

P1 S FO

current over a wide input supply range, with thus the MP1471 skips some pulses for PFM

excellent load and line regulation. (Pulse Frequency Modulation) mode and

achieves the light load power save.

The MP1471 operates in a fixed-frequency,

peak-current–control mode to regulate the Clock

output voltage. An internal clock initiates the

ED

VOUT

1.2pF

PWM cycle to turn on the integrated high-side HS_driver + VAAM

47pF 500k

Q S

power MOSFET. This MOSFET remains on - R1

VCOMP 20k

until its current reaches the value set by the R

- VFB

COMP voltage. When the power switch is off, it + R2

TO SI D

- VREF

remains off until the next clock cycle starts. If VIL sense

+

the current in the power MOSFET does not

7

N

reach the COMP set current value within 90% Figure 2: Simplified AAM Control Circuit

M N

of one PWM period, the power MOSFET is When the load current is light, the inductor peak

47

ER D ME

forced to turn off. current is set internally to about 340mA for

G

Internal Regulator VIN=12V, VOUT=3.3V, and L=6.5μH. Figure 3

The 5V internal regulator powers most of the shows the inductor peak current vs. inductor

internal circuits. This regulator takes VIN and value curve.

operates in the full VIN range. When VIN

EF W M

exceeds 5.0V, the regulator output is in full

E

regulation. When VIN falls below 5.0V, the 1.2

R NE O

output decreases.

Error Amplifier

EC

The error amplifier compares the FB voltage

against the internal 0.8V reference (REF) and

outputs a current proportional to the difference

between the two. This output current charges or

R

discharges the internal compensation network

to form the COMP voltage, which is used to

control the power MOSFET current. The

T

optimized internal compensation network

minimizes the external component counts and Figure 3: Inductor Peak Current vs. Inductor

O

simplifies the control-loop design. Value

AAM Operation Enable

N

The MP1471 has AAM (Advanced

EN is a digital control pin that turns the

Asynchronous Modulation) power-save mode

regulator on and off: Drive EN HIGH to turn on

for light load. The AAM voltage is set at 0.5V

the regulator, drive it LOW to turn it off. An

internally. Under the heavy load condition, the

internal 1MΩ resistor from EN to GND allows

VCOMP is higher than VAAM. When the clock goes

EN to float to shut down the chip.

high, the high-side power MOSFET turns on

and remains on until VILsense reaches the value The EN pin is clamped internally using a 6.5V

set by the COMP voltage. The internal clock series-Zener-diode as shown in Figure 4.

resets every time when VCOMP exceed VAAM. Connecting the EN input pin through a pullup

MP1471 Rev. 1.01 www.MonolithicPower.com 10

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

resistor to the VIN voltage limits the EN input Thermal Shutdown

current to less than 100μA. Thermal shutdown prevents the chip from

operating at exceedingly high temperatures.

For example, with 12V connected to Vin,

R

When the silicon die temperature exceeds

RPULLUP≥ (12V-6.5V) ÷ 100μA =55kΩ

150°C, it shuts down the whole chip. When the

Connecting the EN pin directly to a voltage temperature falls below its lower threshold

P1 S FO

source without any pullup resistor requires (typically 130°C) the chip is enabled again.

limiting the amplitude of the voltage source to ≤

Floating Driver and Bootstrap Charging

6V to prevent damage to the Zener diode.

An external bootstrap capacitor powers the

floating power MOSFET driver. This floating

ED

EN driver has its own UVLO protection, with a

rising threshold of 2.2V and a hysteresis of

Zener EN LOGIC

6.5V-typ

150mV. VIN regulates the bootstrap capacitor

GND

voltage internally through D1, M1, R4, C4, L1

and C2 (Figure 5). If (VIN-VSW) exceeds 5V, U2

TO SI D

Figure 4: 6.5V Zener Diode

will regulate M1 to maintain a 5V BST voltage

across C4.

7

N

Under-Voltage Lockout (UVLO)

M N

47

D1

Under-voltage lockout (UVLO) protects the chip

ER D ME

VIN

from operating at an insufficient supply voltage.

G

U2

The MP1471 UVLO comparator monitors the M1

output voltage of the internal regulator, VCC. R4

The UVLO rising threshold is about 4.2V while 5V

U1

EF W M

its falling threshold is consistently 3.85V. C4

E

Internal Soft-Start VOUT

R NE O

Soft-start prevents the converter output voltage SW L1

C2

from overshooting during startup. When the

chip starts, the internal circuit generates a soft-

EC

start voltage (SS) that ramps up from 0V to Figure 5 : Internal Bootstrap Charging Start-Up

1.2V: When SS falls below the internal and Shutdown Circuit

reference (REF), SS overrides REF so that the If both VIN and EN exceed their respective

error amplifier uses SS as the reference; when thresholds, the chip starts. The reference block

R

SS exceeds REF, the error amplifier resumes starts first, generating a stable reference

using REF as its reference. The SS time is voltage and currents, and then the internal

internally set to 1ms. regulator is enabled. The regulator provides a

T

Over-Current-Protection and Hiccup stable supply for the remaining circuits.

O

The MP1471 has a cycle-by-cycle over-current Three events can shut down the chip: EN low,

limit for when the inductor current peak value VIN low, and thermal shutdown. The shutdown

exceeds the set current-limit threshold. First, procedure starts by initially blocking the

N

when the output voltage drops until FB falls signaling path to avoid any fault triggering. The

below the Under-Voltage (UV) threshold COMP voltage and the internal supply rail are

(typically 140mV) to trigger a UV event, the then pulled down. The floating driver is not

MP1471 enters hiccup mode to periodically subject to this shutdown command.

restart the part. This protection mode is

especially useful when the output is dead-

shorted to ground. This greatly reduces the

average short-circuit current to alleviate thermal

issues and to protect the regulator. The

MP1471 exits hiccup mode once the over-

current condition is removed.

MP1471 Rev. 1.01 www.MonolithicPower.com 11

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

APPLICATION INFORMATION

Setting the Output Voltage Under light-load conditions (below 100mA), use

The external resistor divider sets the output a larger inductance for improved efficiency.

R

voltage. The feedback resistor R1 also sets the

Selecting the Input Capacitor

feedback-loop bandwidth through the internal

P1 S FO

The input current to the step-down converter is

compensation capacitor (see the Typical

discontinuous, and therefore requires a

Application circuit). Choose R1 around 10kΩ,

capacitor to both supply the AC current to the

and R2 by:

step-down converter and maintain the DC input

R1

R2 = voltage. Use low ESR capacitors for the best

ED

VOUT performance, such as ceramic capacitors with

−1

0.8V X5R or X7R dielectrics of their low ESR and

Use a T-type network for when VOUT is low. small temperature coefficients. A 22µF

capacitor is sufficient for most applications.

TO SI D

The input capacitor (C1) requires an adequate

ripple current rating because it absorbs the

7

N

input switching. Estimate the RMS current in

M N

Figure 6: T-Type Network the input capacitor with:

47

ER D ME

Table 1 lists the recommended T-type resistors VOUT ⎛⎜ VOUT ⎞

G

I C1 = ILOAD × × 1− ⎟

value for common output voltages. VIN ⎜⎝ VIN ⎟

⎠

Table 1—Resistor Selection for Common Output The worst-case condition occurs at VIN = 2VOUT,

Voltages

where:

EF W M

VOUT R1 R2 Rt LOUT COUT

(V) (kΩ) (kΩ) (kΩ) (μH) (μF) ILOAD

E

IC1 =

1.05 10 32.4 150 2.2 44 2

R NE O

1.2 20.5 41.2 120 2.2 44 For simplification, choose an input capacitor

1.8 40.2 32.4 75 3.3 44 with an RMS current rating greater than half the

EC

2.5 40.2 19.1 59 4.7 44 maximum load current.

3.3 40.2 13 40.2 6.8 44 The input capacitor can be electrolytic, tantalum,

5 40.2 7.68 24.9 6.8 44 or ceramic. Place a small, high-quality, ceramic

R

capacitor (0.1μF) as close to the IC as possible

Selecting the Inductor when using electrolytic or tantalum capacitors.

Use a 1µH-to-10µH inductor with a DC current When using ceramic capacitors, make sure that

T

rating of at least 25% percent higher than the they have enough capacitance to provide

maximum load current for most applications. sufficient charge to prevent excessive input

O

For highest efficiency, select an inductor with a voltage ripple. Estimate the input voltage ripple

DC resistance less than 15mΩ. For most caused by the capacitance with:

designs, derive the inductance value from the ⎛ ⎞

N

ILOAD V V

ΔVIN = × OUT × ⎜ 1 − OUT ⎟

following equation. fS × C1 VIN ⎝ VIN ⎠

VOUT × (VIN − VOUT )

L1 = Selecting the Output Capacitor

VIN × ΔIL × fOSC

Where ΔIL is the inductor ripple current. Choose The output capacitor (C2) maintains the DC

an inductor current approximately 30% of the output voltage. Use ceramic, tantalum, or low-

maximum load current. The maximum inductor ESR electrolytic capacitors. Use low ESR

peak current is: capacitors to limit the output voltage ripple.

ΔI L Estimate the output voltage ripple with:

IL(MAX ) = ILOAD +

2

MP1471 Rev. 1.01 www.MonolithicPower.com 12

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

PC Board Layout

VOUT ⎛ VOUT ⎞ ⎛ 1 ⎞

ΔVOUT = × ⎜1 − ⎟ × ⎜ RESR + ⎟ PCB layout is very important to achieve stable

fS × L1 ⎝ VIN ⎠ ⎝ 8 × fS × C2 ⎠ operation. For best results, use the following

R

Where L1 is the inductor value and RESR is the guidelines and Figure 8 as reference.

equivalent series resistance (ESR) of the output 1) Keep the connection between the input

P1 S FO

capacitor. ground and GND pin as short and wide as

possible.

For ceramic capacitors, the capacitance

dominates the impedance at the switching 2) Keep the connection between the input

frequency and causes most of the output capacitor and IN pin as short and wide as

voltage ripple. For simplification, estimate the possible.

ED

output voltage ripple with: 3) Use short and direct feedback connections.

Place the feedback resistors and compensation

VOUT ⎛ V ⎞ components as close to the chip as possible.

ΔVOUT = × ⎜ 1 − OUT ⎟

8 × fS 2 × L1 × C2 ⎝ VIN ⎠

4) Route SW away from sensitive analog areas

TO SI D

For tantalum or electrolytic capacitors, the ESR such as FB.

dominates the impedance at the switching

7

N

frequency. For simplification, the output ripple

M N

C1

can be approximated with:

47

GND

ER D ME

C6

VOUT ⎛ V ⎞ VIN

G

ΔVOUT = × 1 − OUT ⎟ × RESR

fS × L1 ⎜⎝ VIN ⎠ 3 2 1

C3

R5

The characteristics of the output capacitor also R4

4 5 6

affect the stability of the regulation system. The

EF W M

MP1471 can be optimized for a wide range of R2

R7

E

R6 C5

capacitance and ESR values.

R NE O

C3

R1

External Bootstrap Diode R3

An external bootstrap (BST) diode can enhance

EC

the efficiency of the regulator given the

following applicable conditions:

z VOUT is 5V or 3.3V; and

C1A

R

V

z Duty cycle is high: D= OUT >65% C1

VIN GND

C6

Connect the external BST diode from the output VIN

T

of voltage regulator to the BST pin, as shown in 3 2 1

C4

Figure 7.

O

R5

R4

4 5 6

N

C7

R2

R6 C5

R7

R1

C3

R3

R8

Figure 7 : Optional External Bootstrap Diode

For most applications, use an IN4148 for the Figure 8: Sample Layout

external BST diode is IN4148, and a 1µF

capacitor for the BST capacitor.

MP1471 Rev. 1.01 www.MonolithicPower.com 13

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

Design Example

Below is a design example following the

application guidelines for the specifications:

R

Table 2—Design Example

VIN 12V

P1 S FO

VOUT 3.3V

Io 2.5A

The detailed application schematic is shown in

Figure 9. The typical performance and circuit

ED

waveforms have been shown in the Typical

Performance Characteristics section. For more

device applications, please refer to the related

Evaluation Board Datasheets.

TO SI D

7

N

M N

47

ER D ME

G

EF W M

E

R NE O

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 14

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

TYPICAL APPLICATION CIRCUITS

R4

0

VIN 3 IN BST 6

R

C1 C6

C4

GND 25V 25V

MP1471 SW

L1

P1 S FO

GND GND GND 5V VOUT

SW 2

R3 C3 C2 C2A

R5

100k NS NS

R7 R1 GND GND

24.9K 40.2K

5 EN FB 4

EN

GND

ED

R6 C5 R2

GND

1

NS 7.68K

NS

GND GND GND GND

TO SI D

Figure 9: 12VIN, 5V/2.5A

R4

0

7

N

VIN 3 IN BST 6

C1 C6

M N

C4

47

GND 25V 25V SW

ER D ME

L1

GND

MP1471 VOUT

GND

G

GND 3.3V

SW 2

R3 C3 C2 C2A

R5

100k NS NS

R7 R1 GND GND

40.2K

EF W M

40.2K

5 EN FB 4

EN

GND

E

R6 C5 R2

GND

1

13K

R NE O

NS

NS

GND GND GND GND

EC

Figure 10: 12VIN, 3.3V/3A

R4

0

VIN 3 IN BST 6

C1 C6

C4

R

GND 25V 25V SW

MP1471 L1

GND GND GND 2.5V VOUT

SW 2

R3 C3 C2 C2A

T

R5

100k NS NS

R7 R1 GND GND

O

59K 40.2K

5 EN FB 4

EN

GND

R6 C5 R2

GND

N

NS 19.1K

NS

GND GND GND GND

Figure 81: 12VIN, 2.5V/3A

MP1471 Rev. 1.01 www.MonolithicPower.com 15

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

R4

0

VIN 3 IN BST 6

C1 C6

C4

GND 25V 25V

MP1471 SW

R

L1

GND GND GND 1.8V VOUT

SW 2

C3

P1 S FO

R3 C2 C2A

R5

100k NS NS

R7 R1 GND GND

75K 40.2K

5 EN FB 4

EN

GND

R6 C5 R2

GND

1

32.4K

ED

NS

NS

GND GND GND GND

Figure 92: 12VIN, 1.8V/3A

R4

TO SI D

0

VIN 3 IN BST 6

C1 C6

C4

7

N

GND 25V 25V SW

MP1471 L1

M N

GND GND VOUT

47

GND 1.2V

2

ER D ME

SW

R3 C3 C2 C2A

G

R5

100k NS NS

R7 R1 GND GND

120K 20.5K

5 EN FB 4

EN

GND

EF W M

R6 C5 R2

GND

1

NS 41.2K

NS

E

R NE O

GND GND GND GND

Figure 103: 12VIN, 1.2V/3A

EC

R

T

O

N

MP1471 Rev. 1.01 www.MonolithicPower.com 16

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

MP1471 – SYNCHRONOUS, STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

PACKAGE INFORMATION

TSOT23-6

R

P1 S FO

See note 7

EXAMPLE

TOP MARK

IAAAA

ED

PIN 1 ID

TO SI D

7

TOP VIEW RECOMMENDED LAND PATTERN

N

M N

47

ER D ME

G SEATING PLANE

EF W M

SEE DETAIL''A''

E

R NE O

FRONT VIEW SIDE VIEW

EC

NOTE:

R

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH ,

PROTRUSION OR GATE BURR.

T

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

OR PROTRUSION.

O

4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING)

SHALL BE 0.10 MILLIMETERS MAX.

5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AB.

N

6) DRAWING IS NOT TO SCALE.

7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK

FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

DETAIL "A"

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP1471 Rev. 1.01 www.MonolithicPower.com 17

8/27/2013 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

Вам также может понравиться

- Iso 27001 Auditor TrainingДокумент19 страницIso 27001 Auditor TrainingITOPS TeamОценок пока нет

- Top Ten Nutrients That Support Fat Loss - Poliquin ArticleДокумент4 страницыTop Ten Nutrients That Support Fat Loss - Poliquin Articledjoiner45Оценок пока нет

- Create SOAP Notes Using Medical TerminologyДокумент4 страницыCreate SOAP Notes Using Medical TerminologyLatora Gardner Boswell100% (3)

- Ledger - Problems and SolutionsДокумент1 страницаLedger - Problems and SolutionsDjamal SalimОценок пока нет

- Theoritical and Applied LinguisticДокумент6 страницTheoritical and Applied LinguisticOdonkz Forrealracingtiga100% (2)

- Lesson Plan For DemoДокумент7 страницLesson Plan For DemoShiela Tecson GamayonОценок пока нет

- Respi-Nclex QuestionsДокумент160 страницRespi-Nclex QuestionsSophia Rose Delos Santos100% (3)

- MP1471Документ18 страницMP1471freddyОценок пока нет

- Recommended For New Designs Refer T O Mp2333: High-Efficiency, 3A, 16V, 500Khz Synchronous, Step-Down ConverterДокумент16 страницRecommended For New Designs Refer T O Mp2333: High-Efficiency, 3A, 16V, 500Khz Synchronous, Step-Down ConverterKen VillanuevaОценок пока нет

- High Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterДокумент15 страницHigh Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterkadirovОценок пока нет

- 28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDДокумент24 страницы28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDElla Wijaya ChandraОценок пока нет

- Nb679a MpsДокумент19 страницNb679a MpswarkeravipОценок пока нет

- 3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterДокумент18 страниц3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterJuan C RiveraОценок пока нет

- 100% Duty Cycle Synchronous: 4A, 21V, 500Khz Step-Down ConverterДокумент19 страниц100% Duty Cycle Synchronous: 4A, 21V, 500Khz Step-Down ConverterRivaldo Barbosa GomesОценок пока нет

- Features Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllerДокумент28 страницFeatures Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllervetchboyОценок пока нет

- MST9220B: General Description FeaturesДокумент8 страницMST9220B: General Description FeaturespepenitoОценок пока нет

- High Current Power Half Bridge: The Future of Analog IC TechnologyДокумент8 страницHigh Current Power Half Bridge: The Future of Analog IC Technologyقناة احترف بنفسكОценок пока нет

- MP28167GQ AДокумент32 страницыMP28167GQ AHamouda MahmodОценок пока нет

- 3A, 50V, 100Khz Step-Down Converter With Programmable Output Ovp ThresholdДокумент14 страниц3A, 50V, 100Khz Step-Down Converter With Programmable Output Ovp Thresholdnan keОценок пока нет

- 24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyДокумент22 страницы24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyEnzoquirozОценок пока нет

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Документ13 страницOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteОценок пока нет

- LM3478MM PDFДокумент22 страницыLM3478MM PDFkarimОценок пока нет

- MP2225GJ-Z Circuito IntegratoДокумент20 страницMP2225GJ-Z Circuito IntegratoMimmo FracchiollaОценок пока нет

- Applications Description: SBFS009Документ16 страницApplications Description: SBFS009amit281276Оценок пока нет

- Sensor Ivc201Документ15 страницSensor Ivc201FarelAhadyatulakbarAditamaОценок пока нет

- Mps Confidential: 1.5A, 210Khz Step-Down ConverterДокумент8 страницMps Confidential: 1.5A, 210Khz Step-Down ConvertergatotОценок пока нет

- 2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterДокумент18 страниц2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterCesarS100% (1)

- Innoswitch-Ep Family Datasheet PDFДокумент34 страницыInnoswitch-Ep Family Datasheet PDFanand shekhawatОценок пока нет

- 2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyДокумент10 страниц2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyAnonymous aP1FSUPoОценок пока нет

- MP1482 r1.31Документ12 страницMP1482 r1.31berkОценок пока нет

- LTC1628-SYNC High Efficiency, 2-Phase Synchronous Step-Down Switching RegulatorДокумент32 страницыLTC1628-SYNC High Efficiency, 2-Phase Synchronous Step-Down Switching Regulatorملاك حمزهОценок пока нет

- A6211 Datasheet PDFДокумент18 страницA6211 Datasheet PDFNestor GlezОценок пока нет

- MP172Документ20 страницMP172leo.alpha94Оценок пока нет

- Inn2603-2605 & Inn2904 Innoswitch-Ep FamilyДокумент32 страницыInn2603-2605 & Inn2904 Innoswitch-Ep FamilyJovial JovОценок пока нет

- LMP91300 Industrial Inductive Proximity Sensor AFE: 1 Features 3 DescriptionДокумент44 страницыLMP91300 Industrial Inductive Proximity Sensor AFE: 1 Features 3 DescriptionYovi Herlin SaputraОценок пока нет

- 3728 FGДокумент36 страниц3728 FGcohito9260Оценок пока нет

- APW7142Документ22 страницыAPW7142gsmaster4141Оценок пока нет

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyДокумент13 страниц3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyIoan TivgaОценок пока нет

- Features Descriptio: LTC1736 5-Bit Adjustable High Efficiency Synchronous Step-Down Switching RegulatorДокумент28 страницFeatures Descriptio: LTC1736 5-Bit Adjustable High Efficiency Synchronous Step-Down Switching RegulatorCarlos Henrique RibasОценок пока нет

- Datasheet LTC3728L & LTC3728LX PDFДокумент32 страницыDatasheet LTC3728L & LTC3728LX PDFSelmar CavalcantiОценок пока нет

- Descriptio Features: Lt1370 500Khz High Efficiency 6A Switching RegulatorДокумент16 страницDescriptio Features: Lt1370 500Khz High Efficiency 6A Switching RegulatorvvvОценок пока нет

- REN Isl6522 DST 20010525-1998129Документ17 страницREN Isl6522 DST 20010525-1998129atillaacar34Оценок пока нет

- Datasheet AP7175Документ14 страницDatasheet AP7175Edwin SorianoОценок пока нет

- 3-A High Voltage Boost Converter With Soft-Start and Programmable Switching FrequencyДокумент24 страницы3-A High Voltage Boost Converter With Soft-Start and Programmable Switching FrequencyVinayak KulkarniОценок пока нет

- Isl 6522Документ15 страницIsl 6522PristisОценок пока нет

- OB On Bright Elec OB2001MP - C138807Документ10 страницOB On Bright Elec OB2001MP - C138807allendohorizontОценок пока нет

- uPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetДокумент13 страницuPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetSultan SinghОценок пока нет

- 2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesДокумент19 страниц2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesBrbrHuehue SzzОценок пока нет

- REN Isl8014a DST 20030828Документ16 страницREN Isl8014a DST 20030828cer cerОценок пока нет

- 2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesДокумент14 страниц2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesMaxОценок пока нет

- Features General Description: PWM/PFM Dual-Mode Step-Down Switching RegulatorДокумент7 страницFeatures General Description: PWM/PFM Dual-Mode Step-Down Switching RegulatorMohit KaundalОценок пока нет

- Features Description: Ltc3565 1.25A, 4Mhz, Synchronous Step-Down DC/DC ConverterДокумент22 страницыFeatures Description: Ltc3565 1.25A, 4Mhz, Synchronous Step-Down DC/DC Converterferney_09Оценок пока нет

- High Performance, Single Synchronous Step-Down Controller For Notebook Power SupplyДокумент27 страницHigh Performance, Single Synchronous Step-Down Controller For Notebook Power Supplyzigmund zigmundОценок пока нет

- 8-Bit Multiplying D/A Converter: Integrated CircuitsДокумент10 страниц8-Bit Multiplying D/A Converter: Integrated CircuitsPraveen KumarОценок пока нет

- PWM Control 2-3A Step-Down Converter Technical SpecificationsДокумент7 страницPWM Control 2-3A Step-Down Converter Technical SpecificationsDimas BarretoОценок пока нет

- 5V/12V Synchronous-Rectified Buck Controller With Reference InputДокумент19 страниц5V/12V Synchronous-Rectified Buck Controller With Reference InputIgor LabutinОценок пока нет

- NB679Документ18 страницNB679Tri Nguyen Real EstateОценок пока нет

- LM3481MM NOPB National SemiconductorДокумент22 страницыLM3481MM NOPB National Semiconductorvs674584Оценок пока нет

- 1871 FeДокумент36 страниц1871 Ferute silvaОценок пока нет

- DC Converter With Low PassДокумент38 страницDC Converter With Low PassMuhammad Fikri Hidayat FikriОценок пока нет

- 3728lxff PDFДокумент38 страниц3728lxff PDFMaria Aleici JerezОценок пока нет

- 3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsДокумент12 страниц3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsElizabet VallejoОценок пока нет

- LWNMNM : General Description FeaturesДокумент16 страницLWNMNM : General Description FeaturesSergio BarbozaОценок пока нет

- Description Features: LT3957 Boost, Flyback, SEPIC and Inverting Converter With 5A, 40V SwitchДокумент28 страницDescription Features: LT3957 Boost, Flyback, SEPIC and Inverting Converter With 5A, 40V Switchsaom09Оценок пока нет

- High Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyДокумент20 страницHigh Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyAspire2222Оценок пока нет

- MP2497 r1.12-371637Документ15 страницMP2497 r1.12-371637SavouretОценок пока нет

- B. Arab X Ak1 SMT GenapДокумент48 страницB. Arab X Ak1 SMT GenapYuber RaptorazorОценок пока нет

- OrangePi Lite2 Schematics v2.0Документ14 страницOrangePi Lite2 Schematics v2.0Yuber RaptorazorОценок пока нет

- 2SC4672Документ4 страницы2SC4672Yuber RaptorazorОценок пока нет

- Bd8153efv RohmДокумент20 страницBd8153efv RohmYuber RaptorazorОценок пока нет

- Bd8153efv RohmДокумент20 страницBd8153efv RohmYuber RaptorazorОценок пока нет

- Applying Ed I UsДокумент5 страницApplying Ed I UsYuber RaptorazorОценок пока нет

- Satellite C55D A5304Документ4 страницыSatellite C55D A5304Yuber RaptorazorОценок пока нет

- Equilibrium of Supply and DemandДокумент4 страницыEquilibrium of Supply and DemandJuina Mhay Baldillo ChunacoОценок пока нет

- DHRM 3 SyllabusДокумент10 страницDHRM 3 SyllabusCherokee Tuazon RodriguezОценок пока нет

- LUTS Spot TestДокумент2 страницыLUTS Spot TestHardiTariqHamma100% (1)

- SAP Untangled: An Introductory Guide To SAP For New HomesДокумент28 страницSAP Untangled: An Introductory Guide To SAP For New HomestempuserОценок пока нет

- Analyzing Visual TextsДокумент4 страницыAnalyzing Visual Textsapi-582845240Оценок пока нет

- Space Oddity Chords (Ver 2) by David Bowie Tabs at Ultimate Guitar ArchiveДокумент3 страницыSpace Oddity Chords (Ver 2) by David Bowie Tabs at Ultimate Guitar ArchiveEMMANUEL ARNOULDОценок пока нет

- SYKES Home Equipment Agreement UpdatedДокумент3 страницыSYKES Home Equipment Agreement UpdatedFritz PrejeanОценок пока нет

- Shakuntala and Other Works, by KåalidåasaДокумент255 страницShakuntala and Other Works, by KåalidåasaMohamed Sayed AbdelrehimОценок пока нет

- Current Electricity O LevelДокумент59 страницCurrent Electricity O LevelNoah OkitoiОценок пока нет

- The Remains of The Day-Excerpts-1Документ2 страницыThe Remains of The Day-Excerpts-1DajanaОценок пока нет

- ADTHEORENT SOTI Programmatic 102722Документ20 страницADTHEORENT SOTI Programmatic 102722chinmayОценок пока нет

- Inner Ear Balance ProblemsДокумент6 страницInner Ear Balance ProblemsaleiyoОценок пока нет

- MR - Abhishek JiДокумент4 страницыMR - Abhishek Jimalikgaurav01Оценок пока нет

- Yealink Device Management Platform: Key FeaturesДокумент3 страницыYealink Device Management Platform: Key FeaturesEliezer MartinsОценок пока нет

- Industrial Training, at DCCPPДокумент26 страницIndustrial Training, at DCCPPGaganil SharmaОценок пока нет

- Che 430 Fa21 - HW#5Документ2 страницыChe 430 Fa21 - HW#5Charity QuinnОценок пока нет

- Essay #01 (First Draft)Документ2 страницыEssay #01 (First Draft)thanhtam3819Оценок пока нет

- Lali The Sun Also Rises Final PaperДокумент4 страницыLali The Sun Also Rises Final PaperDaniel AdamsОценок пока нет

- Galway Music Officer RoleДокумент20 страницGalway Music Officer RoleJohanna KennyОценок пока нет

- Bill Porter Updated PDFДокумент3 страницыBill Porter Updated PDFapi-362500677Оценок пока нет

- Vision CSP22 Abhyaas Test 3SДокумент44 страницыVision CSP22 Abhyaas Test 3SManasa DevarakondaОценок пока нет

- AAU3910 Hardware Description (07) (PDF) - enДокумент46 страницAAU3910 Hardware Description (07) (PDF) - enMd AtaullaОценок пока нет

- 2.3 Temperature Conversions: Chapter 2 Energy and MatterДокумент18 страниц2.3 Temperature Conversions: Chapter 2 Energy and MatterBeverly PamanОценок пока нет