Академический Документы

Профессиональный Документы

Культура Документы

Informe Multietapa Muy Bueno PDF

Загружено:

Eduardo Mayorga EspejoИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Informe Multietapa Muy Bueno PDF

Загружено:

Eduardo Mayorga EspejoАвторское право:

Доступные форматы

UNIVERSIDAD PEDAGOGICA Y TECNOLOGICA DE

COLOMBIA

SEDE SECCIONAL SOGAMOSO

ESCUELA DE INGENIERIA ELECTRONICA

LABORATORIO DE ELECTRONICA III

AMPLIFICADORES MULTIETAPA USANDO MODELO

HIBRIDO H

Oscar Felipe Pérez

e-mail: ingeperez24@uptc.edu.co

Abril 20 de 2012

RESUMEN: En esta práctica se realiza el Distinguir el funcionamiento tanto en DC

diseño y montaje de un amplificador multietapa como en AC de los amplificadores FET y

usando transistores BJT y JFET, basándose en el BJT.

modelo hibrido del transistor.

Proporcionar las pautas básicas para el

diseño de amplificador de Audio.

PALABRAS CLAVE: Ganancia, Impedancia,

Parámetros Híbridos. 3. MATERIALES Y EQUIPOS

Osciloscopio

1. INTRODUCCIÓN

Generador de Señales

Una de las principales aplicaciones de los Protoboard

transistores es la amplificación de pequeña señal.

La amplificación consiste en generar a la salida Resistencias de diferentes valores

del dispositivo una señal eléctrica idéntica a la de

entrada pero de mayor amplitud. Los Multimetro

amplificadores pueden ser de voltaje o de

corriente dependiendo de la configuración. Fuentes de alimentación DC.

Cuando se diseña un amplificador, no es posible Transistores BJT y JFET

obtener las características deseadas (ganancia de

tensión y resistencias de entrada y salida) con una 4. PROCEDIMIENTO:

única etapa, por lo tanto, será necesario utilizar

más de una etapa, resultando un amplificador

multietapa en cascada (La salida de una etapa se Se desea diseñar un amplificador multietapa con

conecta a la entrada de la siguiente). las siguientes características: Avt = 66, RL = 91Ω

y Zi > 100KΩ, para esto se tiene:

2. OBJETIVOS Dado que la carga es considerable, la primera

etapa de diseño será un amplificador en CC, con

par-Darlington:

Diseñar e implementar un amplificador

multietapa con transistores FET y BJT

usando el modelo hibrido H.

Laboratorio de electrónica I Oscar Felipe Pérez Página 1

Teniendo el punto de operación en DC, se miden

los parámetros híbridos del transistor, para lo cual

se tiene:

Tabla 01: Parámetros Híbridos par Darlington:

hfc hic hrc hoc

-12443.55 1356.015 0.996 0.00027

Se calcula la Zin:

Fig. 1: Etapa Colector Común.

Se establece una alimentación de 24 V, para todo

el amplificador, se asume RC = RL = 91Ω.

Ahora se prosigue a diseñar la segunda etapa,

Para establecer Qac= 0.5: que será un EC sin Bypass:

Se mide el Beta, del Darlington: β = 12000

Se calculan las resistencias de polarización: Fig. 2: Etapa Emisor Común 1.

Para esta etapa se asigna una ganancia de 11, se

asume RC = 2kΩ, con esto se tiene que:

Se asume ICQ = 5.0mA, y VCEQ = 11 V, se

miden los parámetros híbridos del transistor

que se presentan a continuación:

Tabla 02: Parámetros Híbridos:

hfe hie (Ω) hre hoe (S)

180 1.10E-03 1.50E-04 2.60E-05

Se calcula la RE, para ajustar la ganancia de

voltaje:

, despejando, RE = 163.16

Se aproxima a 160Ω.

Laboratorio de electrónica I Oscar Felipe Pérez Página 2

Tabla 02: Parámetros Híbridos:

hfe hie (Ω) hre hoe (S)

180 1.10E-03 1.50E-04 2.60E-05

Garantizando Qac = 0.5:

Se calcula la RE, para ajustar la ganancia de

voltaje:

, despejando, RE = 100

Garantizando Qac = 0.5:

[ ]

[ ]

Ahora se prosigue a diseñar la tercera etapa, que

será un E.C. sin Bypass, para esto se tiene:

Se continúa ahora con el diseño de la etapa del

FET, la cual va a garantizar una impedancia de

entrada bastante grande, como ya se ha ajustado

Fig. 3: Etapa Emisor Común 2. la ganancia de 66, esta etapa será diseñada para

una ganancia de 1, el procedimiento es el

Para esta etapa se asigna una ganancia de 6, se siguiente:

asume RC = 2.2 kΩ, con esto se tiene que:

Se asume ICQ = 5.0mA, y VCEQ = 8 V, se miden

los parámetros híbridos del transistor que se

presentan a continuación:

Laboratorio de electrónica I Oscar Felipe Pérez Página 3

Para el cálculo de los condensadores, se tiene

R2 en cuenta la frecuencia de operación mínima,

RD

C

y se aplican las ecuaciones,:

VDD

C J2N5485

J1

VIN

R1

R17

RS Donde ω=2*π*f, y Z es la impedancia

CS

equivalente que ve C en paralelo.

5. ANÁLISIS DE RESULTADOS

0

Fig. 4. Etapa Source Común. Las tablas con los resultados y sus errores se

encuentran adjuntas al final del documento en

Los parámetros importantes del J-FET son IDSS y

la sección de los anexos.

VGSoff, estos parámetros se miden

experimentalmente y se obtiene para este caso la Experimentalmente se obtiene una ganancia

Tabla 04. de 65.8 y de 62 en otra medición, las cuales

son cercanas a la ganancias de diseño, hay

Tabla 04: IDSS y VGSoff del J-FET.

un error máximo del 6 % aproximadamente,

VGSOFF IDSS esto se debe al porcentaje de error de los

-3,60E+00 8,40E-03 diferentes elementos, a cambios térmicos, así

como de las mediciones experimentales de

Con estos valores se asume , y para los parámetros de los transistores, al cambiar

establecer la IDQ, se usa la siguiente expresión: los transistores por otros similares, se

observa un ligero pero notorio cambio en la

; ganancia y en el punto de operación, además

el buen comportamiento del amplificador

De la Ecuación De Shocley: obedece a un buen acople de impedancias.

6. PREGUNTAS

[ ] ,

a. ¿Cómo está conformado el modelo

Para calcular la transconductancia se usa la ecuación: hibrido H para trabajar a altas

frecuencias? ¿cuáles son las diferencias

[ ] y similitudes con el modelo usado en

estas prácticas?

Se despeja ZL a través de la ecuación:

b. Consulte acerca del modelo hibrido pi del

Se obtiene RD a partir de la ecuación: transistor y explique cómo funciona.

El modelo hibrido es importante cuando

Se asume VGG usando la ecuación: el transistor se utilza en alta frecuencia,

en la fig se muestra el modelo r para

| | bajas frecuencias.

De la equivalente de Thévenin a la entrada, se obtiene:

Para garantizar la impedancia de entrada: RG = ZI = 120KΩ.

Ahora se calculan R1 y R2:

Parámetros del modelo pi

Laboratorio de electrónica I Oscar Felipe Pérez Página 4

• rbb’= resistencia de dispersión de base base-emisor de un BJT), se despolariza el BJT y

• rb’e = resistencia que representa el deja de amplificar lo cual también ocurre cuando

efecto de recombinación de los en el otro semiciclo, la tensión no llega todavía a

los 0.6 V. En resumen, en el caso de una senoidal,

portadores minoritarios en la base

tendríamos 1.2 V no amplificados, aunque esta no

• rb’c = resistencia debida al efecto Early es la mejor forma de definirlo.

o modulación del ancho de base

• rce = resistencia entre colector y emisor

salida

• gmvb’e= corriente de cortocircuito en la Amplificador de Clase AB

salida, depende de la polarización

Mismo caso que el amplificador B solo que existe

emisor-base

una pequeña corriente que circula por los 2

transistores constantemente, que los polariza

c. Realice una tabla donde se especifiquen reduciendo enormemente la llamada "distorsión

las principales características de cada por cruce". Como en los amplificadores de clase

una de las etapas utilizadas para la A, hay una corriente de polarización constante,

construcción del amplificador. pero relativamente baja, evitando la distorsión de

cruce (de ahí su nombre: AB). En el caso de

Z entrada Z salida Av Ai amplificadores de sonido son los más usados

Emisor llegando a distorsiones menores del 0.01%

Media Media <20 >1

común sin C (THD=0.01%)

Colector

Alta Baja <1 alta

común

Source

Alta media Baja Baja Los Amplificadores Clase A tienen las

Común

siguientes características:

d. Como se mide la potencia que entrega un

amplificador a la carga. la señal de salida es un ciclo

completo de la señal de entrada.

Se polariza en el punto medio de

recta de carga. Es decir Q=o.5

El único transistor amplifica toda la

e. Que son los amplificadores clase A, señal.

Clase B y clase AB, como funcionan. Tiene un rendimiento muy bajo

(<25%)

Amplificador de Clase A

La corriente de salida circula durante todo el ciclo

Los Amplificadores Clase B tienen las

de la señal de entrada, en un solo transistor. La

corriente de polarización del transistor de salida es siguientes características:

alta y constante durante todo el proceso,

independientemente de si hay o no hay salida de Se utilizan dos transistores

audio. La distorsión introducida es muy baja, pero Se polariza cada transistor en la

el rendimiento también será bajo, estando siempre zona de corte.

por debajo del 50%.Lo que significa que la otra Cada transistor amplifica un

mitad de la corriente amplificada será disipada por semiciclo

el transistor en forma de calor. Tiene mejor rendimiento (hasta

80%).

Amplificador clase B

Durante un semiciclo la corriente circula y es Los Amplificadores Clase AB tienen las

amplificada por un transistor, y durante otro siguientes características:

semiciclo circula y es amplificada por otro

transistor, lo cual permite un descanso de un

Utiliza dos transistores

semiciclo a cada transistor y uno de trabajo y

Se polariza cada transistor un poco

disipación de potencia. Además, no circula

por encima de la zona de corte.

corriente a través de los transistores de salida

Cada transistor amplifica un poco

cuando no hay señal de audio.

más de un semiciclo completo.

El problema es que ocurre la llamada "distorsión

por cruce", ya que cuando en el primer semiciclo Tiene menor rendimiento que la

la tensión de la señal cae por debajo de los 0.6 V clase B.

(tensión aproximada de polarización de juntura

Laboratorio de electrónica I Oscar Felipe Pérez Página 5

1. CONCLUSIONES

Para obtener un buen ancho de de banda

es importante calcular muy bien el

condensador que más afecta esta

característica, en este caso es el

condensador de desacople de la

resistencia de source.

La estabilidad del amplificador, también

se ve afectada por los cambios térmicos

de los transistores, por lo tanto es

importante buscar un punto de trabajo

estable.

Aunque el modelo híbrido H es una

buena herramienta para el análisis de

señal en circuitos con transistores, el

procedimiento de medición y de diseño

es muy tedioso y requiere de bastante

precisión.

9. BIBLIOGRAFIA

BOYLESTAD, Robert L. Electrónica: Teoría de

Circuitos. Editorial Prentice Hall, 1995.

GUTIERRES, Humberto. Electrónica Análoga:

Teoría y laboratorios. Vol. 2.

MALVINO, Albert Paul. Principios de electrónica.

Editorial McGraw-Hill, 1991.

Laboratorio de electrónica I Oscar Felipe Pérez Página 6

ANEXOS

100mV

50mV

0V

-50mV

-100mV

0s 5ms 10ms 15ms 20ms 25ms

V(V2:+) V(R1:2)

Time

Ganancia de Voltaje Etapa Colector Común En Simulación.

Ganancia de Voltaje Etapa Colector Común En Práctica.

Laboratorio de electrónica I Oscar Felipe Pérez Página 7

1.2V

(17.528m,1.113)

0.8V

(12.528m,99.985m)

0.4V

0V

-0.4V

-0.8V

-1.2V

0s 5ms 10ms 15ms 20ms 25ms 30ms

V(V4:+) V(C3:2)

Time

Ganancia De Voltaje Etapa Emisor Común 1 En Simulación.

Ganancia De Voltaje Etapa Emisor Común 1 En Práctica.

Laboratorio de electrónica I Oscar Felipe Pérez Página 8

800mV

(7.5280m,617.851m)

(12.528m,99.985m)

400mV

0V

-400mV

-800mV

0s 5ms 10ms 15ms 20ms 25ms 30ms

V(V6:+) V(R10:2)

Time

Ganancia De Voltaje Etapa Emisor Común 2 En Simulación

Ganancia De Voltaje Etapa Emisor Común 2 En Práctica.

120mV

80mV

40mV

(2.5280m,99.985m)

-0mV

(2.4280m,-101.524m)

-40mV

-80mV

-120mV

0s 2ms 4ms 6ms 8ms 10ms 12ms 14ms 16ms 1

V(V8:+) V(R17:2)

Time

Ganancia De Voltaje Etapa FET

Laboratorio de electrónica I Oscar Felipe Pérez Página 9

8.0V

4.0V

(2.5280m,99.985m)

(7.4280m,6.6074)

0V

-4.0V

-8.0V

0s 2ms 4ms 6ms 8ms 10ms 12ms 14ms 16ms 18ms 20ms

V(V10:+) V(C7:2)

Time

Ganancia De Voltaje Amplificador Multietapa Completo En Simulación.

Ganancia De Voltaje Amplificador Multietapa Completo En Práctica*

*Nota: En la imagen anterior se ven las señales en fase, esto se debe a que en la configuración de canal de

una de las sondas se encontraba habilitada la herramienta de inversión de la señal.

80

60

(3.1623K,66.000)

40

20

0

1.0Hz 3.0Hz 10Hz 30Hz 100Hz 300Hz 1.0KHz 3.0KHz 10KHz 30KHz 100KHz 300KHz 1.0MHz 3.0MHz 10MHz

V(VOUT) / V(VIN)

Frequency

Barrido En Frecuencia Para Determinar Ancho De Banda.

Laboratorio de electrónica I Oscar Felipe Pérez Página 10

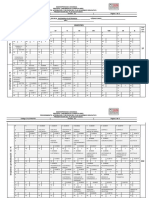

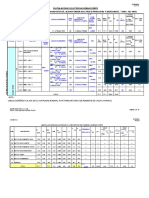

Tabla A1: Error entre los parámetros medidos y simulados para el 2N3904:

PARAMETRSO HÍBRIDOS 2N3904

PARAMETRO SIMULADO EXPERIMENTAL ERROR

hfe 1,620E+02 1,600E+02 1,235E+00

hie 1,050E+03 1,000E+03 4,762E+00

hre 0,000E+00 1,700E-04 1,700E-01

hoe 2,900E-05 3,000E-05 3,448E+00

Beta 1,820E+02 1,800E+02 1,099E+00

Tabla A2: Error entre los parámetros medidos y simulados para el par Darlington:

PARAMETROS HIBRIDOS TIP 41C

PARAMETRO EXPERIMENTAL SIMULADO ERROR (%)

HFE 1,244E+04 1,266E+04 1,737E+00

HIE 1,356E+03 1,336E+03 1,497E+00

HRE 3,782E-03 0,000E+00 3,782E-01

HOE 2,770E-04 2,700E-04 2,592E+00

Tabla A3: Error entre las ganancias por etapas y total medidas y simuladas:

ETAPA AV SIMULADA AV EXPERIMENTAL ERROR (%)

CC 1,000E+00 9,820E-01 1,800E+00

ECSB1 1,100E+01 1,140E+01 3,636E+00

ECSB2 6,000E+00 6,000E+00 0,000E+00

JFET 1,000E+00 9,500E-01 5,000E+00

AMPLIFICADOR 6,600E+01 6,580E+01 3,030E-01

Laboratorio de electrónica I Oscar Felipe Pérez Página 11

Вам также может понравиться

- Laboratorio N°3 Base Común ResueltoДокумент6 страницLaboratorio N°3 Base Común ResueltoARLEY JOSE SUAREZ MERCADOОценок пока нет

- Diseño Multietapa ElectronicaДокумент9 страницDiseño Multietapa ElectronicaYulii Carreño MartinezОценок пока нет

- Densidad de flujo magnético en un solenoide de 20 cmДокумент3 страницыDensidad de flujo magnético en un solenoide de 20 cmVenegas ChioОценок пока нет

- 1 OsciladoresДокумент6 страниц1 OsciladoresAnthony RuelasОценок пока нет

- CFA's y VFA'sДокумент2 страницыCFA's y VFA'sLuis CuadradoОценок пока нет

- Electronica de PotenciaДокумент3 страницыElectronica de PotenciaLuis Ernesto Mercado ChagoyaОценок пока нет

- Transistor BJT PDFДокумент5 страницTransistor BJT PDFSOL GABRIEL RAMIREZ BECERRAОценок пока нет

- Previo 2 Electrónicos 2 UnmsmДокумент7 страницPrevio 2 Electrónicos 2 UnmsmSteven ZacariasОценок пока нет

- Falla Asimétrica en Sistemas de PotenciaДокумент17 страницFalla Asimétrica en Sistemas de PotenciaPaula RodriguezОценок пока нет

- Diodo TunelДокумент10 страницDiodo TunelOliver Perez100% (1)

- Diseño de Amplificadores MultietapasДокумент6 страницDiseño de Amplificadores MultietapasJuanita CastroОценок пока нет

- Laboratorio 3.5 PresiónДокумент4 страницыLaboratorio 3.5 PresiónERIK GABRIEL FALCON CAPILLAОценок пока нет

- Informe Previo 1 IT313 FIEE UNIДокумент8 страницInforme Previo 1 IT313 FIEE UNISXchristianXE100% (1)

- INFORME-015-2020-ELPU-SE-PUT-SSE - Rest. Linea 8002 (R)Документ8 страницINFORME-015-2020-ELPU-SE-PUT-SSE - Rest. Linea 8002 (R)Ebis100% (1)

- Amplificador transistor emisor común BJTДокумент6 страницAmplificador transistor emisor común BJTHenrry Jhonatan100% (1)

- Diodos en Circuitos Recortadores, Limitadores, Multiplicadores y SujetadoresДокумент4 страницыDiodos en Circuitos Recortadores, Limitadores, Multiplicadores y SujetadoresDaniel Santana0% (1)

- Lab Oratorio 4. Stub Sencillo Telecomunicaciones IДокумент5 страницLab Oratorio 4. Stub Sencillo Telecomunicaciones ISergio Fernandez100% (1)

- Unidad 5 SubestacionesДокумент6 страницUnidad 5 SubestacionesJavier Torres0% (1)

- La Distorsión de Cruce Por Cero Es Un Tipo de Distorsión Que Se Caracteriza Por La Conmutación Entre Dispositivos Que Manejan Una CargaДокумент1 страницаLa Distorsión de Cruce Por Cero Es Un Tipo de Distorsión Que Se Caracteriza Por La Conmutación Entre Dispositivos Que Manejan Una Cargamaca arrietaОценок пока нет

- Taller II CorteДокумент2 страницыTaller II Cortemauro ibarraОценок пока нет

- Informe de Electrónica Digital, Corregido .Документ10 страницInforme de Electrónica Digital, Corregido .Ariel GálvezОценок пока нет

- Resumen 4Документ12 страницResumen 4HugoGJimenezОценок пока нет

- Ejercicios Circuitos Magneticos. Electrotecnia y Máquinas Eléctricas de Ingeniería Industrial. UTNДокумент15 страницEjercicios Circuitos Magneticos. Electrotecnia y Máquinas Eléctricas de Ingeniería Industrial. UTNmariОценок пока нет

- Circuitos Rectificadores de Media Onda yДокумент10 страницCircuitos Rectificadores de Media Onda yRoque VergaraОценок пока нет

- Práctica Nº5 - Informe (Amplificador Jfet)Документ8 страницPráctica Nº5 - Informe (Amplificador Jfet)vhirgho13Оценок пока нет

- Conexion Cascode Amplificadores Darlington y Darlington Compuesto PDFДокумент16 страницConexion Cascode Amplificadores Darlington y Darlington Compuesto PDFjohanОценок пока нет

- Informe N 4 - Doblador de TensionДокумент8 страницInforme N 4 - Doblador de TensionMaycon Gomez UnacОценок пока нет

- Filtro C - RECTIFICADOR DE MEDIA ONDAДокумент6 страницFiltro C - RECTIFICADOR DE MEDIA ONDAPao SantosОценок пока нет

- FINAL 3 Amplificador DiferencialДокумент4 страницыFINAL 3 Amplificador DiferencialRoy García DíazОценок пока нет

- Informe 1, CARACTERÍSTICAS DEL TRANSISTOR DE UNIÓN BIPOLAR - BJTДокумент7 страницInforme 1, CARACTERÍSTICAS DEL TRANSISTOR DE UNIÓN BIPOLAR - BJTGüerrëröYöylëОценок пока нет

- Diseño de amplificador de audio discreto multietapaДокумент13 страницDiseño de amplificador de audio discreto multietapaMaría Camila Cepeda SáenzОценок пока нет

- Dispo Preparatorio 0 3Документ11 страницDispo Preparatorio 0 3Bryan Andres YugsinОценок пока нет

- Introducción de Maquinas EléctricasДокумент51 страницаIntroducción de Maquinas EléctricasEnrique Diaz RubioОценок пока нет

- 4 Informe Diseño ElectricoДокумент13 страниц4 Informe Diseño ElectricofiboОценок пока нет

- Preinforme Usc Simple Parte2 Grupo l3 Etn801Документ7 страницPreinforme Usc Simple Parte2 Grupo l3 Etn801Carlos B CaballeroОценок пока нет

- Diseño Colector ComunДокумент9 страницDiseño Colector ComunNaty MatizОценок пока нет

- Informe 3Документ8 страницInforme 3JA SJОценок пока нет

- Informe FotodiodosДокумент9 страницInforme FotodiodosLuis MedinaОценок пока нет

- S05.s1 - Problemas Núcleo Magnético en AC UДокумент7 страницS05.s1 - Problemas Núcleo Magnético en AC UJordan OreОценок пока нет

- Circuitos ResonantesДокумент6 страницCircuitos ResonantesTopcris Na MazОценок пока нет

- GUIA DE LABORATORIO 07 Parte 2 - Comparadores 2Документ4 страницыGUIA DE LABORATORIO 07 Parte 2 - Comparadores 2JORGE LUIS GALA PRADOОценок пока нет

- Polarizacion Del DiodoДокумент38 страницPolarizacion Del DiodoMarx CortesОценок пока нет

- Semana 11 - Circuitos ElectronicosДокумент37 страницSemana 11 - Circuitos ElectronicosJulio Cesar Pampa Mamani100% (1)

- Modos de Operación Del TransistorДокумент3 страницыModos de Operación Del TransistordavidОценок пока нет

- SCR básico de disparoДокумент3 страницыSCR básico de disparoGiselita CalderonОценок пока нет

- Método Suma de Potencias en Sistemas de DistribuciónДокумент4 страницыMétodo Suma de Potencias en Sistemas de DistribuciónEliseo Q JorgeОценок пока нет

- Semana 09Документ38 страницSemana 09Alex PAОценок пока нет

- Circuitos Aritmeticos y Logicos para El Manejo de Datos Utilizando Compuertas Open Colector y TriДокумент16 страницCircuitos Aritmeticos y Logicos para El Manejo de Datos Utilizando Compuertas Open Colector y Tricarlos de la cruzОценок пока нет

- Distribución de Tensión en Cadenas de AisladoresДокумент3 страницыDistribución de Tensión en Cadenas de AisladoresmartinmejiasolanoОценок пока нет

- ErroresДокумент13 страницErroresELISBAN CHILLITUPA SEGOVIAОценок пока нет

- Implementación y análisis del amplificador operacionalДокумент12 страницImplementación y análisis del amplificador operacionalAugusto CesarОценок пока нет

- Circuitos electrónicos cascada amplificaciónДокумент9 страницCircuitos electrónicos cascada amplificaciónomar ramirezОценок пока нет

- Transformador monofásico: Parámetros y circuito equivalenteДокумент8 страницTransformador monofásico: Parámetros y circuito equivalenteVictorAntonioPeraltaBenitesОценок пока нет

- Grupo 5 - Determinación de Distancias Dielectricas en SubestacionesДокумент13 страницGrupo 5 - Determinación de Distancias Dielectricas en SubestacionesPol Klington Aranda PalaciosОценок пока нет

- Transistor BJT Práctica Lab. Circuitos Electrónicos UNCPДокумент14 страницTransistor BJT Práctica Lab. Circuitos Electrónicos UNCPchristianОценок пока нет

- Ip-1 Ee-635-NДокумент21 страницаIp-1 Ee-635-NLizeth CastroОценок пока нет

- Diseño y caracterización de un balun de λ/2Документ2 страницыDiseño y caracterización de un balun de λ/2authorОценок пока нет

- Amplificador multietapa híbrido HДокумент8 страницAmplificador multietapa híbrido HAndrés AvilaОценок пока нет

- Informe MultietapaДокумент11 страницInforme MultietapaINGEPEREZ224Оценок пока нет

- Informe Proyecto de ElectrónicaДокумент5 страницInforme Proyecto de ElectrónicaSebastián RiañoОценок пока нет

- Actividad Semana 1Документ2 страницыActividad Semana 1Eduardo Mayorga EspejoОценок пока нет

- Guía DAC0808Документ1 страницаGuía DAC0808Eduardo Mayorga EspejoОценок пока нет

- Actividad Semana 2Документ2 страницыActividad Semana 2Eduardo Mayorga EspejoОценок пока нет

- Actividad Semana 1Документ2 страницыActividad Semana 1Eduardo Mayorga EspejoОценок пока нет

- Guia - ADC0808Документ6 страницGuia - ADC0808Eduardo Mayorga EspejoОценок пока нет

- Ampli Cadores MultietapaДокумент12 страницAmpli Cadores Multietapaalvin-jesus-coba-garcia-9437Оценок пока нет

- Laboratory Exercise 6a.en - Es PDFДокумент3 страницыLaboratory Exercise 6a.en - Es PDFBriNyanОценок пока нет

- Diapo 2Документ67 страницDiapo 2Eduardo Mayorga EspejoОценок пока нет

- Articles-356420 Archivo PDF ConsultaДокумент4 страницыArticles-356420 Archivo PDF ConsultaEduardo Mayorga EspejoОценок пока нет

- Guia - ADC0808Документ6 страницGuia - ADC0808Eduardo Mayorga EspejoОценок пока нет

- Informe Parte 1,2,3Документ3 страницыInforme Parte 1,2,3Eduardo Mayorga EspejoОценок пока нет

- Laboratorio 3Документ7 страницLaboratorio 3Eduardo Mayorga EspejoОценок пока нет

- Guía PDFДокумент2 страницыGuía PDFEduardo Mayorga EspejoОценок пока нет

- Guía DAC0808Документ1 страницаGuía DAC0808Eduardo Mayorga EspejoОценок пока нет

- Guia de Laboratorio 6Документ5 страницGuia de Laboratorio 6Eduardo Mayorga EspejoОценок пока нет

- Aplicaciones Con DiodosДокумент8 страницAplicaciones Con DiodosEduardo Mayorga EspejoОценок пока нет

- Introduccion A Las Redes Inalambricas-Anaya Multimedia-Adam Engst-Glenn Fleishman para Windows Y MacintoshДокумент356 страницIntroduccion A Las Redes Inalambricas-Anaya Multimedia-Adam Engst-Glenn Fleishman para Windows Y MacintoshGeorgina Meijomin100% (5)

- Clase 1 PDFДокумент16 страницClase 1 PDFEduardo Mayorga EspejoОценок пока нет

- Malla Plan 2010Документ3 страницыMalla Plan 2010Eduardo Mayorga EspejoОценок пока нет

- Naturaleza de SemiconductoresДокумент8 страницNaturaleza de SemiconductoresEduardo Mayorga EspejoОценок пока нет

- Naturaleza de SemiconductoresДокумент8 страницNaturaleza de SemiconductoresEduardo Mayorga EspejoОценок пока нет

- Laboratorio Principios ElectricosДокумент6 страницLaboratorio Principios ElectricosEduardo Mayorga EspejoОценок пока нет

- Diodo Zener 5Документ24 страницыDiodo Zener 5lalala99999Оценок пока нет

- MINIROBOTICAДокумент22 страницыMINIROBOTICAGarcía Ochoa Cynthia CeciliaОценок пока нет

- Ditec E1tДокумент12 страницDitec E1tAmador AguilaОценок пока нет

- 02 Plano - Panel PublicitarioДокумент1 страница02 Plano - Panel Publicitarioficsa20100% (1)

- Contenido Especificaciones de La Cámara: Guía de Inicio RápidoДокумент2 страницыContenido Especificaciones de La Cámara: Guía de Inicio RápidoYOBET NASARET NAVA MARINОценок пока нет

- Condensador-Carga-DescargaДокумент16 страницCondensador-Carga-DescargaGabriel EnzianОценок пока нет

- Maquina de Vulcanizar Tip TopДокумент4 страницыMaquina de Vulcanizar Tip TopALMIVAR SASОценок пока нет

- Tarea 2 - Sandy Guzman - 41Документ7 страницTarea 2 - Sandy Guzman - 41sandyОценок пока нет

- AAC-CRT-1000-EE-002 Rev 3 Criterios para Estudios de SEPДокумент29 страницAAC-CRT-1000-EE-002 Rev 3 Criterios para Estudios de SEPLaura DiazОценок пока нет

- EASUN POWER 10KW Inversor Solar 48 V 380 V Inversor de Conexión de Red 3 FasesДокумент10 страницEASUN POWER 10KW Inversor Solar 48 V 380 V Inversor de Conexión de Red 3 FasesLuis FigueroaОценок пока нет

- Formato de Memoria IT ZumbadoresДокумент4 страницыFormato de Memoria IT ZumbadoresMarta Muñoz GámezОценок пока нет

- Equipos de MediciónДокумент15 страницEquipos de MediciónLuisa FernandaОценок пока нет

- MANUAL DEL MULTIPROBADOR Jan15Документ19 страницMANUAL DEL MULTIPROBADOR Jan15ssaanniittooОценок пока нет

- Comunicación Serial TTLДокумент7 страницComunicación Serial TTLMaria AbramonteОценок пока нет

- 3604 P PR 000005 - 1Документ15 страниц3604 P PR 000005 - 1Q Llanos HenryОценок пока нет

- Universidad Latina de PanamáДокумент5 страницUniversidad Latina de Panamámarcos marcosОценок пока нет

- Instalaciones eléctricas horno Poppi con título optimizado de menos deДокумент10 страницInstalaciones eléctricas horno Poppi con título optimizado de menos deJose L.Оценок пока нет

- Chapter 12 Translated Electrical Power Equipment Maintenance and TestingДокумент111 страницChapter 12 Translated Electrical Power Equipment Maintenance and TestingEddit MercuryОценок пока нет

- Taller 01 Mediciones Electricas Formacion ComplementariaДокумент3 страницыTaller 01 Mediciones Electricas Formacion Complementariafernando torregrozaОценок пока нет

- 05 Transistores MOSFETДокумент5 страниц05 Transistores MOSFETYamila CruzОценок пока нет

- Activacion de La Pantalla TRCДокумент5 страницActivacion de La Pantalla TRCMauro HernandezОценок пока нет

- Tema Proyecto ElectrotecniaДокумент17 страницTema Proyecto ElectrotecniaLIDYA SIMONE anguloОценок пока нет

- Practica 3 Soldadura Electrica Por Arco CДокумент12 страницPractica 3 Soldadura Electrica Por Arco CAngie RiveraОценок пока нет

- Practica 1 Electronica DigitalДокумент8 страницPractica 1 Electronica DigitalEddy MorilloОценок пока нет

- MEMORIAS DE CALCULO Final CasaДокумент17 страницMEMORIAS DE CALCULO Final CasaDANIEL ALFONSO GREIFF DAVILAОценок пока нет

- Capacitores, Bobinas y TransformadoresДокумент8 страницCapacitores, Bobinas y TransformadoresAntonio Contreras OrtizОценок пока нет

- 3RH21401BG40 Datasheet EsДокумент5 страниц3RH21401BG40 Datasheet EsLuis AndresОценок пока нет

- Leyenda de observaciones campo eléctricoДокумент40 страницLeyenda de observaciones campo eléctricoJavier Ramirez VeraОценок пока нет

- Mmad Mmad-414 FormatoalumnotrabajofinalДокумент13 страницMmad Mmad-414 FormatoalumnotrabajofinalNoel Ruben Valverde MarquinaОценок пока нет

- Laboratorio Antenas N°1-Analizador EspectrosДокумент12 страницLaboratorio Antenas N°1-Analizador EspectrosMichael InfantesОценок пока нет