Академический Документы

Профессиональный Документы

Культура Документы

A Practical Clock Control Circuit Design & Example Tessent ATPG Test Case

Загружено:

Siva SreeramdasОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

A Practical Clock Control Circuit Design & Example Tessent ATPG Test Case

Загружено:

Siva SreeramdasАвторское право:

Доступные форматы

AppNote MG580225

A Practical Clock Control Circuit Design & Example

Tessent® ATPG Test Case

October 2012

©Copyright Mentor Graphics Corporation 1995-2012. All rights reserved.

This document contains information that is proprietary to Mentor Graphics ® Corporation. The original recipient

of this document may duplicate this document in whole or in part for internal business purposes only, provided

that this entire notice appears in all copies in duplicating any part of this document, the recipient agrees to make

every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

Trademarks that appear in Mentor Graphics product publications that are not owned by Mentor Graphics are

trademarks of their respective owners.

Mentor Graphics Confidential 1 October 2012

Table of Contents

1. Introduction ................................................................................................................................ 3

2. Clock Control Circuit Description ............................................................................................... 3

2.1. Design Placement .............................................................................................................. 3

2.2. Schematic .......................................................................................................................... 4

2.3. Scan Enable Synchronization ............................................................................................ 5

2.4. Clock Gater Cells ............................................................................................................... 5

2.5. Clock Definition for ATPG .................................................................................................. 5

2.6. Shift Register Block ............................................................................................................ 6

2.7. Clock Control Operation Modes ......................................................................................... 7

2.8. Timing Diagrams ................................................................................................................ 8

2.9. RTL Description ................................................................................................................. 10

3. Test Case Description ................................................................................................................ 12

3.1. Test Case Design Statistics ............................................................................................... 12

3.2. Directory Structure ............................................................................................................. 12

3.3. Test Case Steps................................................................................................................. 13

3.4. RTL Simulation................................................................................................................... 13

3.5. RTL Synthesis .................................................................................................................... 14

3.6. Baseline ATPG................................................................................................................... 14

3.7. Clock Control Logic Insertion ............................................................................................. 14

3.8. Slow Capture ATPG ........................................................................................................... 14

3.8.1. Dofile .............................................................................................................................. 15

3.8.2. Test Procedure File ........................................................................................................ 17

3.9. Fast Capture ATPG ........................................................................................................... 19

3.10. Pattern Verification ......................................................................................................... 20

3.11. Compression Logic Insertion and ATPG ....................................................................... 21

Mentor Graphics Confidential 2 October 2012

1. Introduction

In modern designs, clock control circuits are commonly used to manage clocks during test to ensure the

following requirements are met:

Independent control by ATPG of each clock domain to improve coverage, reduce pattern count, and

achieve safe clocking with minimal user intervention

During capture, deliver correct number of clock pulses on a per-pattern basis

Cleanly switch between shift and capture clocks

Enable slow or fast clocks during capture for application of slow and at-speed patterns

Scan-programmable clock waveforms generated within a wrapped core are ideal for generating

patterns at the core level that can be retargeted to the top level while simultaneously testing

multiple cores without conflicts in how clocks are controlled within each core

This application note describes a practical PLL clock control circuit design and demonstrates its use in a

test case using Tessent® ATPG tools.

A complete test case that demonstrates the use of this clock control design in a circuit is described in the

last section. The test case is available from Mentor Graphics by downloading it from the following

SupportNet page: http://supportnet.mentor.com/reference/tutorials/index.cfm?id=MG576857

2. Clock Control Circuit Description

2.1. Design Placement

In order to avoid delay on the clock path due to test logic, a multiplexer should already exist on the clock

source to the core flops and timed for functional behavior. It is important to only balance the functional

clock path of the mux in order to avoid over-constraining the clock tree synthesis flow and causing

excessive clock latency. For example, if using a layout tool like ICCompiler, this can be accomplished by

using a set_clock_tree_exceptions -exclude_pins command and listing slow and fast clock inputs of

the clock control block. In tools such as Talus from Magma, a skew group definition for each clock control

block can be used.

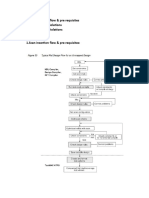

The mux should be controlled by the test mode signal as shown in Figure 1.

Figure 1 – Clock Control Logic Design Placement

The clock control design described in this application note should supply the clock when in test mode

while using the clock output of the PLL as the fast clock for at-speed capture. A top-level slow clock will

be used for shift and slow capture. The reference clock supplied to the PLL is a free-running clock.

It is also recommended not to flatten the clock control blocks during layout in order to keep the test

procedure file definition easier post layout.

Mentor Graphics Confidential 3 October 2012

2.2. Schematic

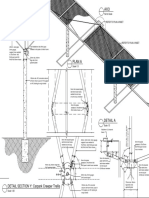

The schematic for the clock control circuit is shown in Figure 2 and the corresponding RTL can be found

in section 2.9 of this document.

Figure 2 – Clock Control Logic Schematic

The following table describes the functionality of pins at the top of the clock control block as well as some

of the internal signals:

Name Direction Description

SCAN_EN Input Scan enable driven by top-level pin

Configures number of clock pulses during capture cycle

CAP_CYCLE_CONFIG [1:0] Input (maximum clock pulses = CAP_CYCLE_CONFIG + 1)

as well as length of scan chain during shift

SCAN_IN Input Scan chain input for loading shift register

FAST_CAP_MODE Input Selects fast or slow capture clock (0 = slow, 1 = fast)

Selects test or functional mode (0 = functional, 1 = test).

TEST_MODE Input During functional mode, the clock control block is

disabled to minimize power and cross talk.

FAST_CLK Input Clock for fast capture (typically output of PLL)

SLOW_CLK Input Clock for shift and slow capture

SCAN_OUT Output Scan chain output for unloading shift register

CLK_OUT Output Controlled clock output

SCAN_EN_sync Internal Synchronized scan enable

SHIFT_REG_CLK_en Internal Clock enable signal for shift register

SHIFT_REG_CLK Internal Clock source for shift register

CLK_OUT_source Internal Clock source for controlled clock output

CLK_OUT_en Internal Clock enable signal for controlled clock output

Static signals that do not change during the test session can be controlled through on-chip controllers

(such as JTAG) or other means in order to reduce the need for top-level pins.

Mentor Graphics Confidential 4 October 2012

2.3. Scan Enable Synchronization

In order to synchronize the top-level scan enable signal with the fast clock (PLL output), a two-flop

synchronization cell is used and clocked by FAST_CLK. This is important because scan enable is used

as the trigger signal to gate the clock to the shift register. The output of the synchronization cell produces

a scan enable signal which is synchronized with the fast clock (SCAN_EN_sync) and can be used during

fast capture test.

In version 1.1 of the clock controller RTL, a flop was added on the input side of the synchronization cell

and clocked by SLOW_CLK. Since SCAN_EN normally fans out to the entire circuit and may arrive after

FAST_CLK, the flop on SLOW_CLK ensures that SCAN_EN is not synchronized by the fast clock until

SLOW_CLK is pulsed thus reducing the risk of a race condition.

Note that the scan enable synchronization logic is not used for slow capture mode which uses

SLOW_CLK for shift and capture.

In the RTL description, the synchronization cell is described as module “tessent_sync_cell” so that it can

be replaced with a technology specific synchronization cell from the appropriate library.

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

In order to ensure proper DRC analysis and simulation, the output of the clock gater cell driven by the

synchronization logic should be defined as a free-running internal clock. This is indicated by an arrow in

Figure 2 and ensures correct simulation of the logic during load_unload and avoids DRC violations.

2.4. Clock Gater Cells

The clock control circuit uses two clock gater cells to gate the clock for sequential elements inside and

outside the circuit. Similar to the synchronization cell, the clock gater cells are described as module

“tessent_cgc” so that they can be replaced with technology specific clock gater cells.

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

2.5. Clock Definition for ATPG

In the ATPG dofile, the output of the clock control logic block should be defined as an internal clock

source as shown in Figure 2. For example:

add_clocks 0 /clock_control_i/CLK_OUT –internal

Mentor Graphics Confidential 5 October 2012

With this specification, both shift and capture clocks are supplied to the design at this location which

means the internal clock should be specified in capture as well as shift procedures.

2.6. Shift Register Block

Figure 3 – Shift Register Block Schematic

The shift register block contains the programmable scan cells which will be loaded during shift in order to

pulse the internal clock during the cycle required by ATPG.

The AND gate on the input of the shift register loads zeros into the register during capture to clear it. The

EN output signal of the shift register block is used in the clock control block (Figure 2) to turn off the fast

clock to the shift register once the shift register has been unloaded. This ensures switching from the fast

capture clock to slow shift clock without risk of glitches and disturbing the values present in the shift

register. It also ensures that the shift register flip-flops have stable values when the ATPG tool simulates

the load_unload procedure and eliminates unnecessary DRC violations.

A lockup cell on the SCAN_OUT output of the shift register block ensures proper shift operation when

several clock control blocks are concatenated into a scan chain or when scan cells from chains with

different clocks are combined with the shift register flops. This is important because as described in

section 2.1, each clock control block forms a locally balanced clock tree which is not balanced with any

other chain segment.

A key feature of the shift register block is the ability to bypass up to 3 shift registers in order to reduce the

number of bits that must be specified in the patterns. This is done by setting the CAP_CYCLE_CONFIG

signals per the following table:

Maximum Clock Pulses

CAP_CYCLE_CONFIG[0] CAP_CYCLE_CONFIG[1]

During Capture Cycle

0 0 1

0 1 2

1 0 3

1 1 4

Limiting the number of condition bits to only those needed for the longest capture sequence reduces the

overall shift cycles as well as the number of scan bits that must be specified for each pattern. Minimizing

Mentor Graphics Confidential 6 October 2012

the number of specified scan cells per pattern will ensure the ATPG tool can provide the most efficient

pattern set as well as the highest compression ratio when using embedded compression.

In addition to limiting the overall number of specified scan cells, it is also important to limit the number of

scan cells that must be specified in each shift cycle. When using compression, the output of the

decompressor loads all chains simultaneously one shift cycle at a time. When stitching the shift register

sub-chains into the design scan chains, care should be taken to avoid the alignment of multiple condition

bits into the same shift cycle. One approach is to stitch the condition registers into an uncompressed scan

chain which is directly loaded. For designs in which all scan chains are compressed, placing condition bits

at the beginning, end or similar cell number of all scan chains should be avoided so that it is not

necessary to load many specified bits in the same shift cycle.

2.7. Clock Control Operation Modes

2.7.1. Functional Mode

When operating in functional mode (TEST_MODE = 0), all clock gaters are disabled to reduce

power.

Figure 4 – Test Mode Disabled

2.7.2. Shift Mode

In shift mode (SCAN_EN = 1), SLOW_CLOCK is used to load/unload scan chains which

include the condition bits in ShiftReg.

Figure 5 – Shift Mode Operation

Mentor Graphics Confidential 7 October 2012

2.7.3. Slow Capture Mode

In slow capture mode (FAST_CAP_MODE = 0), SLOW_CLOCK is used to capture data into

scan cells and to shift the condition bits in ShiftReg

Figure 6 – Slow Capture Mode Operation

2.7.4. Fast Capture Mode

In fast capture mode (FAST_CAP_MODE = 1), FAST_CLOCK is used to capture data into scan

cells and to shift the condition bits in ShiftReg

Figure 7 – Fast Capture Mode Operation

2.8. Timing Diagrams

The timing diagram for slow speed capture (FAST_CAP_MODE = 0) is shown in Figure 8. For this

example, CAP_CYCLE_CONFIG is set to “10” resulting in sequential depth of 3 (per table in section 2.6).

In this mode, SLOW_CLK is used for shift as well as capture. Based on condition bits loaded into the shift

register, the CLK_OUT port will generate the appropriate number of slow clock pulses.

Figure 8 – Slow Speed Capture Timing Diagram

Mentor Graphics Confidential 8 October 2012

In fast capture mode (FAST_CAP_MODE = 1) the waveforms in Figure 9 are generated. Similar to the

previous example, CAP_CYCLE_CONFIG is set to “10” here resulting in sequential depth of 3. In this

mode, the slow clock is still used for shift but the fast capture pulses on CLK_OUT are based FAST_CLK.

As shown, the scan enable signal which has been synchronized to the fast clock (SCAN_EN_sync) is

used to trigger the fast clock pulses on SHIFT_REG_CLK. The SHIFT_REG_CLK signal is the clock

source for the shift register containing the condition bits. Based on the condition bits loaded during shift,

the correct number of fast clock pulses will appear on CLK_OUT.

Figure 9 – Fast Capture Timing Diagram

Mentor Graphics Confidential 9 October 2012

2.9. RTL Description

The RTL description of the circuit described in this application note and used in the test case is shown in

the following section:

(* version=1.1 *)

module tessent_atpg_clock_controller (FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, SCAN_EN,

FAST_CAP_MODE, CAP_CYCLE_CONFIG, SCAN_OUT, CLK_OUT);

input FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, SCAN_EN, FAST_CAP_MODE;

input [1:0] CAP_CYCLE_CONFIG;

output SCAN_OUT, CLK_OUT;

wire SCAN_EN_sync;

wire ShiftReg_EN;

wire ShiftReg_SCAN_OUT;

wire SHIFT_REG_CLK_en;

wire SHIFT_REG_CLK_G;

wire SHIFT_REG_CLK;

wire CLK_OUT_source;

wire CLK_OUT_en;

wire CLK_OUT_G;

reg SCAN_OUT;

reg SE_SLOW_CLK;

always @ (negedge SLOW_CLK) begin

SE_SLOW_CLK <= {SE_SLOW_CLK,SCAN_EN};

end

tessent_sync_cell sync_cell (.d(SE_SLOW_CLK), .clk(FAST_CLK), .q(SCAN_EN_sync));

assign SHIFT_REG_CLK_en = TEST_MODE & ShiftReg_EN & ~SCAN_EN_sync;

tessent_cgc cgc_SHIFT_REG_CLK

(.clk(FAST_CLK), .fe(SHIFT_REG_CLK_en), .te(1'b0), .clkg(SHIFT_REG_CLK_G));

tessent_clk_mux clock_mux_SHIFT_REG_CLK

(.a(SHIFT_REG_CLK_G), .b(SLOW_CLK), .s(SCAN_EN | ~FAST_CAP_MODE), .y(SHIFT_REG_CLK));

always @ (negedge SHIFT_REG_CLK) begin

SCAN_OUT <= ShiftReg_SCAN_OUT;

end

assign CLK_OUT_en = ShiftReg_SCAN_OUT & (~FAST_CAP_MODE | SHIFT_REG_CLK_en) & TEST_MODE;

tessent_clk_mux clock_mux_CLK_OUT_source

(.a(FAST_CLK), .b(SLOW_CLK), .s(TEST_MODE & ~FAST_CAP_MODE), .y(CLK_OUT_source));

tessent_cgc cgc_CLK_OUT

(.clk(CLK_OUT_source), .fe(CLK_OUT_en), .te(1'b0), .clkg(CLK_OUT_G));

tessent_clk_mux clock_mux_CLKP (.a(CLK_OUT_G), .b(SLOW_CLK), .s(SCAN_EN), .y(CLK_OUT));

tessent_atpg_cc_shift_reg ShiftReg

(.CLK(SHIFT_REG_CLK), .SCAN_EN(SCAN_EN), .CAP_CYCLE_CONFIG(CAP_CYCLE_CONFIG),

.EN(ShiftReg_EN), .SCAN_IN(SCAN_IN), .SCAN_OUT(ShiftReg_SCAN_OUT));

endmodule

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

Mentor Graphics Confidential 10 October 2012

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

module tessent_clk_mux (a, b, s, y);

input a, b, s;

output y;

assign y = (s) ? b : a;

endmodule

module tessent_atpg_cc_shift_reg (CLK, SCAN_EN, CAP_CYCLE_CONFIG, EN, SCAN_IN, SCAN_OUT);

input CLK, SCAN_EN, SCAN_IN;

input [1:0] CAP_CYCLE_CONFIG;

output EN, SCAN_OUT;

reg [3:0] FF;

wire [3:0] FFD;

wire CAP_CONFIG_3, CAP_CONFIG_2, CAP_CONFIG_1;

always @ (posedge CLK) begin

FF <= FFD;

end

assign FFD[3] = SCAN_EN & SCAN_IN;

assign FFD[2] = (CAP_CONFIG_3 | CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[3];

assign FFD[1] = ( CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[2];

assign FFD[0] = ( CAP_CONFIG_1) ? FFD[3] : FF[1];

assign CAP_CONFIG_3 = (CAP_CYCLE_CONFIG == 2'b10);

assign CAP_CONFIG_2 = (CAP_CYCLE_CONFIG == 2'b01);

assign CAP_CONFIG_1 = (CAP_CYCLE_CONFIG == 2'b00);

assign EN = |FF;

assign SCAN_OUT = FF[0];

endmodule

RTL Change History

Version 1.0 – Initial release

Version 1.1 – Retiming flop on SLOW_CLK added in front of SCAN_EN synchronization cell

Mentor Graphics Confidential 11 October 2012

3. Test Case Description

In the test case that accompanies this application note, Tessent Shell is used for pattern generation,

hardware insertion. You may also run all steps in this test case using point tools such as Tessent

FastScan® and Tessent TestKompress®. A test case which implements the clock controller design in this

application note has been verified with tool version v2012.3 and is available from Mentor Graphics (see

section 1 for download link). The following section describes the test case in more detail.

3.1. Test Case Design Statistics

The example design used in this test case has the following characteristics:

Gates: 10k

Clocks: 3 internal clocks

Scan chains: 12

o 11 design chains

o 1 clock control condition bits

Scan flops: 446

Total faults: 48k

Test Coverage:

o Stuck-at: ~99%

o Transition: ~93%

3.2. Directory Structure

The test case directory contains the following directories

design

o gates

Gate-level netlist

Synthesized clock controller

o rtl

clock_controller

Clock controller RTL

Simulation test benches and scripts

Synthesis script

pll

Simple RTL simulation model

dofiles

o Command dofile

o Test procedure file

o Clock control definitions for slow and fast capture

library

o atpg

ATPG library

o liberty

Liberty file

o synopsys

Synthesis library (not available in test case)

o verilog

Simulation library

logfiles

o Generated ATPG logfiles

patterns

o Generated pattern files

o Simulation scripts for slow and fast capture

Mentor Graphics Confidential 12 October 2012

3.3. Test Case Steps

Step 1

o Generate baseline stuck-at and transition patterns on original test case with top-level

clocks

Step 2

o Insert clock control logic and PLL

Steps 3 & 4

o Create patterns with internal clocks (slow and fast capture)

Steps 5 & 6

o Create and insert EDT hardware

o Synthesize EDT hardware

Steps 7 & 8

o Create compressed patterns with internal clocks (slow and fast capture)

3.4. RTL Simulation

Before synthesizing the clock controller RTL, it can be simulated to ensure clock pulses are generated as

expected. To run the simulation, execute the following scripts in the design/rtl/clock_controller

directory.

run_vsim_slow_capture

run_vsim_fast_capture

For slow capture test, the test bench in the referenced directory sets the CAP_CYCLE_CONFIG signals

to 01 and loads the condition bits to generate a single clock pulse during capture. The waveform for slow

capture test is shown in Figure 6.

Figure 10 – RTL Simulation Results for Slow Capture Test

Mentor Graphics Confidential 13 October 2012

For the fast capture test example, the CAP_CYCLE_CONFIG value is set to 11 and condition bits are

setup to create 2 fast clock pulses during capture on CLK_OUT in the second and third cycles. The

waveform for fast capture test is shown in Figure 11.

Figure 11 – RTL Simulation Results for Fast Capture Test

3.5. RTL Synthesis

After verification, the RTL is synthesized using a Design Compiler synthesis script in the

design/rtl/clock_controller directory:

run_synthesis

This will run a simple synthesis based on the ADK library and create the following gate-level netlist:

design/gates/clock_controller_gate.v

3.6. Baseline ATPG

Before inserting the clock controller into the design, you can run ATPG in Tessent Shell to get the

baseline test coverage nubmers for stuck-at and transition test. To run the baseline ATPG, execute the

following script:

1.run_atpg_pre_clock_control

The baseline stuck-at test coverage is ~99% while transition fault test coverage is ~99%.

3.7. Clock Control Logic Insertion

The next step is to run Tessent Shell and insert an instance of the clock control logic for each top-level

clock. At the same time, we’ll insert a PLL to provide an internal fast clock for at-speed test. Execute the

following script to insert the clock control logic:

2.run_clock_control_insertion

See the insertion dofile for details of various commands in Tessent Shell for insertion and design editing.

3.8. Slow Capture ATPG

To run pattern generation for slow capture, execute the following script at the top directory:

3.run_atpg_slow_capture

Mentor Graphics Confidential 14 October 2012

3.8.1. Dofile

The script sets an environment variable for slow capture test and launches Tessent Shell with the

atpg.dofile. Contents of this and other included dofiles are shown here:

set_context patterns -scan

read_verilog design/gates/cpu.v

read_cell_library library/atpg/adk.atpg

set_current_design cpu 1

# Define scan chains

add_scan_group grp1 atpg.testproc

dofile scan_setup.dofile

dofile pre_drc.dofile 2

# Run Design Rule Checks

set_system_mode analysis 3

# Read Clock Control Definitions

read_procfile $env(atpg_mode).ccd

# Run ATPG

create_patterns 4

# Save pattern

report_patterns > patterns/patterns_report_$env(atpg_mode).txt

write_patterns patterns/pat1_$env(atpg_mode)_serial.v -verilog -serial -replace

write_patterns patterns/pat1_$env(atpg_mode)_parallel.v -verilog -parallel -replace

exit

scan_setup.dofile

# Define external clocks

add_clocks 1 rst_in

2.1

# Define input constraints

add_input_constraints -c1 rst_in

# Define scan chains

add_scan_chains c1 grp1 test_si1 test_so1

add_scan_chains c2 grp1 test_si2 test_so2

add_scan_chains c3 grp1 test_si3 test_so3

2.2

add_scan_chains c4 grp1 test_si4 test_so4

add_scan_chains c5 grp1 test_si5 test_so5

add_scan_chains c6 grp1 test_si6 test_so6

add_scan_chains c7 grp1 test_si7 test_so7

add_scan_chains c8 grp1 test_si8 test_so8

add_scan_chains c9 grp1 test_si9 test_so9

add_scan_chains c10 grp1 test_si10 test_so10

add_scan_chains c11 grp1 test_si11 test_so11

pre_drc.dofile

add_black_box -module pll

if {$env(atpg_mode) == "slow_capture"} {

# Slow-Speed Capture Test Mode

add_input_constraints -c0 fast_capture_mode

} elseif {$env(atpg_mode) == "fast_capture"} {

3.1

# At-Speed Capture Test Mode

add_input_constraints -c1 fast_capture_mode

set_fault_type transition -no_shift_launch

set_output_masks on 3.2

add_input_constraints -all -hold

set_external_capture_options -capture_procedure ext_fast_cap_proc

add_clocks 0 clock_control_i1/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

-pin_name int_clkg_1

add_clocks 0 clock_control_i2/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

-pin_name int_clkg_2

add_clocks 0 clock_control_i3/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

Mentor Graphics Confidential 15 October 2012

-pin_name int_clkg_3

}

add_clocks 0 clock_control_i1/CLK_OUT -internal -pin_name int_clk1

add_clocks 0 clock_control_i2/CLK_OUT -internal -pin_name int_clk2

add_clocks 0 clock_control_i3/CLK_OUT -internal -pin_name int_clk3 3.3

add_clocks 0 pll_i/pll_clock_0 -internal -free_running -pin_name int_pll

add_clocks 0 slow_clock

add_clocks 0 reference_clock -free_running

add_input_constraints -c1 test_mode

add_input_constraints -c0 test_se

# Define number of shift registers per clock controller 3.4

# cap_cycle_config value Maximum clock pulses

# 00 1

# 01 2

# 10 3

# 11 4 3.5

add_input_constraints -c1 cap_cycle_config[0]

add_input_constraints -c1 cap_cycle_config[1]

3.6

add_scan_chains clock_control_chain grp1 SI_control SO_control

The dofile first reads the netlist and cell library files [1] and sets the current design to the “cpu” module.

The next step [2] is to define the original scan structure of the design (prior to clock control logic

insertion). In section [2.1], the external reset is defined and constrained and section [2.2] defines the

original scan chains in the design.

Command [3] calls the dofile that was generated during clock control logic insertion to setup the new scan

chain as well as ATPG commands for slow and fast capture.

The conditional section at the top of the generated dofile [3.1] defines setting specific to each test mode.

For slow capture test, only the proper constraint for at_speed_capture_mode is needed. For fast capture

[3.2], transition test ATPG commands (fault type, mask PO, hold PI) are defined. Additionally, an external

capture procedure (ext_fast_cap_proc) is defined to ensure proper pulses on external clocks are written

to the pattern file. This step also defines the output of the internal clock gates used for fast capture as

free-running internal clocks. Note that internal clocks are defined with the –pin_name switch in order to

create short aliases for use in the test procedure file.

Section [3.3] defines the internal clocks on the output pin of the clock control logic (CLK_OUT) as shown

in Figure 2. Additionally, the output of the PLL must be defined as a free-running internal clock as this

signal supplies the fast clock input of the clock controllers. As seen on the first line of the dofile, the PLL

module is defined as a black box which is typically how PLL blocks are defined for ATPG.

Section [3.4] adds constraints on primary input pins such as test mode and scan enable signals. The scan

enable signal must be constrained to its off state to ensure the two clock muxes that select

SHIFT_REG_CLK and CLK_OUT are controlled properly except during the load_unload procedure which

overrides this constraint.

The next section [3.5] adds constraints to the pins that select how many condition bits will be used and

how many will be bypassed. See section 2.6 for more details. For the purpose of this test case, the select

pins are constrained to 11 to allow use of all 4 condition bits.

The last command in pre_drc.dofile [3.6] defines the new scan chain added during clock control insertion

that contains all condition bits from the 3 clock control blocks.

After issuing the set_system_mode analysis command to run design rules checks, section [4] reads the

clock control definitions for the appropriate test mode. The clock control definitions will be discussed in

more detail when the test procedure file is described.

The dofile then generates patterns, writes them to a file, and exits the tool.

Mentor Graphics Confidential 16 October 2012

3.8.2. Test Procedure File

The first part of the test procedure file is common for all test modes and is stored in the file

dofiles/atpg.testproc. The content of this file is shown below:

//

// Test Procedure File

//

set time scale 1.000000 ns ;

timeplate tmp1 =

force_pi 0 ;

measure_po 2 ;

///external clocks//////

pulse rst_in 16 32;

pulse slow_clock 16 32;

pulse reference_clock 16 32;

///internal clocks//////

pulse int_clk1 16 32;

pulse int_clk2 16 32;

pulse int_clk3 16 32;

pulse int_pll 16 32;

if {$env(atpg_mode) == "fast_capture"} {

pulse int_clkg_1 16 32;

pulse int_clkg_2 16 32;

pulse int_clkg_3 16 32;

}

period 64 ;

end;

procedure test_setup =

timeplate tmp1 ;

cycle =

force test_mode 1;

pulse rst_in;

pulse slow_clock;

end;

end;

procedure shift =

timeplate tmp1 ;

cycle =

force_sci ;

measure_sco ;

pulse slow_clock;

pulse int_clk1;

pulse int_clk2;

pulse int_clk3;

end;

end;

procedure load_unload =

scan_group grp1 ;

timeplate tmp1 ;

cycle =

force test_se 1;

end;

apply shift 44;

end;

procedure external_capture ext_fast_cap_proc =

timeplate tmp1 ;

cycle =

force_pi ;

pulse slow_clock;

end;

end;

Most of the test procedure file is typical to most design. An “if” statement in the timplate checks the ATPG

mode variable and selectively defines the timing for the internal clocks which are only used for fast

Mentor Graphics Confidential 17 October 2012

capture. Additionally, the test procedure file contains the external capture procedure ext_fast_cap_proc to

ensure proper pulses on external clocks are saved to the pattern file.

Since this designs uses clock control blocks with specific condition bits to control each clock, a clock

control definition must be defined for each internal clock. This is the portion of the test procedure file

which is loaded in section [4] of the dofile using the read_procfile command. The clock control

definitions for slow capture test are shown here:

//

// Clock Control Definitions for Slow Speed Capture Test

//

clock_control "int_clk1" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i1/ShiftReg/FF_reg[0] 1; 1

end; 2

atpg_cycle 1 =

condition /clock_control_i1/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i1/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i1/ShiftReg/FF_reg[3] 1; 3

end;

end;

clock_control "int_clk2" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i2/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i2/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i2/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i2/ShiftReg/FF_reg[3] 1;

end;

end;

clock_control "int_clk3" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i3/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i3/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i3/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i3/ShiftReg/FF_reg[3] 1;

end;

end;

A clock control definition is needed for each internal clock. The first line of the clock control definition [1]

refers to the internal clock port defined using the add_clocks command. Note the short aliases defined

with the –pin_name switch are used here.

The second line [2] refers to the top-level source clock which must be pulsed during each capture cycle

when the internal clock is being pulsed.

Mentor Graphics Confidential 18 October 2012

The third section of the clock control definition [3] defines the scan cell (condition bit) which must be

loaded with the specified value in order to pulse the internal clock during that cycle. Once the ATPG tool

has determined the required clock pulse sequence to detect faults, it will load the appropriate condition

bits during scan chain loading.

3.9. Fast Capture ATPG

Fast capture ATPG is very similar to the slow capture flow described in the previous section. To run

pattern generation for fast capture, execute the following script at the top directory:

4.run_atpg_fast_capture

The conditional statement at the beginning of the dofile will execute the following commands

# At-Speed Capture Test Mode

add_input_constraints -c1 fast_capture_mode

set_fault_type transition -no_shift_launch 1

set_output_masks on

add_input_constraints -all -hold

set_external_capture_options -capture_procedure ext_fast_cap_proc

add_clocks 0 clock_control_i1/cgc_SHIFT_REG_CLK/clkg \

-internal -free_running -pin_name int_clkg_1

add_clocks 0 clock_control_i2/cgc_SHIFT_REG_CLK/clkg \

-internal -free_running -pin_name int_clkg_2

add_clocks 0 clock_control_i3/cgc_SHIFT_REG_CLK/clkg \ 2

-internal -free_running -pin_name int_clkg_3

After constraining the fast capture mode pin and setting the fault type, the dofile masks primary output

pins and holds the primary input pins. This is typical since most testers cannot change or observe I/O

value fast enough for fast capture test.

The set_external_capture_cycles command is issued [1] to ensure all patterns will pulse SLOW_CLK.

This ensures the scan enable synchronization circuitry described in section 2.3 is properly initialized thus

correctly controlling the clock for the condition bits. Note that this command only impacts how patterns are

saved and does not change the simulation during DRC or ATPG. This approach reduces simulation run

time while ensuring the patterns work correctly during Verilog simulation.

The last section [2] adds internal free-running clocks on the output of the clock gater cell that generates

SHIFT_REG_CLK for the shift regiser (see Figure 2). This elimniates stability issues during DRC which

result from the scan enable synchronization circuit described in section 2.3.

As noted in the previous section, the same test procedure file is used for slow and fast capture test with

the exception of the clock control definitions. The clock control definitions for fast clock capture are shown

below:

//

// Clock Control Definitions for Fast Speed Capture Test

//

clock_control "int_clk1" =

atpg_cycle 0 =

condition /clock_control_i1/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i1/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i1/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i1/ShiftReg/FF_reg[3] 1;

end;

end;

Mentor Graphics Confidential 19 October 2012

clock_control "int_clk2" =

atpg_cycle 0 =

condition /clock_control_i2/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i2/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i2/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i2/ShiftReg/FF_reg[3] 1;

end;

end;

clock_control "int_clk3" =

atpg_cycle 0 =

condition /clock_control_i3/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i3/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i3/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i3/ShiftReg/FF_reg[3] 1;

end;

end;

Note that the only difference is the lack of the source_clock statements at the beginning of each clock

control defintion. A source clock is not necessary because the source clock for fast capture mode

(reference_clock) is already defined as a free-running clock and will be pulsed in every capture cycle.

For more information on definition and use of clock control definitions in Tessent ATPG tools, see the

Tessent Shell User’s Manual.

3.10. Pattern Verification

The next step is to simulate the generated patterns to ensure no mismatches exist. The following scripts

in the patterns directory simulate serial and paralel Verilog test benches in various test modes:

runsim_slow_capture

runsim_fast_capture

The scripts compile the design, library, and patterns using ModelSim and verify that all patterns (serial

and parallel) simulate with no mismatches. The simulation waveform for slow capture pattern number 1 is

shown in Figure 12:

Figure 12 – Pattern Simulation Results for Slow Capture Test

The last 3 signals are the output of the clock control blocks which show a single pulse on the output of

clock_control_i2/CLK_OUT. This can also be seen in the output of the report_patterns command

Mentor Graphics Confidential 20 October 2012

which is stored in the file patterns/patterns_report_sa.txt. The content of this file for the first few

pattersn is shown here:

//

// pattern # type cycles loads ... capture_clock_sequence

// --------- ------- ------ ----- ---------------------------------------------

// 0 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk3]

// 1 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk2]

// 2 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk2]

// 3 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk2]

// 4 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk2]

// 5 basic 1 1 [slow_clock,reference_clock,int_pll,int_clk2]

As shown in the waveform, the pattern pulses the top level slow_clock and reference_clock, output of

the PLL, and internal clock 2.

Similar observations can be made for fast capture pattern number 3 which pulses in_clk3 followed by

int_clk2. The waveform for this pattern is shown in Figure 13:

Figure 13 – Pattern Simulation Results for Fast Capture Test

The corresponding report_patterns output is shown below:

//

// pattern # type cycles loads ... capture_clock_sequence

// --------- ------- ------ ----- --------------------------------------

// 0 clock_sequential 2 1

[reference_clock,int_pll,int_clk1,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 1 clock_sequential 2 1

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 2 clock_sequential 2 1

[reference_clock,int_pll,int_clk3,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 3 clock_sequential 2 1

[reference_clock,int_pll,int_clk3,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 4 clock_sequential 2 1

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk3,int_clkg_3,int_clkg_2,int_clkg_1]

// 5 clock_sequential 2 1

[reference_clock,int_pll,int_clk1,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_pll,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

3.11. Compression Logic Insertion and ATPG

The next steps in the test case use Tessent Shell to create and insert EDT compression logic [step 5] and

to synthesize the created RTL with Design Compiler [step 6]:

5.run_edt_ip_creation

6.run_edt_ip_synthesis

Mentor Graphics Confidential 21 October 2012

The IP creation step run Tessent Shell with slow clock and fast clock setup files in order to automatically

create the ATPG fiels for both clock speeds. Since only one compression hardware design file is needed,

only the IP creation step with slow clock writes the compression hardware to a file. This file is synthesized

in step 6. Note that the ADK synthesis library used in step 6 cannot be suuplied with the test case but the

synthesized EDT logic is provided in the design/gates directory.

The final step is to create compressed patterns using the slow and fast capture clocks [steps 7 & 8]:

7.run_edt_atpg_slow_capture

8.run_edt_atpg_fast_capture

To obtain the complete test case for the flow described in this application note, use the download link in

section 1 of this document.

Mentor Graphics Confidential 22 October 2012

Вам также может понравиться

- Mentorpaper 27753Документ8 страницMentorpaper 27753Sunil VermaОценок пока нет

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCДокумент44 страницыMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaОценок пока нет

- On Chip Clock Controller For At-Speed TestingДокумент4 страницыOn Chip Clock Controller For At-Speed TestingSachin*123Оценок пока нет

- Simulation Mismatches Can Foul Up Test-Pattern VerificationДокумент6 страницSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliОценок пока нет

- Timing SimulationДокумент3 страницыTiming SimulationKarthik Sharma100% (1)

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeДокумент15 страницFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaОценок пока нет

- Few Important QuestionsДокумент7 страницFew Important QuestionsShankhadeep DasОценок пока нет

- Training On EDT (1) - Copy (1) (3) 1Документ52 страницыTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Scan Insertion - Week2&3Документ48 страницScan Insertion - Week2&3VENKATRAMAN100% (1)

- Lab2 Block Level SSN Insertion On Processor CoreДокумент33 страницыLab2 Block Level SSN Insertion On Processor Corezys WdОценок пока нет

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingДокумент3 страницыScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- Mbist FlowДокумент2 страницыMbist FlowJaita Bakshi KulshreshthaОценок пока нет

- Synthesis Netlist - Library Model - Dofile CommandsДокумент30 страницSynthesis Netlist - Library Model - Dofile CommandsPrafulani GajbhiyeОценок пока нет

- Compression AssignmentДокумент7 страницCompression Assignmentpoojithas acharya100% (1)

- Assignment - 6Документ4 страницыAssignment - 6kishorОценок пока нет

- DFT DocumentationДокумент20 страницDFT Documentationyamini100% (1)

- Atpg Lab NotesДокумент11 страницAtpg Lab Notesrajkumar gunjaОценок пока нет

- Basic Interview Questions On DFTДокумент5 страницBasic Interview Questions On DFTHardik TrivediОценок пока нет

- Streaming Scan NetworkДокумент51 страницаStreaming Scan NetworkVENKATRAMAN100% (1)

- Split Capture Cycle: During Scan Insertion - During SimulationДокумент1 страницаSplit Capture Cycle: During Scan Insertion - During SimulationsrikanthОценок пока нет

- Embedded Deterministic Test: by M. BalakrishnaДокумент28 страницEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Документ10 страницPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatОценок пока нет

- ATPG Tool FlowДокумент12 страницATPG Tool FlowAdhi SuruliОценок пока нет

- Why Masking Is Needed: Scan Chain Masking in The AcompactorДокумент6 страницWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiОценок пока нет

- Wrapper p1500Документ8 страницWrapper p1500srikanth100% (1)

- Edt Insertion Lab Observations Test Case 1: - Problem Definition: - InputsДокумент42 страницыEdt Insertion Lab Observations Test Case 1: - Problem Definition: - Inputspoojithas acharyaОценок пока нет

- Lab4 Top Level SSN InsertionДокумент19 страницLab4 Top Level SSN Insertionzys WdОценок пока нет

- Debug Broken Scan ChainДокумент31 страницаDebug Broken Scan ChainNitish KumarОценок пока нет

- Full and Fast SequentialДокумент4 страницыFull and Fast SequentialdeepaОценок пока нет

- Atpg Lab Notes PDFДокумент11 страницAtpg Lab Notes PDFrajkumar gunja100% (1)

- 10 Tips For Successful Scan Design Part OneДокумент6 страниц10 Tips For Successful Scan Design Part Onebesha1987Оценок пока нет

- Assignment Section-1 1. What Is DFT?Документ18 страницAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- EDTДокумент47 страницEDTRaghavendra MatturОценок пока нет

- Lab ReportДокумент17 страницLab ReportYashwanthKumarОценок пока нет

- Design Clock Controllers For Hierarchical TestДокумент2 страницыDesign Clock Controllers For Hierarchical Testneelalohith100% (1)

- On DFTДокумент16 страницOn DFTAman TyagiОценок пока нет

- Edt DofileДокумент2 страницыEdt DofilesenthilkumarОценок пока нет

- 1 LOS and LOC in Vlsi Conference-ProceedingДокумент9 страниц1 LOS and LOC in Vlsi Conference-Proceedingbharghav saiОценок пока нет

- AtpgДокумент11 страницAtpgsenthilkumarОценок пока нет

- Jtag PresentationДокумент21 страницаJtag PresentationNivaz ChockkalingamОценок пока нет

- Testing of Repairable Embedded Memories in SoC Approach and ChallengesДокумент6 страницTesting of Repairable Embedded Memories in SoC Approach and Challengesassantiago1Оценок пока нет

- Scan Insertion FlowДокумент9 страницScan Insertion Flowsharath AОценок пока нет

- Scan Insertion Lab ObservationsДокумент2 страницыScan Insertion Lab ObservationssenthilkumarОценок пока нет

- DFTДокумент21 страницаDFTMuhsin Nk100% (1)

- (Design For Testability) Atpg: - Jaganath SinghДокумент23 страницы(Design For Testability) Atpg: - Jaganath SinghSAI KIRAN100% (3)

- DFT Interview QuestionsДокумент2 страницыDFT Interview Questionsrupesh kumarОценок пока нет

- Occ CompleteДокумент25 страницOcc CompleteMayur Mestry100% (1)

- DFT QnsДокумент6 страницDFT QnsRajishaОценок пока нет

- Tracing CoverageДокумент2 страницыTracing CoverageSrinath M SОценок пока нет

- DFT With Tetramax PDFДокумент33 страницыDFT With Tetramax PDFdeepakk_alpineОценок пока нет

- Segregated QuestionsДокумент1 страницаSegregated QuestionsdeepaОценок пока нет

- COMPRESSION PPT by HK - OdpДокумент23 страницыCOMPRESSION PPT by HK - Odpsuneetha100% (5)

- Stil PDFДокумент9 страницStil PDFSaurin ShahОценок пока нет

- DftdocumentДокумент66 страницDftdocumentSumanth Nayak100% (1)

- Assignment 1 Poovika.tДокумент12 страницAssignment 1 Poovika.tsenthilkumarОценок пока нет

- SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckДокумент3 страницыSCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckJayesh Popat100% (2)

- Name DFT Trainee Atpg Insertion Cases ObservationsДокумент17 страницName DFT Trainee Atpg Insertion Cases ObservationssenthilkumarОценок пока нет

- A Practical On-Chip Clock Controller Circuit DesignДокумент22 страницыA Practical On-Chip Clock Controller Circuit DesignNikhil Pratap Garg67% (3)

- At Speed OccДокумент5 страницAt Speed OccAdhi SuruliОценок пока нет

- Design For Test (DFT) Course Module - 1 JTAG and Scan Insertion Course Duration: 6 Weekends (Sundays)Документ2 страницыDesign For Test (DFT) Course Module - 1 JTAG and Scan Insertion Course Duration: 6 Weekends (Sundays)Siva SreeramdasОценок пока нет

- CHIP1Документ40 страницCHIP1Siva SreeramdasОценок пока нет

- VLSI System Testing: Fault ModelingДокумент21 страницаVLSI System Testing: Fault ModelingSiva SreeramdasОценок пока нет

- Test Process and ATE 2015Документ12 страницTest Process and ATE 2015Siva SreeramdasОценок пока нет

- Chapter 1 Introduction To VLSI TestingДокумент67 страницChapter 1 Introduction To VLSI TestingSiva SreeramdasОценок пока нет

- Bscan Kenneth ParkerДокумент315 страницBscan Kenneth ParkerGOKUL TОценок пока нет

- ExamДокумент2 страницыExamSiva SreeramdasОценок пока нет

- Interview Questions Related To Scan, ATPG, EDT and SimulationДокумент1 страницаInterview Questions Related To Scan, ATPG, EDT and SimulationSiva SreeramdasОценок пока нет

- Basic Interview Questions On DFTДокумент5 страницBasic Interview Questions On DFTSiva SreeramdasОценок пока нет

- Medical Image Display & Analysis Group, University of North Carolina, Chapel HillДокумент4 страницыMedical Image Display & Analysis Group, University of North Carolina, Chapel HillSiva SreeramdasОценок пока нет

- An Efficient Classification Method For Knee MR Image SegmentationДокумент6 страницAn Efficient Classification Method For Knee MR Image SegmentationSiva SreeramdasОценок пока нет

- Dfta RefДокумент404 страницыDfta RefSiva SreeramdasОценок пока нет

- Tripathi2016 PDFДокумент7 страницTripathi2016 PDFSiva SreeramdasОценок пока нет

- Polarimetric Sar Images Classification Using Deep Belief Networks With Learning FeaturesДокумент4 страницыPolarimetric Sar Images Classification Using Deep Belief Networks With Learning FeaturesSiva SreeramdasОценок пока нет

- Biao Hou, Yuheng Jiang, Bo Ren, Zaidao Wen, Shuang Wang, and Licheng JiaoДокумент4 страницыBiao Hou, Yuheng Jiang, Bo Ren, Zaidao Wen, Shuang Wang, and Licheng JiaoSiva SreeramdasОценок пока нет

- On Image Classification: City vs. LandscapeДокумент6 страницOn Image Classification: City vs. LandscapeSiva SreeramdasОценок пока нет

- Anatomy-Specific Classification of Medical Images Using Deep Convolutional NetsДокумент4 страницыAnatomy-Specific Classification of Medical Images Using Deep Convolutional NetsSiva SreeramdasОценок пока нет

- Scan and Atpg Process Guide: (Dftadvisor, Fastscan and Flextest)Документ420 страницScan and Atpg Process Guide: (Dftadvisor, Fastscan and Flextest)Siva SreeramdasОценок пока нет

- Scan and Atpg Process Guide: (Dftadvisor, Fastscan and Flextest)Документ420 страницScan and Atpg Process Guide: (Dftadvisor, Fastscan and Flextest)Siva SreeramdasОценок пока нет

- Cell-Aware: ImproveДокумент5 страницCell-Aware: ImproveSiva SreeramdasОценок пока нет

- Contoh Assignment PDFДокумент18 страницContoh Assignment PDFSiti Fatimah A Salam67% (3)

- GTA IV Simple Native Trainer v6.5 Key Bindings For SingleplayerДокумент1 страницаGTA IV Simple Native Trainer v6.5 Key Bindings For SingleplayerThanuja DilshanОценок пока нет

- CEN and CENELEC Position Paper On The Proposal For CPR RevisionДокумент15 страницCEN and CENELEC Position Paper On The Proposal For CPR Revisionhalexing5957Оценок пока нет

- Daikin FUW Cabinet Fan Coil UnitДокумент29 страницDaikin FUW Cabinet Fan Coil UnitPaul Mendoza100% (1)

- Will Smith BiographyДокумент11 страницWill Smith Biographyjhonatan100% (1)

- 1 - Laminar and Turbulent Flow - MITWPU - HP - CDK PDFДокумент13 страниц1 - Laminar and Turbulent Flow - MITWPU - HP - CDK PDFAbhishek ChauhanОценок пока нет

- Jurnal Ekologi TerestrialДокумент6 страницJurnal Ekologi TerestrialFARIS VERLIANSYAHОценок пока нет

- A Junk Project - An Income Generating ProjectДокумент2 страницыA Junk Project - An Income Generating ProjectHercules Verdeflor ValenzuelaОценок пока нет

- Nutrition Great Foods For Getting Vitamins A To K in Your DietДокумент1 страницаNutrition Great Foods For Getting Vitamins A To K in Your DietDhruv DuaОценок пока нет

- Agile ModelingДокумент15 страницAgile Modelingprasad19845Оценок пока нет

- Powerwin EngДокумент24 страницыPowerwin Engbillwillis66Оценок пока нет

- ATADU2002 DatasheetДокумент3 страницыATADU2002 DatasheethindОценок пока нет

- Lab 2 - Using Wireshark To Examine A UDP DNS Capture Nikola JagustinДокумент6 страницLab 2 - Using Wireshark To Examine A UDP DNS Capture Nikola Jagustinpoiuytrewq lkjhgfdsaОценок пока нет

- TrellisДокумент1 страницаTrellisCayenne LightenОценок пока нет

- Brochure International ConferenceДокумент6 страницBrochure International ConferenceAnubhav Sharma sf 12Оценок пока нет

- Adime 2Документ10 страницAdime 2api-307103979Оценок пока нет

- Zahid Imran CVДокумент4 страницыZahid Imran CVDhia Hadj SassiОценок пока нет

- Benko Gambit-Jacobs and Kinsman, 1999Документ163 страницыBenko Gambit-Jacobs and Kinsman, 1999johnson Greker100% (3)

- Ac1025 Exc16 (1) .PDFTTTTTTTTTTTTTTTTTTTДокумент50 страницAc1025 Exc16 (1) .PDFTTTTTTTTTTTTTTTTTTTHung Faat ChengОценок пока нет

- IBPS Clerk Pre QUANT Memory Based 2019 QuestionsДокумент8 страницIBPS Clerk Pre QUANT Memory Based 2019 Questionsk vinayОценок пока нет

- Manual Samsung Galaxy S Duos GT-S7562Документ151 страницаManual Samsung Galaxy S Duos GT-S7562montesjjОценок пока нет

- Research On Export Trade in BangladeshДокумент7 страницResearch On Export Trade in BangladeshFarjana AnwarОценок пока нет

- Student Exploration: Digestive System: Food Inio Simple Nutrien/oДокумент9 страницStudent Exploration: Digestive System: Food Inio Simple Nutrien/oAshantiОценок пока нет

- PDF of Tally ShortcutsДокумент6 страницPDF of Tally ShortcutsSuraj Mehta100% (2)

- CoSiO2 For Fischer-Tropsch Synthesis Comparison...Документ5 страницCoSiO2 For Fischer-Tropsch Synthesis Comparison...Genesis CalderónОценок пока нет

- Session4 Automotive Front End DesignДокумент76 страницSession4 Automotive Front End DesignShivprasad SavadattiОценок пока нет

- Countable 3Документ2 страницыCountable 3Pio Sulca Tapahuasco100% (1)

- Resume NetezaДокумент5 страницResume Netezahi4149Оценок пока нет

- Particle BoardДокумент1 страницаParticle BoardNamrata RamahОценок пока нет

- Ideal Gas Law Lesson Plan FinalДокумент5 страницIdeal Gas Law Lesson Plan FinalLonel SisonОценок пока нет