Академический Документы

Профессиональный Документы

Культура Документы

Btd1857A3: Cystech Electronics Corp

Загружено:

Hla Swe OoИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Btd1857A3: Cystech Electronics Corp

Загружено:

Hla Swe OoАвторское право:

Доступные форматы

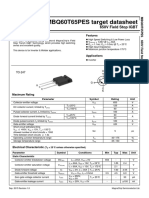

Spec. No.

: C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 1/9

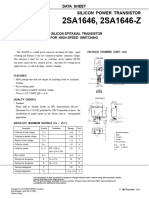

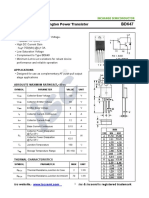

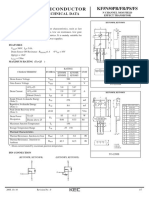

Silicon NPN Epitaxial Planar Transistor

BTD1857A3

Description

• High BVCEO

• High current capability

• Complementary to BTB1236A3

• Pb-free package

Symbol Outline

BTD1857A3 TO-92

B:Base

C:Collector

E:Emitter

ECB

Absolute Maximum Ratings (Ta=25°C)

Parameter Symbol Limits Unit

Collector-Base Voltage VCBO 180 V

Collector-Emitter Voltage VCEO 180 V

Emitter-Base Voltage VEBO 5 V

Collector Current (DC) IC 1.5 A

Collector Current (Pulse) ICP 3 A

Power Dissipation @TA=25℃ PD 750 mW

Junction Temperature Tj 150 °C

Storage Temperature Tstg -55~+150 °C

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 2/9

Characteristics (Ta=25°C)

Symbol Min. Typ. Max. Unit Test Conditions

BVCBO 180 - - V IC=50µA, IE=0

BVCEO 180 - - V IC=1mA, IB=0

BVEBO 5 - - V IE=50µA, IC=0

ICBO - - 1 µA VCB=160V, IE=0

IEBO - - 1 µA VEB=4V, IC=0

*VCE(sat) - - 0.6 V IC=1A, IB=100mA

*VBE(on) 0.45 - 0.8 V VCE=5V, IC=5mA

hFE1 180 - 400 - VCE=5V, IC=200mA

hFE2 30 - - - VCE=5V, IC=500mA

fT - 140 - MHz VCE=5V, IC=150mA

Cob - 18 - pF VCB=10V, IE=0, f=1MHz

*Pulse Test: Pulse Width ≤380µs, Duty Cycle≤2%

Ordering Information

Device Package Shipping Marking

TO-92

BTD1857A3 2000 pcs / Tape & Box D1857

(Pb-free)

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 3/9

Characteristic Curves

Current Gain vs Collector Current Saturation Voltage vs Collector Current

1000 1000

VCE=5V VCE(SAT)@IC=10IB

Tj=125℃

Saturation Voltage---(mV)

Current Gain---HFE

100 100

Tj=75℃ Tj=125℃

Tj=25℃

Tj=75℃

Tj=25℃

10 10

1 10 100 1000 10000 10 100 1000 10000

Collector Current---IC(mA) Collector Current---IC(mA)

Saturation Voltage vs Collector Current On Voltage vs Collector Current

1000 1000

Tj=25℃

Tj=25℃

Saturation Voltage---(mV)

On Voltage---(mV)

Tj=125℃

Tj=75℃ Tj=125℃

Tj=75℃

VBE(SAT)@IC=10IB VBE(ON)@VCE=5V

100 100

1 10 100 1000 10000 1 10 100 1000 10000

Collector Current---IC(mA) Collector Current---IC(mA)

Power Derating Curve

0.8

0.7

Power Dissipation---PD(W)

0.6

0.5

0.4

0.3

0.2

0.1

0

0 50 100 150 200

Ambient Temperature---TA(℃)

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 4/9

Characteristic Curves (Cont.)

Output Characteristics Output Characteristics

1 1

0.9 0.9 IB=10mA

Collector Current---IC(A)

IB=10mA IB=8mA IB=8mA

0.8 0.8

Collector Current---IC(A)

IB=6mA

0.7 IB=5mA 0.7

IB=4mA

0.6 0.6 IB=3mA

IB=3mA

0.5 0.5 IB=2mA

0.4 IB=2mA 0.4 IB=1.5mA

0.3 0.3 IB=1mA

0.2 IB=1mA 0.2 IB=500uA

0.1 IB=0 0.1 IB=0

0 0

0 1 2 3 4 5 6 0 1 2 3 4 5 6

Collector-to-Emitter Voltage---VCE(V) Collector-to-Emitter Voltage---VCE(V)

Output Capacitance vs Reverse Biased Voltage Safe Operating Area

100 10

PT=1ms

Output capacitance---Cob(pF)

Forward Current---IC(A)

PT=10ms

1

PT=100ms

0.1

PT=1s

0.01

10 0.001

0.1 1 10 100 1 10 100 1000

Reverse Biased Voltage---VCB(V) Forward Voltage---VCE(V)

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 5/9

Product Designation

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 6/9

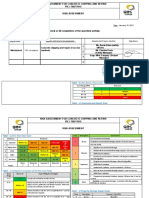

Recommended IR reflow profile

Average ramp-up rate(25 to 150℃) 1~4 ℃/second

Preheat temperature 150~180℃ 60~90 seconds

Temperature maintained above 220℃ 30 seconds min.

Time within 5℃ of actual peak temperature 3~5 seconds

Peak temperature range 255+0/-5℃

Ramp-down rate 2~10 ℃/second

Time 25℃ to peak temperature 6 minutes max.

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 7/9

Recommended temperature profile for wave soldering

Recommendation:

1. Preheat temperature at solder side must be between 100 and 130 ℃ for 80 to 100

seconds.

2. Temperature ramp-up rate : 1~2 ℃/s

3. The temperature gradient between preheat and wave soldering must be smaller than

+100℃.

4. Terminations must go through the wave simultaneously.

5. Travel through the wave from 255 to 260℃ for 2.5 to 3.5 seconds

6. Temperature ramp-down rate : 2~3 ℃/s

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 8/9

TO-92 Taping Outline

Millimeters

DIM Item

Min. Max.

A Component body height 4.33 4.83

D Tape Feed Diameter 3.80 4.20

D1 Lead Diameter 0.36 0.53

D2 Component Body Diameter 4.33 4.83

E 1.5 2.0

F1,F2 Component Lead Pitch 2.40 2.90

F1,F2 F1-F2 - ±0.3

H Height Of Seating Plane 15.50 16.50

H1 Feed Hole Location 8.50 9.50

H2 Front To Rear Deflection - 1

H2A Deflection Left Or Right - 1

H3 Component Height - 27

H4 Feed Hole To Bottom Of Component - 21

L Lead Length After Component Removal - 11

L1 Lead Wire Enclosure 2.50 -

P Feed Hole Pitch 12.50 12.90

P1 Center Of Seating Plane Location 5.95 6.75

P2 4 Feed Hole Pitch 50.30 51.30

T Over All Tape Thickness - 0.55

T1 Total Taped Package Thickness - 1.42

T2 Carrier Tape Thickness 0.36 0.68

W Tape Width 17.50 19.00

W1 Adhesive Tape Width 5.00 7.00

- 20 pcs Pitch 253 255

BTD1857A3 CYStek Product Specification

Spec. No. : C855A3

CYStech Electronics Corp. Issued Date : 2004.12.23

Revised Date : 2012.05.08

Page No. : 9/9

TO-92 Dimension

Marking:

α2

A Product Name HFE

Rank

B D1857 □

1 2 3 □□

Date Code: Year+Month

α3

Year: 4→2004, 5→2005

C Month: 1→1, 2→2, ‧‧‧,

D

9→9, A→10, B→11, C→12

H G

I α1

Style: Pin 1.Emitter 2.Collector 3.Base

E

F

3-Lead TO-92 Plastic Package

CYStek Package Code: A3

*: Typical

Inches Millimeters Inches Millimeters

DIM DIM

Min. Max. Min. Max. Min. Max. Min. Max.

A 0.1704 0.1902 4.33 4.83 G 0.0142 0.0220 0.36 0.56

B 0.1704 0.1902 4.33 4.83 H - *0.1000 - *2.54

C 0.5000 - 12.70 - I - *0.0500 - *1.27

D 0.0142 0.0220 0.36 0.56 α1 - *5° - *5°

E - *0.0500 - *1.27 α2 - *2° - *2°

F 0.1323 0.1480 3.36 3.76 α3 - *2° - *2°

Notes: 1.Controlling dimension: millimeters.

2.Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material.

3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

Material:

• Lead: Pure tin plated.

• Mold Compound: Epoxy resin family, flammability solid burning class: UL94V-0.

Important Notice:

• All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of CYStek.

• CYStek reserves the right to make changes to its products without notice.

• CYStek semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.

• CYStek assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.

BTD1857A3 CYStek Product Specification

Вам также может понравиться

- BTB772J3Документ7 страницBTB772J3jose jesus arteaga gomezОценок пока нет

- Datasheet BTC5706I3Документ5 страницDatasheet BTC5706I3Matrix RevolutionSОценок пока нет

- Afghl50t65sqdc 650v 50a 1,6v SicДокумент11 страницAfghl50t65sqdc 650v 50a 1,6v SicRaduОценок пока нет

- luxin-semi-YGW75N65FP C4153744Документ7 страницluxin-semi-YGW75N65FP C4153744Asantha Buddhi HerathОценок пока нет

- Afghl75t65sqdc Gen4 SicДокумент10 страницAfghl75t65sqdc Gen4 SicRaduОценок пока нет

- FGH4L50T65MQDC50 D-3225044Документ10 страницFGH4L50T65MQDC50 D-3225044cementsaimОценок пока нет

- AOK40B65H2ALДокумент14 страницAOK40B65H2ALRaduОценок пока нет

- mjw18020 NPN 1kv 30a LowceДокумент5 страницmjw18020 NPN 1kv 30a LowceRaduОценок пока нет

- Field Stop Trench IGBT AFGHL50T65SQ: 50 A, 650 V V 1.6 VДокумент8 страницField Stop Trench IGBT AFGHL50T65SQ: 50 A, 650 V V 1.6 VSarah PedolОценок пока нет

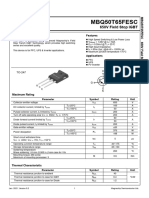

- MBQ60T65PES Target Datasheet: 650V Field Stop IGBTДокумент1 страницаMBQ60T65PES Target Datasheet: 650V Field Stop IGBTamrОценок пока нет

- High Power Bipolar Transistor: TO-220, General Purpose FeaturesДокумент4 страницыHigh Power Bipolar Transistor: TO-220, General Purpose FeaturesLarisa LarisaОценок пока нет

- HMJE13003T: Hi-SincerityДокумент4 страницыHMJE13003T: Hi-SinceritymundyОценок пока нет

- Transistor Bu4508dx OriginalДокумент2 страницыTransistor Bu4508dx Originalds_engenharia8817Оценок пока нет

- 1803 DataДокумент10 страниц1803 DataDarvin VargheseОценок пока нет

- 2N6277 PDFДокумент3 страницы2N6277 PDFAlvaro GonçalvesОценок пока нет

- Datasheet Igbt Lef75g602Документ7 страницDatasheet Igbt Lef75g602Nguyễn ĐứcОценок пока нет

- 2N2222 PDFДокумент2 страницы2N2222 PDFJuniorYanaОценок пока нет

- Mbq40t65qes 1Документ8 страницMbq40t65qes 1vankhacproОценок пока нет

- Btd1858A3: Cystech Electronics CorpДокумент9 страницBtd1858A3: Cystech Electronics CorpRodolfoОценок пока нет

- IKW75N60TДокумент13 страницIKW75N60TY Automation (Jean)Оценок пока нет

- DatasheetДокумент13 страницDatasheetMundo GGОценок пока нет

- PNP Silicon AF Transistor Array: BCM856SДокумент9 страницPNP Silicon AF Transistor Array: BCM856SАлексей АндрияшОценок пока нет

- Switching Regulator Applications FeaturesДокумент6 страницSwitching Regulator Applications FeaturesCleidimar FerreiraОценок пока нет

- STGB20NB41LZ: N-Channel Clamped 20A - D Pak Internally Clamped Powermesh™ IgbtДокумент9 страницSTGB20NB41LZ: N-Channel Clamped 20A - D Pak Internally Clamped Powermesh™ IgbtCarlos Luis ColmenaresОценок пока нет

- SGSD200 100Документ10 страницSGSD200 100isaiasvaОценок пока нет

- bdv65 Bdv65a bdv65b bdv65cДокумент3 страницыbdv65 Bdv65a bdv65b bdv65cMaurice LugusaОценок пока нет

- STN2222A: PIN Connection DescriptionsДокумент4 страницыSTN2222A: PIN Connection DescriptionsJose MartinezОценок пока нет

- Bub323z DДокумент8 страницBub323z Dtomoyo2009Оценок пока нет

- Datasheet 127Документ4 страницыDatasheet 127Francisco Junior Assis JuniorОценок пока нет

- Artschip Mje13009Документ6 страницArtschip Mje13009Vuksanov ZarkoОценок пока нет

- 2SA1646Документ6 страниц2SA1646Alessandro José SilvaОценок пока нет

- DatasheetДокумент9 страницDatasheetJakub PilarskiОценок пока нет

- MD 1803 DFHДокумент10 страницMD 1803 DFHNovri AndiОценок пока нет

- STD888T4: Medium Current, High Performance, Low Voltage PNP TransistorДокумент10 страницSTD888T4: Medium Current, High Performance, Low Voltage PNP TransistorAdis OmanovićОценок пока нет

- SMD General Purpose Transistor (NPN)Документ3 страницыSMD General Purpose Transistor (NPN)Geovanny SanjuanОценок пока нет

- BC847 SerДокумент3 страницыBC847 SerAbel GaunaОценок пока нет

- DatasheetДокумент6 страницDatasheetPUBG MOBILE SG9Оценок пока нет

- Afgy100t65spd D-2037171Документ11 страницAfgy100t65spd D-2037171crisinnaОценок пока нет

- Epitaxial Planar Transistor (NPN)Документ6 страницEpitaxial Planar Transistor (NPN)Isidro CamposОценок пока нет

- Datasheet STD724 TRANSISTORДокумент10 страницDatasheet STD724 TRANSISTORArnoldo DazaОценок пока нет

- STGB10NB37LZ: N-Channel Clamped 20A - D2Pak Internally Clamped Powermesh™ IgbtДокумент10 страницSTGB10NB37LZ: N-Channel Clamped 20A - D2Pak Internally Clamped Powermesh™ IgbtVukica IvicОценок пока нет

- Isc BD647: Silicon NPN Darlington Power TransistorДокумент2 страницыIsc BD647: Silicon NPN Darlington Power Transistornanodocl5099Оценок пока нет

- Silicon Switching NPN Transistor: 2N2222AC3A, 2N2222AC3B 2N2222AC3CДокумент3 страницыSilicon Switching NPN Transistor: 2N2222AC3A, 2N2222AC3B 2N2222AC3CRio CandrapurwitaОценок пока нет

- Conserto de Portao Facility LightДокумент8 страницConserto de Portao Facility LightAlceu DluzniewskiОценок пока нет

- Isc 2N3198: Silicon PNP Power TransistorДокумент2 страницыIsc 2N3198: Silicon PNP Power Transistormiguel h pintosОценок пока нет

- Isc BD263: Isc Silicon NPN Darlington Power TransistorДокумент2 страницыIsc BD263: Isc Silicon NPN Darlington Power TransistorAndrewОценок пока нет

- 2SC3150 BU3150 Posiblemente RC3150Документ4 страницы2SC3150 BU3150 Posiblemente RC3150VictorManuelBernalBlancoОценок пока нет

- MBQ50T65FESCДокумент8 страницMBQ50T65FESCAlanWeissОценок пока нет

- FGY75N60SMD1Документ10 страницFGY75N60SMD1gustavo jesus JimenezОценок пока нет

- STT13005D: High Voltage Fast-Switching NPN Power TransistorДокумент10 страницSTT13005D: High Voltage Fast-Switching NPN Power TransistorErwin Rolando EscobarОценок пока нет

- 2SD357Документ2 страницы2SD357bambuga07Оценок пока нет

- ARTA User ManualДокумент5 страницARTA User ManualestenioОценок пока нет

- KSC5603D NPN Silicon Transistor, Planar Silicon Transistor: FeaturesДокумент5 страницKSC5603D NPN Silicon Transistor, Planar Silicon Transistor: FeaturesParag IngleОценок пока нет

- MBQ50T65FESC MagnaChipДокумент8 страницMBQ50T65FESC MagnaChipFREDDY CHACON BOTELLOОценок пока нет

- 2SC1890, 2SC1890A: Silicon NPN EpitaxialДокумент4 страницы2SC1890, 2SC1890A: Silicon NPN EpitaxialMichael KovalОценок пока нет

- UTCPN2222A UnisonicTechnologiesДокумент4 страницыUTCPN2222A UnisonicTechnologiesMd.Frijul IslamОценок пока нет

- luxin-semi-YGW60N65F1A2 C4153740Документ8 страницluxin-semi-YGW60N65F1A2 C4153740Toader MarcuОценок пока нет

- TT2140 PDFДокумент4 страницыTT2140 PDFAsallimitОценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- Pzuxb Series: 1. Product ProfileДокумент12 страницPzuxb Series: 1. Product ProfileHla Swe OoОценок пока нет

- PNP Silicon: Semiconductor Technical DataДокумент4 страницыPNP Silicon: Semiconductor Technical DataHla Swe OoОценок пока нет

- Silicon Switching Diodes BAS 19 BAS 21: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationДокумент4 страницыSilicon Switching Diodes BAS 19 BAS 21: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationHla Swe OoОценок пока нет

- Cummins Celect or Celect Plus Ecm Order Form: Midwest Ecm Repair LLCДокумент1 страницаCummins Celect or Celect Plus Ecm Order Form: Midwest Ecm Repair LLCHla Swe OoОценок пока нет

- Toshiba: Discrete SemiconductorsДокумент2 страницыToshiba: Discrete SemiconductorsHla Swe OoОценок пока нет

- 1AZ Zener Diode SeriesДокумент3 страницы1AZ Zener Diode SeriesHla Swe OoОценок пока нет

- Data Sheet: High Speed CAN TransceiverДокумент16 страницData Sheet: High Speed CAN TransceiverHla Swe OoОценок пока нет

- Semiconductor KF5N50PR/FR/PS/FS: Technical DataДокумент7 страницSemiconductor KF5N50PR/FR/PS/FS: Technical DataHla Swe OoОценок пока нет

- SS32, SS33, SS34, SS35, SS36: Vishay General SemiconductorДокумент4 страницыSS32, SS33, SS34, SS35, SS36: Vishay General SemiconductorHla Swe OoОценок пока нет

- Semiconductor KF5N50PR/FR/PS/FS: Technical DataДокумент7 страницSemiconductor KF5N50PR/FR/PS/FS: Technical DataHla Swe OoОценок пока нет

- Product Data Sheet: Altira - French Socket-Outlet ROTOCLIP Tamperproof With Lamp Red CoverДокумент2 страницыProduct Data Sheet: Altira - French Socket-Outlet ROTOCLIP Tamperproof With Lamp Red CoverHla Swe OoОценок пока нет

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesДокумент20 страниц5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesHla Swe Oo0% (1)

- TC4027BP, TC4027BF, TC4027BFN: TC4027B Dual J-K Master-Slave Flip FlopДокумент9 страницTC4027BP, TC4027BF, TC4027BFN: TC4027B Dual J-K Master-Slave Flip FlopHla Swe OoОценок пока нет

- SH88F516 88F54 89F52V2.5 PDFДокумент105 страницSH88F516 88F54 89F52V2.5 PDFHla Swe OoОценок пока нет

- 1N5819 SMDДокумент2 страницы1N5819 SMDHla Swe OoОценок пока нет

- Smoke Detector FSI-851 - 0Документ2 страницыSmoke Detector FSI-851 - 0Hla Swe OoОценок пока нет

- FSBB20CH60F 83493Документ15 страницFSBB20CH60F 83493Hla Swe OoОценок пока нет

- STSW Link004Документ3 страницыSTSW Link004Hla Swe OoОценок пока нет

- Unisonic Technologies Co., LTD: Power TransistorДокумент2 страницыUnisonic Technologies Co., LTD: Power TransistorHla Swe OoОценок пока нет

- AC Series Piston Oil Free Air Compressor PumpsДокумент10 страницAC Series Piston Oil Free Air Compressor PumpsHla Swe OoОценок пока нет

- SmartMedia FormatДокумент5 страницSmartMedia FormatHla Swe OoОценок пока нет

- 280 Oil Free CompressorДокумент7 страниц280 Oil Free CompressorHla Swe OoОценок пока нет

- BV DSG eДокумент18 страницBV DSG eIulianIonutRaduОценок пока нет

- Lesson Plan PPEДокумент3 страницыLesson Plan PPEErika Jean Moyo ManzanillaОценок пока нет

- Disorders of The Reproductive SystemДокумент10 страницDisorders of The Reproductive SystemRose Kathreen Quintans AuxteroОценок пока нет

- Amul Amul AmulДокумент7 страницAmul Amul Amulravikumarverma28Оценок пока нет

- Checklist For Surge Arrester Rev00Документ3 страницыChecklist For Surge Arrester Rev00Santhosh Kumar VinayagamОценок пока нет

- 4EVC800802-LFEN DCwallbox 5 19Документ2 страницы4EVC800802-LFEN DCwallbox 5 19michael esoОценок пока нет

- Ra Concrete Chipping 7514Документ5 страницRa Concrete Chipping 7514Charles DoriaОценок пока нет

- Unit Weight of Soil in Quezon CityДокумент2 страницыUnit Weight of Soil in Quezon CityClarence Noel CorpuzОценок пока нет

- Muscle and Fitness Hers Features Elite Lifestyle Chef Carlo FilipponeДокумент4 страницыMuscle and Fitness Hers Features Elite Lifestyle Chef Carlo FilipponeCarlo FilipponeОценок пока нет

- Power Divider and Combiner: EE403-Microwave Engineering MTC, EE Dep., Electromagnetic Waves GroupДокумент52 страницыPower Divider and Combiner: EE403-Microwave Engineering MTC, EE Dep., Electromagnetic Waves GroupHabibat El Rahman AshrafОценок пока нет

- 99 AutomaticДокумент6 страниц99 AutomaticDustin BrownОценок пока нет

- LIC Jeevan Labh Plan (836) DetailsДокумент12 страницLIC Jeevan Labh Plan (836) DetailsMuthukrishnan SankaranОценок пока нет

- Handout Module6Документ69 страницHandout Module6Oana MirceaОценок пока нет

- Total Elbow Arthroplasty and RehabilitationДокумент5 страницTotal Elbow Arthroplasty and RehabilitationMarina EОценок пока нет

- Tcu Module Pe1 Lesson 1Документ7 страницTcu Module Pe1 Lesson 1Remerata, ArcelynОценок пока нет

- What Has The Government and The Department of Health Done To Address To The Issues of Reproductive and Sexual Health?Документ5 страницWhat Has The Government and The Department of Health Done To Address To The Issues of Reproductive and Sexual Health?Rica machells DaydaОценок пока нет

- Cleaning of Contact Points and Wiring HarnessesДокумент3 страницыCleaning of Contact Points and Wiring HarnessesRafa Montes MOralesОценок пока нет

- Fundamental Molecular Biology: GenomesДокумент45 страницFundamental Molecular Biology: GenomesMoonHoLeeОценок пока нет

- Improving The Livelihoods of Smallholder Fruit Farmers in Soroti District, Teso Sub Region, Eastern Uganda RegionДокумент2 страницыImproving The Livelihoods of Smallholder Fruit Farmers in Soroti District, Teso Sub Region, Eastern Uganda RegionPatricia AngatoОценок пока нет

- ANATOMY 1 NILEM and Cat FISHДокумент19 страницANATOMY 1 NILEM and Cat FISHAnisatul Khabibah ZaenОценок пока нет

- Paterno Report: Dr. Fred S. Berlin, M.D., PH.D Final Report 2-7-2013Документ45 страницPaterno Report: Dr. Fred S. Berlin, M.D., PH.D Final Report 2-7-2013The Morning CallОценок пока нет

- Experiment Number 16 Formal ReportДокумент4 страницыExperiment Number 16 Formal Reportapi-524547303Оценок пока нет

- Sol. Mock Test CBSE BiologyДокумент3 страницыSol. Mock Test CBSE BiologysbarathiОценок пока нет

- Chapter 03Документ35 страницChapter 03david jenil nabuaОценок пока нет

- LECTURE NOTES-EAT 359 (Water Resources Engineering) - Lecture 1 - StudentДокумент32 страницыLECTURE NOTES-EAT 359 (Water Resources Engineering) - Lecture 1 - StudentmusabОценок пока нет

- B - Cracked Tooth SyndromeДокумент8 страницB - Cracked Tooth SyndromeDavid TaylorОценок пока нет

- Carolyn Green Release FinalДокумент3 страницыCarolyn Green Release FinalAlex MilesОценок пока нет

- Composite Restorations: Dr. Dina NouriДокумент38 страницComposite Restorations: Dr. Dina NouriCatherine LoyolaОценок пока нет

- Buss 37 ZemaljaДокумент50 страницBuss 37 ZemaljaOlga KovacevicОценок пока нет

- E-Kabin - O Series - Monoblock Enclosure - ENGДокумент12 страницE-Kabin - O Series - Monoblock Enclosure - ENGCatalina CocoşОценок пока нет