Академический Документы

Профессиональный Документы

Культура Документы

Hazards in Digital Logic and Switching

Загружено:

Ayush MukherjeeАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Hazards in Digital Logic and Switching

Загружено:

Ayush MukherjeeАвторское право:

Доступные форматы

Hazards

o A

hazard

is

a

momentary

unwanted

switching

transient

at

a

logic

func?on s

output

(i.e.,

a

glitch).

o Hazards/glitches

occur

due

to

unequal

propaga?on

delays

along

different

paths

in

a

combina?onal

circuit.

o Can

take

steps

to

try

and

eliminate

hazards.

o There are two types of hazards; sta,c and dynamic.

o For

asynchronous

circuits

in

par,cular,

hazards

can

cause

problems

in

addi,on

to

other

issues

like

races

and

non-‐fundamental

mode

opera,on!

n Momentary

false

logic

func2on

values

in

an

asynchronous

circuit

can

cause

a

transi2on

to

an

incorrect

stable

state!

ECE124 Digital Circuits and Systems Page 1

Sta?c hazards

o Sta?c-‐0 Hazard:

n Occurs

when

output

is

0

and

should

remain

at

0,

but

temporarily

switches

to

a

1

due

to

a

change

in

an

input.

o Sta?c-‐1 Hazard:

n Occurs

when

output

is

1

and

should

remain

at

1,

but

temporarily

switches

to

a

0

due

to

a

change

in

an

input.

1 1

0 0

static-0 hazard (0->0) static-1 hazard (1->1)

ECE124 Digital Circuits and Systems Page 2

Dynamic hazards

o Dynamic Hazard:

n Occurs

when

an

input

changes,

and

a

circuit

output

should

change

0

-‐>

1

or

1

-‐>

0,

but

temporarily

flips

between

values.

1 1

0 0

dynamic hazard (0->1) dynamic hazard (1->0)

ECE124 Digital Circuits and Systems Page 3

Illustra?on

o Consider the following circuit with 1 a AND1

1

delays where only one input (input b 1->0

1->0

b) changes… 10->1 1 f=ab+b'c

INV 1->???

o Draw a ?ming diagram to see what 1 0->1

happens at output with delays. 1 c AND2

o From the logic expression, we see

that b changing should result in the b

output remaining at logic level 1…

o Due to delay, the output goes 1-‐>0-‐ INV

>1 and this is an output glitch; we

see a sta,c-‐1 hazard. AND1

AND2

OUTPUT GLITCH!!!

ECE124 Digital Circuits and Systems Page 4

Fixing hazards (2-‐level circuits) (1)

o When circuits are implemented as 2-‐level SOP (2-‐level POS), we can detect and

remove hazards by inspec?ng the K-‐Map and adding redundant product (sum) terms.

bc

00 01 11 10

a

0 0 1 0 0

1 0 1 1 1

f=ab+b'c

o Observe

that

when

input

b

changes

from

1-‐>0

(as

in

the

previous

?ming

diagram),

that

we

jump

from

one

product

term

to

another

product

term.

n If

adjacent

minterms

are

not

covered

by

the

same

product

term,

then

a

HAZARD

EXISTS!!!

ECE124 Digital Circuits and Systems Page 5

Fixing hazards (2-‐level circuits) (1)

bc

00 01 11 10

a

0 0 1 0 0

1 0 1 1 1

f=ab+b'c + ac

o The

extra

product

term

does

not

include

the

changing

input

variable,

and

therefore

serves

to

prevent

possible

momentary

output

glitches

due

to

this

variable.

ECE124 Digital Circuits and Systems Page 6

Fixing hazards (2-‐level circuits) (3)

o The redundant product term is not influenced by the changing input.

1 a AND1

b

1->0

INV AND2 1->1

1 c f=ab+b'c+ac

AND3

1->1

ECE124 Digital Circuits and Systems Page 7

Fixing hazards (2-‐level circuits) (4)

o For 2-‐level circuits, if we remove all sta?c-‐1 hazards using the K-‐Map (adding

redundant product terms), we are guaranteed that there will be no sta?c-‐0 hazards or

dynamic hazards.

o If

we

work

with

Product-‐Of-‐Sums,

we

might

find

sta?c-‐0

hazards

when

moving

from

one

sum

term

to

another

sum

term.

We

can

remove

these

hazards

by

adding

redundant

sum-‐terms.

ECE124 Digital Circuits and Systems Page 8

Hazards in asynchronous circuits

o Consider our first circuit with a hazard, but assume it is not combinatorial, but rather

asynchronous.

o We

can

draw

the

transi?on

table,

and

see

that

there

is

the

poten?al

to

end

up

in

an

incorrect

stable

state.

1 a curr

1->0 next state output

b state

1->0 Y=ab+b'y

ab=00 01 11 10

y Y Y Y Y

y 0 0 0 1 0 0

1 1 0 1 1 1

ECE124 Digital Circuits and Systems Page 9

Hazards in mul?-‐level circuits (1)

o 2-‐level circuits are easy to deal with and hazards can be removed…

o The

situa?on

is

harder

with

mul?-‐level

circuits

in

which

there

are

mul?ple

paths

from

an

input

to

an

output:

0->1 x

a 1

w 1->0->1

1 1 f

1b y

1->0 1 0->1 0->1->0->1

1c 1->0

1

1d z

ECE124 Digital Circuits and Systems Page 10

Hazards in mul?-‐level circuits (2)

o Timing diagram shows output changing 0-‐>1-‐>0-‐>1.

o Hazards

like

this

are

hard

to

fix.

We

could

always

find

a

2-‐level

circuit

of

the

previous

circuit

and

get

something

hazard

free…

ECE124 Digital Circuits and Systems Page 11

Fixing hazards with latches (1)

o Can also fix hazards using SR or S R latches.

n An SR Latch can tolerate momentary 0s appearing at its inputs (since we might momentarily move

from a set or reset to a hold and then back).

n An S R Latch can tolerate momentary 1s appearing at its inputs (since we might momentarily move

from a set or reset to a hold and then back):

R (reset) Q S (set) Q

S (set) !Q R (reset) !Q

ECE124 Digital Circuits and Systems Page 12

Fixing hazards with latches (2)

o Consider our original circuit with a sta?c-‐1 hazard (temporary 0 at output):

1 a bc

b 00 01 11 10

1->0 a

f=ab+b'c 0 0 1 0 0

1 0 1 1 1

1 c f=ab+b'c

ECE124 Digital Circuits and Systems Page 13

Fixing hazards with latches (3)

o Consider that we take our output f from the output of a latch.

o Since

we

are

trying

to

fix

sta?c-‐1

hazards

we

need

to

be

able

to

tolerate

momentary

0s

at

latch

inputs

=>

Use

a

SR

Latch

(NOR

Latch).

o To

get

the

func?on

f

from

the

latch

output,

we

need

equa?ons

for

S

and

R

of

the

latch

(so

that

the

latch

gets

SET

when

f

should

be

one,

otherwise

RESET).

bc bc

00 01 11 10 00 01 11 10

a a

0 0 1 0 0 0 1 0 1 1

1 0 1 1 1 1 1 0 0 0

Equation for S Equation for R

ECE124 Digital Circuits and Systems Page 14

Fixing hazards with latches (5)

o Draw a circuit using the latch, and see that glitch in output due to the hazard is gone.

1 a 0->0

b

1->0 R

0->0 f

1->1

1 c 0->0

1->0

S

0->0

1->1

1->0->1

0->1

ECE124 Digital Circuits and Systems Page 15

Output assignment in asynchronous circuits

o Flow and transi?on tables might have unspecified entries for circuit outputs.

n This might be a result of the fundamental mode assump?on.

n This might be a result of unstable states.

o Note: we always have output values assigned for stable states!

o We

should

think

about

the

what

happens

with

the

unspecified

output

values…

n They

are,

in

effect,

don t

cares

that

we

can

exploit

during

minimiza?on

of

the

output

logic

equa?ons.

n But,

we

might

temporarily

pass

through

these

values

while

transi?oning

from

one

stable

state

to

another

stable

state.

o Depending

on

the

output

equa?ons

that

we

derive

(due

to

minimiza?on

of

the

output

equa?ons),

we

might

end

up

having

glitches

at

our

circuit

outputs.

n Glitches

are

bad;

they

could

get

fed

into

another

circuit

causing

problems.

They

also

waste

power.

ECE124 Digital Circuits and Systems Page 16

Avoiding output glitches

o Consider the following flow table with don t cares at some outputs (circuit has one

input and one output): next state output

curr

state x=0 x=1 x=0 x=1

a a b 0 -

b c b - 0

c c d 1 -

d a d - 1

o Consider

a

transi?on

between

two

stable

states

due

to

a

change

in

an

input

value

and

how

it

might

be

best

to

assign

the

don t

care

value

in

an

unstable

intermediate

state:

n If

both

stable

states

produce

a

0

output,

make

output

0

instead

of

a

don t

care.

n If

both

stable

states

produce

a

1

output,

make

output

1

instead

of

a

don t

care.

n If

stable

states

produce

different

outputs,

the

output

can

remain

a

don t

care

and

be

used

to

find

a

smaller

output

circuit.

o This

will

enable

us

to

avoid

output

glitches

when

passing

through

unstable

temporary

states.

ECE124 Digital Circuits and Systems Page 17

Example

o If we consider possible transi?ons, we see that some of the output don t cares

should be changed to 0 or 1 to avoid glitches.

curr next state output curr next state output

state x=0 x=1 x=0 x=1 state x=0 x=1 x=0 x=1

a a b 0 - a a b 0 0

b c b - 0 b c b - 0

c c d 1 - c c d 1 1

d a d - 1 d a d - 1

o The

above

changes

will

avoid

temporary

glitches

at

the

outputs

during

transi?ons

where

the

output

should

not

change.

ECE124 Digital Circuits and Systems Page 18

Вам также может понравиться

- EXcelДокумент7 страницEXcelMukesh Rao100% (1)

- Flip Flops and Counters: Digital Logic Design LaboratoryДокумент16 страницFlip Flops and Counters: Digital Logic Design LaboratoryTrương Quang Tường100% (1)

- Assignment 2021-22Документ2 страницыAssignment 2021-22Dan Ojwang100% (2)

- Priority EncoderДокумент11 страницPriority Encodershivam007Оценок пока нет

- VLSI - Carry Lookahead AdderДокумент12 страницVLSI - Carry Lookahead AdderK.R.RaguramОценок пока нет

- MSDFFДокумент20 страницMSDFFShweta KumariОценок пока нет

- Electronics Circuits Lab ManualДокумент109 страницElectronics Circuits Lab ManualIndische Mädchen100% (2)

- Unit 2 - Signal SystemДокумент69 страницUnit 2 - Signal SystemAnitha DenisОценок пока нет

- Introduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadДокумент117 страницIntroduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadEnGr Asad Hayat BanGashОценок пока нет

- Stucor CS3351-GKДокумент269 страницStucor CS3351-GKNightdive StudiosОценок пока нет

- Analog ElectronicsДокумент194 страницыAnalog Electronicsshubhamranjan131317Оценок пока нет

- Thevenins and NortonsДокумент26 страницThevenins and NortonsKishan SinghОценок пока нет

- Facilities Required To Do The Experiment:: Loading Effect of PotentiometerДокумент5 страницFacilities Required To Do The Experiment:: Loading Effect of PotentiometerRohan MohataОценок пока нет

- Digital System Module 4 PDFДокумент52 страницыDigital System Module 4 PDFGeethanjali.pОценок пока нет

- Q4Документ3 страницыQ4SkvkОценок пока нет

- Summary of The Types of FlipДокумент1 страницаSummary of The Types of FlipPola RismaОценок пока нет

- Lession-40 - Load-Commutated Current Source Inverter (CSI)Документ8 страницLession-40 - Load-Commutated Current Source Inverter (CSI)Sangeetha DurairajuОценок пока нет

- Me2255 Electronics and Microprocessor Anna University Question BankДокумент6 страницMe2255 Electronics and Microprocessor Anna University Question BankMayakannan RОценок пока нет

- Electronic Devices and CircuitsДокумент4 страницыElectronic Devices and CircuitsSudalai MadanОценок пока нет

- 2.4 DC Characteristics of OpampДокумент23 страницы2.4 DC Characteristics of OpampMichael CampbellОценок пока нет

- Cmos ComparatorДокумент26 страницCmos Comparatorvipul4792100% (3)

- Operational Amplifiers Questions and AnswersДокумент4 страницыOperational Amplifiers Questions and AnswersSuresh L100% (1)

- Experiment No. 01 Experiment Name-ASK ModulationДокумент47 страницExperiment No. 01 Experiment Name-ASK ModulationmuskanОценок пока нет

- Flipflops: Technical Seminar ReportДокумент16 страницFlipflops: Technical Seminar ReportrachitОценок пока нет

- Control System Question BankДокумент3 страницыControl System Question Bankmanish_iitrОценок пока нет

- Fuzzy Logic History and ApplicationsДокумент5 страницFuzzy Logic History and ApplicationsYossry AwadОценок пока нет

- Lecture 6 Gajski Kuhn Y ChartДокумент18 страницLecture 6 Gajski Kuhn Y ChartShiraz HusainОценок пока нет

- Linear and Digital Integrated Circuits Question BankДокумент8 страницLinear and Digital Integrated Circuits Question Bankdhanaram100% (1)

- Differential Amplifier Using BJTДокумент11 страницDifferential Amplifier Using BJTAssini HussainОценок пока нет

- 8086 Microprocessor Lab 1Документ7 страниц8086 Microprocessor Lab 1Tyler BarneyОценок пока нет

- ε-NFA to NFA ConversionДокумент14 страницε-NFA to NFA ConversionKhushbul AlamОценок пока нет

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Документ13 страницPMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarОценок пока нет

- Summary of The Types of FlipДокумент3 страницыSummary of The Types of FlipAnonymous BjaA0IiYОценок пока нет

- Practise Problems For Sequential CircuitsДокумент11 страницPractise Problems For Sequential CircuitsVaibhav KolseОценок пока нет

- Adders and MultipliersДокумент59 страницAdders and Multipliersdbanbumani_501791840Оценок пока нет

- Vishwanathrao Deshpande Institute of Technology, Haliyal: in Today'sДокумент8 страницVishwanathrao Deshpande Institute of Technology, Haliyal: in Today'sAnonymous VASS3z0wTH100% (1)

- Lab Report Electronics 5thДокумент18 страницLab Report Electronics 5thMuhammad kawish iqbal100% (1)

- 1semexam 2015Документ185 страниц1semexam 2015Cham Raul100% (1)

- Implementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan KhalidДокумент7 страницImplementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan KhalidchachunasayanОценок пока нет

- BS Lab ManualДокумент76 страницBS Lab ManualWasim100% (1)

- DLD Lab Manual 7 FlipFlopsДокумент6 страницDLD Lab Manual 7 FlipFlopsHanzala NasirОценок пока нет

- Eletronics Lab Report - TTLДокумент2 страницыEletronics Lab Report - TTLThan Lwin AungОценок пока нет

- Decoder TocciДокумент25 страницDecoder ToccimohitОценок пока нет

- 2-Lecture Notes Lesson4 4Документ10 страниц2-Lecture Notes Lesson4 4kstu1112Оценок пока нет

- 8.1 Finite Word Length EffectsДокумент18 страниц8.1 Finite Word Length EffectsRajaMandapatiОценок пока нет

- Carry Skip AdderДокумент9 страницCarry Skip AdderSimranjeet SinghОценок пока нет

- Exponential Fourier SeriesДокумент4 страницыExponential Fourier SeriesMasuma Anjum ParthimaОценок пока нет

- EDI LAb ManualДокумент33 страницыEDI LAb ManualMadangle JungleОценок пока нет

- EE8461-Linear and Digital Integrated Circuits-Lab ManualДокумент96 страницEE8461-Linear and Digital Integrated Circuits-Lab ManualSETNHILОценок пока нет

- Ee 2254 Linear Integrated Circuits and Applications Anna University Previous Year Question PaperДокумент2 страницыEe 2254 Linear Integrated Circuits and Applications Anna University Previous Year Question Paperkibrom atsbhaОценок пока нет

- Design and Analysis of An Inset Feed X-Band Microstrip Patch AntennaДокумент74 страницыDesign and Analysis of An Inset Feed X-Band Microstrip Patch AntennaNasiruzzaman NahidОценок пока нет

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyДокумент5 страницLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Lab-09 and 10 PDFДокумент14 страницLab-09 and 10 PDFAman RashdiОценок пока нет

- PTSP Subjective QuestionsДокумент5 страницPTSP Subjective QuestionsmanikrishnaswamyОценок пока нет

- Fpga ManualДокумент7 страницFpga ManualRahul SharmaОценок пока нет

- Digital Electronics Circuits: Experiment: 9Документ4 страницыDigital Electronics Circuits: Experiment: 9movabОценок пока нет

- Opamp DesignДокумент60 страницOpamp DesignSiva KumarОценок пока нет

- Signals and Systems: BooksДокумент1 страницаSignals and Systems: Booksfaizan bariОценок пока нет

- Lab ManualДокумент66 страницLab ManualcommunicationridersОценок пока нет

- Unit2 Topic7 HazardsДокумент13 страницUnit2 Topic7 HazardsHari Kumar N CОценок пока нет

- DSP U2Документ11 страницDSP U2Ayush MukherjeeОценок пока нет

- 32 Bit Full Adder: PurposeДокумент5 страниц32 Bit Full Adder: PurposeAyush MukherjeeОценок пока нет

- Ecuaciones Diferenciales de 2 OrdenДокумент45 страницEcuaciones Diferenciales de 2 OrdenJuan Jose Flores FiallosОценок пока нет

- Basics of MOSFET - QuestionsДокумент6 страницBasics of MOSFET - QuestionsAyush MukherjeeОценок пока нет

- Digital Electronics Question Bank, Digital Electronics 2 Mark Questions & AnswersДокумент22 страницыDigital Electronics Question Bank, Digital Electronics 2 Mark Questions & Answerssaipradeepkp92% (74)

- Java Fundamentals NotesДокумент62 страницыJava Fundamentals NotesAyush MukherjeeОценок пока нет

- Semiconductors Module 01Документ9 страницSemiconductors Module 01Rodolfo BetanzosОценок пока нет

- Question Paper IIT 2012Документ1 страницаQuestion Paper IIT 2012Ayush MukherjeeОценок пока нет

- Chapter 6 MOSFETДокумент39 страницChapter 6 MOSFETAyush MukherjeeОценок пока нет

- Semiconductors Module 01Документ9 страницSemiconductors Module 01Rodolfo BetanzosОценок пока нет

- Valkenburg Chapter 1 SolutionsДокумент7 страницValkenburg Chapter 1 SolutionsAyush MukherjeeОценок пока нет

- NYOUG 2016 Whats New Data PumpДокумент27 страницNYOUG 2016 Whats New Data Pumpsherif adfОценок пока нет

- 02-Steps To Analyze AWR Report in OracleДокумент8 страниц02-Steps To Analyze AWR Report in OracleAnonymous 8RhRm6Eo7hОценок пока нет

- CBM292 - 293 Service ManualДокумент26 страницCBM292 - 293 Service ManualHaïthem BEN SALEMОценок пока нет

- TILE-Gx8072 ProcessorДокумент2 страницыTILE-Gx8072 Processorraees74Оценок пока нет

- Parallel Computers Networking PDFДокумент48 страницParallel Computers Networking PDFHemprasad BadgujarОценок пока нет

- SQL Server More Clause Part 2Документ9 страницSQL Server More Clause Part 2Melisa May Ocampo AmpiloquioОценок пока нет

- Claim Digger Baseline Schedule VДокумент28 страницClaim Digger Baseline Schedule VDilip KumarОценок пока нет

- Spring Security WhitepaperДокумент7 страницSpring Security WhitepaperMamat LepakОценок пока нет

- Gigabyte Confidential Do Not Copy: Model Name: 965P-DS3Документ35 страницGigabyte Confidential Do Not Copy: Model Name: 965P-DS3CarlosAlbertoRiosОценок пока нет

- SSAD Assignment 5 Team ID 29Документ7 страницSSAD Assignment 5 Team ID 29Shivani JainОценок пока нет

- Ceragon FibeAir IP-20C Datasheet ETSI Rev A.03Документ6 страницCeragon FibeAir IP-20C Datasheet ETSI Rev A.03Francisco RomanoОценок пока нет

- Erro 11-05Документ852 страницыErro 11-05matheus felipeОценок пока нет

- Vendor Wira Makmur PratamaДокумент1 страницаVendor Wira Makmur PratamaferyОценок пока нет

- Sp3d-Electrical ProcedureДокумент22 страницыSp3d-Electrical Procedurerithesh.kОценок пока нет

- Avamar Staging Tape Out Outputting Avamar Backups To Tape Technical Note PDFДокумент39 страницAvamar Staging Tape Out Outputting Avamar Backups To Tape Technical Note PDFSyedZulhilmiОценок пока нет

- # C4-Catalog - Equipment PDFДокумент52 страницы# C4-Catalog - Equipment PDFKomang Darmawan100% (1)

- PracticalsДокумент15 страницPracticalsmosesОценок пока нет

- How Control Korg Krome With An External Midi ControllerДокумент8 страницHow Control Korg Krome With An External Midi ControllerY FelixОценок пока нет

- Agent Installation Strategy: Solution Manager 7.2Документ22 страницыAgent Installation Strategy: Solution Manager 7.2Fernando Carlos LeaОценок пока нет

- 233 Sites ABIA Optimization - 20220329Документ36 страниц233 Sites ABIA Optimization - 20220329Senetor Brian BakariОценок пока нет

- 16 Kundeninfo enДокумент7 страниц16 Kundeninfo enanil nsОценок пока нет

- Wpa Cli With Wpa SupplicantДокумент7 страницWpa Cli With Wpa SupplicantCyber BellaaОценок пока нет

- Automated Attendance Based On Facial Recognition Using Matlab and ArduinoДокумент69 страницAutomated Attendance Based On Facial Recognition Using Matlab and ArduinoGhana Kiran100% (1)

- Hi-Pe: High Performance Walk-Through Multi-Zone Metal DetectorДокумент6 страницHi-Pe: High Performance Walk-Through Multi-Zone Metal DetectorKhaled ElSaeedОценок пока нет

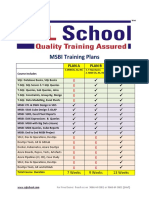

- MSBI Training Plans: Plan A Plan B Plan CДокумент14 страницMSBI Training Plans: Plan A Plan B Plan CVeerendra ReddyОценок пока нет

- Object Oriented DesignДокумент37 страницObject Oriented DesignGanesh ThapaОценок пока нет

- Course Guide-CMSC311Документ5 страницCourse Guide-CMSC311Mark BernardinoОценок пока нет

- Java Applet: Presented By: Feng LiuДокумент15 страницJava Applet: Presented By: Feng LiulalitОценок пока нет

- Market Basket Analysis Using Improved FP-treeДокумент4 страницыMarket Basket Analysis Using Improved FP-treeIIR indiaОценок пока нет