Академический Документы

Профессиональный Документы

Культура Документы

The Most Significant MOSFET Parameters Impact in CMOS Inverter Switching Characteristics

Загружено:

Ahood ZamanОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

The Most Significant MOSFET Parameters Impact in CMOS Inverter Switching Characteristics

Загружено:

Ahood ZamanАвторское право:

Доступные форматы

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

The most significant MOSFET parameters

impact in CMOS inverter switching

characteristics

Milaim Zabeli, Nebi Caka, Myzafere Limani, Qamil Kabashi*

inversion potential (|2øF|) and the channel-length parameter

Abstract - The objective of this paper is to research the impact of (λ). Whereas some of physical parameters of the

electrical and physical parameters that characterize the complementary MOSFET transistors are: the surface mobility

complementary MOSFETs (NMOS and PMOS transistors) in the (µ), the thin oxide thickness (t0x) and substrate doping (Nb).

dynamic behaviour (time-domain) of the CMOS inverter. In addition The values of all these parameters depend on the fabrication

to this, the paper also aims at exploring the directives that are to be

process technology. The MOSFET transistors also characterize

followed during the design phase of the CMOS inverters that enable

designers to design the CMOS inverters with the best possible

a considerable number of other parameters, which should be

dynamic performance, depending on operation conditions. The taken into consideration for specific cases of device operation,

CMOS inverter designed with the best possible dynamic features also but their impact in overall performance of the MOSFETs will

enables the designing of the CMOS logic circuits with the best be less meaningful.

possible dynamic performance, according to the operation conditions If during fabrication process of MOSFET transistors the

and designers’ requirements. their electrical and physical parameters are selected by desired

values dictated by technology process, the MOSFET device

Keywords - CMOS-inverter, load capacitance, NMOS transistor, behaviour can be controlled according designer’s needs,

PMOS transistor, propagation delay time, power supply current, depending on their application in digital circuits [7]. By

threshold voltage, transconductance parameter. controlling the complementary MOSFET transistor behaviour

will be able controlled the CMOS inverter.

I. INTRODUCTION The manuscript objective is to investigate the some typical

The CMOS inverter represents fundamental block of the MOSFET transistors parameters that have the most

CMOS digital integrated circuits based on CMOS inverter [1]. significance impact in dynamic (time-domain) behavior of the

The switching characteristic (time-domain behaviour) of the CMOS inverter, although the switching characteristics of the

CMOS inverter, essentially determine the overall operating CMOS digital circuits and in particular of CMOS inverter

speed of CMOS digital circuits. The dynamic (time-domain) circuits, essentially determine the overall operating seed of

performance requirements of CMOS digital systems are digital systems in common. Therefore, the switching

usually among the most important specifications that must be characteristics of CMOS inverter must be estimated and

taken into consideration during the design phase by circuits’ optimized very early in the design phase. Using analytical and

designer [2], [3]. Therefore the dynamic (transient) behaviour numerical methods supported with the circuit simulator

of the circuit must be estimated and optimized by designer (SPICE) usually provides a very accurate estimate of the

during the design phase. The CMOS inverter structure consists CMOS time-domain behavior.

of a pair of complementary MOSFETs (of an enhancement

type NMOS transistor and an enhancement type PMOS

transistor, because this type of MOSFET have better

performance compared to depletion type of MOSFETs), which

operate in complementary mode. The CMOS inverter circuit is

shown in Fig. 1 [4]-[6].

Both complementary MOS transistors (MOSFETs) are

characterized by electrical and physical parameters, which

determine the behaviour of the CMOS inverter in dynamic

(switching) and static condition of operation. Several of the

main electrical parameters which characterize the

complementary MOSFET transistors are: the process

transconductance parameter (k’), the zero-bias threshold

voltage (Vt0), the body-effect parameter (γ), the surface Fig. 1 The structure of the CMOS inverter which contains two

complementary MOS enhancement-type transistors.

*

Corresponding Author: Qamil Kabashi, e-mail: qamil.kabashi@uni-pr.edu

ISSN: 1998-4464 565

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

II. THE ROLE OF THE COMPLEMENTARY MOSFET (NMOS AND n - number of identical stages (the CMOS inverters) connected

PMOS) TRANSISTORS PARAMETERS IN DELAY TIME OF THE CMOS at the output.

INVERTERS

For transient response of the CMOS inverter have to In load capacitance expression are not included some of

determine the nature and the amount of parasitic capacitances parasitic capacitances shown in Fig. 3, because have no effect

associated with the complementary MOSFET transistors, on the dynamic behavior of the CMOS inverter. The factor 2

where their values are determined by layout geometries and the arises before parasitic capacitances Cgd,n and Cgd,p as result of

manufacturing processes. The most of these parasitic the Miller effect, which will have impact in CMOS inverter

capacitances are distributed, and for simplification the dynamic performance, or in time delays. This effect can

problem, we first combine into an equivalent lumped linear minimized if during design phase of the CMOS inverter, the

capacitance. parasitic capacitances Cdb of the complementary MOSFETs

The speed of the CMOS inverter operation is determined are minimized.

by propagation delay time of the CMOS inverter. To analyse

the switching operation of the CMOS inverter to determine its

delay time (or propagation delay time), there will be used

CMOS inverter with an equivalent lumped linear capacitance,

connected between the output node and ground, as in Fig. 2

[8], [9].

Fig. 3 The CMOS inverter associated with its parasitic

capacitances, the lumped interconnect capacitance and load

capacitance for analyzing the propagation delay.

In Fig. 4 is shown the CMOS inverter circuits with the

equivalent load capacitance for analyzing the propagation

Fig. 2 The CMOS inverter with an equivalent lumped delay time, when the problem of analyzing time-domain

capacitance (equivalent lumped linear capacitance) at the behavior is simplified. Now, the CMOS inverter switching

output node characteristics are reduced to finding the charge-up and

charge-down times of the load capacitance through one

The value of the equivalent lumped capacitance is MOSFET transistor [4].

calculated by using parasitic capacitances of the NMOS and

PMOS transistors, the lumped interconnect capacitance and

input capacitance of load device (one or more identical CMOS

inverter, fan-out parameter) connected at the output of the

CMOS inverter, as in Fig. 3. The equivalent lumped

capacitance at the output node will be called the load

capacitance Cl, and it can be estimate by expression [4], [9],

[10]:

Cl = 2C gd ,n + 2C gd , p + Cdb ,n + Cdb , p + Cint + nC g (1)

Cgd,n - the gate-drain capacitance of the NMOS

Cgd,p - the gate-drain capacitance of the PMOS

Cdb,n - the drain-body capacitance of the NMOS

Cdb,p - the drain-body capacitance of the PMOS

Cint - the lumped interconnect capacitance

Cg - the input parasitic capacitance of load (the oxide-related Fig. 4 CMOS inverter with an equivalent lumped (combined)

capacitances) load capacitance

ISSN: 1998-4464 566

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

The propagation delay times can be found by using the state 1.6 Cl (6)

t PLH =

equation of the output node in the time domain with acceptable k pVDD

accuracy, as:

The inverter propagation delay time (tP) is defined as the

dV

C o = iC = iD , p − iD ,n (2) average of propagation delay times:

dt

1

For calculating the propagation delay time tPHL tP = (t PHL + t PLH ) (7)

(propagation delay time of the output voltage during high-to- 2

low transition), when the input voltage switches from low-to-

high, the NMOS transistor is turned on and it starts to The dynamic power dissipation has two components, the

discharge the equivalent load capacitance, whereas the PMOS first component is due of current which flows through the

transistor is cut off. After calculation depending on mode series of connection of NMOS and PMOS transistors, and

operation of the NMOS transistor (the NMOS transistor will current peaks is at the switching threshold voltage of CMOS

operates in the saturation region when the Vo>VOH - Vt0,n, inverter (for a symmetric case the threshold voltage of the

whereas for Vo ≤ VOH - Vt0,n the NMOS operates in the linear CMOS inverter is Vth = VDD/2). However, the second

region) of the CMOS inverter, and by combining these two component of dynamic power dissipation is more significant

separated intervals can be achieved the expression of the component, results from the current that flows in NMOS and

propagation delay [4]: PMOS transistors when the CMOS inverter is loaded by load

capacitance. Now if the CMOS inverter is switching by

periodic input voltage pluses with negligible rise and fall

Cl 2Vt 0, n 4(VDD − Vt 0, n ) (3)

t PHL = + ln − 1 times, the average dynamic power dissipation in CMOS

kn (VDD − Vt 0, n ) VDD − Vt 0, n VDD + VOL inverter will be:

For calculating the propagation delay time tPLH PD = fClVDD

2

(8)

(propagation delay time of the output voltage during low-to-

high transition) when the input voltage switches from high-to- Now, it is clear that the average dynamic power dissipation

low, the PMOS transistor is turned on and it starts to charge up of the CMOS inverter is proportional to the switching

the equivalent load capacitance, whereas the NMOS transistor frequency (f). Hence, the low-power advantage of CMOS

is cut off. After calculation depending on mode operation of circuits at the higher switching frequency becomes prominent.

the PMOS transistor (following a similar derivation procedure, Also, the maximal operation frequency of the CMOS inverter

as for calculating the propagation delay time tPHL) of the is related to the propagation delay. The average switching

CMOS inverter can be achieved the expression [4], [8]: power dissipation estimate by expression (8) will hold for the

CMOS inverter, when the leakage power is neglected.

Cl 2 | Vt 0, p | 4(VDD − | Vt 0, p |) (4) Under the realistic conditions, when the input voltage pulses

t PLH = + ln − 1

k p (VDD − | Vt 0, p |) VDD − | Vt 0, p | VDD (deviates from ideal step pulses) have nonzero rise and fall

times, both MOSFET (NMOS and PMOS) transistors will

From the expression of the propagation delay time tPHL, it simultaneously conduct (or both transistors temporarily form a

is indicated that the impact on its value will have equivalent conducting path between VDD and the ground, when input

load capacitance (Cl), the value of the power-supply voltage voltage is near the threshold voltage of the CMOS inverter) a

(VDD), the value of transconductance parameter of the NMOS certain amount of current (the short-circuit current), which

transistor (kn) and the value of the NMOS threshold voltage gives rise to dynamic power dissipation in the CMOS inverter.

(Vt0,n). Whereas from the expression of the propagation delay For this reason the dynamic power expression (8) it has to add

time tPLH, it is indicated that the impact on its values will have the additional dynamic power dissipation, which is due to the

equivalent load capacitance (Cl), the value of the power-supply short-circuits current. But, when the load capacitance has

voltage (VDD), the value of transconductance parameter of the higher values, the dynamic power dissipation term which is

PMOS transistor (kp) and the value of the PMOS threshold due to the short-circuit current become negligible in

voltage (Vt0,p). Therefore, the determining parameters of the comparison the dynamic power dissipation term which is due

propagation delay time tPHL are the electrical and physical the loaded a load capacitance [11], [12].

parameters that characterize only the NMOS transistor, The inverter propagation delay time can be used to estimate

whereas the determining parameters of the propagation delay a fundamental parameter for measuring the quality and the

time tPLH are the electrical and physical parameters that performance of the CMOS process. This fundamental

characterize only the PMOS transistor. parameter is called the delay-power product (DP), and it can

For the usual case is assumed that Vt0,n = |Vt0,p| = 0.2VDD, write as:

the expressions reduce as in:

DP = PD t p (9)

1.6 Cl (5)

t PHL = The lower the of DP product the more effective is the

k nVDD technology, which is used for fabrication device.

ISSN: 1998-4464 567

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

III. RESULTS AND DISCUSSION

The dependence of the CMOS propagation delay time tPLH

on the NMOS transistor transconductance parameter (kn) for

two different (parametric) values of the NMOS transistor

threshold voltage (Vt0,n) and other values remains constant.

This is shown in Fig. 5.

The results presented through curves in Fig. 5 indicate the

following: for higher values of the NMOS transconductance

parameter (kn) in CMOS inverter, the propagation delay time

tPHL (the propagation delay time during output voltage

transition from high-to-low level) will be lower. Also, the

smaller value of the NMOS threshold voltage (Vt0,n) will result Fig. 6 The waveforms of output voltage for there different

in lower values of the propagation delay time tPHL, with a more cases of the complementary MOS transconductance

significant impact for the lower values of the NMOS parameters ratio (kn/kp), when the CMOS inverter drives by the

transconductance parameter (kn). ideal pulse and equivalent load capacitance Cl = 1pF, as well

the NMOS transconductance parameter (kn) holds same.

From the time waveforms presented in Fig. 6, it is indicated

that for symmetric cases (kn = kp), the propagation delay times

during low-to-high and high-to-high transition of the output

voltage in CMOS inverter are equal (tPLH = tPHL), whereas in

other cases of the transconductance parameters ratio (kn/kp) the

propagation delay times are asymmetrical. When kn > kp the

propagation delay time tPHL is lower than propagation delay

time tPLH (tPHL < tPLH), and for kn < kp the propagation delay

time tPHL is higher than the propagation delay time tPLH (tPHL >

tPLH).

Significant impact on propagation delay times has the load

Fig. 5 The dependence of propagation delay time tPHL in the capacitance connected at the output of the CMOS inverter

CMOS inverter on the NMOS transconductance parameter (kn) (when load capacitance (fan-out effect) connected at the output

for two different values of NMOS threshold voltage (Vt0,n), of the CMOS inverter is dominant term in the equivalent load

when Cl = 0.1 pF and VDD = 2.5 V. capacitance, or extrinsic terms are dominant). The role of the

output load capacitance (fan-out) in delay times is shown in

The dependence of the CMOS propagation delay time tPLH Fig. 7 by the waveforms of the time response of the output

(the propagation delay time during output voltage transition voltage at the output of the symmetric CMOS inverter for three

from low-to-high level) on the transconductance parameter of different values of equivalent load capacitance, when the

the PMOS transistor (kp), for two parametric values of the CMOS inverter is driven ideal pulse. Form the waveforms of

PMOS threshold voltage (by absolute value of the PMOS the time response in Fig. 7, it is indicated that the higher

threshold voltage Vt0,p), and other values remains constant and values of the equivalent load capacitance will result in higher

it is same as the dependence of propagation delay time tPLH in values of the propagation delays during the transition of the

Fig. 5. output voltage in the CMOS inverter. Since the speed of the

For the same dimensions of NMOS and PMOS transistors operation of the CMOS inverter depends of its propagation

(complementary MOS transistors) propagation delay time in delay time, then the higher values of the propagation delay

the CMOS inverter are asymmetrical tPLH > tPHL (because time will result in low speed of the CMOS inverter operation.

kn>kp). While, for symmetrical (matching) conditions (kn= kp), When the combined output load capacitance is mainly

the propagation delay times in the CMOS inverter are equal dominated by its extrinsic components (which are not very

(tPHL = tPLH). In usual cases the maximal operation frequency sensitive to the NMOS and PMOS device dimensions), the

in CMOS inverter circuits is determined by maximal value of directive to increase the operation speed (decrease the

propagation delay times. propagation delay time) of the CMOS inverter is by designing

The time response waveforms of the output voltage during the NMOS and PMOS transistors with higher values of the

low-to-high transition and high-to-low transition for three transconductance parameters. But, the intrinsic components of

different cases of the complementary MOS transistors the combined load capacitance are increasing functions of the

transconductance parameters ratio (kn/kp), when the CMOS NMOS and PMOS transistor dimensions, Wn (the channel

inverter is driven by the ideal pulse (with zero rise and fall width of NMOS transistor) and Wn (the channel width of

times) and with equivalent load capacitance Cl =1pF, is shown PMOS transistor) [12], [13].

in Fig 6.

ISSN: 1998-4464 568

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

C l = f (W n , W p ) = C gd , n (W n ) + C gd , p (W p ) All of the propagation delay times are derived under

(10) simplified assumption that the input driven signal is an ideal

+ C db , n (W n ) + C db , p (W p ) + C int + C g pulse, but in realistic cases the waveform of the driven input

signal is not an ideal pulse. The real driven pulse at the input

The channel lengths of the NMOS and PMOS transistors in of the CMOS inverter has finite rise time (tr) and fall time (tf).

the CMOS inverters are usually equal and fixed to each other, The exact calculation of the output voltage propagation delay

determined by fabrication process, and then the channel width time is more complicated, because under these conditions both

of MOS transistor is more significant determining parameter of the NMOS transistor and PMOS transistor conduct during the

the MOS transistor transconductance parameter [14], [15]. charge-up and charge-down events. The estimation of the

Then, any effort to increase the channel width of NMOS and propagation delays of the CMOS inverter, when the driven

PMOS transistors in order to reduce propagation delay time in input signal has finite rise and fall time, can utilize the

the CMOS inverter will inevitably increase the intrinsic propagation delay time calculated by ideal pulse (step-input)

components of combined load capacitance at the output of the assumption and using the rise and fall time of the driven input

CMOS inverter. Then increasing channel width of the signal, by using the empirical expressions [4]:

complementary MOS transistors to reduce propagation delay

time, where the intrinsic capacitance terms will have 2

significant impact in equivalent load capacitance, the influence t

t PHL (reale) = t 2

PHL (ideal pulse) + r (11)

on the propagation delay time will diminish and will 2

asymptotically approach a limit value for larger values of the 2

channel width of complementary MOS transistor (the t

t PLH (reale) = t PLH

2

(ideal pulse) + f (12)

propagation delay time cannot be reduced beyond the limit 2

value). In these conditions the propagation delay times are

independent of the extrinsic capacitance components, Cint and

Cg.

When the intrinsic capacitance components are dominant on

combined load capacitance in the CMOS inverter (parasitic

capacitance components of NMOS and PMOS transistors), the

combined load capacitance will reduce by reducing the

channel width of NMOS and PMOS transistors, and

propagation delay time limit is reached for smaller values of

the NMOS and PMOS transistor channel width.

The influence of complementary MOSFET transistors

dimensions upon the propagation delay of CMOS inverter are

inherently limited by parasitic capacitances, and overall

occupied area by CMOS inverter should also be considered. In

fact, the occupied area of CMOS device is proportional to Wn Fig. 8 The waveforms of the CMOS output voltage during

and Wp, since the other MOSFET dimensions are simply kept switching conditions for ideal driver input signal and real

constant. The significant factor which used as practical driver input signal at the input of the CMOS inverter, when the

measure for quantifying design quality is the (area x equivalent load capacitance has fixed value Cl = 2pF.

propagation delay time) that takes into account for delay time

reduction [6], [15]. The impact of the rise and fall time of the driven input

signal on the waveform and propagation delay times of the

output voltage during the switching conditions in the

symmetric CMOS inverter, when the driven input signal is an

ideal pulse and when the driven input signal has a finite rise

and fall time, as well the equivalent load capacitance has a

fixed value is shown in Fig. 8.

During switching conditions in CMOS inverter, there will

be created the conduct path between the power source and the

ground under realistic conditions (the input driven signal

deviates from the ideal step pulse), through NMOS and PMOS

transistor when the input voltage is larger than Vtn,0 and smaller

than (VDD -|Vtp,0|). Under these conditions the NMOS and the

PMOS transistors will simultaneously conduct a nonzero

Fig. 7 The waveforms of time response of the symmetric current (drain current) during low-to-high and high-to-low

CMOS inverter output voltage during switching conductions, transitions, and the current reaches its peak value when the

when the equivalent load capacitance (Cl) has three different input voltage is equal to the CMOS threshold voltage Vin= Vth.

values. Otherwise, the short-circuit current of CMOS invertor is called

the power supply current. Both the NMOS and PMOS

ISSN: 1998-4464 569

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

transistors operate in the saturation mode of operation when

the current reaches its maximum (peak value) [8], [15].

kn V

I DD = (Vin − Vt 0, n ) 2 , ( Vt 0, n ≤ Vin ≤ DD ) (13)

2 2

kp VDD

I DD = (VDD − Vin − | Vt 0, p |) 2 , ( ≤ Vin ≤ VDD − | Vt 0, p | ) (14)

2 2

The CMOS inverter does not draw any significant current

from the power source, when the input voltage is smaller than

Vtn or larger than (VDD - |Vt0,p|), except some small leakage and

subthreshold currents. From the expression above, it is Fig. 10 The waveforms of the power supply current (short-

concluded that the transconductance parameters of the NMOS circuit current) in the symmetric CMOS inverter, for some

and PMOS transistors and the threshold voltage of the NMOS different values of the threshold voltages of the NMOS and

and PMOS transistors have impact in the current peak value. PMOS transistor during transition operation, when the

The dependence of the drain current peak value from the transconductance parameters are fixed.

transconductance parameters of the NMOS and PMOS

transistors in the symmetric CMOS inverters is shown in Fig. The impact of the channel- length modulation effect (λ) in

9. The achieved results indicate that when the the power supply current (short- circuit current) of the CMOS

transconductance parameters of the both NMOS and PMOS inverter during transition operation is shown in Fig. 11. By

transistor increase the short-circuit current peak value of the waveforms presented, the larger values of the channel length

symmetric CMOS inverter during output voltage transition will modulation constant (λ) will result in larger peak values of the

increase. Thus, the higher values of the transconductance power supply current of CMOS inverter, but does not have any

parameters will result to the higher value of short-circuit significant impact compared to the transconductance

current and the higher value of dynamic power dissipation parameters and threshold voltages of complementary MOS

term. transistors.

The power supply current of the CMOS inverter during

transition operation will contribute in the overall power

dissipation of the CMOS inverter under non ideal conditions,

with significant role when output load capacitance has a lower

value. The waveforms of short-circuit current (power supply

current) and its peak value on same different values of

equivalent load capacitance are shown in Fig. 12.

Fig. 9 The short-circuit current in the symmetric CMOS

inverter during switching operation when the transconductance

parameters of the NMOS and PMOS transistors increase

proportionally.

The impact of the threshold voltages of the NMOS and

PMOS transistors on short-circuit current peak of the

symmetric CMOS inverter, when the transconductance Fig. 11 The waveforms of the power supply current of the

parameters of both MOS transistors are fixed, is shown in Fig. CMOS inverter for two parametric values of the channel

10. The achieved results indicate that when the value of the length modulation constant (λ) during transition operation,

threshold voltage of the NMOS transistor and the absolute when the transconductance parameters of the NMOS and

value of the threshold voltage of the PMOS transistor are PMOS transistors and their threshold voltages are fixed.

smaller, the short-circuit current (drain current or power

supply current) peak value of the CMOS inverter will be larger

by values during the transition operation.

ISSN: 1998-4464 570

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

complementary MOS transistors, i.e the threshold voltage of

the NMOS transistor (Vt0,n) and the threshold voltage of the

PMOS transistor (Vt0,p), are controlled, or matched, the CMOS

inverter can be designed with high performance in the dynamic

conditions of operations, depending on the designer

requirements and operating conditions.

For the higher values of complementary MOS transistors’

transconductance parameters (kn and kp), the propagation delay

times during low-to-high (tPLH) and high-to-low (tPHL)

transition of the CMOS inverter output voltage will have lower

values, when in equivalent lumped load capacitance dominate

the extrinsic components. But increasing the transconductance

Fig. 12 The dependence of the power supply current peak parameters beyond certain values, the influence on

value in the CMOS inverter on equivalent load capacitance propagation delay time will diminish, and the propagation

(combined load capacitance). delay time will asymptotically approach the limit values. When

in the equivalent lumped capacitance dominate the intrinsic

In general, the larger supply voltage VDD results in lower a components, the limit values of the propagation delay time are

lower value of propagation time delay tp. But, the dynamic reached for smaller values of the complementary MOS

power dissipation of CMOS inverter will rise by expression transistors’ transconductance parameters. The increasing of the

(8), the short-circuit current will be higher, thus the overall transconductance parameters of complementary MOS

dynamic power dissipation will rise. However, the supply transistors in CMOS inverter are reached by increasing the

voltage VDD is determined by process technology and thus it is channel width of the complementary MOS transistors. But the

not under the control of the designer. Moreover, modern increasing of the channel widths will inevitably increase the

process technologies in which device size are reduced intrinsic components of the equivalent lumped load

continually require lower value of VDD. capacitance. If transconductance parameters of complementary

An important issue is the fact that propagation delay time MOS transistors are equal or matching (kn= kp), the

for sub-micron MOSFETs cannot estimate by expressions (3) propagation delay times are equal (symmetric), and for other

and (4), but have to modify. In sub-micron transistors (or a cases the propagation delay times will be asymmetric. The

small-geometry transistor) the current driving capability MOSFETs transconductance parameters ratio is determined

reduced as ea result of channel velocity saturation. By using parameter of the propagation delay times ratio in the CMOS

the saturation current of a deep-sub-micron MOSFETs, and inverter.

the average current method for estimate the propagation delay For the lower value of the NMOS transistor threshold

times, the expression of the propagation delay time is [16], voltage (Vt0,n) and higher value (or lower absolute value) of the

[17]: PMOS transistor threshold voltage (Vt0.p), the propagation

delay times during output voltage transitions in CMOS inverter

Cl (VDD / 2) (15) will decrease and vice versa.

t PHL =

κWn (WDD − Vt 0,n ) The nonzero rise and fall time of the driver signal at the

input of CMOS inverter will have significant influence to the

The propagation delay time for sub-micron transistors has a propagation delay time during output voltage transition, and

weak dependence on the power supply voltage compared on the higher value of rise and fall time of driven input signal

the propagation delay times estimate by expressions (3) and (input pulse) at the input of CMOS inverter will lead in

(4). The obtained results by this expression have an accurate increasing the propagation delay times.

about 90%, but to achieve the better results must use the The nonzero rise and fall time of input driver signal (input

another MOSFET model for sub-micron transistors. pulse) and the complementary MOS transistors

The obtained results for switching characteristics of the transconductance parameters in CMOS inverter will have

CMOS inverter on specific parameters discussed until now, influence in short- circuit current (power supply current)

also can apply to all general CMOS circuits. The CMOS during output voltage transition, and the higher values of rise

circuit consists of two blocks of MOSFETs, a block of the and fall time of the input driver signal, as well the higher

NMOS transistors and a block of the PMOS transistors, which values of complementary MOS transistor transconductance

can be simplified to one equivalent CMOS inverter with parameter, will result in higher values of the short- circuit

equivalent parameters [6]. current, as well in higher value of the overall dynamic power

dissipation of the CMOS inverter.

IV. CONCLUSION Another parameter called the channel length modulation

coefficient (process-technology parameter), that has to be

If during the design phase of the CMOS inverter, the taken into account especially when MOSFET is defined as a

transconductance parameters of the complementary MOS short-channel device, then for higher value of the channel

transistors, i.e. the transconductance parameter of the NMOS length modulation coefficient (λ) will have a small increase in

transistor (kn) and the transconductance parameter of the

PMOS transistor (kp), and the threshold voltage values of

ISSN: 1998-4464 571

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 12, 2018

the value of the short- circuit current peak during the output Milaim Zabeli received the Dipl.Ing. (1994), Mr.sc. (2006) and Ph.D (2012)

voltage transition of the CMOS inverter. degrees in Electrical Engineering from the University of Prishtina, Faculty of

Electrical and Computer Engineering. He currently holds the position of

Associate Professor at the Faculty of Mechanical and Computer Engineering,

University of Mitrovica. His research interests are in the Digital Electronics,

REFERENCES focused on VLSI design

[1] Muhammad H. Rashid, Microelectronics Circuits Analysis and Design, Nebi Caka received his Dipl. Ing. degree in Electrical Engineering from

3rd, CL Engineering, 2016.

University of Sarajevo, Bosnia and Herzegovina, in 1971 and his Mr. sc.

[2] David A. Hodges, Horace G. Jackon, Resve A. Saleh, Analysis and

degree in Electrical Engineering from University of Zagreb, Croatia in 1988.

Design of Digital Integrated Circuits, Mc Graw Hill, 2003.

He received his Ph.D. degree in Electrical and Computer Engineering from

[3] J. M. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated

Circuits: A Design Perspective, Upper Saddle River, NJ: Pearson the University of Prishtina, Kosovo in 2001. He also received the M. sc.

Education, 2016. (1979) and Mr.sc (1986) degrees in Albanian Philology from the University

[4] S. Kang, Y. Leblebici, Chulwoo Kim, CMOS Digital Integrated Circuits, of Prishtina, Faculty of Philology. He is currently involved in the Academy

4rd edition, McGraw-Hill, 2014. of Arts and Sciences of Kosovo as external expert for Computer language

[5] A. K. Maini, Digital electronics: Principles, Devices and Applications, processing. His research interests are in Microelectronics, Optoelectronics

Jon Wiley, 2007. and Image laser processing, and in Computer linguistics.

[6] R Jacob Baker, CMOS Circuit Design, Layou, and Simulation, 3rd, IEEE

Press, 2010. Myzafere Limani received her Dipl.Ing. degree in Electrical Engineering

[7] M. Zabeli, N. Caka, M. Limani, Impact of MOSFET’s structure from University of Prishtina, Kosova, in 1978 and her Mr.sc. degree in

parameters on its overall performance depending to the mode operation, Electrical Engineering from University of Belgrade, Serbia in 1988. She

International Journal of Circuits, Systems and Signal Processing, vol. received her Ph.D. degree in Electrical and Computer Engineering from the

10, 2016, pp. 390-396. University of Prishtina in 2000. She is currently a Full Professor in the

[8] A. Sedra and K. C. Smith, Microelectronic Circuits, 7th edition, Oxford department of Electronics at the University of Prishtina, Faculty of Electrical

University Press, 2015. and Computer Engineering and a Correspondent Member of the Academy of

[9] J. E. Ayers, Digital Integrated Circuits – Analysis and Design, 2nd, CRC Arts and Sciences of Kosovo. Her current research interests include

Press LLC, 2009. electronics and audio signal processing.

[10] John F. Wakerly, “Digital Design: Principles and Practices”, 5th,

Pearson, UK, 2017. Qamil Kabashi received the Dipl.Ing. (1996), Mr.sc. (2007) and Ph.D (2012)

[11] Sakurai, T. and Newton, A. R., Delay analysis of series-connected degrees in Electrical Engineering from the University of Prishtina, Faculty of

MOSFET circuits, IEEE Journal of Solid-State Circuits, vol. 26, no. 2, Electrical and Computer Engineering. He currently holds the position of

pp.112-131, February 1991. Associate Professor at the Faculty of Mechanical and Computer Engineering,

[12] N. Caka, M. Zabeli, M. Limani, Q. Kabashi, Impact of MOSFET University of Mitrovica. His research interests are in the Power Electronics,

parameters on its parasitic capacitances and their impact in digital focused on harmonic effects by PWM Invereters.

circuits, WSEAS transactions on Circuits and Systems, March 2007, .

Issue 3, vol 6, pp. 281-287.

[13] Yuan, J. and Svensson, C., High-speed CMOS circuit technique, IEEE

Transactions on Circuits and Systems, vol. 38, no. 7, pp. 779-790, July

1991.

[14] James D. Plummer, Micheal D. Deal, Peter B. Griffin, Silicon VLSI

Technology:, Fundamentals, Practice and Modeling, Prentice Hall, 2000.

[15] Neil H. E. Weste, David Money Harris, CMOS VLSI Design: A Circuits

and System Perspective, Addison-Wesley, 2011.

[16] Zhangcai Huang, Atsushi Kurokawa, Masanori Hashimoto, Takashi

Sato, Minglu Jiang Yasuaki Inoue, Modeling the Overshooting Effect

for CMOS Inverter Delay Analysis in Nanometer Technologies, IEEE

Transactions On Computer-Aided Design Of Integrated Circuits And

Systems, vol. 29, no. 2, pp.250-260, February 2010.

[17] Jagannath Samanta, Bishnu Prasad De, Delay analysis of UDSM CMOS

VLSI circuits, Procedia Engineering, vol. 30, pp. 135 – 143, 2012.

ISSN: 1998-4464 572

Вам также может понравиться

- Design of CMOS Inverter Using Different Aspect Ratios: Key Words: CMOS Parameters, Threshold Voltage, W/LДокумент6 страницDesign of CMOS Inverter Using Different Aspect Ratios: Key Words: CMOS Parameters, Threshold Voltage, W/LArshi DhimanОценок пока нет

- Ade Exp 5 Bhuvan BeeraДокумент6 страницAde Exp 5 Bhuvan BeeraBhuvan BeeraОценок пока нет

- Wiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosДокумент10 страницWiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosraoОценок пока нет

- Vlsi SyllabusДокумент2 страницыVlsi SyllabusAkhil NameirakpamОценок пока нет

- Designing 1-V Op Amps Using Standard Digital CMOS TechnologyДокумент12 страницDesigning 1-V Op Amps Using Standard Digital CMOS TechnologynikilquickОценок пока нет

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Документ10 страницQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpОценок пока нет

- CMOS Inverter propagation delayДокумент6 страницCMOS Inverter propagation delayshashwatОценок пока нет

- 1.1 Logic Family: CMOS Differential Logic Family For Low Power ApplicationДокумент27 страниц1.1 Logic Family: CMOS Differential Logic Family For Low Power ApplicationnishiyavijayanОценок пока нет

- Cmos LayoutДокумент13 страницCmos LayoutshastryОценок пока нет

- CMOS InverterДокумент3 страницыCMOS Invertert19125 t19125Оценок пока нет

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedДокумент7 страницComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedArchana SadanandanОценок пока нет

- CMOS BasicsДокумент41 страницаCMOS BasicsYeshoda MallikarjunaОценок пока нет

- Abstract-In This Work, An Analytical Model of The OFF-state: TH Ds DK Ds DKДокумент2 страницыAbstract-In This Work, An Analytical Model of The OFF-state: TH Ds DK Ds DKiprateekОценок пока нет

- Analytical Transient Response and Propagation Delay Evaluation of The CMOS Inverter For Short-Channel DevicesДокумент5 страницAnalytical Transient Response and Propagation Delay Evaluation of The CMOS Inverter For Short-Channel DevicesSANT SARANОценок пока нет

- Electronics 08 01156 With CoverДокумент18 страницElectronics 08 01156 With Coverlravikumar.19.eeeОценок пока нет

- Square Root Domain Filter Design and PerformanceДокумент13 страницSquare Root Domain Filter Design and Performanceaakriti chhabraОценок пока нет

- Triple Well Subthreshold CMOS Logic Using Body-Bias TechniqueДокумент6 страницTriple Well Subthreshold CMOS Logic Using Body-Bias TechniqueRiccardo Della SalaОценок пока нет

- EI2403 - VLSI Design 2 Marks With AnswersДокумент23 страницыEI2403 - VLSI Design 2 Marks With AnswersAnand GvphОценок пока нет

- VLSI Design: Dr. K. Srinivasa RaoДокумент39 страницVLSI Design: Dr. K. Srinivasa Raoshen shahОценок пока нет

- CMOS (Disambiguation) : For Other Uses, SeeДокумент6 страницCMOS (Disambiguation) : For Other Uses, SeeManas NagОценок пока нет

- Vlsi DesignДокумент31 страницаVlsi Designajas777BОценок пока нет

- A Survey Analysis On CMOS Integrated Cir PDFДокумент4 страницыA Survey Analysis On CMOS Integrated Cir PDFNK NKОценок пока нет

- Difference Between CMOS and NMOS TechДокумент5 страницDifference Between CMOS and NMOS TechShavel Kumar100% (1)

- A Novel High Integration-Density TFT-CMOS Inverter With Vertical Structure For Low Power ApplicationДокумент5 страницA Novel High Integration-Density TFT-CMOS Inverter With Vertical Structure For Low Power ApplicationJOAM MANUEL RINCÓN ZULUAGAОценок пока нет

- Cost, Expressed by The Complexity and Area: V V V CДокумент1 страницаCost, Expressed by The Complexity and Area: V V V CAtul NarkhedeОценок пока нет

- For Other Uses, See .: CMOS (Disambiguation)Документ10 страницFor Other Uses, See .: CMOS (Disambiguation)Ashutosh DabasОценок пока нет

- Low Power Ramp Generator With MOSFET and CNTFET TransistorsДокумент3 страницыLow Power Ramp Generator With MOSFET and CNTFET TransistorsBhargav BhatОценок пока нет

- CMOS PortДокумент46 страницCMOS PortZali100% (1)

- MOM Capacitor Design Challenges and Solutions SFT 200904Документ4 страницыMOM Capacitor Design Challenges and Solutions SFT 200904subasumalaОценок пока нет

- For Other Uses, See .: CMOS (Disambiguation)Документ11 страницFor Other Uses, See .: CMOS (Disambiguation)Smitha KollerahithluОценок пока нет

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS)Документ4 страницыTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS)Testing toolsОценок пока нет

- OTA Based On CMOS Inverters and Application in The Design of Tunable Bandpass Filter PDFДокумент10 страницOTA Based On CMOS Inverters and Application in The Design of Tunable Bandpass Filter PDFGenetic JohnОценок пока нет

- Untitled 1Документ1 страницаUntitled 1Mihir DharajiyaОценок пока нет

- A Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency CompensationДокумент12 страницA Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency Compensationtotoya38Оценок пока нет

- MOSFET-Only Switched-Capacitor Circuits in Digital CMOS TechnologyДокумент14 страницMOSFET-Only Switched-Capacitor Circuits in Digital CMOS Technologyfabien33Оценок пока нет

- A Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologyДокумент4 страницыA Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologySowmya ReddyОценок пока нет

- From Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)Документ9 страницFrom Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)bas_cbkОценок пока нет

- Optimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingДокумент7 страницOptimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingSavio SОценок пока нет

- Ec3352 Vlsi and Chip DesignДокумент15 страницEc3352 Vlsi and Chip DesignParanthaman GОценок пока нет

- MOSFET Gate Drive Circuit Design Considerations For Integrated High Switching Frequency Buck ConverterДокумент7 страницMOSFET Gate Drive Circuit Design Considerations For Integrated High Switching Frequency Buck ConverterSergey RosenfeldОценок пока нет

- A Simple Floating MOS-Memristor For High-Frequency ApplicationsДокумент11 страницA Simple Floating MOS-Memristor For High-Frequency ApplicationsAnuradha KhalkhoОценок пока нет

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (Документ9 страницTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (RailyОценок пока нет

- FinalДокумент18 страницFinalitsaartihere001Оценок пока нет

- MOSFET Gate Drive Circuit Design Considerations for Integrated High Switching Frequency Buck ConverterДокумент7 страницMOSFET Gate Drive Circuit Design Considerations for Integrated High Switching Frequency Buck Converterdurrani shaheerОценок пока нет

- ContentДокумент6 страницContentashwingeorge101Оценок пока нет

- IEEE Journal of Solid-State Circuits: "A 3.8-ns CMOS 16 x 16-b Multiplier Using Complementary Pass-Transistor LogicДокумент8 страницIEEE Journal of Solid-State Circuits: "A 3.8-ns CMOS 16 x 16-b Multiplier Using Complementary Pass-Transistor LogicNarendra AchariОценок пока нет

- Fundamentals of CMOS VLSI QBДокумент6 страницFundamentals of CMOS VLSI QBharshithaОценок пока нет

- MOS Transistor Modeling For RF IC Design (Enz)Документ16 страницMOS Transistor Modeling For RF IC Design (Enz)Sharabi.salahОценок пока нет

- Electronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyДокумент17 страницElectronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyRam MОценок пока нет

- Ec1461 Vlsi DesignДокумент17 страницEc1461 Vlsi DesignArunkumarОценок пока нет

- Combinational Logic Circuits DesignДокумент47 страницCombinational Logic Circuits DesignHussein HasenОценок пока нет

- Design of A Telescopic Fully Differential OTAДокумент7 страницDesign of A Telescopic Fully Differential OTAUdai ValluruОценок пока нет

- Vlsi Very Imp QaДокумент38 страницVlsi Very Imp QaAjay Kumar MattupalliОценок пока нет

- s42452-021-04501-yДокумент8 страницs42452-021-04501-yDEEPAK PRAJAPATIОценок пока нет

- VLSIДокумент3 страницыVLSINuniwal JyotiОценок пока нет

- VLSI QuestionsДокумент1 страницаVLSI QuestionsHemant SaraswatОценок пока нет

- CMOS ICДокумент12 страницCMOS ICsalikrishna405Оценок пока нет

- Mathematical Modeling and Simulation of Permanent Magnet Synchronous MachineДокумент6 страницMathematical Modeling and Simulation of Permanent Magnet Synchronous MachineFaiza OuiddirОценок пока нет

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- Electronic Component Measurement and Testing (Part 1) : Electronic Workshop & Domestic WiringДокумент10 страницElectronic Component Measurement and Testing (Part 1) : Electronic Workshop & Domestic WiringNor NadiahОценок пока нет

- DIY 2kVA SMPS 90V 15A HB PFC With IR2110 Mosfet Driver - Electronic CircuitДокумент14 страницDIY 2kVA SMPS 90V 15A HB PFC With IR2110 Mosfet Driver - Electronic CircuitK. RAJA SEKARОценок пока нет

- DIAC characteristics and applications in triac triggering circuitsДокумент7 страницDIAC characteristics and applications in triac triggering circuitsBaquiran John Paul BaquiranОценок пока нет

- 9 MultimeterДокумент8 страниц9 MultimeterrameshОценок пока нет

- Feedback Docu ProjectДокумент35 страницFeedback Docu ProjectAnonymous rgNIr9SYОценок пока нет

- 04 - Second-Order Effects On MOSFET Small Signal ModelДокумент27 страниц04 - Second-Order Effects On MOSFET Small Signal ModelWinnie LahОценок пока нет

- RAD 1406 Appendix 4 - En-Route DCT Limits DCT Segments: Valid From 29/05/2014Документ98 страницRAD 1406 Appendix 4 - En-Route DCT Limits DCT Segments: Valid From 29/05/2014Andrei NecuţăОценок пока нет

- Current, Resistance and DC Circuits: Physics 112NДокумент27 страницCurrent, Resistance and DC Circuits: Physics 112NgiyonoОценок пока нет

- Metal Semiconductor FET MESFETДокумент26 страницMetal Semiconductor FET MESFETsrinathОценок пока нет

- Ceramics PPT CEMДокумент37 страницCeramics PPT CEMskhanveОценок пока нет

- Baritt DiodesДокумент6 страницBaritt DiodesjosephinemalathiОценок пока нет

- K1JD Homebrew Amplifier v1.0Документ10 страницK1JD Homebrew Amplifier v1.0Manuel Costa MoreiraОценок пока нет

- Xem3005 UmДокумент19 страницXem3005 UmJuanmanuel BarroyetaОценок пока нет

- TC 7510Документ2 страницыTC 7510energiculОценок пока нет

- EDC 2 MarksДокумент16 страницEDC 2 Marksdr mbaluОценок пока нет

- Literature Review NanotechnologyДокумент5 страницLiterature Review Nanotechnologyfvfmxb2y100% (1)

- Implementation of Efficient Class B Large Signal Amplifier Using MultisimДокумент5 страницImplementation of Efficient Class B Large Signal Amplifier Using MultisimEditor IJRITCCОценок пока нет

- Cascode Amplifier: Exp - No: 5 Date: 20-9-2021Документ9 страницCascode Amplifier: Exp - No: 5 Date: 20-9-2021annambaka satishОценок пока нет

- Testing A MOSFETДокумент3 страницыTesting A MOSFETttarwinОценок пока нет

- RRB Je Previous Year Paper 8thaug Shift2.PDF 51Документ11 страницRRB Je Previous Year Paper 8thaug Shift2.PDF 51sreenu mОценок пока нет

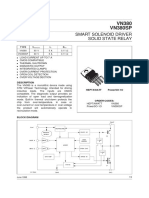

- VN380 Smart Solenoid Driver SpecificationsДокумент10 страницVN380 Smart Solenoid Driver SpecificationsAdan Pérez EchevarríaОценок пока нет

- FreeRTOS V7.1.0 release notes with new ports and demosДокумент32 страницыFreeRTOS V7.1.0 release notes with new ports and demoslna_cooolmadina5742Оценок пока нет

- UVtron TPT1021E PDFДокумент4 страницыUVtron TPT1021E PDFAgam ArlandoОценок пока нет

- 0620 s11 QP 21 PDFДокумент16 страниц0620 s11 QP 21 PDFArasiveluОценок пока нет

- A Stable Radio Microphone With Loop AntennaДокумент6 страницA Stable Radio Microphone With Loop AntennaAdi FadillahОценок пока нет

- PID Issues in BI-FACIAL MODULESДокумент17 страницPID Issues in BI-FACIAL MODULESAnjanareddy SettipalliОценок пока нет

- Murphy ShuTDOWNДокумент12 страницMurphy ShuTDOWNReider AmundarayОценок пока нет

- Allen Bradley F-SERIES MOTORДокумент12 страницAllen Bradley F-SERIES MOTORFamilia Pereztagle BandaОценок пока нет

- Large Signal Modeling of GaN Device For High Power Amplifier DesignДокумент134 страницыLarge Signal Modeling of GaN Device For High Power Amplifier DesignmarcwdОценок пока нет

- When Capability Is Critical PDFДокумент5 страницWhen Capability Is Critical PDFkrechbaОценок пока нет