Академический Документы

Профессиональный Документы

Культура Документы

DFT Interview Questions

Загружено:

rupesh kumar0 оценок0% нашли этот документ полезным (0 голосов)

1K просмотров2 страницыThe document contains questions about the interviewee's experience with design for test techniques like ATPG and scan compression, including topics like scan chain length, fault coverage, handling mismatches during simulation, and factors that influence the number of patterns generated. It also asks about design issues such as clock domain crossing, hold violations, and resolving DRC violations.

Исходное описание:

Basic dft questions to crack any interview

Оригинальное название

DFT INTERVIEW QUESTIONS

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThe document contains questions about the interviewee's experience with design for test techniques like ATPG and scan compression, including topics like scan chain length, fault coverage, handling mismatches during simulation, and factors that influence the number of patterns generated. It also asks about design issues such as clock domain crossing, hold violations, and resolving DRC violations.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

1K просмотров2 страницыDFT Interview Questions

Загружено:

rupesh kumarThe document contains questions about the interviewee's experience with design for test techniques like ATPG and scan compression, including topics like scan chain length, fault coverage, handling mismatches during simulation, and factors that influence the number of patterns generated. It also asks about design issues such as clock domain crossing, hold violations, and resolving DRC violations.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

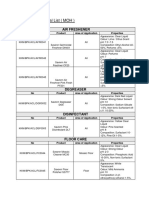

1. How much real time experience do you have in DFT?

2. In project, what you did like ATPG or simulation?

3. In ATPG, what kind of fault did you get?

4. How did you improve the coverage in ATPG?

5. What is the actual flop count and scan chain length in your design?

6. After compression, how much is the chain lenght?

7. Have you ever worked on GLS and JTAG?

8. What is your scan clock frequency and at speed frequency?

9. How much coverage did you get in ATPG?

10. Have you transferred the generated pattern to others person/ team?

11. If a pin value ties to X, then during ATPG, How can it affect the coverage?

12. Due to the Clock domain crossing, In ATPG can we see any coverage loss and if yes then

how will handle it?

13. If a data pin and clk pin of a flop is driven by the same pin then what would it cause and how

to handle this problem?

14. If we have pre-scan inserted net list and later also we have to perform scan insertion for some

of its remaining part then how to take care of this and how can be stich pre-existing chains

with new scan chains ?

15. If parallel simulation is failing, then what can be the cause of it and how will it be resolved?

16. During scan compressed serial pattern simulation, if we find any mismatches then what is the

good approach to detect and clear it?

17. No. of patterns generated by the ATPG tool, depends upon which parameters?

Q1.What is compression ratio and how did you decide it?

Q2. How much was the chain length in your design?

Q3. Explain EDT and why we need the EDT?

Q4. What are the inputs and outputs of the EDT block?

Q5. What is the use of edt_update signal? And when it must be required in the testproc file?

Q6. Explain the testproc file? What are all the events it contains and explain them ?

Q7. Why do we need of edt_clock signal? Can edt_clock and the scan clock be the same

and if No the

Explain it?

Q8. Why we need OCC in our design?

Q9. How many OCC was present in your design and what are all inputs required for the

OCC?

Q10. Where we need to define the OCC, whether it can be define in testproc file or

elsewhere, explain?

Q11. How did you define the OCC and how can you make sure for getting the correct

capture pulse?

Q12. Why we need two capture pulses and in what case it can be more than two, explain?

Q13. What do mean by the sequential depth, elaborate this term?

Q14. What was the slow clk freq. and Fast clk freq. in your design?

Q15. Where you should define the clock to get it at the proper frequency suppose you need

200 MHz

clock?

Q16. How much coverage did you get in your design?

Q17. What did you do to get the maximum coverage in your design, explain your debugging

process?

Q18. What do you understand with Uncontrolled and unobserved fault, and why do they

appear in the

report?

Q19. How many types of DRC’s you have seen?

Q20. Explain T3 and T5 drc’s and how these can be resolved?

Q21. Did you face any D1 and D2 violation and what can be the cause of these and how to

remove?

Q22. What you did to resolve D1 violation?

Q23. Do we need to control the async_reset during scan insertion? Why? And how did you

do it?

Q24. What do know about a lockup latch, explain? And In what scenario we do need of it?

Q25. Do we need the lockup latch if the Trailing edge flop is followed by the leading edge

flop, explain

the scenario?

Q26. What do know about the Hold violation?

Q27. Explain the clock domain crossing?

Q28. What do know about the clock synchronizer and why we need of it?

Q29. What is NCP? And in what practical scenarios we should use NCP, explain?

Q30. Explain the combinational feedback loop and why do we need to control it?

Вам также может понравиться

- Edt Testkompress by Kiran K S: Embedded Deterministic TestДокумент51 страницаEdt Testkompress by Kiran K S: Embedded Deterministic Testsenthilkumar100% (8)

- DFT Interview Questions & AnswersДокумент22 страницыDFT Interview Questions & Answersdeepa100% (4)

- Conrail Case QuestionsДокумент1 страницаConrail Case QuestionsPiraterija100% (1)

- Interview Questions Related To Scan, ATPG, EDT and SimulationДокумент1 страницаInterview Questions Related To Scan, ATPG, EDT and SimulationSiva SreeramdasОценок пока нет

- Tips For Simulation Debug PDFДокумент21 страницаTips For Simulation Debug PDFSaurin Shah100% (1)

- DFT Interview Questions - Welcome To World of VLSIДокумент5 страницDFT Interview Questions - Welcome To World of VLSINaganithesh GhattamaneniОценок пока нет

- Interview QuestionsДокумент155 страницInterview Questionspravallika vysyaraju100% (9)

- DFT Interview Questions1Документ34 страницыDFT Interview Questions1rajkumar gunjaОценок пока нет

- ATPG Methodology FlowДокумент37 страницATPG Methodology FlowaanbalanОценок пока нет

- Scan Insertion Lab Observation (K.S.K.S.sarma)Документ33 страницыScan Insertion Lab Observation (K.S.K.S.sarma)Kittu Krishna100% (2)

- Basic ScanДокумент20 страницBasic Scansaikumar bhavana100% (1)

- Debugging Simulation Mismatches in Fastscan: by Geir Eide Last Modified: July 03, 2001Документ21 страницаDebugging Simulation Mismatches in Fastscan: by Geir Eide Last Modified: July 03, 2001prakashthamankar100% (3)

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseДокумент22 страницыA Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseSiva Sreeramdas100% (1)

- On DFTДокумент16 страницOn DFTAman TyagiОценок пока нет

- VLSI Test Principles and Architectures: Design for TestabilityОт EverandVLSI Test Principles and Architectures: Design for TestabilityРейтинг: 4.5 из 5 звезд4.5/5 (4)

- Theater 10 Syllabus Printed PDFДокумент7 страницTheater 10 Syllabus Printed PDFJim QuentinОценок пока нет

- Apache Hive Essentials 2nd PDFДокумент204 страницыApache Hive Essentials 2nd PDFketanmehta4u0% (1)

- Clearing Negative SpiritsДокумент6 страницClearing Negative SpiritsmehorseblessedОценок пока нет

- 1E Star Trek Customizable Card Game - 6 First Contact Rule SupplementДокумент11 страниц1E Star Trek Customizable Card Game - 6 First Contact Rule Supplementmrtibbles100% (1)

- Service and Maintenance Manual AFPX 513 PDFДокумент146 страницService and Maintenance Manual AFPX 513 PDFManuel Amado Montoya AgudeloОценок пока нет

- DFT Imp Questions 250+Документ5 страницDFT Imp Questions 250+Mayur Mestry100% (1)

- DFT QnsДокумент6 страницDFT QnsRajishaОценок пока нет

- DFT Interview QuestionsДокумент3 страницыDFT Interview QuestionsJayesh PopatОценок пока нет

- DFT Interview QuestionsДокумент2 страницыDFT Interview Questionsrupesh kumar100% (1)

- Segregated QuestionsДокумент1 страницаSegregated QuestionsdeepaОценок пока нет

- QUALCOMM Interview Questions 1. Basic View of Compression?Документ9 страницQUALCOMM Interview Questions 1. Basic View of Compression?deepa100% (2)

- DFT QuestionsДокумент8 страницDFT QuestionsNaga NitheshОценок пока нет

- DFT Interview QsДокумент4 страницыDFT Interview QsHARISH DAMARLAОценок пока нет

- DFT FaqДокумент15 страницDFT FaqBrijesh S D100% (1)

- Atpg Question Answer: Name: Meet ZankatДокумент7 страницAtpg Question Answer: Name: Meet ZankatMeet Zankat100% (2)

- DFT DocumentationДокумент20 страницDFT Documentationyamini100% (1)

- Training On EDT (1) - Copy (1) (3) 1Документ52 страницыTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Few Important QuestionsДокумент7 страницFew Important QuestionsShankhadeep DasОценок пока нет

- Timing SimulationДокумент3 страницыTiming SimulationKarthik Sharma100% (1)

- Assignment - 6Документ4 страницыAssignment - 6kishorОценок пока нет

- Compression AssignmentДокумент7 страницCompression Assignmentpoojithas acharya100% (1)

- Simulation Mismatches Can Foul Up Test-Pattern VerificationДокумент6 страницSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliОценок пока нет

- Wrapper p1500Документ8 страницWrapper p1500srikanth100% (1)

- Assignment CompressionДокумент8 страницAssignment CompressionPrafulani Gajbhiye100% (2)

- (Design For Testability) Atpg: - Jaganath SinghДокумент23 страницы(Design For Testability) Atpg: - Jaganath SinghSAI KIRAN100% (3)

- What Is DFT in VLSIДокумент22 страницыWhat Is DFT in VLSINaga Nithesh100% (4)

- COMPRESSION PPT by HK - OdpДокумент23 страницыCOMPRESSION PPT by HK - Odpsuneetha100% (5)

- Why Masking Is Needed: Scan Chain Masking in The AcompactorДокумент6 страницWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiОценок пока нет

- Atpg Answer Name: Meet ZankatДокумент5 страницAtpg Answer Name: Meet ZankatMeet ZankatОценок пока нет

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeДокумент15 страницFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaОценок пока нет

- Scan Insertion Lab ObservationsДокумент2 страницыScan Insertion Lab ObservationssenthilkumarОценок пока нет

- Scan PDFДокумент49 страницScan PDFferoz100% (1)

- Atpg Lab Notes PDFДокумент11 страницAtpg Lab Notes PDFrajkumar gunja100% (1)

- Embedded Deterministic Test: by M. BalakrishnaДокумент28 страницEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Assignment 1 Poovika.tДокумент12 страницAssignment 1 Poovika.tsenthilkumarОценок пока нет

- Assignment Section-1 1. What Is DFT?Документ18 страницAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- Name DFT Trainee Atpg Insertion Cases ObservationsДокумент17 страницName DFT Trainee Atpg Insertion Cases ObservationssenthilkumarОценок пока нет

- Streaming Scan NetworkДокумент51 страницаStreaming Scan NetworkVENKATRAMAN100% (1)

- Basic Interview Questions On DFTДокумент5 страницBasic Interview Questions On DFTHardik TrivediОценок пока нет

- Design For Test: 1. What Is Sequential Depth in DFT? How Does It Improve Coverage?Документ95 страницDesign For Test: 1. What Is Sequential Depth in DFT? How Does It Improve Coverage?Neusilica school of VLSI100% (2)

- Scan InsertionДокумент16 страницScan InsertionRUPIREDDY PRAVEENОценок пока нет

- Mahitha Scan Insertion Observation PDFДокумент30 страницMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- DFTДокумент21 страницаDFTMuhsin Nk100% (1)

- ATPG Srivatsa PPTДокумент37 страницATPG Srivatsa PPTMayur Mestry100% (1)

- NXP Interview QuestionsДокумент29 страницNXP Interview Questionsdeepa100% (1)

- Jtag PresentationДокумент21 страницаJtag PresentationNivaz ChockkalingamОценок пока нет

- DFT Interview QuestionsДокумент9 страницDFT Interview QuestionsNaga Nithesh100% (1)

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingДокумент3 страницыScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- Atpg Coverage LossДокумент4 страницыAtpg Coverage LossUmesh ParasharОценок пока нет

- SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckДокумент3 страницыSCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - CheckJayesh Popat100% (2)

- Broadcom Interview QuesДокумент5 страницBroadcom Interview QuesShaki Bhanu100% (1)

- Alexander Blok - 'The King in The Square', Slavonic and East European Review, 12 (36), 1934Документ25 страницAlexander Blok - 'The King in The Square', Slavonic and East European Review, 12 (36), 1934scott brodieОценок пока нет

- Customizable Feature Based Design Pattern Recognition Integrating Multiple TechniquesДокумент191 страницаCustomizable Feature Based Design Pattern Recognition Integrating Multiple TechniquesCalina Sechel100% (1)

- Strategic ManagementДокумент14 страницStrategic ManagementvishakhaОценок пока нет

- Approved Chemical ListДокумент2 страницыApproved Chemical ListSyed Mansur Alyahya100% (1)

- Developing Global LeadersДокумент10 страницDeveloping Global LeadersDeepa SharmaОценок пока нет

- Goats & Sheep: What You Need To KnowДокумент74 страницыGoats & Sheep: What You Need To KnowAdrian BAGAYANОценок пока нет

- GAJ Mod 18 Ace Your InterviewДокумент12 страницGAJ Mod 18 Ace Your InterviewAnjela SantiagoОценок пока нет

- Algebra. Equations. Solving Quadratic Equations B PDFДокумент1 страницаAlgebra. Equations. Solving Quadratic Equations B PDFRoberto CastroОценок пока нет

- Annexure 8: Medical Certificate (To Be Issued by A Registered Medical Practitioner) General ExpectationsДокумент1 страницаAnnexure 8: Medical Certificate (To Be Issued by A Registered Medical Practitioner) General ExpectationsMannepalli RamakrishnaОценок пока нет

- Maths Lowersixth ExamsДокумент2 страницыMaths Lowersixth ExamsAlphonsius WongОценок пока нет

- Accounting 110: Acc110Документ19 страницAccounting 110: Acc110ahoffm05100% (1)

- Long 1988Документ4 страницыLong 1988Ovirus OviОценок пока нет

- A Photograph (Q and Poetic Devices)Документ2 страницыA Photograph (Q and Poetic Devices)Sanya SadanaОценок пока нет

- A Guide To Effective Project ManagementДокумент102 страницыA Guide To Effective Project ManagementThanveerОценок пока нет

- Case Study 1 (Pneumonia)Документ13 страницCase Study 1 (Pneumonia)Kate EscotonОценок пока нет

- 206f8JD-Tech MahindraДокумент9 страниц206f8JD-Tech MahindraHarshit AggarwalОценок пока нет

- Trump's Fake ElectorsДокумент10 страницTrump's Fake ElectorssiesmannОценок пока нет

- Work Teams and GroupsДокумент6 страницWork Teams and GroupsFides AvendanОценок пока нет

- Nahs Syllabus Comparative ReligionsДокумент4 страницыNahs Syllabus Comparative Religionsapi-279748131Оценок пока нет

- Counselling Goes To The Movies: Antwone Fisher (2002)Документ12 страницCounselling Goes To The Movies: Antwone Fisher (2002)Azizul MohamadОценок пока нет

- Julie Jacko - Professor of Healthcare InformaticsДокумент1 страницаJulie Jacko - Professor of Healthcare InformaticsjuliejackoОценок пока нет

- Article 1156 Gives The Civil Code Definition of Obligation, in Its Passive Aspect. Our Law MerelyДокумент11 страницArticle 1156 Gives The Civil Code Definition of Obligation, in Its Passive Aspect. Our Law MerelyFeir, Alexa Mae C.Оценок пока нет

- Fundamental Rights-Right To Equality, Prohibition of Discrimination, Right To Equality of OpportunityДокумент76 страницFundamental Rights-Right To Equality, Prohibition of Discrimination, Right To Equality of OpportunityutkarshОценок пока нет

- Writing - Hidden Curriculum v2 EditedДокумент6 страницWriting - Hidden Curriculum v2 EditedwhighfilОценок пока нет