Академический Документы

Профессиональный Документы

Культура Документы

ONE Full Question From Each Module.: (08 Marks) (08 Marks)

Загружено:

NingammaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

ONE Full Question From Each Module.: (08 Marks) (08 Marks)

Загружено:

NingammaАвторское право:

Доступные форматы

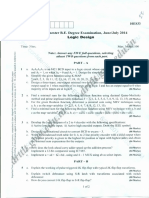

USN 16EVE153

First Semester M.Tech. Degree Examination, June/July 2017

ASIC Design

Time: 3 hrs. Max. Marks: 80

Note: Answer FIVE full questions, choosing

ONE full question from each module.

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice.

Module-1

1 a. Explain standard cell-based ASIC with a neat diagram. (08 Marks)

b. Distinguish between channeled gate array and channellers gate array. (08 Marks)

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

OR

2 a. Explain carry save adder with relevant logic equations and cell diagram. (12 Marks)

b. Explain cell compilers. (04 Marks)

Module-2

3 a. Define logical effort. Predict delay of a 3-input NOR logic cell with 2x drive, driving a neat

with a fanout of four, with a total load capacitance (comprising the i/p capacitance plus inter

conned) of 0.3pF. [Give : tPD = (0.03 + 0.72 cout + 0.6)ns. (08 Marks)

b. Compute delay involved in implanting following function as a multistage A011221 logic.

Zn(A1, A2, B1, B2, c) = NOT (NAND(NAND(A1, A2), AOI21(B1, B2, C)))

Compare this delay with that of single stage implementation. (08 Marks)

OR

4 a. Compare ACT – 1 and ACT – 2 logic modules with examples. (08 Marks)

b. With help of neat diagram, explain Xilinx Xc3000CLB. (08 Marks)

Module-3

5 a. Explain schematic icons and symbols with examples. (08 Marks)

b. What is a netlist screener? List the errors that can be found by a netlist screener. (08 Marks)

OR

6 a. Explain physical design flow in ASIC design. (08 Marks)

b. Explain constrictive partitioning with rules and a relevant illustration. (08 Marks)

Module-4

7 a. Explain input/output power pads with relevant diagrams. (08 Marks)

b. Explain placement goals and objectives. (08 Marks)

1 of 2

16EVE153

OR

8 a. Explain with a neat diagram timing driven floor planning and placement design flow.

b. (08 Marks)

Explain min-out placement with an illustration. (08 Marks)

Module-5

9 a. Explain global routing between blocks for a cell-based ASIC with neat diagram. (08 Marks)

b. What is detailed routing? Explain goals and objectives of detailed routing. (08 Marks)

OR

10 a. Explain the 2 types of design checks in details : DRC and LVS. (04 Marks)

b. Write short notes on :

i) Circuit extraction

ii) SPF, RSPF and DSPF. (12 Marks)

*****

2 of 2

Вам также может понравиться

- FSK Modulator (DCS 6000 07)Документ26 страницFSK Modulator (DCS 6000 07)maafkoroОценок пока нет

- Embedded Systems Road MapДокумент9 страницEmbedded Systems Road MapbajehagОценок пока нет

- 10EC/TE761: at Least TWO Questions From Each PartДокумент1 страница10EC/TE761: at Least TWO Questions From Each PartVamshi KrishnaОценок пока нет

- Inside Intel Management EngineДокумент41 страницаInside Intel Management Engineemazitov-1Оценок пока нет

- PIW Using PyATS To Build A NetDevOps CI CD PipelineДокумент59 страницPIW Using PyATS To Build A NetDevOps CI CD PipelinepapanОценок пока нет

- Shared Memory ArchitectureДокумент2 страницыShared Memory ArchitectureNeethu RajeshОценок пока нет

- Wireless Communication Exam QuestionsДокумент1 страницаWireless Communication Exam QuestionsChetan Naik massandОценок пока нет

- 18ME15/25 Model Question Paper 15ME832Документ1 страница18ME15/25 Model Question Paper 15ME832Adarsh GowdaОценок пока нет

- 18CS33Документ2 страницы18CS33rajut20011Оценок пока нет

- (12 Marks) (04 Marks)Документ2 страницы(12 Marks) (04 Marks)Mr PerfectОценок пока нет

- 15CS565 PDFДокумент1 страница15CS565 PDFjananiОценок пока нет

- 10EC/TE61: at Least TWO Questions From Each PartДокумент2 страницы10EC/TE61: at Least TWO Questions From Each PartdonyarmstrongОценок пока нет

- Previous question papers for energy engineeringДокумент2 страницыPrevious question papers for energy engineeringChiduОценок пока нет

- (08 Marks) (08 Marks)Документ2 страницы(08 Marks) (08 Marks)Yogesh KumarОценок пока нет

- 22EC3PCDSDДокумент2 страницы22EC3PCDSDMayur NayakaОценок пока нет

- 18 MPD 13Документ3 страницы18 MPD 13ShaswathMurtuguddeОценок пока нет

- 15CS563 Fifth Semester B.E. Degree Examination, Dec.204 0/jan:2020Документ1 страница15CS563 Fifth Semester B.E. Degree Examination, Dec.204 0/jan:2020Gagana.k kОценок пока нет

- 16LNI12_3Документ1 страница16LNI12_3keerthiksОценок пока нет

- 10EC/TE61: at Least TWO Questions From Each PartДокумент2 страницы10EC/TE61: at Least TWO Questions From Each PartdonyarmstrongОценок пока нет

- 3rd Btech EEE 2018-19 PSA Ses-Q1Документ2 страницы3rd Btech EEE 2018-19 PSA Ses-Q1sudheepОценок пока нет

- Reactive Power ManagementДокумент1 страницаReactive Power ManagementAravindОценок пока нет

- USN 15CV654 Sixth Semester B.E. Degree ExaminationДокумент1 страницаUSN 15CV654 Sixth Semester B.E. Degree ExaminationVishnu Vardhan MekalaОценок пока нет

- Ec0033-Asic Design-Model Qp-Vii SemДокумент1 страницаEc0033-Asic Design-Model Qp-Vii SemskarthikpriyaОценок пока нет

- 15 Cs 562Документ2 страницы15 Cs 562Pradeep KОценок пока нет

- CMTДокумент2 страницыCMTMohiuddin QureshiОценок пока нет

- First Semester M.Tech. Degree Examination, June 2012 Network Programming 10SCN13Документ1 страницаFirst Semester M.Tech. Degree Examination, June 2012 Network Programming 10SCN13Manjushree S GowdaОценок пока нет

- Dem 22421Документ15 страницDem 22421Payal VeerОценок пока нет

- CBCS Scheme Energy Engineering Exam QuestionsДокумент2 страницыCBCS Scheme Energy Engineering Exam QuestionsMadhu techОценок пока нет

- Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inДокумент2 страницыDrttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inrama KrishnaОценок пока нет

- Ece361 - Ee 2010 S1Документ5 страницEce361 - Ee 2010 S1Mu'izz KaharОценок пока нет

- Atleast TWO Questions From Each Part.: (10 Marks)Документ1 страницаAtleast TWO Questions From Each Part.: (10 Marks)Rajendra sОценок пока нет

- 14SCS41Документ1 страница14SCS41Sharath Kumar VОценок пока нет

- 18AI742Документ1 страница18AI742siddhanth shettyОценок пока нет

- Jan 2020 17cs563Документ1 страницаJan 2020 17cs563qwerty qwertyОценок пока нет

- VLSI DesignДокумент7 страницVLSI DesignVarun ThejОценок пока нет

- ONE Full Question From Each Module.: DX y D P DX y D EIДокумент2 страницыONE Full Question From Each Module.: DX y D P DX y D EIArjunRathodОценок пока нет

- 16LNI12_1Документ2 страницы16LNI12_1keerthiksОценок пока нет

- Atleast TWO Questions From Each Part.: (10 Marks) (10 Marks)Документ1 страницаAtleast TWO Questions From Each Part.: (10 Marks) (10 Marks)Chetan Naik massandОценок пока нет

- (08 Marks) (08 Marks)Документ2 страницы(08 Marks) (08 Marks)SamyОценок пока нет

- (08 Marks) (08 Marks)Документ2 страницы(08 Marks) (08 Marks)Naga prajwal j. AОценок пока нет

- Question Paper Code:: Reg. No.Документ2 страницыQuestion Paper Code:: Reg. No.Anand DuraiswamyОценок пока нет

- Cse 05 KCS-503 SJДокумент2 страницыCse 05 KCS-503 SJshiv.2125csit1121Оценок пока нет

- De 5Документ2 страницыDe 5PADMANABAN SОценок пока нет

- USN 15AE564 Fifth Semester B.E. Degree Examination, Dec.2018/Jan.2019 Basics of Rockets and MissilesДокумент1 страницаUSN 15AE564 Fifth Semester B.E. Degree Examination, Dec.2018/Jan.2019 Basics of Rockets and MissilesRishi PatilОценок пока нет

- Microprocessors (Summer & Winnter) 19Документ57 страницMicroprocessors (Summer & Winnter) 19atharvpatilpatil81Оценок пока нет

- Microsoft Word - KCS503 - 2020-21Документ2 страницыMicrosoft Word - KCS503 - 2020-21Ritik chaudharyОценок пока нет

- Integrated Circuits Nec 501 PDFДокумент2 страницыIntegrated Circuits Nec 501 PDFSaurabhОценок пока нет

- 18EVE322Документ2 страницы18EVE322Vinay JavalkarОценок пока нет

- 10EC/TE61: Answer Any FIVE Full Questions, Selecting at Least TWO Questions From Each PartДокумент2 страницы10EC/TE61: Answer Any FIVE Full Questions, Selecting at Least TWO Questions From Each PartdonyarmstrongОценок пока нет

- Mahendra College of Engineering: Salem-Campus, Attur Main Road, Minnampalli, Salem - 636 106Документ2 страницыMahendra College of Engineering: Salem-Campus, Attur Main Road, Minnampalli, Salem - 636 106Anonymous Ndsvh2soОценок пока нет

- Design and Analysis of Algorithms: Printed Page 1-2Документ2 страницыDesign and Analysis of Algorithms: Printed Page 1-2Utpal RaiОценок пока нет

- Design and Analysis of Algorithm Kcs 503Документ2 страницыDesign and Analysis of Algorithm Kcs 503sanuОценок пока нет

- Control Systems ExamДокумент3 страницыControl Systems ExamDankanVGowdaОценок пока нет

- Dte (22320)Документ71 страницаDte (22320)kolipratham1Оценок пока нет

- Digital Techniques Model Answer BreakdownДокумент26 страницDigital Techniques Model Answer Breakdownrishi sahuОценок пока нет

- MCS 012 June2010 June2023 IGNOUAssignmentGuru.comДокумент120 страницMCS 012 June2010 June2023 IGNOUAssignmentGuru.comsorcererstuffОценок пока нет

- MidSem CSE 1st YearДокумент4 страницыMidSem CSE 1st YearNayanjyot SinghОценок пока нет

- Microelectronic Circuits July 2017 (2010 Scheme)Документ2 страницыMicroelectronic Circuits July 2017 (2010 Scheme)Pavithra RОценок пока нет

- 17 scheme CEДокумент9 страниц17 scheme CEMadhu ReddyОценок пока нет

- Network Security: at Least TWO Questions From Each PartДокумент1 страницаNetwork Security: at Least TWO Questions From Each PartraghuramОценок пока нет

- Ec0033-Asic Design-Model Qp-Vii Sem-Set2Документ1 страницаEc0033-Asic Design-Model Qp-Vii Sem-Set2skarthikpriyaОценок пока нет

- 18EVE322Документ2 страницы18EVE322Vinay JavalkarОценок пока нет

- (08 Marks) (04 Marks)Документ2 страницы(08 Marks) (04 Marks)himanshu malikОценок пока нет

- CASE Tools: Adoption and RelevanceДокумент8 страницCASE Tools: Adoption and RelevancerohitОценок пока нет

- Cs10003: Programming and Data Structures: Indian Institute of Technology KharagpurДокумент75 страницCs10003: Programming and Data Structures: Indian Institute of Technology KharagpurRaghav DhamaniОценок пока нет

- TM 87 10049 - RevA - OTS v5 00 01Документ120 страницTM 87 10049 - RevA - OTS v5 00 01juan guillermo zapataОценок пока нет

- Soft Light Dimmer: Application NoteДокумент8 страницSoft Light Dimmer: Application NoteHassanein Al-hadadОценок пока нет

- RE 615ANSI DNP-3 Communication Manual 065952Документ44 страницыRE 615ANSI DNP-3 Communication Manual 065952Papun Kumar SwainОценок пока нет

- QPR322Документ148 страницQPR322apoorva m nОценок пока нет

- Active Exploitation: Con Uence Server CVE-2021-26084: Learn MoreДокумент2 страницыActive Exploitation: Con Uence Server CVE-2021-26084: Learn Morefateh tiribarkОценок пока нет

- Disaster Recovery For SAP HANAДокумент2 страницыDisaster Recovery For SAP HANAHasan ShahriarОценок пока нет

- Bani PDFДокумент5 страницBani PDFSushil KumarОценок пока нет

- Operation Manual: Worldwide Supplier of Gas Detection SolutionsДокумент32 страницыOperation Manual: Worldwide Supplier of Gas Detection Solutionsyosep naibahoОценок пока нет

- Rsran046 - Sho Adjacencies-CellpairДокумент10 страницRsran046 - Sho Adjacencies-CellpairOnnyОценок пока нет

- Grade 10 Baseline QuizДокумент3 страницыGrade 10 Baseline Quizishratj8736Оценок пока нет

- Exp3 - H3-Characteristics of PN Diode and Zener DiodeДокумент7 страницExp3 - H3-Characteristics of PN Diode and Zener Diodeshubhika guptaОценок пока нет

- Network Access Control Quiz ResultsДокумент2 страницыNetwork Access Control Quiz ResultsDaljeet SinghОценок пока нет

- Transformers Lecture 2Документ10 страницTransformers Lecture 2Ritesh JindalОценок пока нет

- How Cloud Telephony Is Changing The Way We Do BusinessДокумент13 страницHow Cloud Telephony Is Changing The Way We Do BusinessSonu KalwarОценок пока нет

- LD3 Mano ch3 - 2Документ35 страницLD3 Mano ch3 - 2Amr HefnyОценок пока нет

- Steps To Install Android Studio: Practical 1 Building A Simple Hello World ApplicationДокумент16 страницSteps To Install Android Studio: Practical 1 Building A Simple Hello World ApplicationDivya RajputОценок пока нет

- FS 8700 48 Fike CheetahДокумент36 страницFS 8700 48 Fike CheetahEric DunnОценок пока нет

- Table ListДокумент4 страницыTable ListRidho Saputro HutomoОценок пока нет

- Digital-Output Magnetic Sensor (Hall IC) : SSL0003-ANEДокумент8 страницDigital-Output Magnetic Sensor (Hall IC) : SSL0003-ANEHelder CabralОценок пока нет

- Fanuc 21i Configuration DocumentДокумент3 страницыFanuc 21i Configuration DocumentLeonardusОценок пока нет

- Mackie SRS1500 Service ManualДокумент0 страницMackie SRS1500 Service Manualmardonius100% (1)

- Sumator Cu Anticiparea TransportuluiДокумент10 страницSumator Cu Anticiparea TransportuluiCristea YoanaОценок пока нет

- Gorton ESAДокумент164 страницыGorton ESAAurelia PopaОценок пока нет

- CH7 - Remote IO & Wireless Sensing ModulesДокумент59 страницCH7 - Remote IO & Wireless Sensing Modulesatif_aman123Оценок пока нет