Академический Документы

Профессиональный Документы

Культура Документы

09 Cours-S2I2

Загружено:

bhfgtdОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

09 Cours-S2I2

Загружено:

bhfgtdАвторское право:

Доступные форматы

Université Paris-Sud

Extrait du PPN Mesures Physiques (Juillet 2007)

C- Semestre 2 : Tableau Horaire Majeure (Tronc Commun)

© Ministère de l'enseignement supérieur et de la recherche JUILLET 2007

Discipline Tronc Commun Module Cours TD TP Total Coef

UE 2-1 Formation Générale et Connaissance de l’Entreprise II

Langues, Culture et Communication II M 2-1-1 25 35 60 40

Mathématiques II M 2-1-2 20 30 50 30

Informatique M 2-1-3 8 10 27 45 20

UE 2-2 Techniques Instrumentales et Matériaux

Electronique I M 2-2-1 10 15 20 45 25

Informatique d’Instrumentation I M 2-2-1 10 15 20 45 25

Structure des Matériaux M 2-2-3 10 15 20 45 25

Propriétés des Matériaux M 2-2-4 10 15 20 45 25

Projet tutoré et ou PPP M 2-2-4 75 20

UE 2-3 Sciences et Techniques de l’Ingénieur II

Mécanique MC5-1 M 2-3-1 14 22 29 65 33

Machines Thermiques, Cryogénie M 2-3-2 6 9 30 45 24

Systèmes Optiques M 2-3-3 15 22 28 65 33

Total 103 178 229 510 + 75 (projet) 300

Cours d’Informatique d’Instrumentation I

Module M 2-2-2 : « Informatique d’Instrumentation I » – coefficient 25

Total : 45h C/TD/TP : 10/15/20

Pré-requis : acquis des modules M 1-2-1 « Electricité I » et M 1-2-2 « Electricité II ».

Objectifs : apprendre à mettre en oeuvre une chaîne d’acquisition de mesures.

Programme : Numération (codage, codes). Fonctions combinatoires et séquentielles (registres,

compteurs,..). Composants logiques (règles de connexion). Principe des quantificateurs, multiplexeurs,

échantillonneurs bloqueurs, convertisseurs AN et NA. Programmation d’une chaîne d’acquisition (langage,

carte d’acquisition multifonction).

Compétences : à l’issue de ce module, l’étudiant doit savoir traiter les signaux électriques et

comprendre l’acquisition des données.

Horaire au Dépt Mesures Physiques de l’IUT d’Orsay

Cours : 7 cours de 1h15 soit 8h45

TD : 9 séances de 1h30 soit 13h30

TP : 5 séances de 4h soit 20h

Exam : 1 séance 2h30

Total : 44h45

Enseignants : R. Reynaud ; F. Varnière ; T. Saïdani

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Planning 2009

C TD TP 4h

sem 20

sem 21

sem 22

sem 23

sem 24 1 Représentation des entiers

sem 25 2 Réels, Caractères, … TD 1 Nombres entiers

sem 26 3 Algèbre de Boole TD 2 Nombres entiers, nombres réels

sem 27 4 Fonctions combinatoires TD 3 Nombres réels

sem 28 5 Registres et compteurs TD 4 Algèbre de Boole

sem 29

sem 30 6 Convertisseurs

sem 31 7 Chaîne d’acquisition TD 5 Algèbre de Boole

sem 32 TD 6 Logique combinatoire TP1 Labview

E/S Analogiques

sem 33 TD 7 Logique combinatoire TP2 Labview

E/S Numériques

sem 34 TD 8 Logique séquentielle TP3 Contrôle logique

Robots

sem 35 TD 9 Logique séquentielle TP4 ABEL

CAN_CNA

sem 36 TP5

sem 37 Exam

MSB LSB

Cours 1 : semaine 24 Représentation des entiers

q Représentation des données pour l’utilisateur et dans une machine

q Représentation binaire non signée des entiers 8, 16, 32 bits

MSB, plage de représentation des entiers

MSB

Formule X = ∑a

n = LSB

n 2 n = a15 215+ a14 214+ a13 213+ … + a4 24+ a3 23+ a2 22+ a1 21+ a0 20

Algorithme Décimal à binaire : division successive par 2

Algorithme Binaire à décimal : Utilisation de la formule

q Représentation binaire signée des entiers 8, 16, 32 bits

Bit de signe = MSB, LSB, plage de représentation des entiers

15 14 13 4 3 2 1 0

Formule sur 16 bits X = - a15 2 + a14 2 + a13 2 + … + a4 2 + a3 2 + a2 2 + a1 2 + a0 2

Algorithme Décimal à binaire : Complément à 2 (Binariser la partie >0+complémenter chaque bit +1)

Algorithme Binaire à décimal : Utilisation de la formule

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Cours 2 : semaine 25 Représentation des Réels, Caractères,

q Représentation des nombres réels

Format Flottant simple précision sur 32 bits : norme IEEE 754.

Notation S ß Exposant E sur 8bitsà ß Mantisse m sur 23 bits à

E=0 0 < E < 255 E = 255

M=0 X=0 Forme usuelle X = (-1)S × ∞

Forme dénormalisée

M≠0 X = (-1)S × 2 - 126 × 0,m X = (-1)S × 2 E - 127 × (1,m) X = Not A Number

Format Flottant double précision sur 64 bits : norme IEEE 754.

Notation S ß Exposant E sur 11bitsà ß Mantisse m sur 52 bits à

E=0 0 < E < 2047 E = 2047

M=0 X=0 Forme usuelle X = (-1)S × ∞

Forme dénormalisée

M≠0 X = (-1)S × 2 -1022 × 0,m X = (-1)S × 2 E - 1023 × (1,m) X = Not A Number

Plage de représentation :Valeur maximum, minimum en mode normalisé

Précision relative garantie :

q Code binaire décalé pour utilisation en sortie de capteur

q Code binaire réfléchi dit code de Gray

q Code BCD (Décimal codé Binaire) pour conserver la précision des centimes

q Code Octal en base 8

q Code hexadécimal en base 16

q Représentation des caractères : un caractère par octet

q Représentation des chaînes de caractères

q Terminaison

En C un caractère NULL en fin de chaine

En Labview et Pascal : le premier octet indique la longueur de la chaine de caractère limitée donc à 255 caractères

Cours 3 : semaine 26 Algèbre de Boole

q Algèbre de BOOLE

2 valeurs possibles 0 à FAUX et 1 à VRAI + un ensemble d’opérateurs avec des propriétés

q Opérateurs ou portes logiques

OU NOR

ET NAND

NON XOR

q Propriétés permettant de simplifier les équations

Commutativité Complémentarité

Associativité Distributivité

Elémént neutre Absorption

Elément invariant Théorème de Morgan

Idempotence

q Exercices au tableau

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Cours 4 : semaine 27 Circuits combinatoires

q Circuits combinatoires

q Additionneurs

Demi additionneur : 2 entrées sur 1 bits à Une sortie sur 2 bits

Additionneur complet : 3 entrées sur 1 bits à Une sortie sur 2 bits

Additionneur sur n bits : 2 entrées sur N bits + une entrée sur 1 bità Une sortie sur N+1 bits

q Notations

Notation de l’état d’un port : Hà 1 ; l à 0 ; X à indifférent ou quelconque

Sortie active H ou sortie active L

Entrée active H ou entrée active L

q Décodeurs

Décodeurs : adresse sur 2 bits à 4 sorties de sélection dont une seule est à 1

Circuit constructeur avec port d’entrée de validation et sortie active L. Equations

Cascade de plusieurs circuits pour créer un décodeur d’une adresse sur 4 bits à 16 sortie (1 seule active)

q Mux ou multiplexeur

Met en relation une entrée parmi n avec la sortie

q Demultiplexeur

Met en relation une entrée avec une sortie prise parmi N

q Codeur

Opération inverse d’un décodeur

q Comparateur

Sortie VRAI ou FAUX indiquant la comparaison des entrées

Cours 5 : semaine 28 Circuits mémoires

q Circuits de mémorisation

q Bascules

Ø Asynchrone : les sorties réagissent aux variations des entrées

Ø Synchrone : les sorties se positionnent uniquement sur un front montant d’une horloge

Ø Bascule R S (Reset Set)

Ø Bascule J K

Ø Bascule T

Ø Bascule D

q Registres

Ø Registre parallèle

Ø Registre série

Ø Registre à décalage

Ø Compteur, décompteur

q Mémoires

Cours 6 : semaine 30 Convertisseurs Analogiques ß à Numériques

q Composants logiques

Ø Règles de conversion et force d’un signal

q Entrées- sorties analogiques

Ø Convertisseur NA : réseau échelle

Ø Convertisseur A N : Double intégration, incrémental, dichotomie, parallèle, Sigma-Delta

Ø Echantillonneur - bloqueur

Ø Multiplexeur analogique

Ø Carte d’acquisition, oscilloscope numérique

Cours 7 : semaine 32 Chaîne d’acquisition

q Programmation d’une chaîne d’acquisition

Ø Langage

Ø Carte d’acquisition multifonctions

Ø Instruments programmables

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Вам также может понравиться

- Examen 1 Corr 2015 FRДокумент3 страницыExamen 1 Corr 2015 FRchaddad abdllahОценок пока нет

- TD 2: Outils de Base de La QualitéДокумент12 страницTD 2: Outils de Base de La QualitéĎĢx 4š4Оценок пока нет

- TIA - Chap02 - Réseaux de Neurones Artificiels - NewДокумент20 страницTIA - Chap02 - Réseaux de Neurones Artificiels - NewNassr eddineОценок пока нет

- 02 10 241 PDFДокумент87 страниц02 10 241 PDFRora ÄsОценок пока нет

- Le Rôle de L Analogie en Théologie DogДокумент498 страницLe Rôle de L Analogie en Théologie DogS.R. PaineОценок пока нет

- Solides Et Sections Dans L Espace Et Calculs de Volumes Cours de 5emeДокумент6 страницSolides Et Sections Dans L Espace Et Calculs de Volumes Cours de 5emenzalakandaguymydhaОценок пока нет

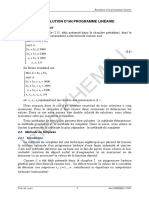

- Chap 2 Résolution D'un Programme LineaireДокумент15 страницChap 2 Résolution D'un Programme LineaireSou TibonОценок пока нет

- Chap2 TFDДокумент18 страницChap2 TFDFatma BelabedОценок пока нет

- C4M Isométries (Cours)Документ4 страницыC4M Isométries (Cours)Seif SouidОценок пока нет

- Cours m1 Econometrie Appliquee Slide3Документ23 страницыCours m1 Econometrie Appliquee Slide3Wajdi Frikha100% (1)

- Carnier D'exercices Types ItmДокумент26 страницCarnier D'exercices Types ItmEPHRICE KITENGE BIN MAKENGOОценок пока нет

- TD m1 Notions de CinematiqueДокумент1 страницаTD m1 Notions de CinematiqueMdzayd EL Fahime100% (1)

- Cem - Td1 - Enet'Com: Exercice 1Документ4 страницыCem - Td1 - Enet'Com: Exercice 1asma nsiriОценок пока нет

- CH2 - Technologies Cibles Pour Les Systèmes Sur Puce - CodesignДокумент24 страницыCH2 - Technologies Cibles Pour Les Systèmes Sur Puce - CodesignMed Aymen MessaoudiОценок пока нет

- Thermochimie Exercices 11Документ10 страницThermochimie Exercices 11anouar agadir0% (1)

- E - Chapitre 5 Processus de ChargementДокумент4 страницыE - Chapitre 5 Processus de ChargementMova GatalassОценок пока нет

- Etude MouvementДокумент3 страницыEtude MouvementJean Leonardo100% (1)

- Cocher Bonne Réponse:: Nom Et PrénomДокумент5 страницCocher Bonne Réponse:: Nom Et PrénommohadОценок пока нет

- COMPRESSUERSДокумент20 страницCOMPRESSUERSDjaber ElhaicharОценок пока нет

- 3 Les Vannes de Reglage-IiiДокумент4 страницы3 Les Vannes de Reglage-IiiSirineJamoussiОценок пока нет

- l3 Neurophysio Chap3Документ14 страницl3 Neurophysio Chap3nobodyОценок пока нет

- Devoir de Contrôle N°1 Avec Correction 2010 2011 (Abdessatar)Документ4 страницыDevoir de Contrôle N°1 Avec Correction 2010 2011 (Abdessatar)Ameni FerchichiОценок пока нет

- Correction Serie 05 - Decisions D'investissementsДокумент5 страницCorrection Serie 05 - Decisions D'investissementsmohameddhia ajmiОценок пока нет

- LE MODBUS CorrectionДокумент31 страницаLE MODBUS CorrectionmheuzОценок пока нет

- Le Tri A PaniersДокумент8 страницLe Tri A PaniersFunkalee100Оценок пока нет

- Forces Et Champs2Документ3 страницыForces Et Champs2MechoupiewouoОценок пока нет

- Annales I B 3Документ10 страницAnnales I B 3Rouchda Ibrahim100% (1)

- Grille de Validation Des Attendus Élève - 6emeДокумент2 страницыGrille de Validation Des Attendus Élève - 6emeJohanJorbbyОценок пока нет

- 43 Tutorial Assemblage VanneДокумент6 страниц43 Tutorial Assemblage VanneAkram Ben KhemisОценок пока нет

- CRPE - Orthographe, GrammaireДокумент3 страницыCRPE - Orthographe, GrammairePhilippe BriendОценок пока нет