Академический Документы

Профессиональный Документы

Культура Документы

Hufa76419P3, Hufa76419S3S: 27A, 60V, 0.040 Ohm, N-Channel, Logic Level Ultrafet® Power Mosfets Packaging Features

Загружено:

AlEjAnDrO CoNtReRaSОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Hufa76419P3, Hufa76419S3S: 27A, 60V, 0.040 Ohm, N-Channel, Logic Level Ultrafet® Power Mosfets Packaging Features

Загружено:

AlEjAnDrO CoNtReRaSАвторское право:

Доступные форматы

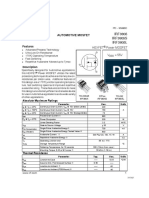

HUFA76419P3, HUFA76419S3S

Data Sheet December 2001

27A, 60V, 0.040 Ohm, N-Channel, Logic

Level UltraFET® Power MOSFETs

Packaging

JEDEC TO-220AB JEDEC TO-263AB Features

• Ultra Low On-Resistance

SOURCE

DRAIN

DRAIN - rDS(ON) = 0.035Ω, VGS = 10V

(FLANGE)

GATE - rDS(ON) = 0.040Ω, VGS = 5V

GATE • Simulation Models

- Temperature Compensated PSPICE® and SABER™

SOURCE Electrical Models

DRAIN

- Spice and SABER Thermal Impedance Models

(FLANGE) - www.fairchildsemi.com

HUFA76419P3 HUFA76419S3S • Peak Current vs Pulse Width Curve

• UIS Rating Curve

Symbol • Switching Time vs RGS Curves

D Ordering Information

PART NUMBER PACKAGE BRAND

G HUFA76419P3 TO-220AB 76419P

HUFA76419S3S TO-263AB 76419S

S NOTE: When ordering, use the entire part number. Add the suffix T

to obtain the variant in tape and reel, e.g., HUFA76419S3ST.

Absolute Maximum Ratings TC = 25oC, Unless Otherwise Specified

HUFA76419P3, HUFA76419S3S UNITS

Drain to Source Voltage (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDSS 60 V

Drain to Gate Voltage (RGS = 20kΩ) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDGR 60 V

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGS ±16 V

Drain Current

Continuous (TC = 25oC, VGS = 5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ID 27 A

Continuous (TC = 25oC, VGS = 10V) (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ID 29 A

Continuous (TC = 100oC, VGS = 5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ID 19 A

Continuous (TC = 100oC, VGS = 4.5V) (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ID 18 A

Pulsed Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IDM Figure 4

Pulsed Avalanche Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UIS Figures 6, 17, 18

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD 75 W

Derate Above 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 W/oC

Operating and Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG -55 to 175 oC

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TL 300 oC

Package Body for 10s, See Techbrief TB334. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T pkg 260 oC

NOTES:

1. TJ = 25oC to 150oC.

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

This product has been designed to meet the extreme test conditions and environment demanded by the automotive industry. For a copy

of the requirements, see AEC Q101 at: http://www.aecouncil.com/

Reliability data can be found at: http://www.fairchildsemi.com/products/discrete/reliability/index.html.

All Fairchild semiconductor products are manufactured, assembled and tested under ISO9000 and QS9000 quality systems certification.

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

Electrical Specifications TC = 25oC, Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

OFF STATE SPECIFICATIONS

Drain to Source Breakdown Voltage BVDSS ID = 250µA, VGS = 0V (Figure 12) 60 - - V

ID = 250µA, VGS = 0V , T C = -40oC (Figure 12) 55 - - V

Zero Gate Voltage Drain Current IDSS VDS = 55V, VGS = 0V - - 1 µA

VDS = 50V, VGS = 0V, TC = 150oC - - 250 µA

Gate to Source Leakage Current IGSS VGS = ±16V - - ±100 nA

ON STATE SPECIFICATIONS

Gate to Source Threshold Voltage VGS(TH) VGS = VDS, ID = 250µA (Figure 11) 1 - 3 V

Drain to Source On Resistance rDS(ON) ID = 29A, VGS = 10V (Figures 9, 10) - 0.029 0.035 Ω

ID = 19A, VGS = 5V (Figure 9) - 0.033 0.040 Ω

ID = 18A, VGS = 4.5V (Figure 9) - 0.035 0.044 Ω

THERMAL SPECIFICATIONS

Thermal Resistance Junction to Case RθJC TO-220 and TO-263 - - 2.0 oC/W

Thermal Resistance Junction to RθJA - - 62 oC/W

Ambient

SWITCHING SPECIFICATIONS (VGS = 4.5V)

Turn-On Time tON VDD = 30V, ID = 18A - - 245 ns

Turn-On Delay Time td(ON) VGS = 4.5V, RGS = 12Ω - 12 - ns

(Figures 15, 21, 22)

Rise Time tr - 150 - ns

Turn-Off Delay Time td(OFF) - 27 - ns

Fall Time tf - 55 - ns

Turn-Off Time tOFF - - 125 ns

SWITCHING SPECIFICATIONS (VGS = 10V)

Turn-On Time tON VDD = 30V, ID = 29A - - 110 ns

Turn-On Delay Time td(ON) VGS = 10V, - 6.7 - ns

RGS = 12Ω

Rise Time tr (Figures 16, 21, 22) - 66 - ns

Turn-Off Delay Time td(OFF) - 45 - ns

Fall Time tf - 76 - ns

Turn-Off Time tOFF - - 185 ns

GATE CHARGE SPECIFICATIONS

Total Gate Charge Qg(TOT) VGS = 0V to 10V VDD = 30V, - 22 28 nC

ID = 19A,

Gate Charge at 5V Qg(5) VGS = 0V to 5V - 13 16 nC

Ig(REF) = 1.0mA

Threshold Gate Charge Qg(TH) VGS = 0V to 1V - 0.9 1.1 nC

(Figures 14, 19, 20)

Gate to Source Gate Charge Qgs - 2.7 - nC

Gate to Drain "Miller" Charge Qgd - 6 - nC

CAPACITANCE SPECIFICATIONS

Input Capacitance CISS VDS = 25V, VGS = 0V, - 900 - pF

Output Capacitance COSS f = 1MHz - 250 - pF

(Figure 13)

Reverse Transfer Capacitance CRSS - 45 - pF

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Source to Drain Diode Voltage VSD ISD = 19A - - 1.25 V

ISD = 10A - - 1.0 V

Reverse Recovery Time trr ISD = 19A, dISD/dt = 100A/µs - - 78 ns

Reverse Recovered Charge QRR ISD = 19A, dISD/dt = 100A/µs - - 230 nC

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

Typical Performance Curves

1.2 30

POWER DISSIPATION MULTIPLIER

1.0 VGS = 10V

ID, DRAIN CURRENT (A)

0.8 20

VGS = 4.5V

0.6

0.4 10

0.2

0

0

0 25 50 75 100 125 150 175 25 50 75 100 125 150 175

TC , CASE TEMPERATURE (oC) TC, CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

TEMPERATURE CASE TEMPERATURE

2

DUTY CYCLE - DESCENDING ORDER

1 0.5

0.2

0.1

THERMAL IMPEDANCE

ZθJC, NORMALIZED

0.05

0.02

0.01

PDM

0.1

t1

t2

NOTES:

SINGLE PULSE DUTY FACTOR: D = t1/t2

PEAK TJ = PDM x ZθJC x RθJC + TC

0.01

10-5 10-4 10-3 10-2 10-1 100 101

t, RECTANGULAR PULSE DURATION (s)

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

500

TC = 25oC

FOR TEMPERATURES

ABOVE 25oC DERATE PEAK

IDM, PEAK CURRENT (A)

CURRENT AS FOLLOWS:

I = I25 175 - TC

100

150

VGS = 10V VGS = 5V

TRANSCONDUCTANCE

MAY LIMIT CURRENT

IN THIS REGION

10

10-5 10-4 10-3 10-2 10-1 100 101

t, PULSE WIDTH (s)

FIGURE 4. PEAK CURRENT CAPABILITY

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

Typical Performance Curves (Continued)

200 60

100

IAS, AVALANCHE CURRENT (A)

STARTING TJ = 25oC

ID, DRAIN CURRENT (A)

100µs 10 STARTING TJ = 150oC

10

OPERATION IN THIS

AREA MAY BE

LIMITED BY rDS(ON) 1ms

If R = 0

tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD)

SINGLE PULSE

10ms If R ≠ 0

TJ = MAX RATED TC = 25oC tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

1 1

1 10 100 200 0.001 0.01 0.1 1 10

VDS, DRAIN TO SOURCE VOLTAGE (V) tAV, TIME IN AVALANCHE (ms)

NOTE: Refer to Fairchild Application Notes AN9321 and AN9322.

FIGURE 5. FORWARD BIAS SAFE OPERATING AREA FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING

CAPABILITY

60 60

PULSE DURATION = 80µs VGS = 10V

VGS = 5V

DUTY CYCLE = 0.5% MAX

50 VDD = 15V 50

ID, DRAIN CURRENT (A)

ID, DRAIN CURRENT (A)

VGS = 4V

40 40

30 30

VGS = 3.5V

20 20

PULSE DURATION = 80µs

TJ = 175oC DUTY CYCLE = 0.5% MAX

10 10

TJ = 25oC

VGS = 3V TC = 25oC

TJ = -55oC

0 0

1 2 3 4 5 0 1 2 3 4

VGS, GATE TO SOURCE VOLTAGE (V) VDS, DRAIN TO SOURCE VOLTAGE (V)

FIGURE 7. TRANSFER CHARACTERISTICS FIGURE 8. SATURATION CHARACTERISTICS

50 2.5

ID = 29A PULSE DURATION = 80µs PULSE DURATION = 80µs

NORMALIZED DRAIN TO SOURCE

DUTY CYCLE = 0.5% MAX DUTY CYCLE = 0.5% MAX

TC = 25oC

rDS(ON), DRAIN TO SOURCE

ID = 10A

ON RESISTANCE (mΩ)

2.0

ON RESISTANCE

40

ID = 19A

1.5

30

1.0

VGS = 10V, ID = 29A

20 0.5

2 4 6 8 10 -80 -40 0 40 80 120 160 200

VGS, GATE TO SOURCE VOLTAGE (V) TJ, JUNCTION TEMPERATURE (oC)

FIGURE 9. DRAIN TO SOURCE ON RESISTANCE vs GATE FIGURE 10. NORMALIZED DRAIN TO SOURCE ON

VOLTAGE AND DRAIN CURRENT RESISTANCE vs JUNCTION TEMPERATURE

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

Typical Performance Curves (Continued)

1.2 1.2

VGS = VDS, ID = 250µA ID = 250µA

NORMALIZED DRAIN TO SOURCE

BREAKDOWN VOLTAGE

THRESHOLD VOLTAGE

1.0

NORMALIZED GATE

1.1

0.8

1.0

0.6

0.4 0.9

-80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200

TJ, JUNCTION TEMPERATURE (oC) TJ , JUNCTION TEMPERATURE (oC)

FIGURE 11. NORMALIZED GATE THRESHOLD VOLTAGE vs FIGURE 12. NORMALIZED DRAIN TO SOURCE BREAKDOWN

JUNCTION TEMPERATURE VOLTAGE vs JUNCTION TEMPERATURE

2000 10

VGS , GATE TO SOURCE VOLTAGE (V)

CISS = CGS + CGD VDD = 30V

1000

COSS ≅ CDS + CGD 8

C, CAPACITANCE (pF)

6

CRSS = CGD

100

4

WAVEFORMS IN

DESCENDING ORDER:

2 ID = 29A

ID = 19A

VGS = 0V, f = 1MHz ID = 10A

10 0

0.1 1 10 60 0 5 10 15 20 25

VDS , DRAIN TO SOURCE VOLTAGE (V) Qg, GATE CHARGE (nC)

NOTE: Refer to Fairchild Application Notes AN7254 and AN7260.

FIGURE 13. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE FIGURE 14. GATE CHARGE WAVEFORMS FOR CONSTANT

GATE CURRENT

250 150

VGS = 4.5V, VDD = 30V, ID = 18A VGS = 10V, V DD = 30V, ID = 29A

tr

200

SWITCHING TIME (ns)

SWITCHING TIME (ns)

100

150 tf

tr

tf

100

td(OFF) 50

td(OFF)

50

td(ON)

td(ON)

0 0

0 10 20 30 40 50 0 10 20 30 40 50

RGS, GATE TO SOURCE RESISTANCE (Ω) RGS, GATE TO SOURCE RESISTANCE (Ω)

FIGURE 15. SWITCHING TIME vs GATE RESISTANCE FIGURE 16. SWITCHING TIME vs GATE RESISTANCE

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

Test Circuits and Waveforms

VDS

BVDSS

L tP

VDS

VARY tP TO OBTAIN IAS

+ VDD

REQUIRED PEAK IAS RG

VDD

VGS -

DUT

tP

0V IAS

0

0.01Ω

tAV

FIGURE 17. UNCLAMPED ENERGY TEST CIRCUIT FIGURE 18. UNCLAMPED ENERGY WAVEFORMS

VDS

RL VDD Qg(TOT)

VDS

VGS = 10V

VGS Qg(5)

+

VDD

VGS VGS = 5V

-

DUT VGS = 1V

Ig(REF) 0

Qg(TH)

Qgs Qgd

Ig(REF)

0

FIGURE 19. GATE CHARGE TEST CIRCUIT FIGURE 20. GATE CHARGE WAVEFORMS

VDS tON tOFF

td(ON) td(OFF)

RL tr tf

VDS

90% 90%

+

VGS

VDD 10% 10%

- 0

DUT 90%

RGS

VGS 50% 50%

PULSE WIDTH

VGS 10%

0

FIGURE 21. SWITCHING TIME TEST CIRCUIT FIGURE 22. SWITCHING TIME WAVEFORM

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

PSPICE Electrical Model

.SUBCKT HUFA76419 2 1 3 ; rev 21 June 1999

CA 12 8 1.1e-9

CB 15 14 1.1e-9

CIN 6 8 8.5e-10

DBODY 7 5 DBODYMOD

LDRAIN

DBREAK 5 11 DBREAKMOD DPLCAP 5 DRAIN

DPLCAP 10 5 DPLCAPMOD 2

10

RLDRAIN

EBREAK 11 7 17 18 69.6 RSLC1

51 DBREAK

EDS 14 8 5 8 1 +

EGS 13 8 6 8 1 RSLC2

5

ESG 6 10 6 8 1 ESLC 11

51

EVTHRES 6 21 19 8 1 -

EVTEMP 20 6 18 22 1 50 +

-

RDRAIN 17 DBODY

6 EBREAK 18

ESG 8

IT 8 17 1

+ EVTHRES 16

-

+ 19 - 21

LDRAIN 2 5 1e-9 LGATE EVTEMP MWEAK

8

LGATE 1 9 4.4e-9 GATE RGATE + 18 - 6

LSOURCE 3 7 4.5e-9 1 22 MMED

9 20

RLGATE MSTRO

MMED 16 6 8 8 MMEDMOD

MSTRO 16 6 8 8 MSTROMOD LSOURCE

CIN SOURCE

MWEAK 16 21 8 8 MWEAKMOD 8 7 3

RBREAK 17 18 RBREAKMOD 1 RSOURCE

RLSOURCE

RDRAIN 50 16 RDRAINMOD 1.5e-2

RGATE 9 20 3.1 S1A S2A

12 RBREAK

RLDRAIN 2 5 10 13 14 15

17 18

RLGATE 1 9 44 8 13

RLSOURCE 3 7 45

S1B S2B RVTEMP

RSLC1 5 51 RSLCMOD 1e-6

RSLC2 5 50 1e3 13 CB 19

CA

RSOURCE 8 7 RSOURCEMOD 9e-3 + + 14 IT -

RVTHRES 22 8 RVTHRESMOD 1 6 5 VBAT

RVTEMP 18 19 RVTEMPMOD 1 EGS EDS +

8 8

- - 8

S1A 6 12 13 8 S1AMOD 22

S1B 13 12 13 8 S1BMOD RVTHRES

S2A 6 15 14 13 S2AMOD

S2B 13 15 14 13 S2BMOD

VBAT 22 19 DC 1

ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*70),3.5))}

.MODEL DBODYMOD D (IS = 1.3e-12 RS = 7.5e-3 TRS1 = 1e-4 TRS2 = 3e-6 CJO = 1.07e-9 TT = 4.9e-8 N = 1.03 M = 0.5)

.MODEL DBREAKMOD D (RS = 3.5e- 1TRS1 = 1e- 4TRS2 = 0)

.MODEL DPLCAPMOD D (CJO = 7.5e-1 0IS = 1e-3 0N = 10 M = 0.85)

.MODEL MMEDMOD NMOS (VTO = 2.0 KP = 4 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 3.1)

.MODEL MSTROMOD NMOS (VTO = 2.34 KP = 43 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u)

.MODEL MWEAKMOD NMOS (VTO = 1.74 KP = 0.13 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 31 RS = 0.1)

.MODEL RBREAKMOD RES (TC1 = 1.2e- 3TC2 = -5e-7)

.MODEL RDRAINMOD RES (TC1 = 9e-3 TC2 = 2e-5)

.MODEL RSLCMOD RES (TC1 = 3.5e-3 TC2 = 7e-6)

.MODEL RSOURCEMOD RES (TC1 = 1e-3 TC2 = 1e-6)

.MODEL RVTHRESMOD RES (TC1 = -1.8e-3 TC2 = -5.8e-6)

.MODEL RVTEMPMOD RES (TC1 = -1.7e- 3TC2 = 1e-6)

.MODEL S1AMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -4.5 VOFF= -2.8)

.MODEL S1BMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -2.8 VOFF= -4.5)

.MODEL S2AMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -0.5 VOFF= 0.5)

.MODEL S2BMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = 0.5 VOFF= -0.5)

.ENDS

NOTE: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global

Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank Wheatley.

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

SABER Electrical Model

REV 21 June 1999

template HUFA76419 n2,n1,n3

electrical n2,n1,n3

{

var i iscl

d..model dbodymod = (is = 1.3e-12, cjo = 1.07e-9, tt = 4.9e-8, n=1.03, m = 0.5)

d..model dbreakmod = ()

d..model dplcapmod = (cjo = 7.5e-10, is = 1e-30, m = 0.85, n = 10)

m..model mmedmod = (type=_n, vto = 2.0, kp = 4, is = 1e-30, tox = 1)

m..model mstrongmod = (type=_n, vto = 2.34, kp = 43, is = 1e-30, tox = 1) LDRAIN

m..model mweakmod = (type=_n, vto = 1.74, kp = 0.13, is = 1e-30, tox = 1) DPLCAP 5 DRAIN

sw_vcsp..model s1amod = (ron = 1e-5, roff = 0.1, von = -4.5, voff = -2.8) 2

10

sw_vcsp..model s1bmod = (ron =1e-5, roff = 0.1, von = -2.8, voff = -4.5) RLDRAIN

sw_vcsp..model s2amod = (ron = 1e-5, roff = 0.1, von = -0.5, voff = 0.5) RSLC1

sw_vcsp..model s2bmod = (ron = 1e-5, roff = 0.1, von = 0.5, voff = -0.5) 51 RDBREAK

RSLC2

72 RDBODY

c.ca n12 n8 = 1.1e-9 ISCL

c.cb n15 n14 = 1.1e-9

c.cin n6 n8 = 8.5e-10 50 DBREAK

-

6 RDRAIN 71

d.dbody n7 n71 = model=dbodymod ESG 8 11

d.dbreak n72 n11 = model=dbreakmod + EVTHRES 16

d.dplcap n10 n5 = model=dplcapmod + 19 - 21

LGATE EVTEMP MWEAK

8 DBODY

i.it n8 n17 = 1 GATE RGATE + 18 - 6

1 MMED EBREAK

9 22 +

20

l.ldrain n2 n5 = 1e-9 RLGATE MSTRO 17

l.lgate n1 n9 = 4.4e-9 18 LSOURCE

l.lsource n3 n7 = 4.5e-9 CIN

8

- SOURCE

7 3

m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u RSOURCE

m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u RLSOURCE

m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u S1A S2A

12 RBREAK

13 14 15

res.rbreak n17 n18 = 1, tc1 = 1.2e-3, tc2 = -5e-7 17 18

8 13

res.rdbody n71 n5 = 7.5e-3, tc1 = 1e-4, tc2 = 3e-6

S1B S2B RVTEMP

res.rdbreak n72 n5 = 3.5e-1, tc1 = 1e-4, tc2 = 0

res.rdrain n50 n16 = 1.5e-2, tc1 = 9e-3, tc2 = 2e-5 13 CB 19

CA

res.rgate n9 n20 = 3.1 + + 14 IT -

res.rldrain n2 n5 = 10 6 5 VBAT

res.rlgate n1 n9 = 44 EGS 8 EDS 8 +

res.rlsource n3 n7 = 45 - - 8

res.rslc1 n5 n51 = 1e-6, tc1 = 3.5e-3, tc2 = 7e-6 22

res.rslc2 n5 n50 = 1e3 RVTHRES

res.rsource n8 n7 = 9e-3, tc1 = 1e-3, tc2 = 1e-6

res.rvtemp n18 n19 = 1, tc1 = -1.7e-3, tc2 = 1e-6

res.rvthres n22 n8 = 1, tc1 = -1.8e-3, tc2 = -5.8e-6

spe.ebreak n11 n7 n17 n18 = 69.6

spe.eds n14 n8 n5 n8 = 1

spe.egs n13 n8 n6 n8 = 1

spe.esg n6 n10 n6 n8 = 1

spe.evtemp n20 n6 n18 n22 = 1

spe.evthres n6 n21 n19 n8 = 1

sw_vcsp.s1a n6 n12 n13 n8 = model=s1amod

sw_vcsp.s1b n13 n12 n13 n8 = model=s1bmod

sw_vcsp.s2a n6 n15 n14 n13 = model=s2amod

sw_vcsp.s2b n13 n15 n14 n13 = model=s2bmod

v.vbat n22 n19 = dc=1

equations {

i (n51->n50) +=iscl

iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/70))** 3.5))

}

}

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

HUFA76419P3, HUFA76419S3S

SPICE Thermal Model th JUNCTION

REV 21 June 1999

HUFA76419T

CTHERM1 th 6 1.1e-3 RTHERM1 CTHERM1

CTHERM2 6 5 2.5e-3

CTHERM3 5 4 3.6e-3

CTHERM4 4 3 8.2e-3 6

CTHERM5 3 2 2.6e-2

CTHERM6 2 tl 3.5e-1

RTHERM1 th 6 6.8e-3 RTHERM2 CTHERM2

RTHERM2 6 5 8.4e-2

RTHERM3 5 4 3.9e-1

RTHERM4 4 3 4.2e-1 5

RTHERM5 3 2 5.0e-1

RTHERM6 2 tl 2.0e-1

RTHERM3 CTHERM3

SABER Thermal Model

SABER thermal model HUFA76419T

4

template thermal_model th tl

thermal_c th, tl

{

RTHERM4 CTHERM4

ctherm.ctherm1 th 6 = 1.1e-3

ctherm.ctherm2 6 5 = 2.5e-3

ctherm.ctherm3 5 4 = 3.6e-3

ctherm.ctherm4 4 3 = 8.2e-3 3

ctherm.ctherm5 3 2 = 2.6e-2

ctherm.ctherm6 2 tl = 3.5e-1

RTHERM5 CTHERM5

rtherm.rtherm1 th 6 = 6.8e-3

rtherm.rtherm2 6 5 = 8.4e-2

rtherm.rtherm3 5 4 = 3.9e-1

rtherm.rtherm4 4 3 = 4.2e-1 2

rtherm.rtherm5 3 2 = 5.0e-1

rtherm.rtherm6 2 tl = 2.0e-1

} RTHERM6 CTHERM6

tl CASE

©2001 Fairchild Semiconductor Corporation HUFA76419P3, HUFA76419S3S Rev. B

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx™ FAST OPTOLOGIC™ SMART START™ VCX™

Bottomless™ FASTr™ OPTOPLANAR™ STAR*POWER™

CoolFET™ FRFET™ PACMAN™ Stealth™

CROSSVOLT™ GlobalOptoisolator™ POP™ SuperSOT™-3

DenseTrench™ GTO™ Power247™ SuperSOT™-6

DOME™ HiSeC™ PowerTrench SuperSOT™-8

EcoSPARK™ ISOPLANAR™ QFET™ SyncFET™

E2CMOSTM LittleFET™ QS™ TinyLogic™

EnSignaTM MicroFET™ QT Optoelectronics™ TruTranslation™

FACT™ MicroPak™ Quiet Series™ UHC™

FACT Quiet Series™ MICROWIRE™ SILENT SWITCHER UltraFET

STAR*POWER is used under license

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT

RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. H4

Вам также может понравиться

- Casio G-Shock Secret Features and Hidden Screens - 60clicksДокумент8 страницCasio G-Shock Secret Features and Hidden Screens - 60clicksVannex Mensidor100% (2)

- Arduino Mega 2560 Crazy Kit ManualДокумент181 страницаArduino Mega 2560 Crazy Kit Manualjasmina_cip100% (6)

- Everlast INTERVAL TRAINING ROUND TIMER PDFДокумент1 страницаEverlast INTERVAL TRAINING ROUND TIMER PDFanniaanniaОценок пока нет

- Manual SL7000Документ101 страницаManual SL7000Juan Carlos Camacho SilesОценок пока нет

- Ev ChargersДокумент29 страницEv ChargersAjay Yadav100% (1)

- Visual & Special Effects ProposalДокумент10 страницVisual & Special Effects ProposalMayur Dev SewakОценок пока нет

- Datasheet: SE-B1, B2, B3, B4Документ4 страницыDatasheet: SE-B1, B2, B3, B4Juan GuzmanОценок пока нет

- VTT10000 Manual PDFДокумент6 страницVTT10000 Manual PDFalekyaОценок пока нет

- Huf 76633 S 3 STДокумент10 страницHuf 76633 S 3 STAdlan MessaoudОценок пока нет

- Huf75645P3, Huf75645S3S: N-Channel Ultrafet Power MosfetДокумент10 страницHuf75645P3, Huf75645S3S: N-Channel Ultrafet Power Mosfetinfo.wenamericaОценок пока нет

- Huf75645P3, Huf75645S3S: 75A, 100V, 0.014 Ohm, N-Channel, Ultrafet® Power Mosfets Packaging FeaturesДокумент10 страницHuf75645P3, Huf75645S3S: 75A, 100V, 0.014 Ohm, N-Channel, Ultrafet® Power Mosfets Packaging FeaturesTon WiseОценок пока нет

- Data Sheet Huf 75852 G 3Документ10 страницData Sheet Huf 75852 G 3FERNANDO FERRUSCAОценок пока нет

- Datasheet Mosfet 76132PДокумент10 страницDatasheet Mosfet 76132Padam woodОценок пока нет

- Data SheetДокумент11 страницData SheetYoscar SanchezОценок пока нет

- HUF75545P3Документ10 страницHUF75545P3Alin MarianОценок пока нет

- 16N06LE FairchildSemiconductorДокумент7 страниц16N06LE FairchildSemiconductorHarald DasselОценок пока нет

- Irfp150n PDFДокумент11 страницIrfp150n PDFAbhijithОценок пока нет

- Isl9N306Ap3/Isl9N306As3St: N-Channel Logic Level PWM Optimized Ultrafet® Trench Power MosfetsДокумент12 страницIsl9N306Ap3/Isl9N306As3St: N-Channel Logic Level PWM Optimized Ultrafet® Trench Power MosfetsСергей БрегедаОценок пока нет

- IRF9520Документ7 страницIRF9520Emilio QuijanoОценок пока нет

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Документ8 страниц6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999Оценок пока нет

- Huf75344G3, Huf75344P3: N-Channel Ultrafet Power Mosfet FeaturesДокумент10 страницHuf75344G3, Huf75344P3: N-Channel Ultrafet Power Mosfet FeaturesChristina MullinsОценок пока нет

- Datasheet RFD16 N05Документ8 страницDatasheet RFD16 N05Nicolau FrançaОценок пока нет

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesДокумент8 страницIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesCesar AzcargortaОценок пока нет

- Rfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets FeaturesДокумент8 страницRfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets Featuresfahmi1987Оценок пока нет

- IRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesДокумент7 страницIRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesAmirОценок пока нет

- 75332S. Trans PDFДокумент10 страниц75332S. Trans PDFDiego CaceresОценок пока нет

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesДокумент7 страницIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesAbel RodriguezОценок пока нет

- RFP50N06: N-Channel Power MOSFET 60V, 50A, 22 M FeaturesДокумент8 страницRFP50N06: N-Channel Power MOSFET 60V, 50A, 22 M FeaturesMohammd EssaОценок пока нет

- Irf 630Документ7 страницIrf 630ban4444Оценок пока нет

- IRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesДокумент8 страницIRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesulisesОценок пока нет

- Fdb20an06a0 1305401Документ14 страницFdb20an06a0 1305401Moi CanoОценок пока нет

- DatasheetДокумент7 страницDatasheetmaximon13Оценок пока нет

- IRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesДокумент7 страницIRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesFran Javi Vila DiazОценок пока нет

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Документ8 страниц10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Lotfi MessaadiОценок пока нет

- RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesДокумент8 страницRFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets Featureswert1a2Оценок пока нет

- Datasheet IRFP 9240Документ7 страницDatasheet IRFP 9240AguilaSolitariaОценок пока нет

- Irf3805Pbf Irf3805Spbf Irf3805Lpbf: FeaturesДокумент14 страницIrf3805Pbf Irf3805Spbf Irf3805Lpbf: Featurescarmel asentistaОценок пока нет

- Irf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: FeaturesДокумент12 страницIrf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: FeaturesVasja OlijarnykОценок пока нет

- IRF 3805-IRF 3805S-IRF 3805L - MosfetДокумент12 страницIRF 3805-IRF 3805S-IRF 3805L - MosfetTiago LeonhardtОценок пока нет

- Preliminary: ARF464A ARF464BДокумент4 страницыPreliminary: ARF464A ARF464Bjingsong heОценок пока нет

- IRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesДокумент6 страницIRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesJaime Enrique ValbuenaОценок пока нет

- FDB13AN06A0Документ11 страницFDB13AN06A0kamil.smolinski.1980Оценок пока нет

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Документ7 страниц5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Rudi AnotheerОценок пока нет

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Документ7 страниц5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Jaricsa BernaolaОценок пока нет

- IRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesДокумент7 страницIRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesvetchboyОценок пока нет

- Irf510 PDFДокумент7 страницIrf510 PDFandri SyahputraОценок пока нет

- Infineon IRFP4332 DataSheet v01 - 01 ENДокумент10 страницInfineon IRFP4332 DataSheet v01 - 01 ENmanuel sierraОценок пока нет

- Irfp4332Pbf: PDP SwitchДокумент9 страницIrfp4332Pbf: PDP SwitchWilliam Rodriguez BermudezОценок пока нет

- IRF540ZPBFДокумент12 страницIRF540ZPBFJose M PeresОценок пока нет

- 14N25 FairchildSemiconductorДокумент8 страниц14N25 FairchildSemiconductorPaulo Henrique SОценок пока нет

- Fdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsДокумент6 страницFdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsAli R.MОценок пока нет

- IRF3205ZДокумент13 страницIRF3205Zdaniel_yonutz07Оценок пока нет

- HGTG 30N60A4 - Fairchild PDFДокумент8 страницHGTG 30N60A4 - Fairchild PDFStevenОценок пока нет

- FQB60N03L: N-Channel Logic Level PWM Optimized Power MOSFETДокумент11 страницFQB60N03L: N-Channel Logic Level PWM Optimized Power MOSFETbelga cemОценок пока нет

- NTE469-Replacemet For J113Документ2 страницыNTE469-Replacemet For J113rdbassesОценок пока нет

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999Документ7 страниц10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999FadiОценок пока нет

- IRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets FeaturesДокумент7 страницIRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets Featuresabduallah muhammadОценок пока нет

- Irlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetДокумент13 страницIrlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetrickiaqpОценок пока нет

- 8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Документ8 страниц8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Agus SuwardonoОценок пока нет

- 8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Документ8 страниц8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Chris GuarinОценок пока нет

- Datasheet For Irfp240Документ7 страницDatasheet For Irfp240Kandeke DaviesОценок пока нет

- Datasheet IRF840 MOSFETДокумент10 страницDatasheet IRF840 MOSFETEdwin FlorezОценок пока нет

- RF Power Mosfets: N - Channel Enhancement ModeДокумент4 страницыRF Power Mosfets: N - Channel Enhancement Modejingsong heОценок пока нет

- IRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesДокумент7 страницIRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesAdah BumboneОценок пока нет

- FDP3652Документ11 страницFDP3652Dávid KisОценок пока нет

- FDPA Programing1231Документ10 страницFDPA Programing1231Engr. Syed Ghulam Mustafa ShahОценок пока нет

- CM-ENS.2x: Liquid Level Monitoring RelayДокумент12 страницCM-ENS.2x: Liquid Level Monitoring RelayAlEjAnDrO CoNtReRaSОценок пока нет

- Zelio Logic SR3B101FUДокумент6 страницZelio Logic SR3B101FUAlexcgОценок пока нет

- Smart Relay - Zelio Logic SR2 - SR3 - SR2USB01Документ1 страницаSmart Relay - Zelio Logic SR2 - SR3 - SR2USB01AlEjAnDrO CoNtReRaSОценок пока нет

- 2CDC110004C0210 02 G 2017 11 07Документ108 страниц2CDC110004C0210 02 G 2017 11 07Sijo JoyОценок пока нет

- Smart Relay - Zelio Logic SR2 - SR3 - SR3B101FUДокумент6 страницSmart Relay - Zelio Logic SR2 - SR3 - SR3B101FUAlEjAnDrO CoNtReRaSОценок пока нет

- Compresor CraftmanДокумент40 страницCompresor CraftmanAlEjAnDrO CoNtReRaSОценок пока нет

- GT3 SeriesДокумент24 страницыGT3 SeriesAgus RohmatОценок пока нет

- US ProgramДокумент20 страницUS ProgramraitoОценок пока нет

- Specifications: AA... C2 Differential Air Pressure Switch Installation InstructionsДокумент4 страницыSpecifications: AA... C2 Differential Air Pressure Switch Installation InstructionsAlEjAnDrO CoNtReRaSОценок пока нет

- Specifications: AA... C2 Differential Air Pressure Switch Installation InstructionsДокумент4 страницыSpecifications: AA... C2 Differential Air Pressure Switch Installation InstructionsAlEjAnDrO CoNtReRaSОценок пока нет

- Gas Appliance Pressure Regulators With Integrated Gas Filter FRI/6 SeriesДокумент8 страницGas Appliance Pressure Regulators With Integrated Gas Filter FRI/6 SeriesAlEjAnDrO CoNtReRaSОценок пока нет

- Dual Modular Safety Shutoff Valves DMV-D/602 Series DMV-DLE/602 SeriesДокумент6 страницDual Modular Safety Shutoff Valves DMV-D/602 Series DMV-DLE/602 SeriesAlEjAnDrO CoNtReRaSОценок пока нет

- Intel Optane Memory User InstallationДокумент66 страницIntel Optane Memory User InstallationAlEjAnDrO CoNtReRaSОценок пока нет

- Kodak Dryview 5850 PDFДокумент40 страницKodak Dryview 5850 PDFJohn RipperОценок пока нет

- ArduinoMEGA2560 PDFДокумент8 страницArduinoMEGA2560 PDFvvipmembersОценок пока нет

- ArduinoMEGA2560 PDFДокумент8 страницArduinoMEGA2560 PDFvvipmembersОценок пока нет

- CM-ENS.2x: Liquid Level Monitoring RelayДокумент12 страницCM-ENS.2x: Liquid Level Monitoring RelayAlEjAnDrO CoNtReRaSОценок пока нет

- Espa Ol-Ingles - Diccionario T CnicoДокумент2 страницыEspa Ol-Ingles - Diccionario T CnicoAlEjAnDrO CoNtReRaSОценок пока нет

- ArduinoMEGA2560 PDFДокумент8 страницArduinoMEGA2560 PDFvvipmembersОценок пока нет

- 2CDC110004C0210 02 G 2017 11 07Документ108 страниц2CDC110004C0210 02 G 2017 11 07Sijo JoyОценок пока нет

- Espa Ol-Ingles - Diccionario T CnicoДокумент2 страницыEspa Ol-Ingles - Diccionario T CnicoAlEjAnDrO CoNtReRaSОценок пока нет

- MATLAB Simulink TutorialДокумент26 страницMATLAB Simulink Tutorialigorica100% (2)

- Solucionario de Álgebra Lineal, 5a Ed PDFДокумент633 страницыSolucionario de Álgebra Lineal, 5a Ed PDFEmmanuelОценок пока нет

- MATLAB Simulink TutorialДокумент26 страницMATLAB Simulink Tutorialigorica100% (2)

- Merivaara OP-1700 Operating Table - Service ManualДокумент24 страницыMerivaara OP-1700 Operating Table - Service ManualAlEjAnDrO CoNtReRaS100% (1)

- Professional 5400N and 3400 User GuideДокумент240 страницProfessional 5400N and 3400 User GuideAlEjAnDrO CoNtReRaSОценок пока нет

- NTDCL 2021a.pdf Version 1Документ16 страницNTDCL 2021a.pdf Version 1engrkumailabbasОценок пока нет

- SK720 ManualДокумент43 страницыSK720 ManualrandyromОценок пока нет

- Data Sheet Led 5mm RGBДокумент3 страницыData Sheet Led 5mm RGBMuhammad Nuzul Nur مسلمОценок пока нет

- Sot Sc70 OcapДокумент63 страницыSot Sc70 OcapPBlurnz005100% (2)

- Alfano Pro: Serial: (82500 - 99999) (20000 - 59999)Документ8 страницAlfano Pro: Serial: (82500 - 99999) (20000 - 59999)BobyRDMОценок пока нет

- TLE-CHS-q3 - Mod7 - Basic-Concepts-of-Electricity - (Part-II) M4Документ16 страницTLE-CHS-q3 - Mod7 - Basic-Concepts-of-Electricity - (Part-II) M4OmengMagcalas100% (2)

- Schneider Clipsal ESM32D20NAДокумент3 страницыSchneider Clipsal ESM32D20NAUmer Farooq100% (1)

- Spectralert® Series: Horns, Strobes, and Horn/StrobesДокумент4 страницыSpectralert® Series: Horns, Strobes, and Horn/Strobesmechengineer3Оценок пока нет

- Drossel EnglishДокумент48 страницDrossel EnglishJuliet SinghОценок пока нет

- 20E082-SP Offer ListДокумент1 страница20E082-SP Offer ListghghОценок пока нет

- DPMErr SEДокумент10 страницDPMErr SEarelyta8123Оценок пока нет

- Contain CeДокумент4 страницыContain CenageshОценок пока нет

- Service Manual: MT1192 19" Color TelevisionДокумент54 страницыService Manual: MT1192 19" Color TelevisionHamilton MoranОценок пока нет

- Operating Instructions UEZ - Intrusion AlarmДокумент48 страницOperating Instructions UEZ - Intrusion AlarmNarcis PatrascuОценок пока нет

- Floor Box Brochure Q-1270BДокумент8 страницFloor Box Brochure Q-1270BEDGAR HUGO CANO HURTADOОценок пока нет

- VA (CR) General DatasheetДокумент56 страницVA (CR) General DatasheetManoj MahendiaОценок пока нет

- 2009 SAJC Prelims H2 P2 QuestionsДокумент18 страниц2009 SAJC Prelims H2 P2 QuestionsJasonОценок пока нет

- "Smart Dustbin Using Arduino": Maharashtra State Board of Technical Education, MumbaiДокумент22 страницы"Smart Dustbin Using Arduino": Maharashtra State Board of Technical Education, MumbaiEr Dinesh TambeОценок пока нет

- Areas of Specialisation in GENCO and DISCO - PPДокумент33 страницыAreas of Specialisation in GENCO and DISCO - PPchdiОценок пока нет

- Instructions For Use en Xo Flex Version 2 02 PDFДокумент95 страницInstructions For Use en Xo Flex Version 2 02 PDFKaren Jezabel Suarez MoralesОценок пока нет

- HPV 02 VariablePump enДокумент36 страницHPV 02 VariablePump enSorinОценок пока нет

- Physics Investigatory Project: by Tarun Singh of XII B, Manav Rachna International SchoolДокумент11 страницPhysics Investigatory Project: by Tarun Singh of XII B, Manav Rachna International Schoolraj60% (5)

- AN1646Документ7 страницAN1646Duc HuynhОценок пока нет