Академический Документы

Профессиональный Документы

Культура Документы

TP4 Atelier MCP

Загружено:

mohamedАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

TP4 Atelier MCP

Загружено:

mohamedАвторское право:

Доступные форматы

IE5 FST 2020/2021

TP4 : Conception schématique de chemin de données et unité de contrôle sous

QUARTUS II

Objectif :

L’objectif de ce Lab est de proposer une implémentation schématique de quelques

éléments constituants une architecture RISC à 8 bits sous environnement Quartus.

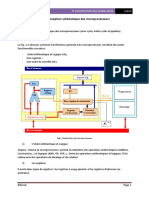

Le schéma de son chemin de données est donné par la figure suivante

Les signaux de contrôle sont générés une unité de contrôle suivant le format d’instruction à

la sortie de la mémoire d’instruction. Sachant que encodage de chaque instruction sur un

mot de 16 bits et elle s’exécute sur un seul cycle horloge de Clk

Dr Dhafer MEZGHANI Page 1

IE5 FST 2020/2021

1. Conception de l’Unité Arithmétique et Logique sous Quartus

1.1. Conception d’une UAL élémentaire sous Quartus

L’UAL élémentaire proposée obéit à la table de fonctionnement suivante suivant ALU_op

Inv C0 S_Select fonction

x x 00 A and B

x x 01 A OR B

0 0 10 A plus B

1/ Rappeler la schématique de cette UAL

1 1 10 A moins B

x x 11 e3 élémentaire (Voir TP1)

2/Implémenter ce schéma déduit sous

environnement quartus sous le nom d’un projet « UAL_ele »

1.2. Conception d’une UAL à 8 bits sous Quartus

Une UAL à 8 bits est constitué de 8 UAL élémentaire en cascade suivant le schéma suivant

Dr Dhafer MEZGHANI Page 2

IE5 FST 2020/2021

Cette UAL à 8 bits dispose de trois drapeaux indiquant l’état de la retenue finale, le résultat

zéro et le débordement. Les signaux de contrôle ALU_ctr sont générés par l’unité de contrôle

1/Implémenter ce schéma sous environnement Quartus sous le nom d’un projet

« UAL_8bits » en faisant appel au symbole UAL_ele.

2. Conception de Banc de registres sous Quartus

Ce banc de registres contient:

– Des registres à chargement parallèle

– Un mécanisme pour les charger à partir d’un port d’entrée (Décodeur+And)

– Un mécanisme pour aiguiller leur valeur à des ports de sortie (Multiplixeurs)

Dr Dhafer MEZGHANI Page 3

IE5 FST 2020/2021

2.1. Conception schématique de registres à chargement parallèle

Les registres de notre processeur RISC est formé de 8 bascules D dont le chargement dépond

de la variable C au moment du front montant de l’horloge Clk. Le schéma bloc est donné

comme suit.

1/Implémenter ce schéma sous environnement Quartus sous le nom d’un projet

« Reg_para » en faisant appel aux symboles de la bascule D et multiplixeur prédéfinis dans

l’environnement.

2.2. Conception du Banc de registres à 8 bits

1/Implémenter le schéma de la figure …. Sous environnement Quartus sous le nom de projet

« Banc_reg_8bits » en utilisant le symbole « Reg_para ».

3. Conception de la mémoire de données

On veut concevoir la schématique suivante, sous environnement Quartus, d’une mémoire de

données à 8 bits d’adresse et un bus de données à 8 bits

1/Implémenter le schéma de la figure ci-dessus Sous environnement Quartus sous le nom de

projet « memoireRAM » de la mémoire de données.

4. Conception de l’unité de Contrôle

4.1. Encodage des instructions en mémoire

Pour l’encodage des instructions, nous supposons que :

– Encodage sur un seul mot de 16 bits: chaque instruction s’exécute en un seul

cycle.

Dr Dhafer MEZGHANI Page 4

IE5 FST 2020/2021

– Le mot d’instruction est divisé en 6 champs pour le type R et 4 champs pour le

type I

– Modes d’adressage limités conformément à la philosophie RISC.

Nous voulons implémenter le jeu d’instructions suivantes :

Add $2,$3,$4

Sub $3,$3,5F

Ori $1,$2,0F

Lw $2, 10($3)

Sw $1, 10($2)

1/déterminer le format d’instruction de chaque instruction Sachant que :

Pour les instructions de type R, code opératoire est 00, fonction 00 pour add, fonction 01

pour sub

Pour les instructions de type I, code opératoire de lw est 01 et code opératoire de sw est 10

et code opératoire 11 pour ori

2/Implémenter les formats en fichier Hexadécimal (Voir TP3) sous le nom tableau3.hex

3/Concevoir une mémoire d’instruction de type ROM en utilisant le symbole utilisé dans le

TP3 en faisant appel à ce fichier héxadécimal. Enregistrer le projet sous le nom

« memoireROM ». dont le bus d’adresse est générér d’un registre à 8 bits qui charge la

nouvelle valeur de PC=PC+1 ou PC=PC+1+imm8 suivant la valeur de NPC_sel

Dr Dhafer MEZGHANI Page 5

IE5 FST 2020/2021

4.2. Conception de l’Unité de Contrôle

1/ Proposer la logique câblée de cette unité de contrôle pour implémentation des

instructions citées précédemment

2/ Proposer une schématique de cette unité sous le nom « unite_controle »

Dr Dhafer MEZGHANI Page 6

Вам также может понравиться

- Exercice 1: Les Interruptions LogiciellesДокумент2 страницыExercice 1: Les Interruptions LogiciellesMounia ChakkourОценок пока нет

- Compte-Rendu FinalДокумент10 страницCompte-Rendu FinalDhafer MezghaniОценок пока нет

- TP3: Conception Schématique Des Microprocesseurs: ObjectifДокумент6 страницTP3: Conception Schématique Des Microprocesseurs: ObjectifDor SafОценок пока нет

- Exo EnslДокумент14 страницExo EnslDhiaeddine AtiОценок пока нет

- Cours VHDL 2Документ45 страницCours VHDL 2Zine Elabidine MoslihОценок пока нет

- Chap5 Description StructurelleДокумент25 страницChap5 Description StructurelleNajlaealalawiОценок пока нет

- PDF Le Grafcet Cours Exercices Corriges - TextmarkДокумент186 страницPDF Le Grafcet Cours Exercices Corriges - Textmarkousmane kaneОценок пока нет

- TP MUX - 4vers1Документ8 страницTP MUX - 4vers1Meriem MeriemОценок пока нет

- Examen PDFДокумент3 страницыExamen PDFbounegab100% (1)

- QuartusДокумент5 страницQuartusMohamed ChaabenОценок пока нет

- Command LineДокумент199 страницCommand LineDIMI EKONGA NZELLYОценок пока нет

- Cours VHDLДокумент44 страницыCours VHDLMustapha El IdrissiОценок пока нет

- Eléments-De-Correction Eval Type CodesignДокумент4 страницыEléments-De-Correction Eval Type CodesignhurnelОценок пока нет

- Cours Microcontrôleur Microprocesseur 66 PDFДокумент28 страницCours Microcontrôleur Microprocesseur 66 PDFAbderrahim RiadОценок пока нет

- TP2Документ8 страницTP2Zouhair IguerhzifenОценок пока нет

- CC2 Ex1Документ7 страницCC2 Ex1kingfak100% (1)

- Corrigé - Devoir 1 - 19-20 - GM2Документ2 страницыCorrigé - Devoir 1 - 19-20 - GM2Elglitia MohamedОценок пока нет

- TP No 7 MicrocontroleursДокумент4 страницыTP No 7 MicrocontroleursKhawlaManaaОценок пока нет

- TP 5 Realisation Modulation FM À VaricapДокумент3 страницыTP 5 Realisation Modulation FM À VaricapYves AbrahamОценок пока нет

- Cours I2CДокумент22 страницыCours I2CMarwen SellamiОценок пока нет

- Chap8-Les RegistresДокумент6 страницChap8-Les RegistresAhmed GourineОценок пока нет

- Travaux Pratiques Electronique NumériqueДокумент10 страницTravaux Pratiques Electronique NumériqueOumaima RhayaОценок пока нет

- Examen Final CLPДокумент4 страницыExamen Final CLPtemp.kahajiОценок пока нет

- Cours HC11Документ27 страницCours HC11bjm63Оценок пока нет

- Le Microprocesseur 8086Документ22 страницыLe Microprocesseur 8086Merbai YassineОценок пока нет

- Ex CorrigéДокумент3 страницыEx CorrigéHamza Rahali100% (1)

- Analyses VH DДокумент10 страницAnalyses VH DMustapha El IdrissiОценок пока нет

- Le Langage VHDL ELKARIДокумент112 страницLe Langage VHDL ELKARIAhmed DoghmiОценок пока нет

- Intro Mémoire ProcesseurДокумент209 страницIntro Mémoire ProcesseurImane el omariОценок пока нет

- TP C PDFДокумент76 страницTP C PDFMed AmallahОценок пока нет

- Add SOUSДокумент9 страницAdd SOUSNabil KhОценок пока нет

- Circuits Programmables Chap5 EtudДокумент36 страницCircuits Programmables Chap5 EtudMohamed Dhia Eddine DrissОценок пока нет

- Projet VHDLДокумент6 страницProjet VHDLFadwa JabriОценок пока нет

- 2 Prog AssembleurДокумент5 страниц2 Prog AssembleurAnonymous Cr8uWCWxu100% (1)

- Interruptions 8086Документ26 страницInterruptions 8086Nadhira AdjОценок пока нет

- ch4 PDFДокумент20 страницch4 PDFYAMALEUОценок пока нет

- Chap II Architecture Des MicrocontrôleursДокумент8 страницChap II Architecture Des MicrocontrôleursMohamed Aziz Ben RomdhaneОценок пока нет

- Serie TD6Документ7 страницSerie TD6Sarah NourОценок пока нет

- CR 7 Test Bench Banc de TestДокумент29 страницCR 7 Test Bench Banc de TestBelkhiri MohammedОценок пока нет

- Introduction Au SystemCДокумент42 страницыIntroduction Au SystemCsupremОценок пока нет

- TD 2021Документ4 страницыTD 2021elhaoudar.nassima100% (1)

- Carte Numerique QuartusДокумент26 страницCarte Numerique QuartusAdiouma DiopОценок пока нет

- TP1Документ5 страницTP1Oumayma AmiriОценок пока нет

- Remarques Et Astuces de Programmation en AssembleurДокумент31 страницаRemarques Et Astuces de Programmation en AssembleuramaniОценок пока нет

- Compteur VHDLДокумент6 страницCompteur VHDLfarah_louzaliОценок пока нет

- Abel Jedec ProteusДокумент4 страницыAbel Jedec ProteusyassineОценок пока нет

- Cours VHDL Fpga 2Документ141 страницаCours VHDL Fpga 2minzo9479Оценок пока нет

- Cours FPGAДокумент47 страницCours FPGAHamza MhalОценок пока нет

- Chap III ExercicesДокумент1 страницаChap III ExercicesMohamed Aziz Ben RomdhaneОценок пока нет

- Fascicule TP - Systeme Embarqués - 2012 - La EEA A3Документ31 страницаFascicule TP - Systeme Embarqués - 2012 - La EEA A3Habib HAMDIОценок пока нет

- TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Документ15 страницTP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Smart ClasseОценок пока нет

- Cours - Composants Logiques Programmables Et VHDLДокумент141 страницаCours - Composants Logiques Programmables Et VHDLYoussef Elalaoui0% (1)

- Projet À Microcontrôleur PIC 16F876AДокумент29 страницProjet À Microcontrôleur PIC 16F876ABoulou Boufaid LyesОценок пока нет

- Le système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoОт EverandLe système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoОценок пока нет

- Li-Fi: Mise en réseau cohérente et à grande vitesse basée sur la lumièreОт EverandLi-Fi: Mise en réseau cohérente et à grande vitesse basée sur la lumièreОценок пока нет

- Identification Radiofréquence: Le rôle de la RFID dans les domaines émergents de l'Internet des objets et de l'Internet des nano-objetsОт EverandIdentification Radiofréquence: Le rôle de la RFID dans les domaines émergents de l'Internet des objets et de l'Internet des nano-objetsОценок пока нет

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesОт EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesОценок пока нет

- Formation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesОт EverandFormation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesОценок пока нет

- Apprendre et enseigner sur le Web: quelle ingénierie pédagogique?От EverandApprendre et enseigner sur le Web: quelle ingénierie pédagogique?Оценок пока нет

- Cycle de VieДокумент2 страницыCycle de ViemohamedОценок пока нет

- Cycle de VieДокумент2 страницыCycle de ViemohamedОценок пока нет

- Cross CopilДокумент1 страницаCross CopilmohamedОценок пока нет

- Scada HelpДокумент1 страницаScada HelpmohamedОценок пока нет

- Compilation DirectДокумент3 страницыCompilation DirectmohamedОценок пока нет

- Organ I StationДокумент2 страницыOrgan I StationmohamedОценок пока нет

- Organ I StationДокумент2 страницыOrgan I StationmohamedОценок пока нет

- HopenДокумент1 страницаHopenmohamedОценок пока нет

- MMP 1Документ1 страницаMMP 1mohamedОценок пока нет

- LiveДокумент2 страницыLivemohamedОценок пока нет

- Copie DviДокумент2 страницыCopie DvimohamedОценок пока нет

- WhynotДокумент2 страницыWhynotmohamedОценок пока нет

- ContexteДокумент2 страницыContextemohamedОценок пока нет

- GrepДокумент4 страницыGrepmohamedОценок пока нет

- SortДокумент3 страницыSortmohamedОценок пока нет

- Help MeДокумент2 страницыHelp MemohamedОценок пока нет

- Étape de Réception: Modulés en Amplitude Diodes Modulés en Fréquence Haut-ParleurДокумент6 страницÉtape de Réception: Modulés en Amplitude Diodes Modulés en Fréquence Haut-ParleurmohamedОценок пока нет

- FindДокумент4 страницыFindmohamedОценок пока нет

- Recepteur RF - 2020'Документ12 страницRecepteur RF - 2020'mohamedОценок пока нет

- SortДокумент3 страницыSortmohamedОценок пока нет

- AwakДокумент7 страницAwakmohamedОценок пока нет

- FindДокумент4 страницыFindmohamedОценок пока нет

- Étape de Réception: Modulés en Amplitude Diodes Modulés en Fréquence Haut-ParleurДокумент6 страницÉtape de Réception: Modulés en Amplitude Diodes Modulés en Fréquence Haut-ParleurmohamedОценок пока нет

- GrepДокумент4 страницыGrepmohamedОценок пока нет

- TD N2 CorrigéДокумент4 страницыTD N2 Corrigémohamed100% (1)

- Correction TD1 Programmation DSPДокумент5 страницCorrection TD1 Programmation DSPmohamedОценок пока нет

- Exercice 1.: TD Système D'émission/réception RF IE5Документ1 страницаExercice 1.: TD Système D'émission/réception RF IE5mohamedОценок пока нет

- IE5 DistДокумент27 страницIE5 DistWejdène GuedriОценок пока нет

- TD 1 Ennoncé IE5 PDFДокумент4 страницыTD 1 Ennoncé IE5 PDFmohamedОценок пока нет

- TP3 Atelier MCPДокумент8 страницTP3 Atelier MCPmohamedОценок пока нет

- Tp8 Partie 1Документ4 страницыTp8 Partie 1maroumedОценок пока нет

- Rhel Sag FR PDFДокумент364 страницыRhel Sag FR PDFSid Ahmed KhobzaouiОценок пока нет

- Chapitre 1Документ10 страницChapitre 1Sami BachaОценок пока нет

- Logiciel de Gestion AdministrativeДокумент3 страницыLogiciel de Gestion AdministrativeMoez FetniОценок пока нет

- TP1 5Документ15 страницTP1 5Salsec ZombreОценок пока нет

- Examen S1 DUT1 MaintenanceДокумент3 страницыExamen S1 DUT1 Maintenancequit_youОценок пока нет

- Acces Au Reseau Etendu CCNA 4 PDFДокумент275 страницAcces Au Reseau Etendu CCNA 4 PDFJPatmos NembalembaОценок пока нет

- Comment Installer Ubuntu 10Документ6 страницComment Installer Ubuntu 10Houssam BahriОценок пока нет

- Créer Un Réseau WiFi Ad HocДокумент5 страницCréer Un Réseau WiFi Ad HocbachirmoОценок пока нет

- CCNA 1 Chapitre 11 v5 2016Документ8 страницCCNA 1 Chapitre 11 v5 2016isimgОценок пока нет

- LinuxMagazine HS 2011 02Документ72 страницыLinuxMagazine HS 2011 02Jacques DeyrieuxОценок пока нет

- Introduction Aux Réseaux - IntroductionДокумент1 страницаIntroduction Aux Réseaux - IntroductionSerigneFallou DIOUFОценок пока нет

- Comment Configurer Le Pilote VAS5054A PassThru Pour XentryДокумент3 страницыComment Configurer Le Pilote VAS5054A PassThru Pour XentryMline-garage DiagnosticОценок пока нет

- Exposé de SI2Документ15 страницExposé de SI2gaspard junior BIWONO NGADENAОценок пока нет

- TD1 ++Документ2 страницыTD1 ++kamedjongernestОценок пока нет

- Sockets Illustration Avec JAVA - Applications RépartiesДокумент88 страницSockets Illustration Avec JAVA - Applications Répartiesroimarco54Оценок пока нет

- Cours VLAN Et VTPДокумент23 страницыCours VLAN Et VTPديب الغابةОценок пока нет

- Logiciel SAS 9.2 Windows Vol1 André WielkiДокумент215 страницLogiciel SAS 9.2 Windows Vol1 André WielkixxformatОценок пока нет

- Siemens Industry Online Support - Automation Service, Automation Support, Simatic Service, Simatic Support, Technical Support, Technical Consulting2Документ6 страницSiemens Industry Online Support - Automation Service, Automation Support, Simatic Service, Simatic Support, Technical Support, Technical Consulting2Mohammed BenbrahimОценок пока нет

- Resume PICДокумент2 страницыResume PICAyoub AbdellaouiОценок пока нет

- Examen Final Du Module Informatique Industrielle: Question - 1 (Документ7 страницExamen Final Du Module Informatique Industrielle: Question - 1 (oassarikhiОценок пока нет

- Upload - Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Документ3 страницыUpload - Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Hayet BechedliОценок пока нет

- AD Plan - StrategieДокумент10 страницAD Plan - StrategieMamadou ThioyeОценок пока нет

- CCNASv2 Chapitre 6-Securisation Du Reseau LocalДокумент66 страницCCNASv2 Chapitre 6-Securisation Du Reseau LocalzamfiralinОценок пока нет

- Facteurs D'encombrementДокумент2 страницыFacteurs D'encombrementRana GhribiОценок пока нет

- Guide ScriptДокумент11 страницGuide ScriptBenjamin ZoreОценок пока нет

- Chap1 2Документ73 страницыChap1 2youssef100% (1)

- Serviceclouds (OpenStack)Документ33 страницыServiceclouds (OpenStack)Félix Thiop FAYEОценок пока нет

- TP4 Mémoire ÉnoncéДокумент2 страницыTP4 Mémoire ÉnoncéYIDHIR HAMMASОценок пока нет