Академический Документы

Профессиональный Документы

Культура Документы

Inf3500 201803 Intra3 Solution

Загружено:

Wessim Ben SaadОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Inf3500 201803 Intra3 Solution

Загружено:

Wessim Ben SaadАвторское право:

Доступные форматы

Nom : _______________________________________ Matricule : ____________________________

INF3500 : Conception et réalisation de systèmes numériques

Examen intra #3 – jeudi 29 novembre décembre 2018

Durée: 1 heure. Documentation: Une feuille recto verso 8.5”×11” ou A4 permise.

Pondération: 0% (formatif). Calculatrice: Programmable permise.

Directives particulières:

Ordinateurs interdits. Appareils mobiles interdits.

Répondre à toutes les questions, la valeur de chaque question est indiquée.

Répondre sur le questionnaire.

Ne posez pas de questions. En cas de doute sur le sens d’une question, énoncez clairement toute

supposition que vous faites.

Question 1. (1 point)

Réponses brèves.

a. Expliquez dans quels cas la division et le calcul du modulo sont supportés par les outils de synthèse

présentement sur le marché, et pourquoi ces opérations ne le sont pas dans les autres cas.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

b. Qu’est-ce qui est produit par un outil de synthèse à partir d’un code VHDL valide?

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

c. Dans quelles conditions une boucle en VHDL est-elle synthétisable ? Expliquez pourquoi.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

d. Donnez deux métriques pour comparer différentes solutions de placement d’un circuit numérique sur

un FPGA.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

Polytechnique Montréal page 1/6 Département de génie informatique et génie logiciel

INF3500 – contrôle périodique #3 – 29 novembre 2018

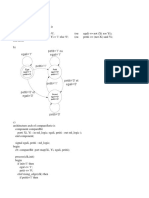

Question 2. (3 points)

Considérez le diagramme suivant du processeur PolyRISC.

Op_UAL:

0: F <= A Bloc des registres UAL

1: F <= B

2: F <= A + B

3: F <= A – B Z

donnéeBR A A

4: F <= A ET B N

5: F <= A OU B

6: F <= NON A F

choixCharge

7: F <= A OUX B

chargeBR Mémoire des données

B B

choixA

choixB

Sélection des muxes:

op_UAL adresse M[adresse]

0: signal du haut

1: signal du bas

choixDonnee_BR

donnee_MD

`

choixB_UAL

charge_MD

valeur

a. (1 point) Donnez la valeur du mot de contrôle pour effectuer les opérations suivantes en complétant le

tableau.

choixB_UAL

choixCharge

charge_MD

choixDon-

chargeBR

op_UAL

nee_BR

choixA

choixB

valeur

opération

R2 := R7 OUX R4

R6 := NON(R6)

M[50 + R5] := R1

R3 := M[100]

b. (2 points) Le bloc des registres a un délai tD de 6.5 ns et un temps de préparation tsu de 1 ns. L’UAL a

un délai de 10 ns. En mode écriture, la mémoire des données a un délai tD de 7.5 ns et un temps de prépa-

ration tsu de 3 ns à cause du décodage d’adresses. En mode lecture, la mémoire des données a un délai de

7.5 ns. Les multiplexeurs ont un délai de 2 ns. On estime que chaque fil d’interconnexion ajoute un délai

de 0.5 ns. On suppose que les signaux de contrôle sont sans délais. Il n’y a pas de déphasage d’horloge.

Identifiez le chemin critique et calculez la fréquence maximale d’horloge.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

___________________________________________________________(Utilisez le verso si nécessaire)

Polytechnique Montréal page 2/6 Département de génie informatique et génie logiciel

INF3500 – contrôle périodique #3 – 29 novembre 2018

Question 3. (3 points)

Considérez le bloc des registres choixA

suivant, et supposez que les ports

donneeBR, A et B ont 16 bits de donnéeBR D Q

large. chargeBR

R0

A

charge

Estimez combien de ressources

seraient nécessaires pour implé- D Q choixB

menter ce bloc des registres sur 2:4

R1

un FPGA de la famille Virtex-7 0

charge

choixCharge

1

que vous avez utilisé au labora- 2 B

3

toire. Énoncez clairement toutes

vos suppositions et justifiez D Q

complètement votre réponse. R2

Donnez votre réponse en termes charge

de LUT, de bascules, de tranches

DSP48 et de bits de mémoire

Block RAM. D Q

Montrez tous vos calculs et justi- R3

charge

fiez complètement votre réponse.

Utilisez le verso si nécessaire.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

Polytechnique Montréal page 3/6 Département de génie informatique et génie logiciel

INF3500 – contrôle périodique #3 – 29 novembre 2018

Question 4. (3 points)

Considérez le diagramme suivant montrant un circuit implémenté sur un FPGA simplifié. Les entrées du

circuit sont les signaux A, B, C, D et E. Il y a deux sorties S et T. Le FPGA est composé de tranches ayant

chacune une table de correspondance (LUT) et une bascule pouvant être utilisée ou non, et de blocs

d’entrée/sortie (IOB) dans lesquels les bascules sont toujours utilisées.

Pour ce FPGA, les LUT ont un délai de 0.3 ns. Les bascules ont un délai de 0.4 ns, un temps de prépara-

tion tsu de 0.2 ns, et un temps de maintien th de 0.1 ns. Chaque fil d’interconnexion ajoute un délai de 0.25

ns pour chaque rangée et chaque colonne de distance. Bien que des lignes diagonales soient tracées sur le

diagramme, tous les signaux sont routés en lignes horizontales et/ou verticales.

Colonne 0 Colonne 1 Colonne 2 Colonne 3

Rangée 0

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

A Bloc entrée/ conversion conversion conversion conversion Bloc entrée/ S

sortie (LUT) (LUT) (LUT) (LUT) sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 1

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

B Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 2

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

C Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 3

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

D Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 4

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

E Bloc entrée/ conversion conversion conversion conversion Bloc entrée/ T

sortie (LUT) (LUT) (LUT) (LUT) sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

a. (1 point) Identifiez le chemin critique du circuit et donnez la fréquence maximale d’horloge.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

b. (2 points) On veut maximiser le débit de ce circuit par la technique du pipeline. Montrez clairement sur

le diagramme quelles bascules utiliser. Quel est le débit maximal qui peut être atteint par ce circuit?

Énoncez clairement toutes vos suppositions et justifiez complètement votre réponse.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

____________________________________________________________________________________

Polytechnique Montréal page 4/6 Département de génie informatique et génie logiciel

INF3500 – contrôle périodique #3 – 29 novembre 2018

Solutions

Q1.

a. Réponse. La division et le modulo sont supportés quand le deuxième argument est une puissance de

deux. Le résultat s’obtient alors par un décalage ou une sélection de bits, respectivement. La division

générale et le modulo général ne sont pas présentement synthétisables parce qu’il n’y a pas de bloc dédié

à cette opération dans la plupart des technologies, dont les FPGA. Ces opérations peuvent être réalisées de

différentes façons, par exemple par la multiplication par la réciproque du diviseur et par des circuits itéra-

tifs. Dans les deux cas, il y a beaucoup de choix de design à faire, incluant la complexité matérielle et la

latence du circuit résultant. Les concepteurs de synthétiseurs préfèrent laisser ces choix à celles et ceux

qui écrivent du code VHDL.

b. Le produit de la synthèse est une liste de composantes de base et des interconnexions entre elles qui

correspond à l’interprétation matérielle du code VHDL. Dans leur plus simple expression, les compo-

santes peuvent être des portes logiques. Les composantes peuvent correspondre à des blocs plus com-

plexes disponibles sur la technologie visée. Par exemple, pour un FPGA, une composante peut être un

multiplieur ou un bloc de mémoire RAM.

c. Pour être synthétisable, une boucle logicielle doit pouvoir être déroulée complètement, et à chaque

itération correspond un bloc matériel distinct. Cela correspond à échanger du temps pour de l’espace. Il

faut donc que les bornes de la boucle soient connues de façon statique au moment de la synthèse, par

exemple en étant des constantes ou des valeurs spécifiées par des énoncés generic.

d. Longueur totale des interconnexions, chemin le plus long, congestion des interconnexions.

Q2.

a.

ChoixB_UAL

choixCharge

Charge_MD

choixDon-

chargeBR

Op_UAL

nee_BR

choixA

choixB

valeur

opération

R2 := R7 OUX R4 1 2 7 4 - 0 7 0 0

R6 := NON(R6) 1 6 6 - - - 6 0 0

M[50 + R5] := R1 0 - 5 1 50 1 2 1 -

R3 := M[100] 1 3 - - 100 1 1 0 1

b. Quelques chemins critiques possibles sont :

Instruction R2 := R7 oux R4 :

bloc des registres, mux, UAL, mux, bloc des registres :

6.5 + 2 + 10 + 2 + 1 + 4 × 0.5 = 23.5 ns

Instruction M[50 + R5] := R1 :

bloc des registres, UAL, mémoire des données (port ‘adresse’, mémoire en mode écriture) :

6.5 + 10 + 3 + 2 × 0.5 = 20.5 ns

Instruction R3 := M[R1 + R4] :

bloc des registres, mux, UAL, mémoire des données (port ‘adresse’, mémoire en mode lecture), mux, bloc

des registres 6.5 + 2 + 10 + 7.5 + 2 + 1 + 5 × 0.5 = 31.5 ns

Donc fmax = 1/31.5 ns = 31.7 MHz

Polytechnique Montréal page 5/6 Département de génie informatique et génie logiciel

INF3500 – contrôle périodique #3 – 29 novembre 2018

Q3

Il faut 4 × 16 = 64 bascules.

Les deux multiplexeurs de sortie ont chacun 6 entrées : un bit par registre et deux bits pour le choix de la

sortie. Donc il faut 1 LUT par bit pour chacun des multiplexeurs, donc 16 LUT chacun, donc 32 LUT.

Il faut 4 LUT pour les 4 portes ET.

Le décodeur a deux entrées et 4 sorties, il faut 4 LUT.

Total BR : 64 bascules, 40 LUT environ.

Q4.

a. Le chemin critique va de l’entrée B, à la LUTR3C0, à la LUTR0C1, à la LUT R0C3, à la sortie S.

Le délai total est td + 3 × tLUT + 10 × tfils = 0.4 + 3 × 0.3 + 10 × 0.25 = 3.8 ns.

La fréquence maximale d’horloge est 1/(3.8 + tsu) = 1 / 4 ns = 250 MHz.

b. Il faudrait tout d’abord insérer des registres de pipeline dans le chemin critique, bascules R3C0, R0C1

et R0C3. Ensuite il faudrait balancer les autres chemins. En y allant colonne par colonne, il faut utiliser

toutes les bascules sur des chemins dans la colonne 0. Pour la colonne 1, on doit utiliser la bascule R4C1.

Il faut aussi insérer une bascule dans le chemin du milieu, par exemple avec la LUT et la bascule R3C1.

La LUT R3C1 ferait la fonction identité. On ajouterait aussi une LUT identité et une bascule à R4C3 sur

le chemin du bas.

Le chemin critique serait alors de R3C1 à R0C3 : td + 5 × tfil + tlut + tsu = 0.4 + 5 × 0.25 + 0.3 + 0.2 =

2.15 ns, et la fréquence maximale d’horloge correspondante serait 465 MHz.

Colonne 0 Colonne 1 Colonne 2 Colonne 3

Rangée 0

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

A Bloc entrée/ conversion conversion conversion conversion Bloc entrée/ S

sortie (LUT) (LUT) (LUT) (LUT) sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 1

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

B Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 2

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

C Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 3

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

D Bloc entrée/

sortie

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

conversion

(LUT)

Bloc entrée/

sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Rangée 4

D Q Table de Table de Table de Table de D Q

D Q D Q D Q D Q

E Bloc entrée/ conversion conversion conversion conversion Bloc entrée/ T

sortie (LUT) (LUT) (LUT) (LUT) sortie

(IOB) CLK (IOB) CLK

CLK CLK CLK CLK

Polytechnique Montréal page 6/6 Département de génie informatique et génie logiciel

Вам также может понравиться

- Examen Correction L2 Base de DonneesДокумент7 страницExamen Correction L2 Base de DonneesR-win89% (71)

- Les NTIC Et Les Impacts Sur Les Missions Des Experts ComptablesДокумент12 страницLes NTIC Et Les Impacts Sur Les Missions Des Experts ComptablesBonnefoyОценок пока нет

- Gestion Du Temps PDFДокумент57 страницGestion Du Temps PDFmounir100% (1)

- Chapitre 1 Simplexe, Dualité Et Analyse de SensibilitéДокумент61 страницаChapitre 1 Simplexe, Dualité Et Analyse de SensibilitéBalkis triki100% (1)

- Optimisation LinéaireДокумент11 страницOptimisation Linéairemehdi kchОценок пока нет

- Vols D'aveugle Autour D'une LibrerieДокумент14 страницVols D'aveugle Autour D'une LibrerieMarcela Rivera HutinelОценок пока нет

- La Protection SocialeДокумент2 страницыLa Protection Socialesoso sosoОценок пока нет

- Cours D'algoДокумент179 страницCours D'algopersieОценок пока нет

- Ordre Rosicrucien AMORC Vs - Imperator Gary L StewartДокумент25 страницOrdre Rosicrucien AMORC Vs - Imperator Gary L Stewartkaldeter50% (2)

- Cahier #38: Jean RayДокумент5 страницCahier #38: Jean RayHerne EditionsОценок пока нет

- La LGDДокумент29 страницLa LGDMàlika IzegОценок пока нет

- Corrosion TecsupДокумент34 страницыCorrosion TecsupHebert Vizconde PoemapeОценок пока нет

- dc1 2017Документ4 страницыdc1 2017tueveenmoutlonОценок пока нет

- 1-Simple Linear RegressionДокумент6 страниц1-Simple Linear RegressionAlex LionelОценок пока нет

- Chapitre 02Документ17 страницChapitre 02Imane KennishОценок пока нет

- 3Ms CombiДокумент18 страниц3Ms CombiMYSTÉRESОценок пока нет

- ch4 BDДокумент15 страницch4 BDSa MuelОценок пока нет

- TP3 Calibrer Evaluer Comparer CorrecДокумент9 страницTP3 Calibrer Evaluer Comparer CorrecGurzil MlhОценок пока нет

- IN311 2021 2022 BDD Partiel V2 CorrigéДокумент9 страницIN311 2021 2022 BDD Partiel V2 CorrigéNotnowОценок пока нет

- MiniProjet BanqueДокумент3 страницыMiniProjet Banqueibrahimoulmouden2005Оценок пока нет

- Maths 2005Документ7 страницMaths 2005Issa KABOREОценок пока нет

- Algorithme de Simplexe: Méthode TabulaireДокумент42 страницыAlgorithme de Simplexe: Méthode TabulaireOussama oussamaОценок пока нет

- MATHS 6ème Séquence 2Документ2 страницыMATHS 6ème Séquence 2atsangueyayaОценок пока нет

- Examen Emd 20232024Документ2 страницыExamen Emd 20232024abderrahmani faresОценок пока нет

- TDR 602Документ11 страницTDR 602SAFOОценок пока нет

- ch4 BDДокумент15 страницch4 BDKhadidiatou SARRОценок пока нет

- Trans POOДокумент98 страницTrans POOMohsine BenallalОценок пока нет

- Fiabilité LoiДокумент2 страницыFiabilité LoiBilelОценок пока нет

- MsExcel ACTIVITESДокумент3 страницыMsExcel ACTIVITESSaid Sunghour SunghourОценок пока нет

- Correction Creation MatricesДокумент8 страницCorrection Creation MatricesSaif EddineОценок пока нет

- Partiel In311 2021-2022Документ8 страницPartiel In311 2021-2022NotnowОценок пока нет

- Bac Blanc ES SpecialiteДокумент5 страницBac Blanc ES SpecialitealiОценок пока нет

- Révisions - Calcul Numérique - Fiche de Cours: 1. Règles Des Signes 5. Nombres PremiersДокумент2 страницыRévisions - Calcul Numérique - Fiche de Cours: 1. Règles Des Signes 5. Nombres PremiersMay'Axel RomaricОценок пока нет

- Correct TD1Документ3 страницыCorrect TD1ismailОценок пока нет

- Sujet DS DDS 2021Документ4 страницыSujet DS DDS 2021Antoine ThorОценок пока нет

- 001aquestionnaire Sur Le Dessin Technique RappelДокумент5 страниц001aquestionnaire Sur Le Dessin Technique RappelyousefОценок пока нет

- Test Des POSTULANTSДокумент2 страницыTest Des POSTULANTSPierre Dugens MathiasОценок пока нет

- DC 1 TH - 3 SI 2 Algo&ProgДокумент3 страницыDC 1 TH - 3 SI 2 Algo&ProgPROF PROFОценок пока нет

- Proposition Des Correction TD de Méthodes de Collecte Des Données AE L1 202Документ5 страницProposition Des Correction TD de Méthodes de Collecte Des Données AE L1 202Adama BouareОценок пока нет

- Presentation TP1Документ21 страницаPresentation TP1Emmanuel PuatiОценок пока нет

- Outil Aide DecisionДокумент3 страницыOutil Aide DecisionAbdellah El BarkanyОценок пока нет

- TD 4 ANOVAДокумент8 страницTD 4 ANOVAMagnifico FangaWoroОценок пока нет

- TP Cara Diode PrimoДокумент3 страницыTP Cara Diode PrimosowОценок пока нет

- Chapitre 2: Algorithmes Du Simplexe: Abdelkrim E Professeur Habilité en Mathématique AppliquéeДокумент37 страницChapitre 2: Algorithmes Du Simplexe: Abdelkrim E Professeur Habilité en Mathématique AppliquéeAbdel El MouatasimОценок пока нет

- Centres Etrangers 1 Spe 11 06 2021 DV FHДокумент6 страницCentres Etrangers 1 Spe 11 06 2021 DV FHJordanОценок пока нет

- Mini Projet Recherche Operationnelle Programmation Dans CДокумент12 страницMini Projet Recherche Operationnelle Programmation Dans CBitote ADОценок пока нет

- Chapitre 1Документ14 страницChapitre 1Dkfk HdjdОценок пока нет

- Serie n1 AlgorithmeДокумент2 страницыSerie n1 AlgorithmeAbdoulaye DialloОценок пока нет

- CoursДокумент97 страницCoursStève Loris NambeyeОценок пока нет

- ConventionAlgorithmiqueAS2022 2023Документ8 страницConventionAlgorithmiqueAS2022 2023hiba hitanaОценок пока нет

- TP AutomatiqueДокумент63 страницыTP AutomatiqueNabil BounouОценок пока нет

- Sujet Bac Spe Maths 2021 Polynesie Specialite MathsДокумент9 страницSujet Bac Spe Maths 2021 Polynesie Specialite MathsBELLE GABRIELОценок пока нет

- Actions Méca - TD 1à 4 - 2021 - ÉlèveДокумент6 страницActions Méca - TD 1à 4 - 2021 - Élèveabou imranОценок пока нет

- ACM EncoursДокумент17 страницACM EncoursHamza HbdzОценок пока нет

- Mini Projet Recherche Operationnelle Programmation Dans CДокумент11 страницMini Projet Recherche Operationnelle Programmation Dans CBitote ADОценок пока нет

- Métropole 9 juin 2021Документ2 страницыMétropole 9 juin 2021teixido.anna66aragoОценок пока нет

- Quiz MIAS 2018Документ2 страницыQuiz MIAS 2018choukriОценок пока нет

- Examen 2019Документ1 страницаExamen 2019Mohammed El khayatiОценок пока нет

- DC 2 TH - 2 TiДокумент2 страницыDC 2 TH - 2 TiPROF PROFОценок пока нет

- TP4 Méthodes DirectesДокумент4 страницыTP4 Méthodes DirectesyoussefОценок пока нет

- TP2 BdaДокумент3 страницыTP2 BdaMariem SelmiОценок пока нет

- Algo TPДокумент2 страницыAlgo TPhakimaОценок пока нет

- TD Eco104cДокумент5 страницTD Eco104cCarmel BABAОценок пока нет

- Test MatemathiquesДокумент28 страницTest MatemathiquesPaul Giovanny MaОценок пока нет

- Faco 8Документ24 страницыFaco 8NBanan OUATTARAОценок пока нет

- Inf3500 201501 Intra1 - SolutionДокумент6 страницInf3500 201501 Intra1 - SolutionWessim Ben SaadОценок пока нет

- Inf3500-201102 Intra SolutionДокумент8 страницInf3500-201102 Intra SolutionWessim Ben SaadОценок пока нет

- INF3500 202003 Intra2 SolutionДокумент7 страницINF3500 202003 Intra2 SolutionWessim Ben SaadОценок пока нет

- Inf3500-201002 Intra SolutionДокумент11 страницInf3500-201002 Intra SolutionWessim Ben SaadОценок пока нет

- Inf3500-201002 Intra EnonceДокумент10 страницInf3500-201002 Intra EnonceWessim Ben SaadОценок пока нет

- Inf3500-200703 Intra SolutionДокумент6 страницInf3500-200703 Intra SolutionWessim Ben SaadОценок пока нет

- Inf3500-200801 Intra SolutionДокумент3 страницыInf3500-200801 Intra SolutionWessim Ben SaadОценок пока нет

- Inf3500-200801 Final EnonceДокумент4 страницыInf3500-200801 Final EnonceWessim Ben SaadОценок пока нет

- Inf3500 200702 Intra SolutionДокумент5 страницInf3500 200702 Intra SolutionSlim SghirОценок пока нет

- Inf3500-200703 Final SolutionДокумент9 страницInf3500-200703 Final SolutionWessim Ben SaadОценок пока нет

- Inf3500-200702 Final SolutionДокумент12 страницInf3500-200702 Final SolutionWessim Ben SaadОценок пока нет

- DS 6 SupДокумент2 страницыDS 6 SupSara MaroucheОценок пока нет

- Advancing Women's Digital FinancialДокумент69 страницAdvancing Women's Digital FinancialMariem CherifОценок пока нет

- D Omraam Mikhaël Aïvanhov - PDFДокумент1 страницаD Omraam Mikhaël Aïvanhov - PDFadonis kria100% (2)

- Miele G 4991 ScviДокумент96 страницMiele G 4991 ScviAmine MedОценок пока нет

- Asservissement de Vitesse D'une Charge Entrainée Par Un Moteur À Courant Continu, À Excitation Séparée ConstanteДокумент24 страницыAsservissement de Vitesse D'une Charge Entrainée Par Un Moteur À Courant Continu, À Excitation Séparée ConstanteAlfredho ShactarОценок пока нет

- Unité 4, Nouveau Taxi 1Документ3 страницыUnité 4, Nouveau Taxi 1corell90100% (1)

- Fiche Projet AftoutДокумент13 страницFiche Projet AftoutcissmarocОценок пока нет

- Ce2 Evaluation PronomДокумент2 страницыCe2 Evaluation PronomlawdepoliОценок пока нет

- Traçage Des Données Mobiles Dans La Lutte Contre Le Covid-19 (Note Parlementaire)Документ43 страницыTraçage Des Données Mobiles Dans La Lutte Contre Le Covid-19 (Note Parlementaire)l'Opinion100% (1)

- PS42Документ2 страницыPS42Franco GalvánОценок пока нет

- AgitationДокумент5 страницAgitationMahefa Serge RakotozafyОценок пока нет

- Franchir Une Intersection 1.2Документ22 страницыFranchir Une Intersection 1.2ArbnorОценок пока нет

- Sangalkam - SVT - 5ème - 2022Документ2 страницыSangalkam - SVT - 5ème - 2022Kiiller Kiler0% (1)

- 10 Cheville Et TarseДокумент52 страницы10 Cheville Et TarseefqsdfqsОценок пока нет

- CMAP Health Economics Outline Revised July 2020 1Документ26 страницCMAP Health Economics Outline Revised July 2020 1nihad jessica AGOLIGANОценок пока нет

- Taguelmint Ikram (Développement D'une Application...Документ64 страницыTaguelmint Ikram (Développement D'une Application...Fkaier AlaeddineОценок пока нет

- L Histoire Des VoleursДокумент5 страницL Histoire Des VoleursMustapha Ben MansourОценок пока нет

- Preconisation TechniqueДокумент3 страницыPreconisation TechniquetéléОценок пока нет

- Résumé Philosophie de SpinozaДокумент20 страницRésumé Philosophie de SpinozaBerenice Vargas BravoОценок пока нет

- 4 Limites Continuité.1Документ2 страницы4 Limites Continuité.1Mohamed Hedi GhomrianiОценок пока нет

- 2.cor 1fДокумент8 страниц2.cor 1fbulgo abelОценок пока нет