Академический Документы

Профессиональный Документы

Культура Документы

Cert 02 Sol

Загружено:

Susana RebellónОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Cert 02 Sol

Загружено:

Susana RebellónАвторское право:

Доступные форматы

ELO311 Estructura de Computadores Segundo Semestre 2008.

1. Para el procesador Monociclo visto en clases:

Sin efectuar modificaciones al camino de datos, ¿pueden efectuarse las operaciones, descritas en

RTL:

a) De tipo Load Word: R[rd] = Mem[ R[rs]+R[rt] ]; PC= PC + 4; 10 puntos

b) De tipo Store Word, descrita en RTL: Mem[ R[rs]+R[rt] ] = R[rd]; PC = PC + 4; 20 puntos

Justifique su respuesta, indicando las señales de control que las implementan.

Efectuando modificaciones al camino de datos, ¿pueden efectuarse las operaciones, descritas en

RTL?

c) De almacenamiento de dirección de instrucción siguiente: R[rs] = PC+4; PC = PC+4;

20 puntos

d) Mem[ R[rs]+R[rt] ] = 0; PC = PC + 4; 10 puntos

Justifique su respuesta, agregando las señales de control que sean necesarias, las modificaciones

al camino de datos, y las señales de control que las implementan.

Solución.

a) Puede efectuarse, en forma similar a la instrucción Load Word, pero direccionando la memoria

de datos con la suma de los contenidos de los registros indexados por rt y rs.

ADD: R[rd] = Mem[ R[rs]+R[rt] ]; PC = PC + 4

nPC_sel = “+4”, WEPC =1, Unidad Instrucción.

RegDst = "rd", Unidad Registros. Lectura.

AluSrc = "busB", AluCtr = “add”, ExtOp=∅, Unidad Operaciones.

MemWr=0, MemRd=1, Unidad Memoria Datos.

Memtoreg="mem", RegWr=1. Unidad Registros. Escritura.

b) La instrucción requiere la lectura simultánea de tres registros, lo cual no puede efectuarse, ya

que no puede leerse R[rd].

Lo que está disponible en el bus de datos de entrada de la memoria es R[rt], y no R[rd].

Lo que si puede efectuarse, sin modificaciones al hardware, es:

Mem[ R[rs]+R[rt] ] = R[rt]; PC = PC + 4;

c) Se requiere modificar las entradas del arreglo de registros. Es preciso colocar un mux,

controlado por la nueva señal de control RegBusW, que permite ingresar la señala (PC+4) en el bus

de escritura del arreglo de registros.

Además debe agregarse una entrada en el mux, con el campo rs de la instrucción, que selecciona

el registro destino, donde se escribirá un nuevo valor (el seleccionado por RegBusW).

R[rs] = PC+4; PC = PC+4;

nPC_sel = “+4”, WEPC =1, Unidad Instrucción.

RegDst = "rs", Unidad Registros. Lectura.

AluSrc = "busB", AluCtr = “add”, ExtOp=∅, Unidad Operaciones.

MemWr=0, MemRd=∅, Unidad Memoria Datos.

RegBusW=”PC+4”, Memtoreg=∅, RegWr=1. Unidad Registros. Escritura.

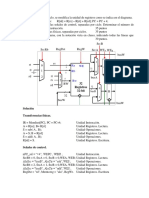

El siguiente diagrama muestra las modificaciones al camino de datos:

RegBusW RegDst RegWr

rs Ra WE

5 32

Rb

5

1 busA

rt 5

2 Rw

PC+4 0 RW

32

1 rd 32 Registros

32-bit busB

32

0

busW

d) Es preciso agregar un mux, para llevar al bus de entrada de datos de la memoria el contenido

del busB o una señal formada por puros ceros. El mux queda controlado por la nueva señal: CtrDin.

MemWr MemRd MemtoReg

CtrDin

AddrD Dout busW

busB Memoria 1

0 Datos

Din

Cero

1

Mem[ R[rs]+R[rt] ] = 0; PC = PC + 4;

nPC_sel = “+4”, WEPC =1, Unidad Instrucción.

RegDst = ∅, Unidad Registros. Lectura.

AluSrc = "busB", ExtOp = “∅”, AluCtr = “add”, Unidad Operaciones.

CtrDin=”Cero”, MemWr=1, MemRd=0, Unidad Memoria Datos.

Memtoreg=∅, RegWr=0. Unidad Registros. Escritura

2. Para el procesador Monociclo visto en clases, efectuar las modificaciones necesarias al hardware

para que se pueda ejecutar la siguiente instrucción: Add3 $t0, $t1, $t2, $t3

Transferencia Lógica: add3: R[rd] = R[rs] + R[rt] +R[shamt]; PC =PC +4

a) Indicar las modificaciones a las unidades y señales de control que se agregan. 20 puntos

b) Transferencias Físicas separadas por unidad. 20 puntos.

Solución.

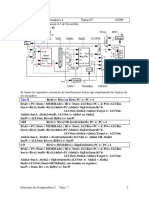

Para obtener tres salidas del arreglo de registros es necesario modificar dicha unidad de tal manera de tener

una entrada Rc (en la cual se ingresa shamt) y una salida adicional que entregue R[rc]. Ver figura 1.

Ra

RegWr R0 Rb

Rc

Decodi- 0

ficador 1

1

5 a 32

R1 BusA

RW 31

BusB

31

BusW

BusC

R31

Figura 1

Adicionalmente se hace necesario realizar la suma de R[rs] + R[rt] +R[shamt]. Ya se encuentra

implementada la suma de R[rs] + R[rt], pero la ALU no es de 3 entradas por lo que se tiene que agregar

un nuevo sumador para lograr: R[rs] + R[rt] +R[shamt]. Además se agrega un multiplexor para mantener

las operaciones anteriores. Ver Figura 2

ExtOp Equal AluSrc AluCtr_1 AluCtr_2 Aluout_Ctr

BusA

Igual

AluOut

AluOut_1

BusB

AluOut_2

Extensor Op3

2

BusC

Inm16

busB

Figura 2

Transferencias físicas de datos.

add3: R[rd] = R[rs] + R[rt] +R[shamt]; PC =PC +4

AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Unidad Instrucción.

Ra=rs, Rb=rt, Rc= shamt, RW=rd, busA=R[Ra], busB=R[Rb], busC=R[Rc), Unidad Registros. Lectura.

AluOut_1=add(busA, busB), AluOut_2 = add(AluOut_1, busC),Alu_Out = AluOut_2,

Unidad Operaciones.

busW=AluOut, R[RW]=busW. Unidad Registros. Escritura.

Valores de las señales de control para activar las transferencias lógicas. (esto no se pedía responder)

nPC_sel = “+4”, WEPC =1, Unidad Instrucción.

RegDst = "rd", Unidad Registros. Lectura.

AluSrc = "busB", AluCtr_1 = “add”, AluCtr_2 = “add”, ExtOp=∅, Aluout_ctr= 1, Unidad Operaciones.

MemWr=0, MemRd=∅, Unidad Memoria Datos.

Memtoreg="alu", RegWr=1. Unidad Registros. Escritura.

Вам также может понравиться

- Elo312 0208 Lab06Документ6 страницElo312 0208 Lab06Susana RebellónОценок пока нет

- Elo312 0208 Lab02Документ7 страницElo312 0208 Lab02Susana RebellónОценок пока нет

- Elo312 0208 Lab02Документ7 страницElo312 0208 Lab02Susana RebellónОценок пока нет

- QuickStart MSP430Документ9 страницQuickStart MSP430b4suraОценок пока нет

- Quizz 03 SolДокумент2 страницыQuizz 03 SolSusana RebellónОценок пока нет

- Elo312 0208 q2pДокумент1 страницаElo312 0208 q2pSusana RebellónОценок пока нет

- Tarea 03 SolДокумент18 страницTarea 03 SolSusana RebellónОценок пока нет

- Tarea 02 SolДокумент14 страницTarea 02 SolSusana RebellónОценок пока нет

- Elo312 0208 q1pДокумент1 страницаElo312 0208 q1pSusana RebellónОценок пока нет

- Tarea 04Документ2 страницыTarea 04Susana RebellónОценок пока нет

- Tarea 07Документ2 страницыTarea 07Susana RebellónОценок пока нет

- Tarea 06Документ1 страницаTarea 06Susana RebellónОценок пока нет

- Tarea 05Документ1 страницаTarea 05Susana RebellónОценок пока нет

- ENSAMBLADORДокумент6 страницENSAMBLADORJose Javier Atilano VargasОценок пока нет

- Tarea 03 SolДокумент18 страницTarea 03 SolSusana RebellónОценок пока нет

- Quizz 02 SolДокумент1 страницаQuizz 02 SolSusana RebellónОценок пока нет

- Quizz 03 SolДокумент2 страницыQuizz 03 SolSusana RebellónОценок пока нет

- Elo312 0208 q2pДокумент1 страницаElo312 0208 q2pSusana RebellónОценок пока нет

- Quizz 01 SolДокумент2 страницыQuizz 01 SolSusana RebellónОценок пока нет

- 1426541501540-Guía 5 Principiantes IДокумент1 страница1426541501540-Guía 5 Principiantes ISusana RebellónОценок пока нет

- Cert 01 SolДокумент4 страницыCert 01 SolSusana RebellónОценок пока нет

- Cert 03 SolДокумент3 страницыCert 03 SolSusana RebellónОценок пока нет

- 1427114448804-Guía 6 Principiantes IДокумент1 страница1427114448804-Guía 6 Principiantes ISusana RebellónОценок пока нет

- Brochure Postes CamelДокумент3 страницыBrochure Postes Camelcarolina moralesОценок пока нет

- 1425390234157-Guía 3 Principiantes IДокумент2 страницы1425390234157-Guía 3 Principiantes ISusana RebellónОценок пока нет

- 1426008526748-Guía 4 Principiantes IДокумент1 страница1426008526748-Guía 4 Principiantes ISusana RebellónОценок пока нет

- Guía Completa para Garantizar La Calidad en La FranquiciaДокумент15 страницGuía Completa para Garantizar La Calidad en La FranquiciaTatiana SotoОценок пока нет

- Mantenimiento Sys20Документ18 страницMantenimiento Sys20Bernardo PáramoОценок пока нет

- VERSIÓN 4.1. Manual - Polymath - EspañoldocxДокумент68 страницVERSIÓN 4.1. Manual - Polymath - EspañoldocxElizabeth EscalanteОценок пока нет

- Gssl-Prl-01-Procedimiento Registro Linea InpsaselДокумент8 страницGssl-Prl-01-Procedimiento Registro Linea Inpsaselg torresОценок пока нет

- EQUIPO FUJIFILM para Desbloquear El Envío de Imágenes o Se Quedo en Cola de Envio EstudiosДокумент11 страницEQUIPO FUJIFILM para Desbloquear El Envío de Imágenes o Se Quedo en Cola de Envio EstudiosMARIA F. GUERRAОценок пока нет

- Reglamentacion Diversion NocturnaДокумент10 страницReglamentacion Diversion NocturnaAnonymous AkkWQNОценок пока нет

- XADESDIANДокумент2 страницыXADESDIANJose AguilarОценок пока нет

- Mapa C. de Estructura de Programas Leng BasicoДокумент1 страницаMapa C. de Estructura de Programas Leng BasicoViridiana ColoradoОценок пока нет

- 1.1 Cep - Ofimatica ProfesionalДокумент5 страниц1.1 Cep - Ofimatica ProfesionalEDWIN OMAR LEIVA SANCHEZОценок пока нет

- Análisis de Mercado para TELMEXДокумент1 страницаAnálisis de Mercado para TELMEXEduardo Hernández100% (1)

- TAREAДокумент7 страницTAREAMabel Rojas RoqueОценок пока нет

- Unir DI Deteccion de Delitos InfoДокумент13 страницUnir DI Deteccion de Delitos InfoDarwin Díaz Calderón100% (1)

- Definición de Contabilidad GeneralДокумент4 страницыDefinición de Contabilidad GeneralMemoGEОценок пока нет

- Cufe: 4fcaee29fcb0 E73cabb49433 01f28ecc Representacion Grafica de La Factura ElectronicaДокумент2 страницыCufe: 4fcaee29fcb0 E73cabb49433 01f28ecc Representacion Grafica de La Factura Electronicasofia avilaОценок пока нет

- Plantilla Manual InstalacionДокумент21 страницаPlantilla Manual InstalacionBrayan Bernal BrsОценок пока нет

- Programas Parcial 2Документ22 страницыProgramas Parcial 2Roldán Ortiz César GeovanniОценок пока нет

- Prueba 7º EcuacionesДокумент2 страницыPrueba 7º EcuacionesHernán CorreaОценок пока нет

- Ensamblador Procesador 80 X 86Документ22 страницыEnsamblador Procesador 80 X 86kev41424344Оценок пока нет

- Programacion Avanzada en JavaДокумент347 страницProgramacion Avanzada en JavaCarlos Daniel Valente AlbarracinОценок пока нет

- Manual Scratch para RobóticaДокумент12 страницManual Scratch para RobóticaMoises David Bados OsorioОценок пока нет

- Manualcon MinitabДокумент76 страницManualcon MinitabAntony Vega CernaОценок пока нет

- Material de Reforzamiento Unidad 5 (Networking), (Senati)Документ8 страницMaterial de Reforzamiento Unidad 5 (Networking), (Senati)Jesús IsiqueОценок пока нет

- Analisis de Las MarcasДокумент5 страницAnalisis de Las MarcasAlonso HernándezОценок пока нет

- Hackeando+Mentes+ (1) PT EsДокумент60 страницHackeando+Mentes+ (1) PT EsAlmacen 387Оценок пока нет

- Ensayo Cap 10-Detección, Administración y Mantenimiento de DispositivosДокумент4 страницыEnsayo Cap 10-Detección, Administración y Mantenimiento de DispositivosAlixmario Alexander Gomez SolanoОценок пока нет

- Sistemas de Informacion TransaccionalesДокумент4 страницыSistemas de Informacion TransaccionalesKevin VsОценок пока нет

- OBJETIVOS Sap2000Документ1 страницаOBJETIVOS Sap2000GABRIELA FRANCOОценок пока нет

- Didáctica en El Uso de Recursos InformáticosДокумент12 страницDidáctica en El Uso de Recursos InformáticosFelipeОценок пока нет

- Presentacion Fibra Optica Consideraciones de InstalaciónДокумент27 страницPresentacion Fibra Optica Consideraciones de InstalaciónEdwin TellezОценок пока нет

- UmlДокумент1 страницаUmlMarvin Rivas EscobarОценок пока нет