Академический Документы

Профессиональный Документы

Культура Документы

Hittinger R. Warner,: " A Developmental Intrinsic-Barrier Transistor"

Загружено:

Susanoo12Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Hittinger R. Warner,: " A Developmental Intrinsic-Barrier Transistor"

Загружено:

Susanoo12Авторское право:

Доступные форматы

3.

“ A DevelopmentalIntrinsic-Barrier

Transistor”

W. C. HITTINGER

and R. M. WARNER,JR.

Bell Telephone Laboratories

The intrinsic-barrier design extends transistor frequency

range

withoutsacrificing

power-handlingcapacity. A

review of the design principles is presented, together with

adescription of a moderate-powerdevelopmental model,

the M1830. Aset of 156 M1830 unitswasrecentlymade

in the laboratory; 53 of these possessed measurable VHF

characteristics,anddiagramsarepresentedhereshowing

parameterdistributions for theseunits.Outputpower

determinationsweremade for 15 units(notnecessarily

thebestones of the group). Nine units gave morethan

20 milliwatts of sustainedusefuloutputat 200 mega-

cycles per second. The bestunitstudied indetailthus

far displayed an alpha of 0.88 at 100 cycles persecond,

ohmic base resistance of 106 ohms at 250 megacycles per

second, collector

capacitance of 0.2 micromicrofarads,

groundedbase cutoff frequency of 238 megacycles per

second,andoutput power of 30 milliwatts at 200 mega-

cycles per second.

p. “Recent Advances in Power Junction

Transistors”

B. N. SLADE

RCA Laboratories, Princeton

This paper will discuss experimental P-N-P and N-P-N

power transistors having low collectorleakage,

high

breakdownvoltageandhighcurrent gain. P-N-Ptransis-

tors have been made with d.c. current amplification factors

ashighas 140 at 1 ampere, collector leakage current on

the order of 20 microamperes and collector breakdown as

highas 200 volts. Thesecharacteristicsareattributedin

parttotheuse of specialjunctionalloysconsisting of

indiumandgalliumoraluminum.

N-P-N transistors having leakage and voltage breakdown

characteristics similar to the P-N-P transistors have been

madewith d.c. currentamplificationfactorsashigh as

200 at 1 ampere.An alloy of arsenic in lead is used for

boththeemitterandcollectorjunctions.

Other considerations in the design of power transistors

suchas baseleadresistance, emitter tocollectorpunch

through,andthermaldropwillbe discussed. Typical

characteristics of transistorsdesignedforClass B ampli-

fier useaswellashighvoltageswitchingapplications

willbepresented.

5. “Yacuum-Baking Encapsulation Techniques

and Improved Reliability of NPN Alloy

Transistors”

N. P. BURCHAM

and P. MILLER

Bell Telephone Laboratories

Otherinvestigators*havereported that improvedre-

liabilityfor NPN alloytransistorscanbeexpectedwith

vacuumbakingandvacuumencapsulation of the device.

Our pilotshopexperiencewithrelativelylargenumbers

13

of NPN alloytransistorshasdemonstratedthat vacuum

encapsulation does offer definitegains in reliability over

earliermethodsforencapsulation.Anextension of this

encapsulationtechnique involving employing a gettering

agentresultsinfurtherimprovementinthestability of

the device characteristicswith time.

Feasibility of use of theseencapsulationprocedures in

high level productionhasbeenachievedthroughdesign

of the high-vacuum station and the procedures associated

withitsoperation.

Details of theequipmentandprocessandplots of

transistor parameters versus time will be presented.

"A. J. Wahl and J. J. Kleimack, Bell Telephone Labora-

tories, atthe A.1.E.E.-I.R.E. transistorconference, Uni-

versity of Pennsylvania, 1955.

14

Вам также может понравиться

- High Voltage Fast Ramp Pulse Generation Using AvalДокумент3 страницыHigh Voltage Fast Ramp Pulse Generation Using AvalНенад СаканОценок пока нет

- Wireless NanotechnologyДокумент8 страницWireless NanotechnologymssprasadОценок пока нет

- Focusing of The 80 GHZ Microwave-InterferometerДокумент13 страницFocusing of The 80 GHZ Microwave-InterferometerpinoОценок пока нет

- Palmer 2001 0420Документ3 страницыPalmer 2001 0420Particle Beam Physics LabОценок пока нет

- Output Characteristics of A Kind of High-Voltage Pulse Transformer With Closed Magnetic CoreДокумент9 страницOutput Characteristics of A Kind of High-Voltage Pulse Transformer With Closed Magnetic Corekar mugilanОценок пока нет

- Transistor Technique, GernsbackДокумент97 страницTransistor Technique, GernsbackKevin HaworthОценок пока нет

- Zhang 1995 0221Документ3 страницыZhang 1995 0221Particle Beam Physics LabОценок пока нет

- Simple MOSFET-Based High-Voltage Nanosecond Pulse Circuit: Alton Chaney and Raji SundararajanДокумент6 страницSimple MOSFET-Based High-Voltage Nanosecond Pulse Circuit: Alton Chaney and Raji SundararajanNikОценок пока нет

- Stability in Small Signal Common Base AmplifiersДокумент11 страницStability in Small Signal Common Base AmplifiersFoo BerryОценок пока нет

- The Resonant Link Converter-A New Concept in Static Power ConversionДокумент9 страницThe Resonant Link Converter-A New Concept in Static Power ConversionDar JahangeerОценок пока нет

- Practical Design of Generator Surge Protection PDFДокумент8 страницPractical Design of Generator Surge Protection PDFAlvaro OliveiraОценок пока нет

- Multirestransfoindth: BetweentheДокумент6 страницMultirestransfoindth: BetweenthepedramОценок пока нет

- P 664Документ10 страницP 664TomasОценок пока нет

- DC PlasmaДокумент10 страницDC PlasmaiyengarnrОценок пока нет

- A High Current Pulse Generator For Magnetizing Thin Magnetic FilmsДокумент3 страницыA High Current Pulse Generator For Magnetizing Thin Magnetic FilmslakisОценок пока нет

- Variable Pulse Width Piezoelectric Ultrasonic TR PDFДокумент5 страницVariable Pulse Width Piezoelectric Ultrasonic TR PDFMoriartyОценок пока нет

- Fault Location in Power Transformers During Impulse TestsДокумент6 страницFault Location in Power Transformers During Impulse TestsMozar CostaОценок пока нет

- Simulation and Tests On Surge Arresters in High-Voltage LaboratoryДокумент5 страницSimulation and Tests On Surge Arresters in High-Voltage LaboratoryM. REZA FEBRI PUTRAОценок пока нет

- Metal Detector (E) : HN Prolcct$ F or THC HloilmcnbrДокумент5 страницMetal Detector (E) : HN Prolcct$ F or THC HloilmcnbrtihomihoОценок пока нет

- Electromechanical Properties of New Electrostrictive Materials For Underwater Acoustical ApplicationsДокумент2 страницыElectromechanical Properties of New Electrostrictive Materials For Underwater Acoustical Applicationsritzky fachriОценок пока нет

- Wang 2Документ9 страницWang 2sarangapaniОценок пока нет

- High-Voltage Impulse Testers: E.K. HowellДокумент7 страницHigh-Voltage Impulse Testers: E.K. Howellshrikris51Оценок пока нет

- Surge-Transferred Overvoltages in Earthing/Auxiliary TransformersДокумент6 страницSurge-Transferred Overvoltages in Earthing/Auxiliary TransformersSudhir RavipudiОценок пока нет

- JE Meyer MOS Cap Model RCA-Review-1971-MarДокумент180 страницJE Meyer MOS Cap Model RCA-Review-1971-MarKrzyszto FPОценок пока нет

- Digital Testing of High-Voltage Circuit BreakersДокумент5 страницDigital Testing of High-Voltage Circuit Breakersvallala venkateshОценок пока нет

- Applications of High Frequency Magnetic Components For Switching Resonant Mode Power SupplyДокумент6 страницApplications of High Frequency Magnetic Components For Switching Resonant Mode Power SupplyOBOSA EGHE-AIDEYANОценок пока нет

- Surge Protection of A Large Medium Voltage Motor - A Case StudyДокумент6 страницSurge Protection of A Large Medium Voltage Motor - A Case StudywillytОценок пока нет

- Elka Telkom Week 2Документ48 страницElka Telkom Week 2AzHar HrОценок пока нет

- Measuring very low AC resistances in large cablesДокумент4 страницыMeasuring very low AC resistances in large cablesMarcio Antonio SensОценок пока нет

- A.A Low Cost Spectrometer For NMR Measurements in The Earth S Magnetic Field PDFДокумент9 страницA.A Low Cost Spectrometer For NMR Measurements in The Earth S Magnetic Field PDFDejan CorovicОценок пока нет

- Sheet Beam Klystron RF CavltlesДокумент3 страницыSheet Beam Klystron RF CavltlesrajarpitОценок пока нет

- Elf Circuit DesignДокумент5 страницElf Circuit DesignKatja GoiteОценок пока нет

- Bandwidth of Current TransformersДокумент9 страницBandwidth of Current TransformersarturcmaОценок пока нет

- GaN-Based Microwave Power Amplifiers with Broadband MatchingДокумент3 страницыGaN-Based Microwave Power Amplifiers with Broadband MatchingRabbia SalmanОценок пока нет

- Fun Projects 07 ChapterДокумент3 страницыFun Projects 07 ChaptertihomihoОценок пока нет

- Jurnal Kickless-PN - 183 - PriceДокумент6 страницJurnal Kickless-PN - 183 - PriceRais MuzhaffarОценок пока нет

- Simulation of Power Quality Problems On A University Distribution SystemДокумент6 страницSimulation of Power Quality Problems On A University Distribution SystemViralBipinchandraRathodОценок пока нет

- Thyristors For Commutation of Current Impulse With Extremely High AmplitudeДокумент5 страницThyristors For Commutation of Current Impulse With Extremely High AmplitudeAndres BornacellyОценок пока нет

- Designand Analysisofthecontrolsystemofhighvoltage 400 K VDCpowerДокумент6 страницDesignand Analysisofthecontrolsystemofhighvoltage 400 K VDCpowerSebastian CostaОценок пока нет

- Scheme For Accelerated Trip For Faults in The SecoДокумент3 страницыScheme For Accelerated Trip For Faults in The SecoSALAH SALLAMОценок пока нет

- Transmission and Attenuation of Electromagnetic Pulses: Id: 004.pulses - Tex, V 1.35 2013/08/27 19:30:54 Spatrick ExpДокумент4 страницыTransmission and Attenuation of Electromagnetic Pulses: Id: 004.pulses - Tex, V 1.35 2013/08/27 19:30:54 Spatrick ExpTulsiОценок пока нет

- A CMOS Bandgap ReferenceДокумент10 страницA CMOS Bandgap ReferencemeslonОценок пока нет

- Single-Sideband Transmission by Envelope: Elimination RestorationДокумент4 страницыSingle-Sideband Transmission by Envelope: Elimination Restorationgaurav bhargavОценок пока нет

- An Improved Transformer For LLC Resonant Inverter For Induction Heating ApplicationsДокумент8 страницAn Improved Transformer For LLC Resonant Inverter For Induction Heating ApplicationsIvan PopovicОценок пока нет

- Pruebas en Transformadores IeeeДокумент9 страницPruebas en Transformadores IeeeMarcelo VillarОценок пока нет

- Some Aspects of The Design of Balanced Rectifier Modulators For Precision Applications by D. G., PH.D., Associate MemberДокумент1 страницаSome Aspects of The Design of Balanced Rectifier Modulators For Precision Applications by D. G., PH.D., Associate MembershirtquittersОценок пока нет

- An 1210Документ3 страницыAn 1210RNNPVNОценок пока нет

- Neukomm PДокумент15 страницNeukomm PDiego RodriguezОценок пока нет

- Basic Study On Pulse Generator For micro-EDM: OriginalarticleДокумент6 страницBasic Study On Pulse Generator For micro-EDM: OriginalarticlegerdОценок пока нет

- Alpha-Voltaic Sources Using Diamond As Conversion MediumДокумент1 страницаAlpha-Voltaic Sources Using Diamond As Conversion MediumHarsh VardhanОценок пока нет

- Metal Oxide Surge Arrester A Tool For LiДокумент6 страницMetal Oxide Surge Arrester A Tool For LiCLAVOTОценок пока нет

- Abridgment of Movements of Overhead Line Conductors During Short Circuits - 1927Документ5 страницAbridgment of Movements of Overhead Line Conductors During Short Circuits - 1927Sirous EghlimiОценок пока нет

- Syllabus and Questionbank Electrical Power System I 19 20Документ12 страницSyllabus and Questionbank Electrical Power System I 19 20dhyan shahОценок пока нет

- AM Antenna System For DRMДокумент18 страницAM Antenna System For DRMETIVNSОценок пока нет

- Electronics – From Theory Into Practice: Applied Electricity and Electronics DivisionОт EverandElectronics – From Theory Into Practice: Applied Electricity and Electronics DivisionРейтинг: 5 из 5 звезд5/5 (1)

- Electronics—From Theory Into Practice: Pergamon International Library of Science, Technology, Engineering and Social StudiesОт EverandElectronics—From Theory Into Practice: Pergamon International Library of Science, Technology, Engineering and Social StudiesРейтинг: 5 из 5 звезд5/5 (2)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Radio Frequency Transistors: Principles and Practical ApplicationsОт EverandRadio Frequency Transistors: Principles and Practical ApplicationsРейтинг: 4 из 5 звезд4/5 (2)

- Constraint Programming: Michael Trick Carnegie MellonДокумент41 страницаConstraint Programming: Michael Trick Carnegie MellonSusanoo12Оценок пока нет

- Akron 1Документ2 страницыAkron 1Susanoo12Оценок пока нет

- Pipeline Fracture Experience - Cabral and Kimber 1997Документ21 страницаPipeline Fracture Experience - Cabral and Kimber 1997Susanoo12100% (1)

- Solving Polynomial Systems Using Branch and PruneДокумент31 страницаSolving Polynomial Systems Using Branch and PruneSusanoo12Оценок пока нет

- Drama Glossary A-ZДокумент9 страницDrama Glossary A-ZSusanoo12Оценок пока нет

- 1.1 Economic Losses: © 2010 by Taylor and Francis Group, LLCДокумент4 страницы1.1 Economic Losses: © 2010 by Taylor and Francis Group, LLCSusanoo12Оценок пока нет

- Dancehall's Negative Impacts on StudentsДокумент6 страницDancehall's Negative Impacts on StudentsSusanoo120% (2)

- OMHS Procedures ManualДокумент187 страницOMHS Procedures ManualSusanoo12Оценок пока нет

- Pipeline Mechanical Design Formulas and Stress CalculationsДокумент94 страницыPipeline Mechanical Design Formulas and Stress CalculationsSusanoo12100% (1)

- Fault Tree Handbook With Aerospace ApplicationsДокумент218 страницFault Tree Handbook With Aerospace ApplicationsRakesh SandarativjuОценок пока нет

- FMEA Guide Failure ModesДокумент21 страницаFMEA Guide Failure ModesSusanoo12Оценок пока нет

- CHP 9Документ11 страницCHP 9Susanoo12Оценок пока нет

- 15 FtaДокумент2 страницы15 FtaSusanoo12Оценок пока нет

- EUR22302ENДокумент58 страницEUR22302ENSusanoo12Оценок пока нет

- Chap9 1200Документ29 страницChap9 1200Susanoo12Оценок пока нет

- 3 10 245809AutomotiveFTAДокумент12 страниц3 10 245809AutomotiveFTASusanoo12Оценок пока нет

- Shaft Alignment ManualДокумент76 страницShaft Alignment Manualmjerkan100% (11)

- 10 1 1 57Документ14 страниц10 1 1 57Susanoo12Оценок пока нет

- A New Method For Abbreviating The Fault Tree Graphical RepresentationДокумент4 страницыA New Method For Abbreviating The Fault Tree Graphical RepresentationSusanoo12Оценок пока нет

- Answering Substation Automation Questions Through Fault Tree AnalysisДокумент29 страницAnswering Substation Automation Questions Through Fault Tree AnalysisMichael Parohinog GregasОценок пока нет

- 1313Документ5 страниц1313Susanoo12Оценок пока нет

- CO2 Well Drilling&Completion ProcedureДокумент7 страницCO2 Well Drilling&Completion Proceduresmithyry2014Оценок пока нет

- Full TextДокумент8 страницFull TextSusanoo12Оценок пока нет

- MC02-02 Fighting Debris HTF Bearings For TransmissionsДокумент10 страницMC02-02 Fighting Debris HTF Bearings For TransmissionsSusanoo12Оценок пока нет

- Lead-Acid Battery InfoДокумент16 страницLead-Acid Battery Infongt881Оценок пока нет

- 2008 04 25 - C04Документ6 страниц2008 04 25 - C04Susanoo12Оценок пока нет

- 1998 08 Asymtek Flip Chip Encapsulation ReliabilityДокумент13 страниц1998 08 Asymtek Flip Chip Encapsulation ReliabilitySusanoo12Оценок пока нет

- Industry Definitions For The Condition of Electronic Components and PackagingДокумент3 страницыIndustry Definitions For The Condition of Electronic Components and PackagingSusanoo12Оценок пока нет

- Takahashi Japanese Electronics After WWIIДокумент16 страницTakahashi Japanese Electronics After WWIISusanoo12Оценок пока нет

- Original PhotonicsEurope2006 - NEMOДокумент11 страницOriginal PhotonicsEurope2006 - NEMOSusanoo12Оценок пока нет

- IT Phy F5 Final Year (BL)Документ18 страницIT Phy F5 Final Year (BL)Noorleha Mohd YusoffОценок пока нет

- 74HC195Документ10 страниц74HC195MUHAMMAD SISWANTOROОценок пока нет

- Rfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets FeaturesДокумент8 страницRfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets Featuresaleh sharapovОценок пока нет

- Leph 201404 Econtent2019 PDFДокумент27 страницLeph 201404 Econtent2019 PDFPriyanshu VishwakarmaОценок пока нет

- Standpipe Piezo DatasheetДокумент2 страницыStandpipe Piezo DatasheetQoudar RamdhaniОценок пока нет

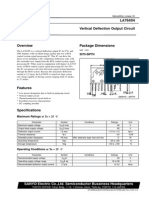

- LA7845NДокумент5 страницLA7845NGerardo ReyesОценок пока нет

- 3rdTLE ExamДокумент2 страницы3rdTLE ExamSheila Divinagracia - EscobedoОценок пока нет

- Light Dependent ResistorДокумент4 страницыLight Dependent ResistorantonerajОценок пока нет

- Class XII Chemistry Important Questions and Common Errors Chapter 1 Solid State 1. Types of Packing Square Close PackingДокумент77 страницClass XII Chemistry Important Questions and Common Errors Chapter 1 Solid State 1. Types of Packing Square Close PackingDeepak Singh100% (1)

- LG L222WS Color Monitor Service ManualДокумент41 страницаLG L222WS Color Monitor Service ManualDorian SvircevicОценок пока нет

- I A) B) 2 A) B) If 3 A) B) C) : Unitvnnsifv''.. Examination (R&S)Документ2 страницыI A) B) 2 A) B) If 3 A) B) C) : Unitvnnsifv''.. Examination (R&S)Adithyan JОценок пока нет

- Chapter 2Документ114 страницChapter 2aregawi weleabezgiОценок пока нет

- Automatic Street Light Control System Using IOTpptДокумент21 страницаAutomatic Street Light Control System Using IOTpptjeevi90% (10)

- Faac 400 ManДокумент24 страницыFaac 400 ManJuanОценок пока нет

- Sandeep ThesisДокумент67 страницSandeep Thesiskuldeep100% (1)

- EDC 2markДокумент15 страницEDC 2markavv456Оценок пока нет

- Tremo CB ReportДокумент51 страницаTremo CB ReportmadnarkОценок пока нет

- Olivier Mongin Et Al - Brilliant Organic Nanodots: Novel Nano-Objects For BionanophotonicsДокумент12 страницOlivier Mongin Et Al - Brilliant Organic Nanodots: Novel Nano-Objects For BionanophotonicsGlade680Оценок пока нет

- Schering BridgeДокумент13 страницSchering BridgeEngr Wahab Marwat100% (2)

- Temp Based Fan Speed Control ProjectДокумент62 страницыTemp Based Fan Speed Control ProjectKushal Malhotra100% (1)

- Microcontroller Based Power Transformer Protection SystemДокумент77 страницMicrocontroller Based Power Transformer Protection SystemFuh ValleryОценок пока нет

- Akai-AM2200 AmpДокумент23 страницыAkai-AM2200 AmpRinaldo RakОценок пока нет

- LS7210 (Programmable Digital Delay Timer)Документ4 страницыLS7210 (Programmable Digital Delay Timer)carlosОценок пока нет

- PCB Component MBI ICДокумент22 страницыPCB Component MBI ICAmit BhatiaОценок пока нет

- Accurate Evaluation of Leakage Inductance in High-Frequency Transformers Using AnДокумент8 страницAccurate Evaluation of Leakage Inductance in High-Frequency Transformers Using AnNishi mallickОценок пока нет

- Multi-functional LCR meter measures components and IR signalsДокумент1 страницаMulti-functional LCR meter measures components and IR signalsManu NОценок пока нет

- Compal Electronics Schematic for Intel Ivy Bridge CPU and Panther Point PCHДокумент46 страницCompal Electronics Schematic for Intel Ivy Bridge CPU and Panther Point PCHamier jrs100% (1)

- Datasheet HMC285 para El ExamenДокумент4 страницыDatasheet HMC285 para El ExamenMarcoОценок пока нет

- VersaSTAT 3 Manual PDFДокумент30 страницVersaSTAT 3 Manual PDFFelipe SanhuezaОценок пока нет

- Faraday's Laws of Electrolysis and Battery StorageДокумент20 страницFaraday's Laws of Electrolysis and Battery StorageAnonymous eWMnRr70qОценок пока нет