Академический Документы

Профессиональный Документы

Культура Документы

PLL en VHDL

Загружено:

Josué JmlАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

PLL en VHDL

Загружено:

Josué JmlАвторское право:

Доступные форматы

SOMI XV

Ele – 24 - 1

Implementación de un PLL Digital con Dispositivos

programables en VHDL

J. Lopez, F. Sandoval, J. Santana.

CINVESTAV-Guadalajara

Prol. López Mateos Sur #590, C.P. 45090, Guadalajara, Jalisco

Tel.+52 (3) 6-841580, e-mail: olopez@gdl.cinvestav.mx

Resumen.

Este trabajo ha enfocado su atención al desarrollo de un PLL a través de software. Se ha elegido

un PLL lineal (SPLL) como ejemplo para demostrar la factibilidad de este tipo de diseño así como

su buen desempeño. Se hace el estudio de los diferentes bloques que componen a un SPLL y se

obtienen las ecuaciones matemáticas, así como sus correspondientes modelos algorítmicos. Estos

algoritmos fueron empleados para crear un programa en Lenguaje con el objetivo de poder simular

el comportamiento del PLL. Posteriormente, se implementarán dichos algoritmos en un dispositivo

programable.

Abstract.

In this paper, the developing of a PLL by software is presented. As an example, We have chosen a

linear PLL (LPLL) to show that this sort of design is practicability and to prove its performance. Each

block of a LPLL is analyzed in order to get their mathematical expressions and then their algorithm

models. Those algorithms were used to create a C program to simulate the behavior of the PLL.

After that, we will implement such algorithms in a programmable device.

1. INTRODUCCIÓN.

En los últimos años dos tipos diferentes de PLL se han hecho muy atractivos: Los PLL

completamente digitales (ADPLL) y el PLL por software (SPLL). Las aplicaciones de los PLL por

software fueron consideradas bastante exóticas hace diez años, pero hoy en día, la disponibilidad

de procesadores de señales digitales rápidos (DSP) ha ampliado el campo de aplicación de este

tipo de PLLs.

Otro dramático cambio en los últimos años ha sido la manera en que se puede desarrollar el

diseño y simulación de los diferentes tipos de PLL. En la era de los microcontroladores y

Procesadores Digitales de Señales (DSP) es obvia la idea de poder implementar un sistema PLL

por software. Cuando se hace de esta manera, las funciones del PLL son efectuadas por

algoritmos. Usando programas por software uno puede revisar el desempeño de un circuito PLL

como si éste fuera verificado físicamente por un osciloscopio.

Debido a que cada PLL conocido (PLL lineal, PLL digital, PLL completamente digital) puede ser

implementado por software, el número de variantes se ha vuelto infinito, este trabajo enfocará su

atención en implementar un PLL lineal a través de esta técnica de diseño.

2. OBTENCIÓN DE LAS ECUACIONES REPRESENTATIVAS DE LOS BLOQUES DE UN PLL

LINEAL

Un PLL. Sincroniza, dentro de cierto ancho de banda, una señal de salida con una señal de

entrada tanto en frecuencia como en fase. Si la señal cambia de frecuencia, el PLL también lo hace

de tal manera que la diferencia de fase entre la señal de salida generada por él y la señal entrante

sea cero o casi cero. A partir de la anterior descripción de funcionamiento, se puede ir formando el

bloque requerido para la implementación por hardware de un LPLL, y a partir de las ecuaciones

que describen a cada bloque, su respectiva analogía por software. Un LPLL esta formado por las

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

siguientes etapas: a)Un oscilador controlado por voltaje (VCO), b) un detector de fase (PD) y c) un

filtro de lazo.

La mayoría de los sistemas son analizados por medio de su función de transferencia H(s), que

relaciona la señal de entrada con la señal de salida de un sistema. H(s) esta dada por

(1)

H (s ) =

U 2 (s)

U 1 ( s)

donde U1(s) y U2(s) son la transformada de Laplace u1(t) y u2(t), respectivamente. La señal de

entrada u1(t) es una onda senoidal y es descrita por

u1 (t ) = A sin[ω 1t + θ 1 (t )] (2)

Considerando una señal de entrada con modulación en frecuencia, con una frecuencia central ωo,

un incremento en dicha frecuencia provocara un cambio de fase de manera que

u1 (t ) = A sin[ω 0 t + ∆ω t ] = A sin φ1 ( 3)

Del anterior análisis, es posible concluir que la información en esta señal va en la fase, por lo que

los subsecuentes estudios se enfocaran en ella. Para iniciar el análisis, se supone que el PLL está

sincronizado y que permanece en este estado, así, se podrá determinar la función de transferencia

H(s) que relaciona la fase θ1 de la señal de entrada con la fase θ2 de la señal de salida:

Θ2 (5)

H ( s) =

Θ1

Donde Θ1(s) y Θ2(s) representan la transformada de Laplace de las señales de fase θ1(t) y θ2(t),

respectivamente. Para obtener la función de transferencia completa, se deben obtener las

funciones de transferencia y expresiones matemáticas para cada una de los bloques que forman el

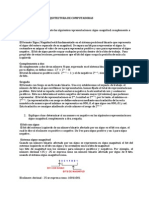

PLL lineal. La figura 1 muestra la relación entre los diferentes bloques de un LPLL .

2.1 Detector de Fase

La señal de entrada es una señal senoidal dada por Ec. (2). mientras que para cualquier PLL, la

1

señal de salida es una onda cuadrada y puede ser escrita como una función Walsh

u 2 ( t ) = Bw (ω 2 t + θ 2 ) (6)

Esta señal, junto con u1(t), es mostrada en la Figura 2. u1(t) se ha representado con un ángulo de

fase θ1 diferente al de u2(t), θ2. Por simplicidad se asume que las fases son constantes en el

2

tiempo. u2(t) también puede ser representada por su serie de Fourier como

∞ ∞ (7)

u 2 (t ) = a o + ∑ a n cos(nω o t + θ 2 ) + ∑ b n sen(nω o t + θ 2 )

−∞ −∞

De la Figura 2, se concluye que u2(t) es una función con simetría de cuarto de onda par, por lo que

ao y bn son cero y u2(t) constará únicamente de componentes armónicas de orden par

2,3

cosenoidales dadas por

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Figura 1. Diagrama a bloques de un LPLL.

4 nπ (8)

an = sen para n = 1,3,5,7,..

πnT 2

entonces

4 (9)

cos(ω o t + θ 2 ) − cos(3ω o t + θ 2 ) + cos(5ω o t + θ 2 ) − cos(7ω o t + θ 2 ) + K

1 1 1

u 2 (t ) =

π 3 5 7

Multiplicando u1(t) y u2(t) se obtiene la señal del detector de fase ud(t). Cuando el PLL está

sincronizado con la señal de entrada ω2=ω1, esta multiplicación se puede expresar por

A ⋅ Bsen(θ 1 − θ 2 ) + A ⋅ Bsen(2ω 1t + θ 1 + θ 2 ) + A ⋅ Bsen(2ω 1t + θ 2 − θ 1 )

2 2 2

u d (t ) =

π π π

+ A ⋅ Bsen(4ω 1t + θ 2 + θ 1 ) + A ⋅ Bsen(4ω 1t + θ 2 − θ 1 ) + A ⋅ Bsen(6ω 1t + θ 2 + θ 1 ) + K

2 2 2

π π π

(10)

El primer término de Ec. 10, es un término de DC y es el que nos interesa, puesto es empleado

para corregir la diferencia de fases. La señal que el detector de fase arroja no esta libre de

términos de armónico; al revisar estos términos armónicos se concluye que bastará con un filtro

pasabajos, con la frecuencia adecuada de corte, para eliminar las componentes que no sean de

DC. Tomando en cuenta únicamente el término de DC

u d (t ) = K d senθ e (11)

2

Kd = A⋅ B

π (12)

donde θe = θ1-θ2 y Kd es la ganancia del detector. Cuando el error de fase es pequeño, y en

radianes, la función seno puede ser reemplazada por el ángulo, por lo que

u d (t ) ≈ K d θ e (13)

2.2. Filtro Pasa Bajos

Para eliminar los armónicos presentes en ud(t) resulta indispensable un filtro pasabajas. Este filtro

es el llamado filtro de lazo. En la mayoría de los diseños para LPLL un filtro de primer orden es

1

utilizado . En este caso, el filtro requerido es diseñado para una frecuencia de corte igual o menor

que ω1, de acuerdo con Ec. (10).

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Figura 2. Señales que entran al detector de fase.

La elección adecuada del filtro será fundamental en el desempeño del LPPL y también influye en el

algoritmo por software que será implementado. Se eligió un filtro activo del tipo integrador

proporcional) cuya topología es mostrada en la Figura 3. La señal que se obtiene a la salida del

filtro es uf(t). Efectuando un análisis en el circuito de la figura 3, se obtiene

U d (s)

I R1 =

R1 (14a)

U f (s)

I R2 =

1

R1 +

SC (14b)

Como IR2 = -IR1 se obtiene

U f (s)1 + sτ 2

F ( s) = = (15)

U d ( s) sτ 1

con τ 1 = R1C

(16a)

τ 2 = R2 C (16b)

La Figura 4 muestra la respuesta de este tipo de filtro. Los valores que se asignaron fueron: R1 =

50KΩ, R2 = 100 KΩ y C = 10 µF. De la gráfica se observa que la respuesta es decreciente y

presenta un cero en τ2, y un polo en cero por lo que empieza a decrecer desde una frecuencia casi

cero. Estas dos características fueron las que determinaron la elección de este filtro Se podría

haber usado un filtro de más alto orden pero ello implica una mayor dificultad para mantener la

estabilidad del sistema ya que se introduciría un corrimiento de fase, que es precisamente lo que

se quiere corregir.

2.3. VCO

La frecuencia del VCO esta dada por

ω 2 = ω o + ∆ω 2 (t ) (17)

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Figura 3. Diagrama esquemático del Filtro activo PI.

Como el desvío de frecuencia, ∆ω(t), es controlado por uf(t), entonces

∆ω (t ) = K o u f (t ) (18)

donde Ko es la ganancia del VCO. E l modelo del VCO debería de proporcionar la fase de salida θ2,

y no la frecuencia de salida, puesto que se está buscando la función de transferencia de Fase y no

de frecuencia. La fase instantánea total φ 2 esta dada por:

φ 2 = ω o t + K o ∫ u f (t ) (19)

donde

θ 2 = K o ∫ u f (t )

(20)

La transforma de Laplace de la fase de salida θ2 es definida como

Ko

Θ 2 ( s) = U f (s)

s (21)

Así que la función de transferencia del VCO esta dada por

Θ 2 (s) K o

=

U f (s) s (22)

Para las señales de fase, el VCO simplemente representa un integrador. Con las ecuaciones

obtenidas ya es posible dar un modelo lineal del LPLL. Del modelo de la Figura 5, la función de

transferencia de fase es

Θ 2 (s) K o K d F ( s) (23)

H ( s) = =

Θ1 ( s ) s + K o K d F ( s )

F(s) representa la función de transferencia del filtro PI. Sustituyendo Ec. (15) en Ec. (23)

Ko Kd

(τ 2 s + 1)

τ1

H ( s) =

K K τ K K

s2 + o d 2 s + o d

τ1 τ1 (24)

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

10V

5V

0V

1.0mHz 10mHz 100mHz 1.0Hz 10Hz 100Hz

V(C2:2)

Frequency

Figura 4. respuesta en frecuencia del filtro PI.

Es bien conocida la ecuación que gobierna todo sistema de segundo orden en el dominio de la

4

variable s, la cual se define como

k1s 2 + k2 s + K 0

H ( s) =

s 2 + ζω n s + ω n2 (25)

Comparando el denominador de Ec. (24) con el de Ec. (25), las variables k1 y k2 son nulas y se

tiene que

Ko Kd

ωn = (26a)

τ1

τ2

ζ = ωn (26b)

2

Un diagrama de Bode para Ec. (24), Figura 6, indica que el LPLL es un filtro pasa bajos de primer

orden capaz de seguir a una señal cuyo espectro de frecuencia está entre cero y la frecuencia

natural ωn. El factor ζ indica el nivel de sobretiro que puede tener el sistema PLL en el borde de la

frecuencia natural, como se requiere de un sistema con una banda de paso plana, un ζ=0.707 es

1

óptimo . Si se define una función de error

Θ 1 ( s ) −Θ 2 ( s )

H ( s) = (27)

Θ1 ( s )

es fácil ver en un diagrama de bode con ζ=0.707, Figura 7, que para modulaciones de frecuencia

más pequeñas que ωn, el error de fase permanece pequeño.

3. IMPLEMENTACIÓN DE LOS ALGORITMOS PARA EL PLL LINEAL.

Después de la obtención de las expresiones matemáticas que representan a cada etapa de un PLL

lineal, se procede hora a la implementación del algoritmo de cada una de ellas.

3.1. Señal de Entrada.

La señal de entrada u1(t) es una señal senoidal y será muestreada periódicamente a una

frecuencia fs=1/T mediante un convertidor analógico-digital (ADC), donde T es el intervalo de

muestreo. Estas muestra serán tomadas en los tiempos t=0, T, 2T, 3T,...nT. En este caso u1(t) se

denota por u1(n), que es la notación simplificada para u1(nT). Las otras señales que intervienen en

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

un SPLL también son señales muestreadas. Consecuentemente todos los bloques que conforman

este sistema, están sincronizados con el reloj del ADC. De acuerdo con el teorema de muestreo, el

algoritmo del SPLL debe ser ejecutado dos o, aún mejor, cuatro veces la frecuencia de la señal de

3

entrada.

Figura 5. Modelo del PLL lineal considerando las fases θ1 y θ2.

3.2. DCO

La implementación por software del VCO se hará por medio de un Oscilador Controlado

Digitalmente (DCO). El DCO es el encargado de generar la señal de salida de onda cuadrada u2(t).

Esta señal solamente está presente en cada instante de muestreo, así que u2(n) representa la

señal de salida muestreada y esta definida por Ec. (6). La fase total φ2 es empleada para

determinar el valor instantáneo de la señal de salida u2(n). Como

∆t = (n + 1)T − nT = T (28)

De Ec. (19) se obtiene el siguiente algoritmo para φ2

[ ]

∆φ = φ 2 (n + 1) − φ 2 (n) = ω o + K o u f (n) T (29)

Se observa que si se conoce la fase en el tiempo nT, es posible saber el valor para (n + 1)T. Este

algoritmo es posible debido se puede inicializar la fase total φ2(n=0) a cero antes de que el proceso

de inicio De aquí, es posible extrapolar φ2(1) en el tiempo t=0.T, t=1.T, t=2.T, etc. El DCO no es

capaz de generar por si mismo la señal u2(n); esta señal será calculada de manera indirecta por

medio de la señal de fase φ2(n). Es posible obtener u2(n+1) a partir de φ2(n+1) aprovechando la

definición dada por la función Walsh mediante el algoritmo dado por Ec. (30)

u 2 (n + 1) = 1 si 2πk ≤φ 2 (n + 1) < (2k + 1)π (30a)

(30b)

u 2 (n + 1) = −1 si (2k − 1)π ≤φ 2 (n + 1) < 2kπ k es entero

3.3. Detector de Fase

El algoritmo del detector de fase puede ser obtenido a partir de Ec. 10. En el instante de muestreo

nT, la señal de salida ud(n) se obtiene a partir de

u d (n) = K d u1 (n)u 2 (n) (31)

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Figura 6. Diagrama de Bode de la función de transferencia H(s).

Figura 7. Diagrama de Bode de la función de transferencia.

Ec. (31) es realizable ya que u2(n) ha sido inicializada y u1(n) es tomada del ADC. La ganancia Kd

es fijada de acuerdo a las necesidades del sistema.

3.4. Filtro de lazo PI

Para obtener la función en el tiempo discreto de la función de transferencia de este filtro, dada por

Ec. (15), se requiere conocer la función de transferencia H(z). Para obtener la función de

transferencia en el dominio de la variable z, se debe realizar la transformada bilineal, ya que se

debe realizar el mapeo de s correspondiente a z, por lo tanto, partiendo de la expresión

2 1 − z −1

s=

T 1 + z −1 (32)

z=e

sT

con (33)

se obtiene

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

−1

U f ( z) bo + b1 z (34)

H ( z) = =

U d ( z) 1 + a1 z −1

donde

a1 = −1 (35)

T 1

bo = 1 +

tan (T / 2τ 2 )

2τ 1

T 1

b1 = 1 −

2τ 1 tan (T / 2τ 2 )

Para pasar al dominio del tiempo, habrá que recordar que un corrimiento en el tiempo continuo se

hace presente en el dominio de la frecuencia mediante

− as (38)

f (t − a ) → e F (s)

Donde a representa el corrimiento en el tiempo. Un corrimiento en el tiempo discreto estaría

-1 -sT -1

representado por a= nT. Puesto que z =e , según Ec. (33), la multiplicación por z en el dominio

de z, representaría un corrimiento por un periodo de muestreo T en el dominio del tiempo. De

acuerdo con lo anterior

z − n F ( z ) → f (t − nT ) (39)

Convirtiendo al dominio del tiempo discreto Ec. (37) se obtiene la expresión recursiva para el filtro

u f (t ) = − a1 + bo u d (n) + b1u d (n − 1) (40)

4. IMPLEMENTACIÓN DEL ALGORITMO DEL SPLL

Para derivar el algoritmo deseado, primero se ha planteado un diagrama de flujo para mostrar las

definir la secuencia que las señales deben. Este diagrama se muestra en la Figura 8. Como se ve,

existen tres bloques básicos: un multiplicador digital, un filtro digital y un DCO. El multiplicador es

usado como detector de fase,. El filtro digital sirve como el filtro de lazo y finalmente el DCO

genera una onda cuadrada que deberá estar sincronizado tanto en fase como en frecuencia con la

señal de entrada.

De acuerdo con el flujo de la señal en la Figura 8, el planteamiento del algoritmo desarrollado es el

mostrado en la Figura 9. Se supone que la señal de muestreo cuenta con un reloj que

periódicamente proporcionara la señal de interrupción para iniciar cada ciclo de ejecución. Estas

interrupciones deben de presentarse en t=T, 2T, 3T,..., nT. Tan pronto como la señal de

interrupción es reconocida, el algoritmo del SPLL es ejecutado y se toma una muestra de la señal

de entrada. Cuando todos lo cálculos han sido realizados, las variables deben de ser retrasadas

en el tiempo. Esto se consigue almacenando en una variable el valor actual de la variable en

cuestión y emplearla como el valor pasado en la próxima iteración.

Cuando el algoritmo es ejecutado por un largo periodo de tiempo el valor de φ2(n+1) se volverá

muy grande y podría exceder el rango permitido de punto flotando del procesador empleado. Para

evitar un sobre flujo aritmético, el rango de φ2 puede ser limitado dentro del rango

− π ≤ φ2 < π (41)

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Figura 8. Diagrama a bloques del SPLL mostrando las operaciones a ser ejecutas en cada etapa.

Para limitar a φ2 dentro del limite dado, siempre que el valor de φ2(n+1) exceda π, se le resta 2π. El

nuevo valor de u2(n+1) es computado checando el signo del resultado de la resta anterior con lo

que

u (n + 1) = 1

2 si φ (n + 1) ≥ 0

2

(42)

Por último, hay que recalcar que para implementar un LPPL por software, la frecuencia de

muestreo fs debe ser al menos cuatro veces la frecuencia de la señal de entrada con el fin de evitar

aliasing (cruce de bandas de frecuencia) en el espectro de la señal dada la naturaleza de la señal

al hacer un muestreo.

5. IMPLEMENTACIÓN EN LENGUAJE C DE ALGORITMO DEL PLL POR SOFTWARE

. El lenguaje elegido a sido C, por su gran cercanía a un lenguaje de bajo nivel pero con la

característica de poder realizar rutinas poderosas de manera sencilla. Para mayor facilidad, se creo

5

una interfaz basada en C Builder4. Esta interfaz permite la entrada de valores como kd, ko,

frecuencia de muestreo (fs), frecuencia de la señal de entrada (f1). En base a estos valores se

realiza el cálculo de los coeficientes del filtro digital con un valor para ζ=0.707. La Figura 10

muestra la interfaz realizada y los resultados de una corrida del programa. Lla Figura 11 muestra

las diferentes formas de onda que se observan en este tipo de PLL.

6. CONCLUSIONES.

Hasta ahora se ha desarrollado un SPLL en lenguaje C que realiza las misma funciones que un

LPLL implementado con Hardware. Las limitaciones del tipo de implementación hecho en lenguaje

C es la carencia de una prueba física, ya que no es posible ni factible económicamente emplear

todo una computadora para ejecutar las instrucciones necesarias. Sin embargo, es muy útil para

llevar a cabo simulaciones del comportamiento de LPLL que se intentarán implementar en

hardware con el fin de prevenir ciertas fallas o determinar rangos de trabajo de los mismos en base

a los valores de sus parámetros (kd, ko, y ω1,) y del tipo de filtro que se quiera implementar.

Algo que también hay que tomar en cuenta, es la limitante en frecuencia. De acuerdo con el

teorema de muestreo, el algoritmo del SPLL debe ser ejecutado dos veces, o aún, cuatro veces en

cada ciclo de la señal de referencia. Si la frecuencia de referencia es de 100 KHz, por ejemplo, el

algoritmo debe de ejecutarse de manera completa 2,000,000 veces por segundo. Por otro lado,

conforme las funciones se hacen más sofisticadas, el número de instrucciones se ven

incrementadas, lo que nos lleva a disminuir la frecuencia de operación del SPLL. El siguiente paso

a desarrollar es la implementación de este algoritmo es un dispositivo programable y de preferencia

empleando lenguaje VHDL.

Los algoritmos que se han desarrollado en este trabajo pueden ser usados como base para la

implementación del LPLL en cualquier dispositivo programable con tan solo traducirlos al

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

respectivo lenguaje. Así mismo, la metodología presentada pude ser útil como guía para

implementar otros tipos de PLL.

Figura 9. Diagrama de flujo del algoritmo del LPLL.

Figura 10. Interfaz y graficas de las diferentes señales que intervienen en el SPLL

CONGRESO NACIONAL DE INSTRUMENTACION

SOMI XV

Ele – 24 - 1

Durante el desarrollo del presente trabajo se obtuvo información sobre ciertos

microcontroladores fabricados por SCENIX. La opción que este fabricante propone es el

empleo del SX52BD, que cuenta con una característica única comparada con otros

microcontroladores de su tipo: realiza una instrucción por ciclo y puede trabajar hasta 100

MHz. Esto nos proporciona mayor rapidez, menor tiempo de ejecución de una iteración y por lo

tanto un rango de frecuencia de trabajo más elevado comparado con cualquier otro dispositivo

de bajo costo disponible en el mercado. Esta propuesta se ha adoptado como una segunda

opción para implementar de manera física el PLL propuesto.

Figura 11. Señales que tienen que ser calculadas por el algoritmo del SPLL.

Referencias.

BEST, Roland E. PHASE LOOK LOOPS.. Edit. McGraw Hill. USA 1993 [1]

HSU, Hwei P. Análisis de Fourier. Addison-Wesley Iberoamericana. USA, 1987 [2]

HAYKIN, Simon, AN INTRODUCCTION TO ANALOG AND DIGITAL COMMUNICATIONS.

Edit. Jhon Wyley & Sons. USA. 1989. [3]

YANG, Lewis, Sistemas de Control en Ingeniería.Edit. prentice Hall. España.1999 [4]

Inprise Corporation. Borland C++ Builder. Versión 4.0 Copyright 1983-1999 [5]

CONGRESO NACIONAL DE INSTRUMENTACION

Вам также может понравиться

- Texcom 2Документ85 страницTexcom 2aymara santanaОценок пока нет

- Problema de Coca-ColaДокумент32 страницыProblema de Coca-ColaAimee MizraimОценок пока нет

- Guia Un1Документ20 страницGuia Un1Damian PalomanesОценок пока нет

- 2011 1 Parcial TresДокумент1 страница2011 1 Parcial TresSebastian VasquezОценок пока нет

- Teorema de NisquisДокумент73 страницыTeorema de NisquisPaulo CamposОценок пока нет

- Tarea 2 ConvoluciónДокумент15 страницTarea 2 ConvoluciónEdwin LarrahondoОценок пока нет

- Plantilla Informe LaboratorioДокумент4 страницыPlantilla Informe Laboratoriojuan pabloОценок пока нет

- Parcial 2 SeñalesДокумент5 страницParcial 2 SeñalesAndres GenoyОценок пока нет

- Aplicaciones de Las SeriesДокумент11 страницAplicaciones de Las SeriesjjphОценок пока нет

- TL00304CДокумент40 страницTL00304CEdwin4321Оценок пока нет

- PLLДокумент50 страницPLLMiguel Angel Giraldo NoguesОценок пока нет

- Actividad Analisis de SistemasДокумент2 страницыActividad Analisis de SistemasYesid PeñaОценок пока нет

- Operaciones Básicas de Señales y Sistemas Continuos y DiscretosДокумент9 страницOperaciones Básicas de Señales y Sistemas Continuos y DiscretosNixon RojasОценок пока нет

- (PDS) Lab 05 DTFT 19 IIДокумент12 страниц(PDS) Lab 05 DTFT 19 IIjaneth rodriguez0% (1)

- Feb 05 SolДокумент10 страницFeb 05 SolArnulfo OrtizОценок пока нет

- Transformada ZДокумент11 страницTransformada ZAlex Mendez NavarroОценок пока нет

- Tema LaplaceДокумент21 страницаTema LaplaceRobertoGarciaОценок пока нет

- Practica Convergencia Serie FourierДокумент5 страницPractica Convergencia Serie Fouriercarlo espinoza fabian100% (1)

- 21506-14 TECNOLOGIA DE CONTROL Función TransferenciaДокумент15 страниц21506-14 TECNOLOGIA DE CONTROL Función TransferenciaRene RomeroОценок пока нет

- Plantilla Formato iEEEДокумент4 страницыPlantilla Formato iEEEandrea contrerasОценок пока нет

- Tarea 1 - Señales y Sistemas - Trabajo ColaborativoДокумент63 страницыTarea 1 - Señales y Sistemas - Trabajo ColaborativoJose Eduardo Garcia CamargoОценок пока нет

- 006 Práctica de Laboratorio JPRRДокумент11 страниц006 Práctica de Laboratorio JPRRjeanОценок пока нет

- Tarea 1 - Señales y SistemasДокумент6 страницTarea 1 - Señales y SistemasJose Eduardo Garcia CamargoОценок пока нет

- Reporte # 2 Señales y Sistemas Discretos en El TiempoДокумент16 страницReporte # 2 Señales y Sistemas Discretos en El Tiempodelgadito99 delgatoОценок пока нет

- Simulacion 1Документ10 страницSimulacion 1Santiago SanchezОценок пока нет

- 1 IntroduccionДокумент100 страниц1 IntroduccionJavier MejiaОценок пока нет

- Problemario de Analisis de Señales y SistemasДокумент4 страницыProblemario de Analisis de Señales y SistemasAlfredo RosasОценок пока нет

- PLLsДокумент87 страницPLLsErik VRОценок пока нет

- Capa Física - Bases Teóricas - Redes y TelecomunicacionesДокумент6 страницCapa Física - Bases Teóricas - Redes y Telecomunicacionesproyecto 2023Оценок пока нет

- Modulación y Demodulación PSK y QPSKДокумент22 страницыModulación y Demodulación PSK y QPSKfabrizzioОценок пока нет

- Senales y Sistemas II RepasoДокумент2 страницыSenales y Sistemas II RepasoSebastian GilОценок пока нет

- Examen Extraordinario de Analisis de Sistemas y Señales Ago 2021Документ8 страницExamen Extraordinario de Analisis de Sistemas y Señales Ago 2021Joel RamirezОценок пока нет

- Preguntas SeñalesysistemasДокумент4 страницыPreguntas SeñalesysistemasBrendal Molina100% (2)

- Sistemas de Modulacion I 24-03-2015Документ37 страницSistemas de Modulacion I 24-03-2015Andy VillasantiОценок пока нет

- Lab 2 Control II (Trans Z)Документ6 страницLab 2 Control II (Trans Z)Jose Antonio Sanchez PinilloОценок пока нет

- Taller SimscapeДокумент16 страницTaller Simscapedaniel tovarОценок пока нет

- Sistemas de Comunicaciones ProakisДокумент156 страницSistemas de Comunicaciones ProakisGabrielОценок пока нет

- La Transformada Rápida de FourierДокумент24 страницыLa Transformada Rápida de FourierDoom FletcherОценок пока нет

- Práctico 4 2020 Aplic de T Fourier Introd T LaplaceДокумент3 страницыPráctico 4 2020 Aplic de T Fourier Introd T Laplacejael molina huancaОценок пока нет

- Analisis Sistemas RosasДокумент8 страницAnalisis Sistemas RosasAlfredo RosasОценок пока нет

- Clase Martes 22 de FebreroДокумент31 страницаClase Martes 22 de FebreroBrenis Mateo DiegoОценок пока нет

- Presencial Serie FourierДокумент4 страницыPresencial Serie FouriersebastianОценок пока нет

- FiltrosДокумент29 страницFiltrosadrianОценок пока нет

- LABORATORIO 04 y 05 Transformada Z y Fourier AluДокумент12 страницLABORATORIO 04 y 05 Transformada Z y Fourier AluKarolaym Julieth Ruiz TorresОценок пока нет

- Trabajo Final de Series y TransformadasДокумент17 страницTrabajo Final de Series y TransformadasRoberto Mori100% (1)

- Tarea 3. Analisis en El Dominio Del Tiempo - Nicolas AlvarezДокумент15 страницTarea 3. Analisis en El Dominio Del Tiempo - Nicolas AlvarezVBiomedica SASОценок пока нет

- Matematica Iii - Resolucion de Ejercicios - Sesion 14 - Grupo #02Документ7 страницMatematica Iii - Resolucion de Ejercicios - Sesion 14 - Grupo #02Chris stefany Alvarado CheroОценок пока нет

- Convolucion Correlacion Ortogonalidad Abril 2011Документ49 страницConvolucion Correlacion Ortogonalidad Abril 2011MarialeCuestas02Оценок пока нет

- Labscontiii Pre1 Ygonzalez 20185248 20-9-2021Документ3 страницыLabscontiii Pre1 Ygonzalez 20185248 20-9-2021Elvis CarrascoОценок пока нет

- La Transformada Rápida de FourierДокумент24 страницыLa Transformada Rápida de FourierJorge Arturo Rodriguez BadilloОценок пока нет

- Comunicacion 2Документ7 страницComunicacion 2Pepe GlezОценок пока нет

- La Transformada Rápida de Fourier PDSДокумент24 страницыLa Transformada Rápida de Fourier PDSFredy AlbornozОценок пока нет

- Resumen SistemasДокумент74 страницыResumen Sistemasjose.bailen03Оценок пока нет

- Cap1 NOCIONES SOBRE MUESTREO Y RECONSTRUCCIÓN DE SEÑALES.Документ10 страницCap1 NOCIONES SOBRE MUESTREO Y RECONSTRUCCIÓN DE SEÑALES.ijalvaОценок пока нет

- Funcion de TransferenciaДокумент24 страницыFuncion de TransferenciaSergio Zuniga QuispeОценок пока нет

- Sesión 4-Discretizacion PDFДокумент4 страницыSesión 4-Discretizacion PDFgorkantolinprraОценок пока нет

- Series de FourierДокумент10 страницSeries de FourierDANIEL ONASIS BAÑOS FIGUEROAОценок пока нет

- Introduccion A UMTSДокумент26 страницIntroduccion A UMTSJulio HuayhuamezaОценок пока нет

- MPH Final ES-LA With LinksДокумент48 страницMPH Final ES-LA With LinksJosué JmlОценок пока нет

- Manual Basico Telefonia TradicionalДокумент117 страницManual Basico Telefonia TradicionalbuyesyohanОценок пока нет

- Cdma Principios BasicosДокумент70 страницCdma Principios BasicosJosué JmlОценок пока нет

- Dispersion Por Modo Polarizacion-EspДокумент3 страницыDispersion Por Modo Polarizacion-EspJosué JmlОценок пока нет

- Pasos A Seguir para Hacer Un Trabajo de InvestigacionДокумент3 страницыPasos A Seguir para Hacer Un Trabajo de InvestigacionJosué JmlОценок пока нет

- Protocolo CIPДокумент20 страницProtocolo CIPJosué JmlОценок пока нет

- Macros para WarriorДокумент3 страницыMacros para WarriorJosué JmlОценок пока нет

- Robotica Pic Basic Stamp Micro Control Adores SpanishДокумент114 страницRobotica Pic Basic Stamp Micro Control Adores Spanishhugo_valles_2Оценок пока нет

- Algoritmos Geométricos Marco TeóricoДокумент24 страницыAlgoritmos Geométricos Marco TeóricoArthur Arizzmendii100% (1)

- ICONIXДокумент17 страницICONIXYuri BarzolaОценок пока нет

- Actividad 13 de InformaticaДокумент6 страницActividad 13 de InformaticaMarcos Daniel EscamillaОценок пока нет

- Parametros Por Valor Referencia y RecursividadДокумент16 страницParametros Por Valor Referencia y RecursividadPaula Mariana FuentesОценок пока нет

- DSM Actividad 1Документ1 страницаDSM Actividad 1AlbertoОценок пока нет

- Manual para Reparar Windows XP Que No ArrancaДокумент4 страницыManual para Reparar Windows XP Que No ArrancaAna Milena Tarra Reyes0% (1)

- Protocolo PS7Документ31 страницаProtocolo PS7carlos mejia50% (2)

- Diagrama de ComponentesДокумент6 страницDiagrama de ComponentesRockwell David Clemente100% (1)

- Manual Parametrizacion Workflow MMДокумент11 страницManual Parametrizacion Workflow MMdf_maldonadoОценок пока нет

- Exposición COM DCOMДокумент7 страницExposición COM DCOMGabriela MtzОценок пока нет

- Actividad - Introducción A JavaScriptДокумент2 страницыActividad - Introducción A JavaScriptJennyk TorresОценок пока нет

- Reconocimiento de Imágenes Utilizando Redes Neuronales ArtificialesДокумент72 страницыReconocimiento de Imágenes Utilizando Redes Neuronales ArtificialesProgramando JavaОценок пока нет

- psp-0 1Документ18 страницpsp-0 1Luis Fernando Hernandez ReynosoОценок пока нет

- Matlab en El Análisis y Simulación de Sistemas de PotenciaДокумент30 страницMatlab en El Análisis y Simulación de Sistemas de PotenciaLuis AlexisОценок пока нет

- CronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidДокумент10 страницCronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidHarold Stiven Amaya VillamilОценок пока нет

- Clases AbstractasДокумент8 страницClases AbstractaseddyОценок пока нет

- Arquitectura de ComputadorasДокумент30 страницArquitectura de Computadorashicaro_112550% (2)

- Newton Sistemas No LinealesДокумент6 страницNewton Sistemas No LinealesWeroHerreraОценок пока нет

- Guia de Imagej para MicrosДокумент24 страницыGuia de Imagej para MicrosMariuGmОценок пока нет

- UTF 8 EstructuraDeDatos PDFДокумент11 страницUTF 8 EstructuraDeDatos PDFdeawrfОценок пока нет

- Apuntes MySql.Документ36 страницApuntes MySql.Hugo Sanchez ZaguiñoОценок пока нет

- Guia 001 Practica UMLДокумент8 страницGuia 001 Practica UMLAlbita CaminoОценок пока нет

- Visual FoxPro y Sql-ServerДокумент16 страницVisual FoxPro y Sql-ServerJorge Luis Lopez PinedaОценок пока нет

- Windows - 3.1 - Instalacion y Administracion de ArchivosДокумент27 страницWindows - 3.1 - Instalacion y Administracion de ArchivosdiegoОценок пока нет

- GUIA 6 Tecnologia 1, 2 y 3 SemanaДокумент10 страницGUIA 6 Tecnologia 1, 2 y 3 SemanaFelix Andres MorenoОценок пока нет

- Robo CellДокумент2 страницыRobo CellRobert SmithОценок пока нет

- Electrónica - Tarea 6Документ3 страницыElectrónica - Tarea 6Luis MoraОценок пока нет

- Folleto Historia de La ComputacionДокумент1 страницаFolleto Historia de La ComputacionEINERDY NETОценок пока нет

- Caso Estudio - Control de Parking RfidДокумент2 страницыCaso Estudio - Control de Parking RfidantonioherediaОценок пока нет

- Cocomo I y IiДокумент3 страницыCocomo I y IiEmmanuel MaciasОценок пока нет