Академический Документы

Профессиональный Документы

Культура Документы

Scaling Si To 10nm

Загружено:

Lewis HarperИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Scaling Si To 10nm

Загружено:

Lewis HarperАвторское право:

Доступные форматы

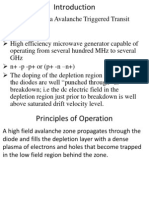

REVIEW

Silicon Device Scaling to the

Sub-10-nm Regime

Meikei Ieong,1* Bruce Doris,2 Jakub Kedzierski,1 Ken Rim,1 Min Yang1

channel transistors. This source, substrate,

In the next decade, advances in complementary metal-oxide semiconductor fabrication and drain doping effectively produces two

will lead to devices with gate lengths (the region in the device that switches the current back-to-back junction diodes from the source

flow on and off) below 10 nanometers (nm), as compared with current gate lengths in terminal to the drain terminal. When a suf-

chips that are now about 50 nm. However, conventional scaling will no longer be ficiently large positive voltage is applied to

sufficient to continue device performance by creating smaller transistors. Alternatives the gate of an N-channel transistor (which

that are being pursued include new device geometries such as ultrathin channel struc- creates an electric field, hence the field ef-

tures to control capacitive losses and multiple gates to better control leakage pathways. fect), the silicon surface is ‘‘inverted’’—the

Improvement in device speed by enhancing the mobility of charge carriers may be ob- conduction band is populated and forms a

tained with strain engineering and the use of different crystal orientations. Here, we narrow conducting layer between the source

discuss challenges and possible solutions for continued silicon device performance trends and the drain. If there is a voltage difference

down to the sub-10-nm gate regimes. between the source and the drain, an electric

current can flow between them. When the

T

he steady reduction in the minimum 10 nm (1). We discuss below the challenges gate voltage is removed or set at zero volt-

feature size in integrated circuits has in device scaling and possible solutions in age, the surface region under the gate is

helped the microelectronic industry to maintaining the performance trend. depleted with electric carriers and there is no

produce products with spectacular increase in current flow between the source and the

computational capability and integration den- MOSFETs: The Building Blocks drain. We can therefore see that the current

sity at lower cost. Smaller transistors operate The MOSFET, or metal oxide semiconductor flowing through the structure can be regulat-

faster than larger ones, and for a given chip field-effect transistor, is a fundamental ed by applying voltage to the gate electrode.

technology, the cost

of a chip decreases

with area rather than B C

A Scaled Device

with the number of

transistors. Voltage, V/α

The exponential ed

tox/α pe

ctive

s

Gate delay

scaling trend surely SCALING e

as

Pa

will eventually hit Voltage: V/α re

GATE Vt In

c

uce

fundamental limits, Oxide: tox/α

Red

but the many predic- n+ source n+ drain

Gate Length: L/α

tions of a near-term Diffusion: xd/α e P standby

end of device scaling Substrate: α*NA Reduc

have proven too pes- L/α

xd/α Vt Vdd Vdd

simistic. With the

introduction of the p substrate, doping α*NA

production of 90-nm

node technology in

2004, the semicon- Fig. 1. (A) Schematic of MOSFET indicating various relevant device scaling parameters. (B) Complementary metal-oxide

ductor industry is en- semiconductor (CMOS) inverter gate delay as a function of power-supply voltage (Vdd). Gate delay rapidly increases as Vdd

tering the Bnano[ era approaches the threshold voltage (Vt). (C) Design space for supply and threshold voltages for optimum performance and

power dissipation. Technology scaling diminishes this design space.

(1). (The B90-nm

node[ refers to the

smallest half-pitch metal lines available in the switching device in very-large-scale integrat- A MOSFET can be used either as an elec-

technology. The actual gate lengths of the de- ed (VLSI) circuits. A MOSFET (Fig. 1A) trical switch or as an amplifier. The majority

vices are about 50 nm.) In the next decade, has at least three terminals, which are des- of MOSFETs on an integrated circuit today

device gate lengths will be scaled to below ignated as gate, source, and drain. The gate are used as electrical switches. How fast a

electrode is separated electrically from the MOSFET can be switched on and off is

1

IBM Semiconductor Research and Development source and the drain by a thin dielectric film, therefore a critical figure of merit to deter-

Center, T. J. Watson Research Center, Yorktown

2

Heights, NY 10598, USA. IBM Semiconductor Re-

usually silicon dioxide. The source and the mine the competitiveness of the technology.

search and Development Center, Microelectronic drain are doped with impurities that are op- The two major factors that control the speed

Division, Hopewell Junction, NY 12533, USA. posite in polarity to the substrate, which is of MOSFETs are the channel length from

*To whom correspondence should be addressed. doped with boron for N-channel transistors the source to the drain and the speed at which

E-mail: mkieong@us.ibm.com and with arsenic or phosphorous for P- channel charge carriers travel from the source

www.sciencemag.org SCIENCE VOL 306 17 DECEMBER 2004 2057

REVIEW

to the drain. We will discuss these two fac- (SCE). According to the scaling theory of constant are needed. It is also difficult to pro-

tors in more detail below. Dennard (2), the vertical dimensions (gate- duce an extremely shallow and abrupt junction

oxide thickness, junction depth, and depletion without increasing the external resistance.

Shrinking the Transistor width) must be scaled down with the lateral (Junction resistance is inversely proportional

Shrinking transistors not only packs more dimensions such as gate length. This theory to junction depth.)

devices into a given area but also shortens the guarantees appropriate electrostatic character- Ion implantation has been the dominant

distance between source and drain, or the gate istics when a larger device is scaled down to process for the creation of shallow junctions. A

length, which can improve the switching a smaller one (Fig. 1A). The industry has high-temperature annealing process is needed

speed. The two challenges in to repair the damage to the

decreasing MOSFET size are single crystal and to activate

fabrication and maintaining the dopant atoms. During this

performance. The backbone step, diffusion and redistribu-

of MOSFET fabrication is a tion of dopant atoms occur. A

process called lithography, high-temperature, short time

which resembles the printing scale annealing process is

of a photograph by shining more desirable to produce

light through a negative onto shallow and abrupt junctions.

a photosensitive surface. Li- A near-zero thermal-budget

thography allows complex junction technology, such as

patterns to be created through millisecond flash-lamp and la-

a series of printing and etch- ser annealing, will be required.

ing steps. The ability to print Finally, the increase in

ever-smaller fine lines is channel doping needed for

mandatory for continued de- SCE control will substantial-

vice scaling. Advanced photo- ly increase the junction ca-

lithography techniques have pacitance and leakage. All of

enabled the industry to keep these changes degrade de-

pace with the demand im- vice performance. The prob-

posed by increasingly smaller Fig. 2. Device schematics and cross sections for (A) SOI MOSFET, (B) UTSOI lem is exacerbated by the

structures. However, the MOSFET, and (C) FinFET double-gate MOSFET. ‘‘nonscaling’’ factors that

smallest feature size is re- arise when the traditional

lated to the fundamental MOSFET design is scaled.

limit of wavelength used in

conventional optical lithog- Nonscaling Factors

raphy. Alternative technol- As pointed out above, sev-

ogies capable of writing eral factors do not scale as

features far smaller than we shrink MOSFETs. The

those produced by conven- subthreshold nonscaling issue

tional optics have also been is the most fundamental one

demonstrated and include (3). A MOSFET is turned on

the use of extreme ultravio- when a sufficiently high volt-

let (EUV) radiation, x-rays, age is applied to the gate.

and electron beams. Re- The voltage above which the

cently, the self-assembly MOSFET is turned on is

process has attracted much loosely defined as threshold

attention because of its po- voltage. The leakage current

tential in producing nano- in the off state depends ex-

scale patterns. The concern ponentially on the threshold

is whether any of these al- voltage. Ideally, one would

ternatives can be scaled up keep the threshold voltage

to meet the throughput, con- high to minimize the power

trol, and cost requirements Fig. 3. Device cross sections for (A) strained silicon on insulator (SGOI), (B) strained consumed when the device

for manufacturing. silicon directly on insulator (SSDOI), and (C) hybrid-orientation technology (HOT). is off (the stand-by power)

Given the ability to cre- and to ensure an appropri-

ate smaller device features, ate noise margin. The sup-

to what extent can the gate length be re- been by and large following this scaling ply voltage is usually reduced in device

duced before the MOSFET ceases to func- guideline for shrinking MOSFETs to gain scaling to keep the active power manageable

tion as a switch? The gate terminal can lose higher density and speed without degrading and to ensure reliability. However, higher

the control of channel electric carriers when reliability and power. device performance will require as much

the source and the drain are brought into The accelerated gate-length scaling in the gate overdrive (the excess voltage applied

proximity without scaling other device pa- past decade has pushed many vertical device above the threshold) as possible, because

rameters. Eventually, the gate terminal can- parameters to their fundamental or techno- higher driving voltages lead to faster switch-

not turn off the devices, and transistor action logical limits. For example, gate oxide now ing. Figure 1B shows the circuit delay as

can no longer be observed. This phenom- consists of only a few atomic layers; alterna- a function of supply voltage, Vdd. Perform-

enon is the so-called short-channel effect tive gate materials with a higher dielectric ance can only be maintained by keeping

2058 17 DECEMBER 2004 VOL 306 SCIENCE www.sciencemag.org

REVIEW

threshold voltages low, but the threshold tension should be designed to minimize loss SOI channels could be a fundamental issue.

voltage cannot be scaled down much without of dopant dose and to avoid complete amor- The channel mobility is substantially reduced at

causing a substantial increase in leakage cur- phization of the silicon layer by the ion im- SOI thicknesses below 10 nm. This decrease

rent in the off state. The proper choice of plantation process. A thin gate spacer coupled may be caused by a ‘‘surface roughness’’–like

Vdd and threshold voltage for best per- with the raised-source-drain process has been scattering mechanism that results from the

formance and power tradeoff depends on the shown to be effective in minimizing external perturbation of band potential by variations

application. The design window rapidly dimin- resistance without compromising parasitic in the SOI layer thickness (10).

ishes as technology is scaled down (Fig. 1C). capacitance. With this new process scheme, The ultrathin SOI thickness requirement for

In addition, the aggressive reduction in gate improved drive currents were realized (9). SCE control in single-gate FETs can be relaxed

dielectric has also caused exponential in- Setting and controlling the threshold volt- by using a more complex ‘‘double-gate’’ FET

crease in gate leakage. age in devices with such thin SOI layers is also that offers improved electrostatic gate control

Together, these effects have caused of the body. There are many review ar-

the so-called power crisis in the silicon ticles on double-gate devices (11–13).

chip industry. Power management has The symmetric nature in a double-gate

Gate

now become the number one issue in Z FET reduces the depletion width by 50%

any high-performance and low-power compared with that of a single-gate

application. Currently, there is a con- structure. In addition, there is no drain-

Source Drain

sensus that maintaining the device to-body fringing field through the buried

performance trend with conventional STI

oxide (BOX) (Fig. 2A) in a double-gate

device scaling technique is extremely Desired Stress: structure. Numerical simulations indicate

Transverse

challenging, if possible at all. New Tran. Long. Z that scalability for double-gate FETs

Gate

device structures and materials will be Source Drain

pFET T C T improves by a factor of 2.5 to 3 (5). Be-

needed to sustain the current rate of nFET T T C

cause the double-gate device operates

progress in device technology. at much lower vertical electric fields,

T: Tensile stress the mobility requirement in double-gate

C: Compressive stress

Possible Solutions for Longitudinal devices can be lower than that of con-

Device Scaling Fig. 4. Possible directions of uniaxial stresses and their effects ventional planar MOSFETs (14).

Circuit performance can be improved on N-channel and P-channel MOSFETs. Double-gate FETs can be fabricated

by building conventional MOSFETs on in planar (14, 15), vertical (16), and

a silicon-on-insulator (SOI) substrate finlike (17–19) structures. Of all the

(Fig. 2A). The insulator layer can be Conduction band Unstr. Si Strained Si double-gate device structures, the FinFET

created by implanting oxygen ions and ∆2 valleys ∆4 m is the simplest to implement. The body

then annealing the layer to form an ∆6 l of a FinFET device consists of a vertical

oxide. The addition of an oxide layer Ec crystalline silicon wall (Fig. 2C). The

below the transistor junction SOI layer gate wraps around both sides of the fin

can effectively reduce the junction ∆ mt and creates a channel on each side of

capacitance and leakage current. It ∆4 valleys ml 2

the fin. In a FinFET, the two channels

also eliminates the so-called ‘‘reverse mt mt < ml are perpendicular to the wafer surface

body effect’’ (4) in stacked circuits. As and the current direction is parallel to

mt

a result, SOI technology offers a faster the wafer surface. High current has been

circuit and consumes less power. Valence band demonstrated when the FinFET struc-

Ultrathin SOI (UTSOI) MOSFET is ture is combined with a raised-source-

Bulk Si E Strained Si E

an attractive option for device scaling, drain process.

because it can effectively reduce the SCE out-of-

and eliminate most of the leakage plane Enhanced Mobility: Making

paths (5–7). For thicker SOI channels, HH k meV k Carriers Travel Faster

∆E 38

the drain field could easily penetrate to 10%Ge Mobility enhancement is an attractive

the source side through the channel or LH option, because it can potentially im-

buried oxide when the gate length is prove device performance beyond any

reduced. However, a thin SOI channel Spin-orbit of the benefits from device scaling.

can resolve this problem. Based on this The two main approaches being pursued

Fig. 5. Biaxial stress effects on the conduction and valence

concept, a functional transistor with a bands of strained silicon. are strain engineering (both process-

gate length of 6 nm was demonstrated induced and substrate-induced) and ori-

(Fig. 2B) by using an ultrathin channel entation effects (Fig. 3).

of 4 to 8 nm and aggressive ‘‘halo’’ (8) im- quite challenging. Conventional doping schemes Strain engineering. Strain effects induced

plantation (6). This extremely small silicon may not be effective as a result of doping during the fabrication process can increase the

MOSFET was functional, but its device drive fluctuation. One attractive process option is channel mobility. Both tensile and compres-

current suffered from channel mobility degra- to completely ‘‘silicide’’ the polycrystalline- sive stresses can be introduced in any one of

dation and high external resistance. silicon gate stack by converting the polysili- the three dimensions by process techniques

The integration of ultrathin SOI channels con to a metal silicide. The gate work function (20–27). The electron and hole mobility re-

into the conventional MOSFET process is can be adjusted over a substantial range by spond differently to uniaxial stresses (Fig. 4).

quite challenging. The gate and spacer mod- alloyed silicide and ion implantation to the The most effective way to introduce high

ules must be carefully designed to prevent gate before silicidation (7). Although the ex- tensile strain to the channel is to epitaxially

substantial silicon consumption. The ion im- ternal resistance can be reduced by process grow strained silicon on a relaxed silicon ger-

plantation process for the source/drain ex- improvement, the mobility degradation in thin manium (SiGe) layer. Because of the lattice

www.sciencemag.org SCIENCE VOL 306 17 DECEMBER 2004 2059

REVIEW

mismatch between silicon and SiGe, the lat- tage of the carrier mobility dependence on ent crystal orientations are promising methods

tice of the silicon layer is stretched (strained) surface orientation, a new technology has been for mobility enhancement. In fact, some form

in the plane of the interface. This deformation developed to fabricate complementary metal- of strained-silicon techniques are already being

breaks the symmetry of the energy-band struc- oxide semiconductor (CMOS) on hybrid sub- used in silicon integrated-circuit manufactur-

ture and results in band splitting (Fig. 5). The strates with different crystal orientations, with ing. Some scaling and mobility-enhancement

reduced interband/intervalley scattering and NFETs on silicon of (100) surface orientation options can be combined for even higher per-

effective masses result in enhanced carrier and PFETs on (110) surface orientation (31). formance gains. One example that integrates

transport in the strained-silicon layer that is In this hybrid-orientation technology (HOT), both UTSOI and FinFET devices on the same

used as the channel of the MOSFET. En- layer-transfer process, block-level trench etch, wafer and that enables hybrid orientation was

hanced drive currents of 15 to 25% have been and epitaxial regrowth were performed before reported by Doris et al. (32).

demonstrated on sub-100-nm bulk strained- the conventional CMOS device process. A The growing power density and the diminish-

silicon MOSFETs (20). The performance ben- cross section of CMOS on hybrid substrate is ing process margin of sub-10-nm gate-length

efit of combining strained silicon with an shown in Fig. 3C, with NFET on (100) SOI MOSFETs cannot be dealt with by process tech-

SOI substrate has also been demonstrated in a and PFET on (110) silicon epitaxial layer. The nology alone. Overall system performance gain

60-nm gate length, N-channel MOSFET with hybrid substrate was formed by layer-transfer will require optimization among the technol-

ultrathin thermally mixed strained silicon/ technique through wafer bonding. First, hy- ogy, circuit, packaging, and architecture levels.

SiGe on insulator substrate (28). The presence drogen was implanted into an oxidized silicon

of the SiGe layer in strained-silicon substrate substrate. The wafer was then flip-bonded to a References and Notes

1. Semiconductor Industry Association, International

leads to several challenges related to materials handle wafer with different surface orienta- Technology Roadmap for Semiconductors (2003);

and integration, such as a high density of tion. A two-phase heat treatment was then available at http://public.itrs.net.

defects in strained silicon on relaxed SiGe carried out to split the hydrogen-implanted 2. R. H. Dennard et al., IEEE J. Solid-State Circuits 9, 256

(1974).

induced by the strain relaxation in SiGe and a wafer and strengthen the bonding. Finally, the 3. Y. Taur, IEEE Spectrum 36, 25 (1999).

substantial difference in doping diffusion top SOI layer was polished and thinned down 4. The performance of bulk MOSFETs is often degraded

property in SiGe. (Boron diffusion is retarded, to the desired thickness. A substantial PFET in a stack configuration. This is known as the reverse

body effect. In SOI technology, the body is isolated

whereas arsenic diffusion is enhanced as com- performance enhancement was demonstrated from other terminals; therefore, the reverse body

pared with the diffusion in silicon.) Such on 90-nm-node CMOS devices. effect can be avoided.

challenges require additional efforts in junc- Threshold voltage roll-off behavior, junc- 5. M. Ieong, J. Kedzierski, Z. Ren, B. Doris, T. Kanarsky, H.-S.

tion engineering to control SCEs and to set tion leakage current, overlap, and junction P. Wong, Extended Abstract of the 2002 International

Conference on Solid State Devices and Materials (SSDM),

the MOSFET threshold voltages to the desired capacitances are all very similar between Nagoya, Japan, 17 to 19 September 2002, pp. 136–137.

values. Substantial device self-heating is also (110) and (100) substrates, which indicates 6. B. Doris et al., International Electron Device Meeting

observed in strained silicon/SiGe devices similar dopant diffusion characteristics for (IEDM) Tech. Dig. 2002, 267 (2002).

7. J. Kedzierski et al., IEDM Tech. Dig. 2002, 247 (2002).

because of the lower thermal conductivity in these orientations. The HOT technology is 8. A halo implant is an ion implantation technique that

SiGe. Recently, Rim et al. (29) demonstrated clearly an attractive option to improve device places impurity dopants next to the junction tip to

transistors using ultrathin strained silicon performance without introducing new mate- prevent SCEs without substantially increasing the

total amount of impurity dopants in the channel.

directly on insulator (SSDOI) structures that rial. However, the impact on circuit perform- Because of the halo implant, devices can be scaled to

eliminate the SiGe layer before transistor fab- ance of mixing SOI and bulk devices on the shorter gate lengths before notable SCE sets in.

rication, thereby providing higher mobility same chip will require more detailed analysis. 9. B. Doris et al., IEDM Tech. Dig. 2003, 631 (2003).

10. Z. Ren et al., IEDM Tech. Dig. 2002, 51 (2002).

while mitigating the SiGe-induced material 11. H.-S. P. Wong, IBM J. Res. Dev. 46, 133 (2002).

and process integration problems. Viability: The Crucial Issues 12. M. Ieong, H.-S. P. Wong, E. Nowak, J. Kedzierski, E. Jones,

An SSDOI structure is fabricated by a The 2003 version of the International Road- Proc. Third International Symposium on Quality Electronic

Design (ISQED) (2002), pp. 492–495.

layer-transfer or ‘‘wafer-bonding’’ technique. map for Semiconductors (1) projected that, by 13. L. Chang et al., Proc. IEEE 91, 1860 (2003).

First, an ultrathin layer of strained silicon is 2016, sub-10-nm gate-length MOSFETs will 14. M. Ieong et al., IEDM Tech. Dig. 2001, 441 (2001).

formed epitaxially on a relaxed SiGe layer, be in production with equivalent oxide thick- 15. K. W. Guarini et al., IEDM Tech. Dig. 2001, 425 (2001).

and an oxide layer is formed on top. After nesses of 5 Å and junction depths below 10 nm. 16. J. M. Hergenrother et al., IEDM Tech. Dig. 1999, 75 (1999).

17. J. Kedzierski et al., IEDM Tech. Dig. 2001, 437 (2001).

hydrogen is implanted into the SiGe layer, the Although functional MOSFETs with sub-10- 18. D. Hisamoto, T. Kaga, Y. Kawamoto, E. Takeda, IEDM

wafer is flipped and bonded to a handle nm gate lengths have been demonstrated using Tech. Dig. 1989, 833 (1989).

substrate. A high-temperature process splits UTSOI substrate, manufacturability problems 19. X. Huang et al., IEDM Tech. Dig. 1999, 67 (1999).

20. K. Rim et al., Symposium on VLSI Technology, Honolulu,

away most of the original wafer and leaves of sub-10-nm gate devices remain to be re- HI, 11 to 15 June 2002, pp. 12–13.

the strained-silicon and SiGe layers on top of solved. First, gate stacks with higher dielectric 21. A. Lochtefeld, D. Antoniadis, IEEE Electron Device Lett.

the oxide layer. The SiGe is then selectively constants and metal gate electrodes are needed 22, 591 (2001).

22. S. Ito et al., IEDM Tech. Dig. 2000, 247 (2000).

removed and transistors are fabricated on the to mitigate the gate leakage problem. Second, 23. G. Scott, J. Lutze, M. Rubin, F. Nouri, M. Manley, IEDM

remaining ultrathin strained-silicon. A fabri- alternative doping techniques are required to Tech. Dig. 1999, 827 (1999).

cated SSDOI device structure is shown in produce shallow and abrupt junction profiles 24. T. Ghani et al., IEDM Tech. Dig. 2003, 631 (2003).

25. C.-H. Ge et al., IEDM Tech. Dig. 2003, 73 (2003).

Fig. 3A. Both electron and hole mobility without severely increasing the external re- 26. V. Chan et al., IEDM Tech. Dig. 2003, 77 (2003).

enhancement have been observed, which indi- sistance. Third, alternative device structures 27. K. Goto et al., IEDM Tech. Dig. 2003, 623 (2003).

cates that strain is retained after the device- such as UTSOI and double-gate structures will 28. B.-H. Lee et al., IEDM Tech. Dig. 2002, 946 (2002).

29. K. Rim et al., IEDM Tech. Dig. 2003, 49 (2003).

processing steps have been completed (29). likely be needed for sub-10-nm gate devices. 30. M. Yang, IEEE Electron Devices Lett. 24, 339 (2003).

Crystal orientation effects. The carrier Additional sources of performance gain are 31. M. Yang et al., IEDM Tech. Dig. 2003, 453 (2003).

mobility of inversion layers depends on surface also needed to compensate for any degradation 32. B. Doris et al., Symposium on VLSI Technology, Honolulu,

HI, 15 to 19 June 2004, pp. 86–87.

orientations and current flow directions. For P- from the subthreshold nonscaling phenomenon. 33. The authors are grateful to their IBM colleagues.

channel MOSFETs, hole mobility is 2.5 times Mobility-enhancement technique is attractive, Fabrication support by the Advanced Semiconductor

as high on (110) surface orientation as on a because it provides performance enhancement Technology Center of IBM Microelectronic Division

standard wafer with (100) surface orientation in addition to any benefits derived from device and the Advanced Semiconductor Technology Labo-

ratory of IBM Research are very much appreciated.

(30). However, electron mobility is highest on scaling alone. Straining the silicon crystal and

(100) substrates. To fully realize the advan- building N-type and P-type MOSFETs on differ- 10.1126/science.1100731

2060 17 DECEMBER 2004 VOL 306 SCIENCE www.sciencemag.org

Вам также может понравиться

- Chapter 7 Mosfets in Ics - Scaling, Leakage, and Other TopicsДокумент43 страницыChapter 7 Mosfets in Ics - Scaling, Leakage, and Other Topicsmorcov19Оценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- Dual-Gate Lateral Double-Diffused Metal&ndash Oxide Semiconductor With Ultra-Low Specific On-ResistanceДокумент6 страницDual-Gate Lateral Double-Diffused Metal&ndash Oxide Semiconductor With Ultra-Low Specific On-ResistanceAnonymous G1iPoNOKОценок пока нет

- Mosfet PDFДокумент5 страницMosfet PDFChandru BadachiОценок пока нет

- On The 60 Mv/dec @300 K Limit For MOSFET Subthreshold SwingДокумент3 страницыOn The 60 Mv/dec @300 K Limit For MOSFET Subthreshold Swingmayuri sritharanОценок пока нет

- Kelompok 4 Bab 4Документ81 страницаKelompok 4 Bab 4Wisnu WicaksonoОценок пока нет

- Dančak2018 Chapter TheFinFETATutorialДокумент33 страницыDančak2018 Chapter TheFinFETATutorialAhmed KamalОценок пока нет

- Test of Fast SCRs As Spark Gap ReplacementДокумент5 страницTest of Fast SCRs As Spark Gap Replacementandy1144552Оценок пока нет

- Vlsi Topic2bДокумент4 страницыVlsi Topic2bsyabseeshoesОценок пока нет

- Avalanche Transit Time DevicesДокумент8 страницAvalanche Transit Time DevicesSiddhesh PhapaleОценок пока нет

- EI2301-IE - Unit 1 - Part A and Part B - With Answers PDFДокумент21 страницаEI2301-IE - Unit 1 - Part A and Part B - With Answers PDFsartpgitОценок пока нет

- ABB PartДокумент86 страницABB PartLing Kun YangОценок пока нет

- REN An7244 APN 19980812Документ5 страницREN An7244 APN 19980812Jeff PalaganasОценок пока нет

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorДокумент14 страницMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaОценок пока нет

- Zhang 2009Документ4 страницыZhang 2009badid SusskindОценок пока нет

- DABRSwithreactivePower PDFДокумент6 страницDABRSwithreactivePower PDFAyral FernandezОценок пока нет

- Charge Transport Acoustic Waves GaAsДокумент5 страницCharge Transport Acoustic Waves GaAsSaleem SaleemОценок пока нет

- Rik W - 1991 - A Three-Phase Soft-Switched High-Power-Density DC - DC Converter For High-Power ApplicationsДокумент11 страницRik W - 1991 - A Three-Phase Soft-Switched High-Power-Density DC - DC Converter For High-Power ApplicationsashnajosephОценок пока нет

- 18ec61 Text Book 2Документ25 страниц18ec61 Text Book 2Pritam SarkarОценок пока нет

- Study and Analysis of Advanced 3D Multi-GateДокумент15 страницStudy and Analysis of Advanced 3D Multi-GateRaj sambhavОценок пока нет

- 4.1 Device Structure and Physical Operation: Reading Assignment: Chapter 4 Covers Field Effect TransistorsДокумент22 страницы4.1 Device Structure and Physical Operation: Reading Assignment: Chapter 4 Covers Field Effect Transistorsjatanbhatt89Оценок пока нет

- Power Electronics Ned Mohan Slides Ch22Документ35 страницPower Electronics Ned Mohan Slides Ch22Anoop MathewОценок пока нет

- Section 3A Transmission Lines PackageДокумент10 страницSection 3A Transmission Lines PackagealfredomatiasrojoОценок пока нет

- Anomalously Beneficial Gate-Length Scaling Trend of Negative Capacitance TransistorsДокумент4 страницыAnomalously Beneficial Gate-Length Scaling Trend of Negative Capacitance Transistorswhdrhks7907Оценок пока нет

- Chapter 3-Dielectric PropertiesДокумент38 страницChapter 3-Dielectric Propertieskanita_jaww100% (1)

- Chenming Hu ch7 SlidesДокумент43 страницыChenming Hu ch7 SlideseleenaamohapatraОценок пока нет

- A PCB Integrated Differential Rogowski Coil For Non-Intrusive Current Measurement Featuring High Bandwidth and DVDT ImmunityДокумент6 страницA PCB Integrated Differential Rogowski Coil For Non-Intrusive Current Measurement Featuring High Bandwidth and DVDT Immunityu.s.routОценок пока нет

- MosfetДокумент13 страницMosfetSristick100% (3)

- Chapter 3XДокумент38 страницChapter 3XdsaОценок пока нет

- EI2301 IE Notes FullДокумент103 страницыEI2301 IE Notes FullVenkatesan SatheeswaranОценок пока нет

- MOSCAPДокумент6 страницMOSCAPEjder YildizОценок пока нет

- FORTH 4H-SiC High Frequency DiodesДокумент6 страницFORTH 4H-SiC High Frequency DiodesKonstantinos ZekentesОценок пока нет

- Application Note AN-1084: Power MOSFET BasicsДокумент13 страницApplication Note AN-1084: Power MOSFET Basicshardcore18Оценок пока нет

- Power MOSFET BasicsДокумент13 страницPower MOSFET BasicsTim PriceОценок пока нет

- Mesfet 1Документ25 страницMesfet 1Kiran KirruОценок пока нет

- Edited - VLSI DESIGN U4Документ26 страницEdited - VLSI DESIGN U4merupuОценок пока нет

- Trapatt ModeДокумент30 страницTrapatt Modebchaitanya_555100% (1)

- Tunnel Field EffectДокумент28 страницTunnel Field EffectGary Ryan DonovanОценок пока нет

- Extraction SystemДокумент3 страницыExtraction Systemdev.phani225757Оценок пока нет

- HW1 SolДокумент4 страницыHW1 Soluzair ahmadОценок пока нет

- Notes On ScallingДокумент9 страницNotes On ScallingSGSОценок пока нет

- 15-20W Class AB Audio AmplifierДокумент4 страницы15-20W Class AB Audio AmplifierhsОценок пока нет

- Detailed Notes: IC Fabrication ProcessДокумент81 страницаDetailed Notes: IC Fabrication ProcessimmadiuttejОценок пока нет

- A Circuit For All Season - The Bandgap Refernce (Razavi2016)Документ4 страницыA Circuit For All Season - The Bandgap Refernce (Razavi2016)jackal1710Оценок пока нет

- CMOS Interview QAДокумент14 страницCMOS Interview QAarammartОценок пока нет

- 12-MOSFET - Structure and DC Characteristics-22!02!2024Документ20 страниц12-MOSFET - Structure and DC Characteristics-22!02!2024ashbinny1Оценок пока нет

- MOS Integrated Circuit DesignОт EverandMOS Integrated Circuit DesignE. WolfendaleОценок пока нет

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1От EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (5)

- A Guide to Vintage Audio Equipment for the Hobbyist and AudiophileОт EverandA Guide to Vintage Audio Equipment for the Hobbyist and AudiophileОценок пока нет

- Highly Integrated Gate Drivers for Si and GaN Power TransistorsОт EverandHighly Integrated Gate Drivers for Si and GaN Power TransistorsОценок пока нет

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 3От EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 3Рейтинг: 3 из 5 звезд3/5 (2)

- Density Functional Theory (DFT)Документ42 страницыDensity Functional Theory (DFT)karandeep1Оценок пока нет

- 2.9.31. Particle Size Analysis by Laser Light Diffraction 20931eДокумент4 страницы2.9.31. Particle Size Analysis by Laser Light Diffraction 20931eAna MariaОценок пока нет

- D & F Block Elements UploadДокумент13 страницD & F Block Elements UploadNihalОценок пока нет

- Physics and Technology - Vishay SemiconductorsДокумент8 страницPhysics and Technology - Vishay Semiconductorsdanny_nikhilОценок пока нет

- Ase102:Aerospace Materials and Processes: Session 2019-20 Page:1/1Документ1 страницаAse102:Aerospace Materials and Processes: Session 2019-20 Page:1/1Yashwanth Krishna GampaОценок пока нет

- Selected Solutions, Griffiths QM, Chapter 1Документ4 страницыSelected Solutions, Griffiths QM, Chapter 1Kenny StephensОценок пока нет

- Beta DecayДокумент5 страницBeta DecayengrroyОценок пока нет

- Crossword PuzzleДокумент1 страницаCrossword Puzzlejoshualohman6Оценок пока нет

- The Preparation of Magnetic Nanoparticles For Applications in BiomedicineДокумент17 страницThe Preparation of Magnetic Nanoparticles For Applications in BiomedicineMadavat Prem Pai LópezОценок пока нет

- High Resolution Imaging Detectors: K.S. SureshДокумент26 страницHigh Resolution Imaging Detectors: K.S. Sureshvishnu girish cОценок пока нет

- Magnetic Properties of The LanthanidesДокумент92 страницыMagnetic Properties of The LanthanidesAnonymous pjRBh8vXvОценок пока нет

- Physics Investigatory ProjectДокумент23 страницыPhysics Investigatory ProjectChampa Deepa PalialОценок пока нет

- Exam Chapters 7, 8, 9 ReviewДокумент2 страницыExam Chapters 7, 8, 9 ReviewAlain CheryОценок пока нет

- Power Electronic DevicesДокумент18 страницPower Electronic DevicesSree ShobhaОценок пока нет

- 26.8% Improved Triple Junction (ITJ) Solar Cells: FeaturesДокумент2 страницы26.8% Improved Triple Junction (ITJ) Solar Cells: FeaturesMordi DomiОценок пока нет

- δ-Bi2O3 thin films prepared by reactive sputtering - Fabrication and characterizationДокумент6 страницδ-Bi2O3 thin films prepared by reactive sputtering - Fabrication and characterizationrafael pimentelОценок пока нет

- Properties of Engineering Materials: Chapter 3Документ52 страницыProperties of Engineering Materials: Chapter 3Alaa AfanehОценок пока нет

- States of MatterДокумент19 страницStates of MatterOmar ChaudhryОценок пока нет

- Elements and AtomsДокумент16 страницElements and Atomshhemn94Оценок пока нет

- Pre TestДокумент2 страницыPre TestGhem EmeloОценок пока нет

- Journal Pre-ProofsДокумент54 страницыJournal Pre-ProofsSubham AdhikariОценок пока нет

- Atomic Packing FractionДокумент17 страницAtomic Packing FractionMd. Ashraf AliОценок пока нет

- Static ElectricityДокумент4 страницыStatic ElectricityMuhammad Wasil KhanОценок пока нет

- Wright1997 PDFДокумент8 страницWright1997 PDFEdmundo LópezОценок пока нет

- Coatings: Influence of Growth Temperature of The Nucleation Layer On The Growth of Inp On SiДокумент9 страницCoatings: Influence of Growth Temperature of The Nucleation Layer On The Growth of Inp On SitaikiОценок пока нет

- Elektronika Daya Dan PenerapannyaДокумент30 страницElektronika Daya Dan PenerapannyaMuhammad AfdalОценок пока нет

- Diodes For Optical RectennaДокумент203 страницыDiodes For Optical RectennaronbinyeОценок пока нет

- Mse Imperfections in Solids 1 StudentДокумент42 страницыMse Imperfections in Solids 1 StudentRishav PrasadОценок пока нет

- Infrared Plastic Solar CellДокумент19 страницInfrared Plastic Solar CellAjay Mv100% (2)

- Gss Ug en PDFДокумент165 страницGss Ug en PDFk_gh22Оценок пока нет