Академический Документы

Профессиональный Документы

Культура Документы

ASIC Design/Verification

Загружено:

api-787211740 оценок0% нашли этот документ полезным (0 голосов)

26 просмотров2 страницыASIC Design/Verification

Авторское право

© Attribution Non-Commercial (BY-NC)

Доступные форматы

TXT, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документASIC Design/Verification

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате TXT, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

26 просмотров2 страницыASIC Design/Verification

Загружено:

api-78721174ASIC Design/Verification

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате TXT, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

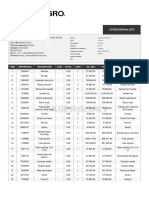

439 South 4th St Apt 10

San Jose, CA-95112

Contact no: (408)759 1338

Mail:

Professional Objective:

Seeking a position to utilize my skills and abilities as an ASIC Design/Verifica

tion Engineer that offers professional growth while being resourceful, innovativ

e and flexible

Academic Qualification:

MS in Electrical Engineering, San Jose State University, CA, May 2010. GPA 3.5/4

.0

BS in Electrical Engineering Mumbai University, Mumbai, India, Jan 2007

Coursework:

Semiconductor Devices

Digital System Design and Synthesis

CMOS ASIC Design

SOC and System Verilog concepts

Digital Signal Processing

Skills:

Languages: Verilog, C, Python

Design Tools: Cadence Schematic and Virtuoso, ModelSim, VCS

Verification: System Verilog

Operating Systems: UNIX, Windows

* Hands on experience with 8051 Microcontroller

* Good knowledge about ARM processors

* Hands on experience with test instruments like oscilloscopes

* Good knowledge of Static Timing analysis (STA)

* Good understanding of OVM verification methodology

Project Summary:

* Design of a Low cost direct RF PSK demodulator using PLL, August 2009 - May 2

010

Design, schematic and Layout of PLL, using a differential VCO and CML divider, i

n CMOS 0.18? TSMC technology locking at 433.93MHz ISM bandwidth and Verilog A co

ding for a Finite state machine as well as NRZ, bit unstuffing and framing of th

e data output

* Design of Phase Locked Loop, August 2009 - December 2009

Designed a phase locked loop in CMOS 0.13?m TSMC technology. The PLL locked the

reference at a natural frequency of 2GHz with a tuning frequency range of 250MHz

. The design of the VCO was achieved using CMOS differential ring oscillator

* ATM switching using System Verilog, January 2009 - May 2009

System Verilog was used for verification of the ATM switching SOC with assertion

and functional coverage based verification on VCS as well as ModelSim tool

* 64-bit Adder that drives a load of 20fF, Jan 2009 - May 2009

Design schematic of a 64bit 5 stage Carry look Ahead adder in CMOS 45 nm TSMC te

chnology and performing Layout and LVS

* Analysis of Area-Delay and Power-Delay Tradeoffs in Addition Circuits, August

2008 -December 2008

RTL Design and comparative study including Timing Analysis for 8,16,32,64 bit Ri

pple carry adders and Carry look-ahead adders using Verilog coding using VCS and

for synthesis used the Toshiba library

* Circuit simulation for a Confuzer to Unconfuzer circuit with the concept of t

he Networking Cryptography, August 2008 - December 2008

Implemented and tested the Unconfuzer circuit with test-bench with CRC in Verilo

g also done in VCS

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Xerox® ColorQube® 9303 Family Service ManualДокумент1 812 страницXerox® ColorQube® 9303 Family Service Manualvitalkriven82% (11)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- 6000 Tech ManualДокумент42 страницы6000 Tech Manualaung minhtet67% (3)

- 1100 Series 115 Issue 1 New Priming Pump For Certain Generator Sets (BFPM) February 2015Документ4 страницы1100 Series 115 Issue 1 New Priming Pump For Certain Generator Sets (BFPM) February 2015Ayobami JubrilОценок пока нет

- Inductance of A 3 Phase Overhead Line With Equilateral SpacingДокумент20 страницInductance of A 3 Phase Overhead Line With Equilateral SpacingAp kowshikОценок пока нет

- Speed Control of Induction Motor Using PI and V/F Scalar Vector ControllersДокумент9 страницSpeed Control of Induction Motor Using PI and V/F Scalar Vector ControllersYesha ShahОценок пока нет

- Cable Price ListДокумент2 страницыCable Price ListPrantik Adhar SamantaОценок пока нет

- Input and Output DevicesДокумент6 страницInput and Output DevicesLakshmiRengarajanОценок пока нет

- PE Manual 2017-18Документ49 страницPE Manual 2017-18sandeep sОценок пока нет

- Frendx: AnarcДокумент60 страницFrendx: AnarcKasi XswlОценок пока нет

- Chapter 3: Symmetrical ComponentsДокумент18 страницChapter 3: Symmetrical ComponentsKvv BapirajuОценок пока нет

- Telephone Network and DSL Technology: U.K.P. Mihiranga (MBA in MOT, B.Sc. Eng. (Hons), PMP-PMI (USA), AMIESL)Документ37 страницTelephone Network and DSL Technology: U.K.P. Mihiranga (MBA in MOT, B.Sc. Eng. (Hons), PMP-PMI (USA), AMIESL)Pathum MihirangaОценок пока нет

- COT-ASERGRO-NUMERO-2270 BarrazaДокумент2 страницыCOT-ASERGRO-NUMERO-2270 Barrazasandra ariasОценок пока нет

- Micro Program Control UnitДокумент27 страницMicro Program Control UnitNaman GuptaОценок пока нет

- Orcad LayoutДокумент21 страницаOrcad LayoutjeepschuleОценок пока нет

- Samsung Bluetooth Hm1100 Manual enДокумент21 страницаSamsung Bluetooth Hm1100 Manual enshoeb2007Оценок пока нет

- XNS50660ABДокумент4 страницыXNS50660ABmajochepe25Оценок пока нет

- Lighting Katalog 2014Документ25 страницLighting Katalog 2014team37Оценок пока нет

- Stepper Motor Implementation On FPGA (1) With 1.5 FinalДокумент61 страницаStepper Motor Implementation On FPGA (1) With 1.5 Finalswati sakhare100% (1)

- Epever Datasheet SPP 02Документ2 страницыEpever Datasheet SPP 02hermantoОценок пока нет

- GBSS19.1 Feature DescriptionДокумент461 страницаGBSS19.1 Feature DescriptionHoyekunleyОценок пока нет

- TM9 2920 242 35Документ110 страницTM9 2920 242 35Rulax MtzОценок пока нет

- Módulo Bluethoo PDFДокумент6 страницMódulo Bluethoo PDFEduard SastoqueОценок пока нет

- Building A Serial Interface For JP1.2 and JP1.3Документ2 страницыBuilding A Serial Interface For JP1.2 and JP1.3Yo YoОценок пока нет

- Lead Acid BatteryДокумент6 страницLead Acid BatterysafariОценок пока нет

- Equalizer RingsДокумент1 страницаEqualizer RingsMr. No oneОценок пока нет

- Sirona Orthophos XG Dental X-Ray - Maintenance Instructions PDFДокумент58 страницSirona Orthophos XG Dental X-Ray - Maintenance Instructions PDFomar kassarОценок пока нет

- Fulltext01 4Документ83 страницыFulltext01 4survivalofthepolyОценок пока нет

- Yagi Uda AntennaДокумент14 страницYagi Uda AntennaKeerthi Vasan SОценок пока нет

- Image Tamper Detection Based On JPEG ArtifactsДокумент6 страницImage Tamper Detection Based On JPEG ArtifactsInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- Ceramic and Mylar Capacitor Value Howto and Code SheetДокумент3 страницыCeramic and Mylar Capacitor Value Howto and Code SheetSynworks Development Group67% (3)