Академический Документы

Профессиональный Документы

Культура Документы

FPGA Implementation of Biometric Authentication System Based On Hand Geometry

Загружено:

begamotikИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FPGA Implementation of Biometric Authentication System Based On Hand Geometry

Загружено:

begamotikАвторское право:

Доступные форматы

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

Celia Lpez-Ongil, Raul Sanchez-Reillo, Judith Liu-Jimenez, Fernando Casado, Leslie Snchez, and Luis Entrena

Microelectronics Group, Electronic Technology Department. University Carlos III of Madrid. Avda. de la Universidad, 30. 28911 Legans. Madrid Spain {celia,rsreillo,jliu,fcasado,lsanchez,entrena}@ing.uc3m.es Abstract. The increasing demand for pervasive security poses a challenge in achieving robust authentication at very low cost. Identification using human biometrics is considered the most robust solution, but requires powerful computers to be performed in acceptable time. In this work a FPGA implementation of a biometric authentication system based on hand geometry is presented. The system covers all necessary steps to process a human hand pattern and verify it against a user template. This solution is able to reduce processing time by three orders of magnitude with respect to microprocessorbased solutions of similar cost, while keeping the same identification quality. On the other hand, it can be implemented in a small size FPGA, thus making it suitable for a large number of low cost applications.

1 Introduction

The increasing demand for security in our society is driving attention towards more robust and efficient solutions for user authentication and identification. Biometrics has been traditionally considered one of the best solutions for human recognition. Biometric patterns are unique for each person and are more difficult to fake than others based on passwords and secret codes or those based on physical tokens. Existing biometric systems are based on different biological or behavioural features such as speaker verification, signature recognition, fingerprint measure, iris pattern or hand geometry [1] and [2]. Among these, hand geometry has the advantage of being user-friendly and ergonomic. The quality of these techniques is represented by two ratios, False Acceptance Ratio (FAR) and False Rejection Ratio (FRR) which try to report the number of errors the system performs when recognizing users. Biometric authentication systems require complex pattern recognition algorithms. These algorithms can be executed in todays computers within acceptable time. However, execution time is still unacceptable in low cost microprocessors. This fact prevents the widespread use of biometric systems in an important market that requires very low cost systems and includes applications such as ubiquitous access control,

J. Becker, M. Platzner, S. Vernalde (Eds.): FPL 2004, LNCS 3203, pp. 4353, 2004. Springer-Verlag Berlin Heidelberg 2004

44

C. Lpez-Ongil et al.

smart cards, etc. In order to satisfy this demand, low cost systems with higher performance are needed. In this work, an efficient hardware implementation of a biometric authentication system based on hand geometry is proposed. This implementation provides an improvement of three orders of magnitude in processing time and can be downloaded in a small FPGA (ASICs could be used if the product volume is large enough). In addition, it can also be used to improve performance for systems that require verification with respect to a large user database. This work has been partially funded by Spanish Government, through the research project TIC-2003-01793 SIDECAR, (Identification and Communications Systems through Reconfigurable Hardware) The paper is organized as follows. In section 2, main aspects of the hand geometry authentication algorithm are explained. Section 3 details architecture implementation. Results are shown in section 4 and, finally, conclusions are stated in section 5.

2 Hand Geometry Recognition

Hand geometry recognition systems are quite good for environments where mediumhigh security is required, and where a medium cost equipment (only a low resolution CCD camera is needed), relative low computational cost (because the algorithms to extract the features are based on basic morphological image processing [3],[4] and [5]) are needed. Finally, it implies a very low feature vector size. A typical biometric recognition system is normally structured in two phases, namely enrollment and verification, Fig. 1. The enrollment process consists in taking various samples of a user pattern and generating a user template that it is stored for eventual comparison. The authentication process is launched every time a user wants to gain access to the secure environment, and decides whether the current user data corresponds to the user template. Currently, user templates are stored in smart cards which act as physical tokens.

Fig. 1. Hand Geometry Recognition System

The authentication process involves three main steps. First, the user pattern must be captured and preprocessed in order to enhance the features of interest. The second step is feature extraction. Finally, the current features are compared with the template features in order to authenticate the current user. Our hand geometry recognition is

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

45

based on the algorithm proposed in [6] and [7], and the main steps are described in the sequel. Image Capture In this step an image of the hand is taken using a low resolution CCD camera. The hand is placed on a platform guided by 6 tops, in order to position the hand in front of the camera objective. Different views of the prototype designed can be seen in Fig. 2.

Fig. 2. Prototype developed (a. general view; b. placement of the hand; c. sample taken)

A mirror is located on one side of the platform for obtaining a side view of the hand and performing more measures. The platform is painted in blue to increase the contrast with the human skin. Images taken are RGB with 480x640 pixels (24 bits). Data Preprocessing This step converts input data into manageable information where biometric features could be easily extracted. The algorithm transforms a color image of the users hand into a hand profile. First, a grey-scale image of the hand is generated in order to eliminate all unnecessary information (background). Secondly, a black and white image is obtained in order to generate, finally, a hand profile with an edge detection filter. Grey Scale Conversion The original algorithm applies the equation (1), in order to eliminate blue color (background) from the image and to obtain a grey-scale one. Normalizations are done in order that histogram can be expanded. Resulting image has 480x640 pixels (8 bits pp).

((Rn + Gn )n Bn )n

(1)

Black and White Conversion This process converts the grey-scaled image into a black and white one. A threshold is applied in order to decide if the pixel is black (hand) or white (background). The result is an image of 480x640 pixels (1 bit pp).

46

C. Lpez-Ongil et al.

Edge Detection This process applies filters to generate a hand profile that enables the measuring of the main features. Sobel and Laplacian filters have been considered in this work. Both of them consist in detecting pixels surrounded by different colored pixels. A mask matrix is applied on every pixel. The results obtained by Sobel filter are better for noisy input images but the profile has wider edges. Feature Extraction In this step geometrical measures are performed, from the hand profile, to obtain a set of 25 features. These features have been previously defined and stated as the most representative set of measurements, [1] and [2], and include:

Widths of the 4 fingers (thumb is excluded) Width of the palm Height of the palm, the middle finger and the small finger Distances between the finger joints Angles between the finger joints

To avoid changes due to gain or losing of weight, all the measures (except the angles) are normalized by the first width measured of the middle finger. The result is a feature vector with 25 components, each of them coded in 1 byte. Feature Matching Once pattern features are available, they are compared with template features in order to obtain the distance between them. Euclidean distance, Hamming distance, etc. could be applied depending on the degree of security that is considered, [6] and [7]. With the distance obtained from the comparison between template and measurements, the recognition system must decide user access to the secure environment. A threshold is set in such a way that FAR as well as FRR are minimized. This threshold must be statistically calculated during enrollment process. In this biometric technique Continuous Hamming distance is applied on the 25 1 2 features obtained from the users hand image. Considering r and r , pattern features and user template features respectively, and b typical deviation of every data, Hamming distance, d(r1,r2), is defined as shown in equation (3).

r 1= [K 11, K 12,..., K 1n ].

r 2 = [K 21, K 22,..., K 2 n ] .

b = [b1, b 2,..., bn ]

(2) (3)

(4)

d ( r1, r 2) = j =1 ( K 1 j, K 2 j )

n

( K 1 j, K 2 j ) = 0 if K 1 j K 2 j bj

( K 1 j , K 2 j ) = 1 if K 1 j K 2 j > bj

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

47

3 System Architecture

In order to improve the performance of the hand geometry recognition algorithm, a hardware implementation is proposed. Fig. 3a shows the architecture of this hardware implementation. It contains four main blocks, according to the steps of the algorithm, preprocessing (Grey Scale and Edge Detector), feature measuring and feature matching. Also, the architecture has three interfaces for receiving user pattern and user template, as well as for storing temporary data in external memory banks. An internal RAM memory is used to store temporary data in the latest steps of the algorithm execution. In the hardware implementation information storage is a key factor due, mainly, to the large amount of data to be processed. It is important how and where the information is stored, as it could be seen in Fig. 3b where storage blocks are filled. In this implementation partial and global results are stored in RAM blocks, external or internal to the circuit. The use of various banks of memory and fast memories has provided short access times and a small number of memory accesses. a)

Red Green Blue

b)

External RAM

Pre-processed Data Storage

Pre-processing

RAM Interface Grey Scaler Internal RAM Cammera Interface Edge Detector

Features extraction

Data Storage

Features Storage

User Template Interface

Verifier

Features Measurer

Template Storage

Comparator

Fig. 3. a) Architecture of the proposed hardware implementation b) Storage blocks

In order to generate a high speed application, faster operators, parallelism and pipelining have been applied. Finally, it is important to set the precision required not only for achieving good results in the information processed but also for reducing resources employed. Arithmetic operations are performed with full precision. Regularly it is not possible to store the amount of information generated and results data will be truncated in order to be stored in memory. The FPGA implementation of the hand geometry recognition technique is described in this section. The resulting system is analyzed with respect to the enhancements obtained in the time domain, in the resources used and in the cost achieved. Also, the accuracy terms FAR and FRR is taken into account. These ratios are detailed in section 4.

48

C. Lpez-Ongil et al.

Data Storage This first step in the processing receives input data, which is a hand image (RGB) of M pixels (8 bits per pixel), being M=480x640. In the following M will state for 480x640, to represent the number of pixels. Image is coming from a digital camera and it is stored in external memories. In the process of downloading, some values are calculated that could be applied in latter processes, such as normalizations (e.g. Rn). The use of three banks of memory reduces the number of memory accesses from 3M to 1M. On the other hand, accuracy is maintained and resources needed are a Data Path and an Address Generator. Black and White The original algorithm for grey scale conversion applies the equation (1). In this work, equation (5) has been implemented, in order to reduce memory accesses as well as arithmetic operations. (R + G)n Bn . (5) Table 1 shows the complexity of the hardware and software implementations as a function of M. Second column contains cycles needed for arithmetic operations, while third and fourth are for memory readings and writings. Last column shows total cycles required in each implementation. As it can be seen, FPGA implementation reduces memory accesses as well as cycles employed in arithmetic operations, thanks to parallelism and pipelining. Pixels are processed in one clock cycle with a latency of 5 cycles. It should be noted that in FPGA implementation these arithmetic operations are performed in parallel with memory readings and writings, so as total execution times is even less.

Table 1. Cycles required in preprocessing hand image in FPGA and software implementation

Algorit hm (1) (5)

Implementatio n

# Arithmetic Operations

#Memory Readings

#Memory Writings

Total

HW (FPGA) SW (uP) HW (FPGA) SW (uP)

3M 12M 1M 6M

3M 12M 1M 6M

3M 7M 1M 4M

6M 31M 2M 16M

Once the grey scale image is obtained, a black and white conversion is performed, by the application of a threshold. This last step produces images of 480x640 pixels (1 bit pp) which are stored in an internal memory of the circuit. With respect to the accuracy, the comparison between results given by the FPGA and the software implementation has shown slight differences. Fig. 4a shows a black and white image generated by the hardware block. In Fig. 4b, differences with software application image could be seen. The average error is less than 2%. This error is due to internal precision, 16 bits in hardware and 64 bits in Matlab.

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

49

a)

b)

Fig. 4. a) Black and white image. b) Difference between results given by hardware and software implementation

Edge Detection In this step, filter application consist in matrix multiplication (3x3) on every pixel of the black and white image. As masks are composed of constant values, multiplications become very simple. The main bottleneck in this task is memory access to read the whole image. It is necessary to read 9 values per pixel, so 9M reads are needed. This is solved by using 3 banks of memory to store the image. If the black and white image is stored in the three banks at a time, only one cycle is needed to read three values. Also, if values used for the previous pixel processing are maintained, only three new values are needed for the next. With these two conditions, only M cycles are needed to operate pixels and M memory accesses are needed. b)

Table(apos)

a)

Areg

Table(bpos) Breg Table(cpos) Creg Table(dpos)

BW1

A

BW2

C

Dreg Table(epos) Ereg Table(fpos) DataOut

UMB

D

BW3

Freg

G

FirstLoad Right Left Down FirstLoad Right Left Down

H

FirstLoad Right Left Down

I

Greg

Table(gpos)

Table(hpos) Hreg Table(ipos) Ireg

Clk

Fig. 5. Circular shift register and data path for edge detection

This solution has been implemented in the FPGA with a circular shift register which is able to store, rotate and shift values coming from the memories, shown in Fig. 5a. Parallelism and pipelining has been applied in order to reduce the time delay in the arithmetic operations. Pixels are processed in one clock cycle, with a latency of 5 cycles, within data path shown in Fig. 5b. In Table 2, cycles needed to process the image, in hardware and software implementation are compared. Second column

50

C. Lpez-Ongil et al.

contains cycles needed for arithmetic operations, while third and fourth are for memory readings and writings. Last column shows total cycles required in each implementation. It could be seen that software implementation uses 27M memory while FPGA uses only 1M.

Fig. 6. Edges detected with Laplacian and Sobel filters in the hardware implementation. Table 2. Cycles required for edge detection in FPGA and software implementation Implementation # Arithmetic Operations #Memory Readings #Memory Writings Total

HW (FPGA) SW (uP)

1M 17M

1M 9M

1M 1M

1M 27M

The accuracy obtained in the FPGA implementation is quite good. Currently, hardware provides results quite similar to software implementation. In Fig. 4 and Fig. 5 the superposition of both results are given for Laplacian and Sobel filters. As it could be seen, Sobel filter provides wider edges. Biometric Feature Extraction In this step the hand profile is read and measured in order to obtain the 25 features that characterize a human hand [1] and [2]. The architecture of the feature extraction module is shown in Fig. 7. This architecture is able to compute all features in parallel as the hand profile is being read from the memory. Thus, all features can be extracted within a single full memory read. Data path for arithmetic operations is pipelined in order to improve throughput.

ClearAddress LoadAddress RowAddress

FingerJoints

Measurer Widths

Measurer Datapath

ColumnAddress

AddressRow

EdgePixelReg

DesvPixels

AddressCol

Widths

Hand DataVector

MEASURES

MeasurerRegisters MeasurerMainControl

Start

End

Fig. 7. Architecture of feature matching block

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

51

The architecture contains a data path (FingerJoints) that is in charge of reading the hand profile from memory and identifying some key points of the hand geometry, the finger joints which serve as reference points for other measures. Measurer Widths is a specific data path for obtaining finger widths and Measurer Datapath is in charge of calculating features that involve complex operations (angles, deviations, etc.). Finally, a set of register is used to store final measurements. Execution process takes as much as M+ M/20 memory readings and the same for arithmetic operations. Table 3 presents a comparison with software implementation.

Table 3. Cycles required for edge detection in FPGA and software implementation Implementation # Arithmetic Operations

M/20+1M M/20+1M

#Memory Readings

M/20+1M 25*1M

#Memory Writings

Total

FPGA uP

1

25

M/20 + 1M M/20 +26M

The accuracy has been checked and the results are quite similar. Differences are due to internal bit precision employed (16 bits in FPGA and 64 bits in Matlab). Feature Matching The hardware implementation of this block is a comparator that decides if differences between user pattern and user template are less than a provided threshold (typical deviation). This block implements the Hamming distance detailed in section 2. Comparison is done in parallel, and only one cycle is required for this block. FAR and FRR for FPGA implementations is quite similar to those for software implementation, Fig. 8, therefore quality is maintained.

False Rejection Ratio False Acceptance Ratio

Threshold

Fig. 8. FAR and FRR ratios in software implementation

4 Implementation Results

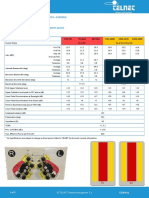

The Hand Geometry Authentication system implemented with a FPGA solution has been designed following top-down methodology. Hardware descriptions have been done in VHDL language at RT level. Synopsys, ISE and Modelsim CAD tools have been used during the design process for RTL simulation, logic synthesis, place&route and FPGA mapping. Final prototyping has been done in a platform

52

C. Lpez-Ongil et al.

FPGA from Xilinx (Virtex 2000E) included in a PCI board from Celoxica Ltd, [8] and [9]. This board provides also four banks of memory (2MB per bank) as well as PCI communication. Comparison with respect to software application has been represented graphically, according to steps needed in the whole process. This information is shown in Fig. 9, for memory readings, memory writings and arithmetic operations. Implementation report is shown in Table 4. There is a low FPGA occupation except for Block RAMs, used to store hand profile and to enhance memory accesses. It is possible to use smaller FPGAs storing this partial result in external memory also. With respect to maximum frequency, typical delay is 29.7 ns. Therefore this FPGA implementation works at 33 MHz.

Memory Readings

Memory Writings

MATLAB VHDL Hand Image Edge Comparison Storage Detection Grey Scale Features Conversion Extraction

MATLAB VHDL Hand Image Edge Detection Comparison Storage Grey Scale Features Extraction Conversion

Arithmetic Operations

MATLAB VHDL Hand Image Grey Scale Edge Detection Features Storage Conversion Extraction Comparison

Fig. 9. Comparison of memory accesses and arithmetic operations in both implementations Table 4.

FPGA Elements Slices Slice Flip-flops 4 input Lust Bounded IOs BRAMs GClks

Used 1,578 892 2,813 263 128 1

Available 19,200 38,400 38,400 408 160 4

% 8% 2% 7% 64% 80% 25%

From tables 1, 2 and 3 the total number of cycles for algorithm execution has been obtained. FPGA implementation takes 1,551,360 operation cycles while software solution takes 22,133,760 cycles. Considering two scenarios, implementation in the selected FPGA and in a typical microprocessor (1Minst. per cycle) typical execution time will be 47ms and 20s respectively (taking into account that an instruction cycle in a microprocessor takes more than one clock cycle). On the other hand, if we

FPGA Implementation of Biometric Authentication System Based on Hand Geometry

53

consider the use of a high performance PC, times are in the same order as in FPGA but cost, resources and power consumption is much higher. Therefore, FPGA implementation has been proved as the best solution with respect to cost-effective and fast applications.

5 Conclusions

In this work, a hardware implementation for biometric recognition system based on hand geometry has been presented. Main aspects related to area, speed and accuracy have been considered. The proposed solution is able to reduce processing time by 3 orders of magnitude with respect to microprocessor based solutions, with a similar cost, size and power consumption, while keeping the same identification quality. On the other hand, it can be implemented in a small size FPGA, or an ASIC if product volume is large enough, thus making it suitable for a large number of low cost applications.

References

[1] Jain A. K., Bolle R., Pankanti S., et al., Biometrics: Personal Identification in Networked Society. Kluwer Academic Publishers. 1999. [2] Jain L.C., Halici U., Hayashi I., Lee S. B., Tsutsui S., et al., Intelligent Biometric Techniques in Fingerprint and Face Recognition. CRC Press LLC. 1999. [3] Schalkoff R.J. Digital Image Processing and Computer Vision. John Wiley & Sons. 1989 [4] Jain A. K., Fundamentals of Digital Image Processing. Prentice Hall. 1989. [5] Jhne B., Practical Handbook on Image Processing for Scientific Applications. CRC Press LLC. 1997. [6] Ral Snchez Reillo Mecanismos de autenticacin biomtrica mediante tarjeta inteligente. Tesis doctoral. Universidad Politcnica de Madrid. Escuela Tcnica Superior de Ingenieros de Telecomunicacin. Madrid, 2000 [7] Sanchez-Reillo, R. Sanchez-Avila, C., Gonzalez-Marcos, A. Biometric Identification through hand geometry measurements. IEEE. T. on Pattern Analysis and Matching Intelligence. Vol. 22, No 10. Oct. 200, pp. 1168-1171. [8] Celoxica Ltd. www.celoxica.com [9] Xilinx www.xilinx.com

Вам также может понравиться

- From Prognostics and Health Systems Management to Predictive Maintenance 2: Knowledge, Reliability and DecisionОт EverandFrom Prognostics and Health Systems Management to Predictive Maintenance 2: Knowledge, Reliability and DecisionОценок пока нет

- Smart Camera: Revolutionizing Visual Perception with Computer VisionОт EverandSmart Camera: Revolutionizing Visual Perception with Computer VisionОценок пока нет

- Smart Card Implementation: Biometric Techniques AttemptedДокумент5 страницSmart Card Implementation: Biometric Techniques Attemptedsubu100Оценок пока нет

- Iris V9Документ26 страницIris V9arakhalОценок пока нет

- New Approach To Similarity Detection by Combining Technique Three-Patch Local Binary Patterns (TP-LBP) With Support Vector MachineДокумент10 страницNew Approach To Similarity Detection by Combining Technique Three-Patch Local Binary Patterns (TP-LBP) With Support Vector MachineIAES IJAIОценок пока нет

- (IJCT-V2I4P12) Authtors :swapnali G. Garud, Ravindra A. NikamДокумент6 страниц(IJCT-V2I4P12) Authtors :swapnali G. Garud, Ravindra A. NikamIjctJournalsОценок пока нет

- An Embedded Finger Vein Recognition SystemДокумент5 страницAn Embedded Finger Vein Recognition SystemInternational Journal of Research in Engineering and TechnologyОценок пока нет

- Design A Biometric Identification System Based On The Fusion of Hand Geometry and Backhand Patterns Raid R. Al-NimaДокумент12 страницDesign A Biometric Identification System Based On The Fusion of Hand Geometry and Backhand Patterns Raid R. Al-Nimamais taherОценок пока нет

- Multispectral Palmprint Recognition Using Wavelet-Based Image FusionДокумент8 страницMultispectral Palmprint Recognition Using Wavelet-Based Image Fusionsaran52_eceОценок пока нет

- Palmprint Identification Using Feature-Level Fusion: Adams Kong, David Zhang, Mohamed KamelДокумент10 страницPalmprint Identification Using Feature-Level Fusion: Adams Kong, David Zhang, Mohamed KamelSally SamehОценок пока нет

- IOT-Assignment 2 PDFДокумент5 страницIOT-Assignment 2 PDFQusai KHОценок пока нет

- 2011 Springer FKP MeraoumiaДокумент11 страниц2011 Springer FKP MeraoumiaRitu JangraОценок пока нет

- Vision Based Gesture Recognition Systems - A SurveyДокумент4 страницыVision Based Gesture Recognition Systems - A SurveyInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- J. Vis. Commun. Image R.: Bee Yan Hiew, Andrew Beng Jin Teoh, Ooi Shih YinДокумент13 страницJ. Vis. Commun. Image R.: Bee Yan Hiew, Andrew Beng Jin Teoh, Ooi Shih YinRahul AlwalОценок пока нет

- Design and VLSI Implementation of High-Performance Face-Detection Engine For Mobile ApplicationsДокумент2 страницыDesign and VLSI Implementation of High-Performance Face-Detection Engine For Mobile ApplicationsArjun0607Оценок пока нет

- Alphanumeric Recognition Using Hand Gestures: Shashank Krishna Naik, Mihir Singh, Pratik Goswami, Mahadeva Swamy GNДокумент7 страницAlphanumeric Recognition Using Hand Gestures: Shashank Krishna Naik, Mihir Singh, Pratik Goswami, Mahadeva Swamy GNShashank Krishna NaikОценок пока нет

- Content 5d2Документ17 страницContent 5d2Kiranmai DindigalaОценок пока нет

- Voter Authentication System Using Feature Level Fusion of Iris, Face and PalmprintДокумент10 страницVoter Authentication System Using Feature Level Fusion of Iris, Face and PalmprintIJRASETPublicationsОценок пока нет

- A Genetic Algorithm Based Approach For Segmentingand Identifying Defects in Glass BottlesДокумент9 страницA Genetic Algorithm Based Approach For Segmentingand Identifying Defects in Glass BottlesAJER JOURNALОценок пока нет

- Gesture Recognition of Handwritten Digit Using Accelerometer Based Digital PenДокумент5 страницGesture Recognition of Handwritten Digit Using Accelerometer Based Digital PenInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- A Human Iris Recognition Techniques To Enhance E-Security Environment Using Wavelet TrasformДокумент8 страницA Human Iris Recognition Techniques To Enhance E-Security Environment Using Wavelet Trasformkeerthana_ic14Оценок пока нет

- A Distributed Computer Machine Vision System For Automated Inspection and Grading of FruitsДокумент4 страницыA Distributed Computer Machine Vision System For Automated Inspection and Grading of FruitsMekaTronОценок пока нет

- Research Article Image Processing Design and Algorithm Research Based On Cloud ComputingДокумент10 страницResearch Article Image Processing Design and Algorithm Research Based On Cloud ComputingKiruthiga PrabakaranОценок пока нет

- Personal Authentication Using 3 D Finger GeometryДокумент10 страницPersonal Authentication Using 3 D Finger GeometryShabeer VpkОценок пока нет

- V. (PP 25-28) ABDUL Manan - Implementation of Image Processing Algorithm On FPGA - 24.2.11Документ5 страницV. (PP 25-28) ABDUL Manan - Implementation of Image Processing Algorithm On FPGA - 24.2.11Nguyen Tuong ThanhОценок пока нет

- Applied Sciences: Application Research of Improved YOLO V3 Algorithm in PCB Electronic Component DetectionДокумент21 страницаApplied Sciences: Application Research of Improved YOLO V3 Algorithm in PCB Electronic Component DetectionMiftОценок пока нет

- Background Differencing Algorithm For Moving Object Detection Using System Generator HWSW Co-SimulationДокумент4 страницыBackground Differencing Algorithm For Moving Object Detection Using System Generator HWSW Co-SimulationInternational Journal of Research in Engineering and TechnologyОценок пока нет

- Journal - A Smart Attendance System Based On Face Recognition Challenges and EffectsДокумент6 страницJournal - A Smart Attendance System Based On Face Recognition Challenges and EffectsAbdulkadir Shehu bariОценок пока нет

- Procesos InglesДокумент5 страницProcesos InglesMaye CastroОценок пока нет

- Towards More Accurate Iris Recognition System by Using Hybrid Approach For Feature Extraction Along With ClassifierДокумент12 страницTowards More Accurate Iris Recognition System by Using Hybrid Approach For Feature Extraction Along With ClassifierIJRES teamОценок пока нет

- A Simple Technique For Palm Recognition Using MajoДокумент6 страницA Simple Technique For Palm Recognition Using MajoAayuОценок пока нет

- Computer Vision CS-6350: Prof. Sukhendu Das Deptt. of Computer Science and Engg., IIT Madras, Chennai - 600036Документ48 страницComputer Vision CS-6350: Prof. Sukhendu Das Deptt. of Computer Science and Engg., IIT Madras, Chennai - 600036Nadia F Mohammad Al-RoshdeeОценок пока нет

- Face Identification Using Kinect Technology: Ana-Andreea Nagâţ, Cătălin-Daniel CăleanuДокумент4 страницыFace Identification Using Kinect Technology: Ana-Andreea Nagâţ, Cătălin-Daniel Căleanuworldofd12Оценок пока нет

- Elbeqqal 2018Документ9 страницElbeqqal 2018Dickson Scott Rosales CanoОценок пока нет

- Image Processing by Digital Filter Using MatlabДокумент7 страницImage Processing by Digital Filter Using MatlabInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- International Journal of Computational Engineering Research (IJCER)Документ7 страницInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)Оценок пока нет

- Official Voting System ForДокумент12 страницOfficial Voting System ForCS & ITОценок пока нет

- Palm Verification Using Sift and Majority Voting Based KNNДокумент4 страницыPalm Verification Using Sift and Majority Voting Based KNNPasindu AbeysunderaОценок пока нет

- Multi 20 SensorДокумент9 страницMulti 20 SensorMemory KambaОценок пока нет

- Finger Vein Identification System Using Capsule Networks With Hyperparameter TuningДокумент8 страницFinger Vein Identification System Using Capsule Networks With Hyperparameter TuningIAES IJAIОценок пока нет

- Computer Integerated Apparel Manufacturing: Fault Analysis Using Image Processing TechniqueДокумент28 страницComputer Integerated Apparel Manufacturing: Fault Analysis Using Image Processing TechniqueMadhu MathiОценок пока нет

- Stereo Video Processing For Depth Map: Harlan Hile and Colin ZhengДокумент8 страницStereo Video Processing For Depth Map: Harlan Hile and Colin Zhengajnabee4u18100% (2)

- Rfid Based Electronic PassportДокумент6 страницRfid Based Electronic PassportIjsrnet EditorialОценок пока нет

- 109 - IOT and E Glove Based Nurse Calling SystemДокумент7 страниц109 - IOT and E Glove Based Nurse Calling SystemPavan Yashoda PkОценок пока нет

- Enabling Fingerprint Authentication in Embedded Systems For Wireless ApplicationsДокумент11 страницEnabling Fingerprint Authentication in Embedded Systems For Wireless Applicationspatilrahul100% (2)

- Hand Gesture Recognition in Images and Video: Ilan Steinberg, Tomer M. London, Dotan Di CastroДокумент21 страницаHand Gesture Recognition in Images and Video: Ilan Steinberg, Tomer M. London, Dotan Di CastroSukh VirОценок пока нет

- ThesisДокумент51 страницаThesisPROJECT POINTОценок пока нет

- Fingerprint Image Enhancement: Iterative Fast Fourier Transform Algorithm and Performance EvaluationДокумент10 страницFingerprint Image Enhancement: Iterative Fast Fourier Transform Algorithm and Performance EvaluationProdi Tmj-pnlОценок пока нет

- Viola Jone's AlgorithmДокумент25 страницViola Jone's AlgorithmAkhil AhujaОценок пока нет

- Surveillance Robot For Tracking Multiple Moving TargetsДокумент7 страницSurveillance Robot For Tracking Multiple Moving Targetspurushothaman sinivasanОценок пока нет

- FPGA Based Area Efficient Edge Detection Filter For Image Processing ApplicationsДокумент4 страницыFPGA Based Area Efficient Edge Detection Filter For Image Processing ApplicationsAnoop KumarОценок пока нет

- Assignment 1 NFДокумент6 страницAssignment 1 NFKhondoker Abu NaimОценок пока нет

- 3.KRS036 Final SubmissionДокумент6 страниц3.KRS036 Final SubmissionAravind MikeОценок пока нет

- Final Project PosterДокумент1 страницаFinal Project Posterapi-297515479Оценок пока нет

- Image Processing Technique For Ac Motor Speed ControlДокумент6 страницImage Processing Technique For Ac Motor Speed ControlUtkarsh VermaОценок пока нет

- Zone Theory Applied To Boost Recognition Rate of HMM Based SystemДокумент7 страницZone Theory Applied To Boost Recognition Rate of HMM Based SystemInternational Association of Scientific Innovations and Research (IASIR)Оценок пока нет

- Human Activity Recognition Based On Time Series Analysis Using U-NetДокумент21 страницаHuman Activity Recognition Based On Time Series Analysis Using U-NetEzequiel França Dos SantosОценок пока нет

- PDF/JCSSP 2012 528 532Документ5 страницPDF/JCSSP 2012 528 532mohitegaurv87Оценок пока нет

- Multimodal Biometric Authentication System Using Hand Shape, Palm Print, and Hand GeometryДокумент14 страницMultimodal Biometric Authentication System Using Hand Shape, Palm Print, and Hand GeometryKarama AbdelJabbarОценок пока нет

- Development of Palmprint Verification System Using BiometricsДокумент13 страницDevelopment of Palmprint Verification System Using BiometricsAkash HulkodОценок пока нет

- Automation TestingДокумент20 страницAutomation TestingmaryamОценок пока нет

- Social Media CompetencyДокумент2 страницыSocial Media CompetencyNoah OkitoiОценок пока нет

- Denon Home Theater Sys 5 1 Avr x500Документ2 страницыDenon Home Theater Sys 5 1 Avr x500D_D_76Оценок пока нет

- Protocol Padlet - Online Projects 2020Документ2 страницыProtocol Padlet - Online Projects 2020api-284373535Оценок пока нет

- UZZ32 Suspension Codes PDFДокумент32 страницыUZZ32 Suspension Codes PDFAdel Sta MariaОценок пока нет

- Commutation Circuits SCR PDFДокумент2 страницыCommutation Circuits SCR PDFRhondaОценок пока нет

- Satyam Eye Hospital - Google SearchДокумент1 страницаSatyam Eye Hospital - Google SearchRajeshwar GargeОценок пока нет

- 2023-24 S.Y. B.sc. ElectronicsДокумент14 страниц2023-24 S.Y. B.sc. Electronicsanil sonawaneОценок пока нет

- Online Recruitment SystemДокумент42 страницыOnline Recruitment SystemTanmay Abhijeet74% (19)

- Skill Builder 3 S14Документ3 страницыSkill Builder 3 S14daneshnedaieОценок пока нет

- Essentials of Rational Clearcase Module 7: Integrating Parallel DevelopmentДокумент28 страницEssentials of Rational Clearcase Module 7: Integrating Parallel DevelopmentmnreddyОценок пока нет

- The 8086 BookДокумент619 страницThe 8086 BookFathi ZnaidiaОценок пока нет

- Bess 1Документ180 страницBess 1dan_geplОценок пока нет

- Wireless Communication Networks and Systems 1st Edition Beard Solutions ManualДокумент11 страницWireless Communication Networks and Systems 1st Edition Beard Solutions ManualHasnin shah0% (1)

- Basic of SoundДокумент54 страницыBasic of SoundRoslina Jaafar75% (4)

- Summer 2016 Model Answer Paper PDFДокумент24 страницыSummer 2016 Model Answer Paper PDFDeepali Bhaskar KarandeОценок пока нет

- Bts3900 v100r010c10spc255 Enodeb FDD UpgДокумент38 страницBts3900 v100r010c10spc255 Enodeb FDD UpgJennis Sherano FernandoОценок пока нет

- DS ANT TNA352A33rДокумент3 страницыDS ANT TNA352A33rEdelОценок пока нет

- 8 K C3 I ScrimДокумент6 страниц8 K C3 I ScrimJoshua WatrousОценок пока нет

- Platform Size 350x350 MM: Easy System IntegrationДокумент4 страницыPlatform Size 350x350 MM: Easy System IntegrationHuy VũОценок пока нет

- Psur-Sscp UnterschiedeДокумент14 страницPsur-Sscp UnterschiedewОценок пока нет

- H1 Bent-Axis Motor: Customer / ApplicationДокумент1 страницаH1 Bent-Axis Motor: Customer / ApplicationRodrigues de OliveiraОценок пока нет

- Canada Product Line Guide: Heliforklift - CaДокумент48 страницCanada Product Line Guide: Heliforklift - CaRS TZ100% (1)

- CC1 - AssignmentДокумент1 страницаCC1 - AssignmentAssiah AndreaОценок пока нет

- D1 - ModBus Device Importer - LABДокумент11 страницD1 - ModBus Device Importer - LABGonzo MelaoОценок пока нет

- Xds510pp PlusДокумент30 страницXds510pp PlusgarriyakОценок пока нет

- Security Specialization Sample Exam - ENДокумент8 страницSecurity Specialization Sample Exam - ENbloodscreamОценок пока нет

- Electric Motor 7Документ84 страницыElectric Motor 7abdulkadhirОценок пока нет

- Sample On The Job Training Weekly Report 1Документ1 страницаSample On The Job Training Weekly Report 1Jerrick Wayne VertudazoОценок пока нет

- Pic 16F84Документ12 страницPic 16F84Ingwaar RosensonОценок пока нет