Академический Документы

Профессиональный Документы

Культура Документы

MTech ECE (Microelectronics & VLSI Designs) Comm Detail Syllabus 2010

Загружено:

jagannath_stud83Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MTech ECE (Microelectronics & VLSI Designs) Comm Detail Syllabus 2010

Загружено:

jagannath_stud83Авторское право:

Доступные форматы

M.Tech.

- ECE (Microelectronics & VLSI Designs) Common Syllabus

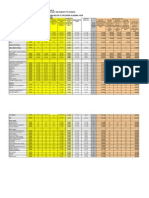

Semester 1: Paper Paper Type Code

Paper Name L 3 4 4 4 4

Instruction Hours T 1 0 0 0 0 P 0 0 0 0 0 4 4 4 4 4

Credit

C-Th MVLSI Advanced Engg Maths 101 C-Th MVLSI VLSI Device & Modelling 102 C-Th MVLSI Digital IC Design 103 C-Th MVLSI Microelectronic Technology & IC 104 Fabrication E-Th MVLSI 105A 105B 105C 105D Elective I: 1. Bioelectronic System 2. Embedded System Fundamentals 3. AI & Neural Networks 4. Advanced Digital Communication Total of Theory C-Pr MVLSI CAD Tools for VLSI Design 191 E-Pr MVLSI 192A 1. Microelectronic Technology 192B 2. Embedded Systems Total of Practical S MVLSI Seminar 181 Total

19 0 0

1 0 0

0 3 3

20 2 2

0 0 19

0 2 3

6 0 6

4 1 25

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Semester 2:

Paper Type C-Th C-Th C-Th E-Th Paper Code MVLSI 201 MVLSI 202 MVLSI 203 MVLSI 204A 204B 204C 204D MVLSI 205A 205B 205C 205D 205E Paper Name L Processor Architecture for VLSI Digital Signal Processing & Aplications Analog IC Design Elective II: 1. Quantum & Nano-science 2. Error Control & Coding 3. Sensors 4. Physical Design & Testing Elective III: 1. RF Circuits & Systems 2. Low Power VLSI Design 3. Mobile Communication 4. Advanced Micro & Nano Devices 5. Advanced FET Technology Total of Theory E-Pr MVLSI 291A 291B 1. Microelectronic Technology 2. Embedded Systems Total of Practical S V MVLSI 281 MVLSI 282 Term paper leading to Thesis Comprehensive Viva Voce Total credit Semester 3: Paper Paper Type Code C-Th MVLSI 381A 381B MVLSI 302/392 20 1 3 0 0 0 1 3 0 2 1 4 27 4 4 4 4 Instruction Hours T 0 0 0 0 P 0 0 0 0 4 4 4 4 Credit

E-Th

20 0

0 0

0 3

20 2

Paper Name L 4 1. Project Management or 2. Teaching & Reseach Methodologies Elective Theory or Practical Papers to be suggested by College. Total of Theory 4 8 0

Instruction Hours T 0 P 0 4

Credit

AETh/Pr

0 0 2

0 0 0

4 4+4 1 25

MVLSI 383

Dissertation Part I Total of Credit

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Semester 4: Paper Paper Type Code S MVLSI 481 MVLSI 482

Paper Name L Dissertation Part II (Completion) Post submission defence of dissertation Total of Credit 24

Instruction Hours T P 6 18 24

Credit

Details: VL SI De vi c e s & M o del l in g [ Se m - 1] 3 ( L ) ( 4 0 l ect ure s ) P r e- r e q ui si te : K n ow l e d g e of ba si c p h ys ic s of di o de s, B J Ts, FE Ts, MO S st r uc t ur e s. Se m ic o n d u c t or s, J u nc ti o n s a n d MO S FE T O ve r vi e w: I n tr od u c ti on , S e mi c on d u c t or s, C on d u c ti on , C on t ac t P ot e n ti al s, P- N J u nc ti on , O ver vi e w of t he MO S Tr a nsi st or. B a si c De vi c e P h ys ic s: Tw o Ter m i na l MO S Str u ct ur e : Flat - ba n d v ol ta g e, P ote nt ia l bal a nce & c ha rge ba la n c e, E ff e c t of Ga t e- su bs tr a te v ol ta ge o n s ur fa ce c on d i ti on , In v e r si on , Sma ll si gn a l ca p aci ta nc e; T hr ee Te r mi n al MO S Str uc t u re : C on ta c t i n g t he i n ver si on l a ye r, B od y eff ect , Re gi on s o f i n ve r si on , P i nc h- off v ol ta ge ; F ou r Te r m i na l MO S Tr a n sis t or : Tr a n si st o r r e g i on s of op er at i on , ge n e r al c h ar ge s hee t m od e l s , r e gi on s of i n ver s i on i n ter m s of ter m i nal v ol t a ge , st r on g i n ve r si on , wea k i n ver s i on , m od e r a te i n ve r si on , i nt er p ola ti on m od e l s, eff ec ti ve m ob ili t y, te m p er a t ure eff ect s, bre a kd ow n p- c h a n ne l M OS FE T, e n h a nc e m e nt a n d de pl et i on t yp e , mod e l par a me te r va l ue s, m o de l a cc ura c y e tc; S ma ll d i me n si on eff e ct s: c ha n ne l l e n gt h mo d u l ati on , b ar r i er l ow er i n g, tw o di m e n si on a l c h a rge s har i n g a n d t hr e s h ol d v ol ta ge , p u n c h-t hr ou gh , car r ier v e l oc it y sat ur a ti on , h ot ca r r ie r e ff e ct s, sca li n g, eff ec t s of sur f ace a n d dr a i n se ri e s r es is ta nc e , eff ec t s d u e t o t h i n ox i de s a n d hi gh d o p i n g. S u b t hr es h ol d r e gi o n s. C MO S De vic e D esi g n : S cal i n g, Thr e sh ol d v ol ta g e, MOSFE T c h a n ne l l e n gt h ; C MO S Pe rf or m a nce Fa ct or s: B as ic C M OS c ir c u it el e me n ts; pa r a si tic e le m e nt s ; se n si t i vi t y o f C MO S de la y t o de vi c e p ar a me te r s; p er f or m a nce f act or s of a d v a nc e d C MOS d e vi ce s. B i p ol ar De vi ce s, De s i gn & P er f or ma n c e: O ut c ome : St u d e nt w il l be a b le t o m od e l de vi c es a n d st u d y t h eir pe rf or m a nce i n a na l o g a n d d i gi t al, c ir c ui ts . As si gn me nt : Si m ple Cir cu it si m ul at i on u si n g Sp ic e. Text: Fundamentals of Modern VLSI Devices by Yuan Taur & Tak H. Ning (Cambridge) The MOS Transistor (second edition) Yannis Ts i vi di s ( Ox f or d) R ef er e nc e : CM O S An al o g C irc uit De si gn ( se c on d e di ti o n) Phi ll ip E. Al le n a n d D o ugl a s R. H o l be r g ( O xf or d) Di g it al I C D esi gn [ Se m 1] 3 ( L ) 1( T) 2 ( P ) Prerequisite: Overview of CMOS VLSI fabrication, CMOS process steps; fabrication; yield; design rules for custom layout; Layout - hand layout, graphical layout, low-level language; design rule checking; stick diagrams; placement of cells; simulation of design; function generation from masks; test pattern generation; structured design methodology for VLSI; hierarchical design techniques and examples. Concept of Mask design, Mask layout, Stick diagram, Standard cell Vs Custom design, 1. Specification Methods: Language based methods including VHDL/Verilog, hierarchical state machine

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

descriptions such as State Charts, and Petri net based methods. Functional languages for formal verification. (Laboratory Practises: RTL description of combinational and sequential circuits using Verilog/VHDL and simulation of the designs using open source and propietary softwares) Synthesis tools: High level synthesis; Scheduling allocation, communication and control.(Laboratory Practises : Synthesis of the RTL designs using an industry standard synthesis tool and power and timing analysis of the synthesised designs) Module Generation: Finite State machines, state encoding, parameterised blocks PLA, RAM, ROM generation. Gate Level Synthesis; Binary Decsision Diagrams, Logic minimisation, optimisation and retargetting.(Laboratory Practises : Simulation and Synthesis of finite state machines) Layout Synthesis: Placement; simulated annealing, genetic algorithms, constructive methods. routing; nets, layers, Lees algorithms, cost functions, channel routing. Examples of a channel router with placement expansion. Case Study: Synthesis of a chosen algorithm to the gate level using CAD tools. (Laboratory Practices ) Case Study Lecture: Design of MSI chip using proprietary CAD system; use of circuit description language; layout considerations. (Laboratory Practises : A complete VLSI design example : from RTL to GDSII) 6.Complex gates: pseudo NMOS; dynamic logic; dynamic cascaded logic; domino logic; 2 and 4 phase logic; pass transistor logic. Control and timing; synchronous and asynchronous; self-timed systems; multi-phase clocks; register transfer; examples of ALU, shifters, and registers. (Laboratory Practises: Schematic and layout creation of basic and complex gates based on different design libraries). E m er gi n g c on c e pt s: S yn c hr on i se r s a n d ar bei te r s, n e tw or ks on a c h i p. Effects of scaling circuit dimensions: physical limits to develop fabrication. Optional extended course work for final year students, using VLSI design software to produce a chip to meet a given specification; the chip may be fabricated if the design is successful. To study the different stages in the design of integrated chip using VLSI design software. The design is to meet a given specification.

2.

3.

4.

5.

6.

7.

Reading List 1. CAD for VLSI: Author: Russell, G, Kinniment, D.J., Chester, E.G., and McLauchlan, M.R. Notes: Van Norstrand Rheinhold, 1985. 2. Tutorial on High Level Synthesis Author: McFarland, M.C., Parker, A.C and Camposano R Notes: Proc 25th ACM/IEEE Design Automation Conf pp330-336 3. CMOS VLSI Design A Cir c ui t s a n d S ys t e ms Pe rs pe c ti ve ( 3r d E di ti on ) A ut h or Ne il We ste a n d David Harris Microelectronics Technology & IC Fabrication: 3(L) (40 lectures) Cleanroom technology - Clean room concept Growth of single crystal Si, surface contamination, cleaning & etching. (Laboratory Practices : Cleaning of p-type & n-type Si-wafer by solvent method & RCA cleaning) Oxidation Growth mechanism and kinetic oxidation, oxidation techniques and systems, oxide properties, oxide induced defects, charactrisation of oxide films, Use of thermal oxide and CVD oxide; growth and properties of dry and wet oxide, dopant distribution, oxide quality; (Laboratory Practices : Fabrication of MOS capacitor) Solid State Diffusion Fick's equation, atomic diffusion mechanisms, measurement techniques, diffusion in polysilicon and silicon di-oxide diffusion systems. Ion implantation Range theory, Equipments, annealing, shallow junction, high energy implementation. Lithography Optical lithography, Some Advanced lithographic techniques. Physical Vapour Deposition APCVD, Plasma CVD, MOCVD. Metallisation - Different types of metallisation, uses & desired properties.(Laboratory Practices : Metallisation & Schottky diode fabrication) VLSI Process integration. (3+3+3+3+3+3+3+3+3+3+3+3+4 = 40 hrs theory) Reading List 8. Semiconductor Devices Physics and Technology, Author: Sze, S.M.; Notes: Wiley, 1985 9. An Introduction to Semiconductor Microtechnology, Author: Morgan, D.V., and Board, K 10. The National Technology Roadmap for Semiconductors , Notes: Semiconductors Industry Association, SIA, 1994 11. Electrical and Electronic Engineering Series VLSI Technology, Author: Sze, S.M. Notes: Mcgraw-Hill International Editions

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Electives: Embedded Systems Fundamentals Introduction to embedded systems: Concept, Difference between embedded computer systems and general purpose computer Systems, Classification, Characteristics, Applications Overview of Embedded Processors: Classification: GPP, ASIP, SPP, ASSP, MULTI-CORE, SOFT-CORE -Examples Overview of Embedded Memories & Interfacing: SRAM, DRAM, EEPROM, FLASH, DUAL-PORT, CACHE, INTERLEAVED MEMORIES Overview of Embedded Networking & Standards: RS232, RS485, SPI, USB, ISA, PCI, I2C, CAN, LIN IrDA, Bluetooth, Zigbee. Overview of Embedded Sensors and Transducers: Pressure, Temperature, Acceleration, Image, Rain, Proximity, Hall-effect, Artificial eyes Overview of I/P-O/P devices & Interfacing Keypad, TWS, JoyStick, SSL, LCD, VGA Case study: The Weather Station Advanced digital communication Pre-requisites: o Fourier Expansion, Fourier transform, Normalized power spectrum, Power spectral density, Effect of transfer function on output power spectral density, Persevals theorem. o Autocorrelation & cross correlation between periodic signals, cross correlation power. o Relation between power spectral density of a signal, its autocorrelation function and its spectrum. o Distinction between a random variable and a random process. o Probability, sample space, Venn diagramme, joint probability, bays theorem, cumulative probability distribution function, probability density function, joint cumulative probability distribution function, joint probability density function. o Mean/average/expectation of a random variable and of sum of random variables. o Standard deviation, variance, moments of random variables, - explanation with reference to common signals. o Tchebycheffs inequality. o Gaussian probability density function error function & Q function o Central limit theorem. Spectral analysis of signals: o Orthogonal & orthonormal signals. Gram-Schmidt procedure to represent a set of arbitrary signals by a set of orthonormal components; - numerical examples. o The concept of signal-space coordinate system, representing a signal vector by its orthonormal components, measure of distinguishability of signals. Characteristics of random variables and random processes: o Common probability density functions, - Gaussian, Rayleigh, Poisson, binomial, Rice, Laplacian, lognormal, etc. o Probability of error in Gaussian Binary symmetric channel. o Random processes time average, ensemble average, covariance, autocorrelation, cross correlation, stationary process, ergodic process, wide sense stationary process. o Power spectral density and autocorrelation, power spectral density of a random binary signal. o Linear mean square estimation methods. Revision of source coding: Sampling theorem, instantaneous/ flat top/ natural sampling, band width of PAM signal,

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

quantization, quantization noise, principle of pulse code modulation, delta modulation & adaptive delta modulation. Parametric coding/ hybrid coding/ sub band coding: APC, LPC, Pitch predictive, ADPCM, voice excited vocoder, vocal synthesizer. Line codes: o UPNRZ, PNRZ, UPRZ, PRZ, AMI, Manchester etc. o Calculation of their power spectral densities. o Bandwidths and probabilities of error Pe for different line codes. Revision of digital modulation: Principle, transmitter, receiver, signal vectors, their distinguish ability (d) and signal band width for BPSK, QPSK, M-ARY PSK, QASK, MSK, BFSK, M-ARY FSK. Spread spectrum modulation: o Principle of DSSS, processing gain, jamming margin, single tone interference, principle of CDMA, MAI and limit of number of simultaneous users. o Digital cellular CDMA system: model of forward link, reverse link, error rate performance of decoder using m-sequence chip codes. o Properties of m-sequences, their generation by LFSR, their PSDs, limitations of m-sequences. o Gold sequence, Kasami sequence generating the sequences, their characteristic mean, cross correlation and variance of cross correlation, their merits and limitations as chip codes in CDMA. Multiplexing & multiple access: o TDM/TDMA, FDM/FDMA, Space DMA, Polarization DMA, OFDM, ALOHA, Slotted ALOHA, Reservation ALOHA, CSMA-CD, CSMA-CA basic techniques and comparative performances e.g. signal bandwidth, delay, probability of error etc. Noise: o o o o

Representation of noise in frequency domain. Effect of filtering on the power spectral density of noise Low pass filter, band pass filter, differentiating filter, integrating filter. Quadrature components of noise, their power spectral densities and probability density functions. Representation of noise in orthogonal components.

Characteristics of different types of channels: o Gaussian, Poisson etc.

Band limited channel: o Characteristics of band limited channel, inter symbol interference (ISI) - its mathematical expression. o Niquists theorem for signal design for no ISI in ideal band limited channel, Niquists criteria, raised cosine pulse signals. o Signal design for controlled ISI in ideal band limited channel, partial response signals, duobinary & partial duobinary signals - their methods of generation and detection of data. o Concept of maximum likelihood detection, log likely hood ratio. o Detection of data with controlled ISI by linear transverse filters. o Performance of minimum mean square estimation (MMSE) detection in channels with ISI.

Base band signal receiver and probabilities of bit error: o Peak signal to RMS noise output ration, probability of error. o Optimum filter, its transfer function. o Matched filter, its probability of error. o Probability of error in PSK, effect of imperfect phase synchronization or imperfect bit synchronization. o Probability of error in FSK, QPSK. o Signal space vector approach to calculate probability of error in BPSK, BFSK, QPSK.

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

o o Relation between bit error rate and symbol error rate. Comparison of various digital modulation techniques vis--vis band width requirement and probabilities of bit error.

Text Books: 1. Digital communication, 4th ed. - J. G. Proakis, MGH International edition. 2. Principle of Communication Systems Taub, Schilling, TMH 3. Digital and Analog Communication Systems, 7th ed. Leon W. Couch, PHI. 4. Principles of Digital Communication Haykin 5. Digital Communication Zeimer, Tranter. 6. Principle of Digital communication - J. Das, S. K. Mallick, P. K Chakraborty, New Age Int. 7. Communication Systems, 4th ed. A. Bruce Carlson, Paul B. Crilly, Janet C. Rutledge, MGH International edition. 8. Digital Communications, 2nd ed. Bernard Sklar, Pearson Education. 9. Electronic Communications, 4th ed. Dennis Roddy, John Coolen, PHI Processor Architecture for VLSI Fundamentals: Components of (an embedded) computer, Architecture organization, Von-Neumann vs Harvard, Microcoded vs hardwired, scalar and vector processors, Flynns taxonomy CISC arch, the RISC movement, ISA arch, basic structure, pipelining, pipeline hazards and solutions, comparison, merging RISC and CISC: the microchip PIC Superscalar arch: parallel computation, Ways of parallelism, the IBM PowerPC The DSP and Its Impact on Technology: Why a DSP is different. The evolving architecture of a DSP VLIW arch: the TI TMS320C6x, advancement to EPIC Coprocessor Approach: Need for accelerators, Accelerators and different types of parallelism, Processor architectures and different approaches to acceleration General-Purpose Embedded Processor Cores: The ARM Processors using course-grain parallelism: utilization of course-grain parallelism, chip-multiprocessors, multithreaded processors, SMT proc Customizable Processors and Processor Customization: A benefits analysis of processor customization, Using microprocessor cores in SOC design, Benefiting from microprocessor extensibility, how microprocessor use differs between SOC and board-level design Run-Time Reconfigurable Processors: Embedded microprocessor trends, Instruction set metamorphosis, Reconfigurable computing, Run-time reconfigurable instruction set processors, Coarse-grained reconfigurable processors Stream Multicore Processors: Introduction, Raw architecture overview Asynchronous and Self-Timed Processor: Motivation for asynchronous design, The development of asynchronous processors,

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Ana l o g IC De si g n: [ Se m II] 3( L ) 0 T) 0( P ) 3 Lec ture s Recapitulation: 12. CMOS models for analog circuits - Small signal equivalent circuit, temperature effect and sensitivity, overview of electrical noise. 2L 13. Analog subcircuits : CMOS switch, resistors, current source, sink, current mirror, voltage and current references. 2L 14. MO S FET M od e ll i n g f or Cir c ui t Si m u la ti on : 2 L (Assignment using Spice) 3. C MO S A m pli f ie rs & C MO S O pe rat i o n A m plif i e rs: Ba sic c on c e p ts , P er f or m a nc e Pa r a me t er s, O ne sta te OPA MP, Tw o st a ge OPA MP, Sta b il it y a n d P ha s e c omp e n s at i o n , Ca sc o d e O PA MP, De si g n o f t w o- st a ge a n d Ca sc od e OPA MP, SP I C E si m u la ti on of A m p lif i er, Hi gh p er f o r m a nc e C MO S OPA MP s, Micr op ow er OPA MP, 6 L + 6P * De si g n e xa m p le s, ( S PI CE s i mu l at i o n L a b or at or y ) 2. Switch Capacitor circuits: Gen er a l c on si d er at i on s , S wit c he d c a pa c it or i nt e gr a t or s, Fi r st a n d se c n d or d e r swi t c h e d c a p ac i t or f il ter c ir c ui ts, 2 L+ 3P * De si g n e xa m p le s, ( S PI CE s i mu l at i o n L a b or at or y ) 3. D ata C o nve rt e r F und a m enta l s & Arc h ite ct ure : I d eal D/ A c on ver ter s, I de a l A /D c on ver te r, Se r i al a n d Fla s h D/ A c on ver ter s a n d A /D c on ver te r s, Me di u m a n d H i gh Sp e e d c on ve r ter s, O ver- sa m p l i n g c o n v er te r s, per f or m a nc e li m it at i on s , De s i gn c on s i der at i o n , SP I C E si m u la ti o n . 4L 4. Spe c i al C irc ui ts : C M OS v ol ta ge c on t r ol le d os cil la t ors , R i n g os ci ll a t o rs, P ha se l oc ke d l o op s wit h p u m p p ha se c omp a r a t or s, Gm- C Ci r c ui t s. * De si g n e xa m p le s, ( S PI CE s i mu l at i o n L a b or at or y ) 4 L+ 6P 5. R F A na l o g C ir c ui t s & S u bc ir c ui t s: C a pac it or s a n d In d u c t or s i n V LS I cir c ui ts , Ba n d wi d t h est i ma t i on te c h ni q u e s, De si gn of h i gh f re q u e nc y a m p li f ier s, De si gn of l ow n oi s e a m p lif ier s, De si g n of Mi xer s o f R F p ow e r a mpl i fi er s, Ar ch it ec t u r e s o f r f r e c ei v er s a n d tr a n s mi tt er s. 6L 6 . Ca m p ar a t or s : C har ac t er i sa ti on , Tw o st a te op e n l o o p c o mp a ra t or s, Di scr e te t i me c om p ar at or s, hi g h sp e e d c om p ar a t or c ir c ui t s, C MOS S /H c ir c u it s, 4L * De si gn e xa m p le s, ( S PI CE s i mu l at i o n L a b or at ory ) Text: The MOS Transistor (second edition) Yannis Tsi vi di s ( O xf or d) R ef er e nc e : CM OS A nal o g C irc uit De si g n ( sec on d e d it i on ) Ph il li p E. Al le n an d D o u gl a s R. H o lb er g ( Oxf or d) Intended Knowledge Outcomes Understand the main elements of hierarchical VLSI design namely interested circuit technology, approaches to system design, architectural issues, design implementation and layout. The ability to analyse the effect of future integrated circuit technologies on device parameters. Intended Skill Outcomes Ability to apply VLSI design methodology for the design of Application Specific Integrated Circuits. Reading List 1. Principles of CMOS VLSI Design (Essential reading) Author: Weste N and Eshraghian K Notes: Addision Wesley 1985 2. Introduction to NMOS and CMOS VlSI Systems Design (Essential reading) Author: Mukherjee A Notes: Prentice-Hall 1986 3. Introduction to VLSI Systems (Essential reading) Author: Mead and Conway Notes: Addison Wesley D C & Co

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

AI & Neural Networks Overview of AI - Introduction, hierarchical perspective and foundations. Problems of AI, AI techniques , Tic-Tac-Toe problem. Basic problem solving methods: Production systems-State space search-Control strategies- Heauristic search techniques-Forward and backward reasoning-Hill climbing techniques-Best search. Knowledge representation: Predicate logic- Resolution Question answering-Nonmonotic reasoning-Statistical and probabilistic reasoning-Semantic nets-Frames -Scripts. Neural Network: Biological neurons and brain, mathematical models of neuron, basic structure of a neural network, Learning rules, ANN training, back propagation algorithm, Hopfield nets and application of Neural Network. Introduction to expert system-Design of an expert system-Fuzzy logic and neural network in control system, modeling estimation and design methodologies and real time application of Intelligent control system like TRMS, Robot and Magnetic levitation system. AI languages : Important characteristics of AI languages-PROLOG. Application of AI & neural networks in VLSI and embedded systems.

Electives- II: Sensors UNIT 1 Principles of Physical and Chemical Sensors: Sensor classification, Sensing mechanism of Mechanical, Electrical, Thermal, Magnetic, Optical, Chemical and Biological Sensors. Sensor Characterization and Calibration: Study of Static and Dynamic Characteristics, Sensor reliability, aging test, failure mechanisms and their evaluation and stability study. UNIT 2 Sensor Modeling: Numerical modeling techniques, Model equations, Different effects on modeling (Mechanical, Electrical, Thermal, Magnetic, Optical, Chemical and Biological) and examples of modeling. Sensor Design and Packaging: Partitioning, Layout, technology constraints, scaling. UNIT 3 Sensor Technology: Thick and thin films fabrication process, Micro machining, IOC (Integrated Optical circuit) fabrication process, Ceramic material fabrication process, Wire bonding, and Packaging. Sensor Interfaces: Signal processing, Multi sensor signal processing, Smart Sensors, Interface Systems. Sensor Applications: Process Engineering, Medical Diagnostic and Patient monitoring,

UNIT 2 Introduction, Scaling, MEMS Markets and Applications MEMS materials and fabrication methods, with emphasis on silicon micromachining Process simulation: basic lithography, deposition, and etching processes for mems.

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Phy s ic al D e si gn & Te st i n g: [ H e a vy sy l la bu s; N eed s mo d if ic at i on] Te st in g: Te st i n g: W h y t es t? Diffe r en ce b et wee te st i n g & ver if i c a ti on . Ph ysi c a l f a ul ts & t h ei r mod e li n g: Fa u lt e q ui va l e n ce, d omi n a n ce & c ol la p si n g. Fa u lt si mu l a ti on : pa r al le l, de d uc ti ve & c on c ur re nt te c h ni q u es , cr it i ca l p a t h t r ac i n g. Te st pa tte r n g e ner a ti on f o r c omb i n a ti on a l c ir c u it s: B o ol ea n diff er e nce , D- a l g or i t h m, P od e m, etc , ex h a us ti ve , r a n d o m , wei gh t e d t e st pa tt er n ge n e ra ti on , a l ia si n g a n d i t s eff ct s on f a u lt c o ver a ge . Te st p at ter n g e n er ati on f or s e q ue nt ia l c ir c u i t s: ad- h oc a n d str uc t ur e s te ch n i q ue s sc a n pa t h a n d LS S D, b ou n d a r y s ca n . B ui lt- i n se lf t e st tec h n i q ue s: De si gn of te s ta bi li t y: Ve rif ic a ti o n: I n tr o d u ct i on : Wh y ve r if y? W ha t i s a t e st be n c h? Wh a t i s bei n g ve r if ie d: For ma l v e r if ica ti on , e q ui va l e nc e c h ec k i n g, m o de l c he c ki n g, f u nc ti on a l ver if i ca t i on , di ff e r e nt ap pr oa c he s t o ve r if ic at i on , b la c k b ox , w hi te b ox , gre y b ox , d e si g n ver if i ca t i on a n d r e u se. Ver if ic a ti on t o ol s : Li n t in g t o ol s , si mu la t or s, v e r if i ca ti on i n t el lec t ua l pr op e t y ( V IP ) ar t of ma ki n g V IP, wa vef or m v i ew er s, c od e & f u n c ti on al c o ve r a ge s. La n gu a ge s: O ut l i ne of e a n d Ver a, te mp or a l m o de l s & a s se r ti on s, Li n e ar Ti me Te m p or a l Lo gi c ( LT L) , C omp u t a ti on Tr e e Lo gi c ( C TL) , a sse r t i o n. Th e ver if ica t i on p la n: R ole of ver if i ca ti on pl a n, le ve l s of ver i f ic a ti on , d ir c t e d te st be n c h ap pr oa c h, c o ve ra ge - ba se d r a n d om - ba se d a p pr oa c h ( C DV) , ge ne r a t or s, m o ni t o r s & c he c ke r s. Ver if ic a ti on pr a c t ice s & a r ch it ec t u r e: o ver vi e w of r ef er e n c e ver if ic a ti on me t h od ol o g y ( RV M) & ver if i ca t i on m et h od ol o g y m a n u al ( V MM) . De si gn f or ver if ic at i on : El ec t i v e I II RF circuits & Systems

Characterization of materials used for different RF electronic devices. Heterostructure-overview. High frequency transistors- BJT,field effect transistors . Basics of resonant tunneling, RT devices. Introduction to RF/Microwave Concepts .Active and passive RF components , circuit representations of two port RF/MW networks scattering and T parameters , smith chart. Basic Considerations in Active Networks- Stability and noise considerations, Gain Considerations in Amplifiers. Active Networks - Linear and Nonlinear Design, RF/MW Amplifier . RF/MW Oscillators- Basic topologies ,VCO, Quadrature and single sideband generators. Radio frequency Synthesizers- PLLS, Various RF synthesizer architectures and frequency dividers . Overview of RF Filter design, design of rectifier , detector , mixer , RF/MW control circuit. Small RF/MW antenna and array . RF/MW Integrated circuits - design and applications

10

M.Tech. - ECE (Microelectronics & VLSI Designs) Common Syllabus

Low Power VLSI Design Introduction to low power VLSI design-Need for low power-CMOS leakage current-static current-Basic principles of low power design-probabilistic power analysis-random logic signal-probability and frequency-power analysis techniques-signal entropy. Circuit - transistor and gate sizing - pin ordering - network restructuring and reorganization - adjustable threshold voltages - logic-signal gating - logic encoding. Pre-computation logic. Power reduction in clock networks - CMOS floating node - low power bus - delay balancing - SRAM. Switching activity reduction - parallel voltage reduction - operator reduction -Adiabatic computation - pass transistor logic Low power circuit design style - Software power estimation - co design. TEXT BOOKS 1. Gary Yeap "Practical Low Power Digital VLSI Design", 1997 2. Kaushik Roy , Sharat C. Prasad, "Low power CMOS VLSI circuit design", Wiley Inter science Publications". (1987) Micro and Nano Devices : Prerequisite : Fundamentals of semiconductor physics and basics of p-n junctions, bipolar transistors, JFETs, MOS capacitors, MOSFETs, CMOS, LEDs, laser diodes, photodetectors, solar cells; low and high frequency equivalent circuits of BJTs and MOSFETs, IC technology. Course content : Module-1 (14 lectures) [Recapitulation of MOS scaling laws, Short channel effects, MOSFET models], Nano CMOS, Effects of gate oxide tunneling, Concept of EOT, high-k dielectrics, Effects of nanoscaling on MOSFET characteristics and performance, Technology trend, Advanced CMOS structures, SOI. Module-2 (8 lectures) Semiconductor heterojunctions; compound semiconductor and silicon-germanium heterostuctures, superlattice, HBTs, PETs, MESFETs, advanced solar cell structures. Module-3 (14 lectures) Fundamental concepts of quantum structures and tunneling junctions, Nanotubes, Devices based on quantum wells, quantum wires/nanotubes and quantum dots HEMTs, RTDs, CNT MOSFETs, SETs, Terahertz devices, advanced optoelectronic devices. Module-4 (6 lectures) Outline of nanofabrication nanolithography, MBE, MOVPE; Introduction to molecular electronics. Outcome: Familiarity with advanced structures, their relative merits and demerits, areas of application,

Text Books: Ning & Taur B.R.Nag S. M. Sz e

11

Вам также может понравиться

- Data 4551uploadДокумент2 страницыData 4551uploadanilshaw27Оценок пока нет

- Data 2Документ1 страницаData 2anilshaw27Оценок пока нет

- Data UploadДокумент2 страницыData Uploadanilshaw27Оценок пока нет

- Data UploadДокумент2 страницыData Uploadanilshaw27Оценок пока нет

- Data UploadДокумент2 страницыData Uploadanilshaw27Оценок пока нет

- DataДокумент1 страницаDataanilshaw27Оценок пока нет

- Admission AdvertisementДокумент4 страницыAdmission AdvertisementGhosh SurojitОценок пока нет

- Data UploakodДокумент1 страницаData Uploakodanilshaw27Оценок пока нет

- Data Upl65oadДокумент2 страницыData Upl65oadanilshaw27Оценок пока нет

- Data UploadДокумент1 страницаData Uploadanilshaw27Оценок пока нет

- Data UploadiiДокумент1 страницаData Uploadiianilshaw27Оценок пока нет

- TR 99 27Документ9 страницTR 99 27anilshaw27Оценок пока нет

- Data UploajjdДокумент1 страницаData Uploajjdanilshaw27Оценок пока нет

- Visitor's VisaДокумент2 страницыVisitor's Visaanilshaw27Оценок пока нет

- WB MДокумент18 страницWB Manilshaw27Оценок пока нет

- Partial Differential Equations: Analytical and Numerical MethodsДокумент136 страницPartial Differential Equations: Analytical and Numerical MethodsMohamed Mounir FekriОценок пока нет

- 1st NKN Public Lecture Poster PDFДокумент1 страница1st NKN Public Lecture Poster PDFanilshaw27Оценок пока нет

- 0601185Документ14 страниц0601185anilshaw27Оценок пока нет

- Flower PotДокумент4 страницыFlower Potanilshaw27Оценок пока нет

- Data V Table1Документ3 страницыData V Table1anilshaw27Оценок пока нет

- Direct Admission - B. TechДокумент2 страницыDirect Admission - B. Techanilshaw27Оценок пока нет

- FCI RecruitmentДокумент36 страницFCI RecruitmentHsamb AbmОценок пока нет

- Extension of Pmegp DateДокумент1 страницаExtension of Pmegp Dateanilshaw27Оценок пока нет

- 1031 - Application FormДокумент3 страницы1031 - Application Formanilshaw27Оценок пока нет

- 24 Sept 2012 ScheduleДокумент5 страниц24 Sept 2012 Scheduleanilshaw27Оценок пока нет

- Result WebДокумент2 страницыResult Webanilshaw27Оценок пока нет

- SwadharДокумент32 страницыSwadharShailander Singh100% (1)

- Ready To Send Revised Sci Comm ProgДокумент4 страницыReady To Send Revised Sci Comm Proganilshaw27Оценок пока нет

- PHD FinalДокумент8 страницPHD Finalanilshaw27Оценок пока нет

- Costs 2013Документ6 страницCosts 2013Sehar AhmedОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)