Академический Документы

Профессиональный Документы

Культура Документы

FPGA Implementation of Simplified SVPWM Algorithm for Three Phase Voltage Source Inverter

Загружено:

Venkata Krishna AndeyИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FPGA Implementation of Simplified SVPWM Algorithm for Three Phase Voltage Source Inverter

Загружено:

Venkata Krishna AndeyАвторское право:

Доступные форматы

International Journal of Computer and Electrical Engineering, Vol.2, No.

6, December, 2010

1793-8163

1010

AbstractA resource efficient with low computational

overheads SVPWM algorithm for three phase voltage source

inverter which is used to supply variable voltage and variable

frequency to three phase AC drives is proposed in this paper.

Because of its advantages like lower switching losses, higher dc-

bus utilization SVPWM scheme becomes the preferred PWM

technique for various three-phase power converter applications.

Conventional SVPWM algorithm involves complex

mathematics and requires more hardware resources to

implement and takes more time for its execution. The Field

Programmable Gate Arrays (FPGAs) offer high computational

ability and flexibility due to their parallel execution and

reconfigurable hardware. Hence the scheme suggests the

implementation of a resource efficient algorithm with low

computational overheads for SVPWM generation using FPGA

and obtains higher sampling rates with minimal use of

hardware resources. Resource utilization of proposed

algorithm obtained is 4% for XILINX XC3S500E processor

operating at 50 MHz. The output fundamental frequency can

be adjusted from 0.1Hz to 1500Hz and PWM switching

frequency can be set from 200 to 50 KHz. The adjustable delay

time logic for PWM gating signals is also implemented. The

proposed algorithm is tested for 3-phase induction motor with

VSI and the experimented results are validated.

Index TermsDigital Control, FPGA, SVPWM, Xilinx

XC3S500E

I. INTRODUCTION

Variable voltage and frequency supply for ac drive is

invariably obtained from three-phase Voltage Source

Inverter. A number of PWM techniques have been presented

to obtain variable voltage and variable frequency supply[4].

Space Vector Pulsewidth Modulation has become one of the

most important PWM method for three-phase voltage

source inverters[5]. It has an advantages over carrier-based

sine tringle pwm such as higher dc bus utilization, lower

switching losses and less harmonic distortions [14].

In order to implement SVPWM algorithm DSPs are

widely used but the execution of SVPWM algorithm in less

number of machine cycles is need of many applications

which can not be satisfied with conventioanl DSPs because

Manuscript received June 30, 2010.

D. N. Sonawane is with the Department of Instrumentation and Control

of College of Engineering, Pune-411005, MH,INDIA (91-020- 25507185;

fax: 91-020-25507299; e-mail: dns.instru@ coep.ac.in).

M. S. Sutaone is with Department of Electronics and Communication of

College of Engineering, Pune-411005, MH, INDIA (91-020- 25507141; fax:

91-020-25507299; e-mail: mssutaone@ extc.coep.org.in)

B. N. Choudhari is with Department of Electrical Engineering of

College of Engineering, Pune-411005, MH, INDIA (91-020- 25507112; fax:

91-020-25507299; e-mail: bnc.elec@ coep.ac.in)

they executes instructions sequentially and thus requires

more time to compute. Whereas, field programmable gate

array (FPGA) performs the entire procedures with

concurrent operation by using its reconfigurable hardware

and parallel processing. Employing FPGA to realize PWM

strategies provides advantages such as rapid prototyping,

simple hardware and software design, higher switching

frequency and reduction of computational overheads [5].

Computational Complexity and resource utiliazation of

conventional SVPWM algorithm increases thus the

execution time with number of levels of converter [2].

In this paper, a resource efficient SVPWM algorithm is

proposed which reduces computational overheads and

solves the problem of high sampling time in real time

applications. The proposed algorithm uses only adders,

subtractors, comparators, shifters,etc to be implemeted using

FPGAs and takes less number of resources and execution

time than conventional algorithm. Finally, experimental

results from an inverter prototype are presented to confirm

the validity and performance of the designed SVPWM

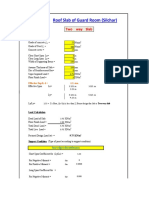

algorithm. Fig.1 shows the open loop control scheme for

three phase induction motor which is used for testing and

validation of algorithm.

This paper is organized as follows. Section II introduces

conventional SVPWM algorithm and mathematics involved

in it. Section III discusses simplified SVPWM algorithm.

Section IV describes FPGA implementation of proposed

simplified SVPWM algorithm and experimental results.

Finally conclusion is in Section V.

Fig. 1 Open loop scheme for three-phase induction motor

II. CONVENTIONAL SVPWM ALGORITHM

To implement the space vector PWM, the voltage

equations in the abc reference frame can be transformed into

FPGA Implementation of Simplified SVPWM

Algorithm for Three Phase Voltage Source

Inverter

D. N. Sonawane, M. S. Sutaone , B. N. Choudhari and Abhijeet Badurkar

International Journal of Computer and Electrical Engineering, Vol.2, No.6, December, 2010

1793-8163

1011

the stationary d-q reference frame that consists of the

horizontal (d) and vertical (q) axis as depicted in Fig. 2

Fig. 2 Relationship between a-b-c reference frame and stationay d-q frame

The relationship is expressed as

dq0

= Ks

ubc

(1)

Where Ks = |

1 12 -12

u S 2 -S 2

12 12 12

|

The transformation is equivalent to an orthogonal

projection of a-b-c reference frame onto two dimensional

perpendiculars to the equivalent d-q plane in a three

dimensional co-ordinate system. As a result six nonzero and

two zero vectors are obtained. The six non zero vectors are

shape to hexagonal as shown in fig. 3(a). The angle between

any two non zero adjacent vectors is 60. The objective of

SVPWM is to approximate reference voltage vector V

ref

using eight switching pattern. Therefore, space vector PWM

can be implemented by following three steps:

Determining V

d,

V

q,

V

ref

and angle for sector

Determining the time duration T1, T2 and T0

Determining the switching time of each

switching devices ( S1 ~ S6)

(a) (b)

Fig. 3 (a) d-q transfomation of Space Voltage Vectors in

different sectors

Fig 3 (b) Space Vector time calculations with Vref

The relationship between switching variable vector and

phase voltage vector [V

a

V

b

V

c

] can be expressed as follows.

I

d

= I

un

-I

bn

. cos6u -I

cn

. cos6u

= I

un

- 1 2 I

bn

- 1 2 I

cn

I

q

= u + I

bn

. cosSu -I

cn

. cosSu

= S 2 I

bn

] - S 2I

cn

]

(2)

|

v

d

v

q

| =

2

3

|

1

-1

2

-1

2

u

3

2

-3

2

| |

v

an

v

bn

v

cn

|

(3)

From fig. 3 (b), the reference vectror V

ref

is calculated as

|I

c]

| = I

d

2

+I

q

2

o = ton

-1

|

I

q

I

d

(4)

In general, V

ref

in n sector is obtained by two adjecent

non-zero vectors (V

j

, V

j+1

) and two-zero vectors. V

ref

is

expressed as

v

rcI

=

T

n

T

z

. vn +

T

n+1

T

z

. v

n+1

(S)

where T

n

&

T

n+1

are on time of V

n

and V

n+1

during each

sampling period (Tz) respectively and n is the sector

number in which V

ref

resides. Fig 3 (b) shows the space

vectro time representation with V

ref

for sector 1. The

magnitude of non zero sapce vector always ||Vj||= 2V

dc

/3.

The sectors are identifide depending on values of angle 'o.

The switching time duration T1, T2 and T0 for a

perticular sector can be calculated from following equations .

I

1

=

S. I

z

IJc

|sin|

pi

S

n1 I

d

-cos |

pi

S

n1 I

q

|

I

2

=

S. I

z

IJc

|-sin|

pi

S

(n -1)| I

d

+cos |

pi

S

(n -1)| I

q

|

I

0

= I

z

-I

n

-I

n+1

(6)

The switching time of each switching devices (S1~ S6)

per sector is given as per table I

TABLE I SWITCHING TIME AT EACH SECTOR

SECTOR S1, S3, S5 S2, S4, S6

1 S1= T1 + T2 + T0/2

S3= T2 + T0/2

S5= T0/2

S4 = T0/2

S6 = T1 + T0/2

S2 = T1 + T2 + T0/2

2 S1= T1 + T0/2

S3= T1+T2 + T0/2

S5= T0/2

S4= T2+T0/2

S6= T0/2

S2= T1+T2+T0/2

3 S1= T0/2

S3= T1+T2+T0/2

S5= T1+T2

S4= T1+T2+T0/2

S6= T0/2

S2= T1+T0/2

4 S1= T0/2

S3= T1+T0/2

S5= T1+T2+T0/2

S4= T1+T2+T0/2

S6= T2+T0/2

S2= T0/2

5 S1= T2+T0/2

S3= T0/2

S5= T1+T2+T0/2

S4= T1+T0/2

S6= T1+T2+T0/2

S2= T0/2

6 S1= T1+T2+T0/2

S3= T0/2

S5= T1+T0/2

S4= T0/2

S6= T1+T2+T0/2

S2= T2+T0/2

From the above equations and fig 3 (a) and (b), the sector

identification criterion of conventional algorithm involves

International Journal of Computer and Electrical Engineering, Vol.2, No.6, December, 2010

1793-8163

1012

floating point operations as to get angle that requires

calculating inverse tan function. Because of sine function and

square root values involved in computation switching time

duration i.e. T1, T2 and T0, implementation of conventional

algorithm using digital processor becomes difficult. In

context with FPGA implementation the floating point

operations and trigonometric functions increases resource

utilization thus execution time. Attempt to be made to

simplify mathematical equations which require only addition,

subtraction, shifting, etc. to implement the SVPWM

algorithm for three phase VSI.

III. SIMPLIFIED ALGORITHM

The conventional SVPWM algorithm includes d-q

transformation of three input voltages V

an

, V

bn

and V

cn

as

given by equation (4) this transformation requires value

of S to be calculated it is difficult to implement floating

point numbers using FPGA. Hence instead of d-q

transformation, intermediate transformation vectors are used.

The eq. (3) can be written as:

I

d

=

2

S

Io -

1

S

Ib -

1

S

Ic &

Io =

1

S

Ib -

1

S

Ic (7)

IJ =

1

S

|2Io -Ib -Ic]

Io =

1

S

| Ib - Ic]

(8)

By defining intermediate variables as X

d

and X

q

, the eq.

(7) written as:

XJ = 2Io -Ib -Ic &

Xo = Ib - Ic

(9)

By combining eq. (8) and (9), the V

d

and V

q

are

expressed in terms of intermediate vectors as:

IJ =

1

3

|XJ]

Io =

1

3

| Xo]

(10)

Hence the algorithm needs only to calculate X

d

and X

q

which requires simple operators namely shifter (for

multiplication by 2), adder and subtractor. The

corresponding V

d

and V

q

calculated by normalizing the

values with 1/3 and 1/S units.

The determination of sector depends only on the sign of

X

d

and X

q

as per following rules. Determination of the

sectors can be done by simply checking 3 conditions:

Condition 1: sign of Xd

Condition 2: sign of Xq

Condition 3: |Xd | > |Xq/2|

The rules to find sectors:

Rule 1: if (Xd>0 & Xq>0 & |Xd|>|Xq/2|)

Sector- 1

Rule 2: if (Xd>0 & Xq>0 & |Xd|<|Xq/2|)

Sector- 2

OR

if (Xd<0 & Xq>0 & |Xd|<|Xq/2|)

Sector- 2

Rule 3: if (Xd<0 & Xq>0 & |Xd|>|Xq/2|)

Sector-3

Rule 4: if (Xd<0 & Xq<0 & |Xd|>|Xq/2|)

Sector-4

Rule 5: if (Xd>0 & Xq<0 & |Xd|<|Xq/2|)

Sector-5

OR

if (Xd<0 & Xq <0 & |Xd|<|Xq/2|)

Sector-5

Rule 6: if (Xd>0 & Xq<0 & |Xd|>|Xq/2|)

Sector-6

For a symmetric space vector PWM, the output voltage i.e.

X

d

and X

q

can be in any of the sector 1 to sector 6 is given

by the equation

|

T

n

T

n+1

| = T

PWM

N

0

|

X

d

X

q

| (11)

Eq. (11) shows that every PWM period, the output

voltages are approximated as (T

z

/V

dc)

by switching between

the two non zero basic vectors that border the sector of the

current output voltages. The sum of T

n

and T

n+1

should be

less than or equal toT

PWM

and rest of period the switching

time should be T

0

. The N

0

is called as decomposition

matrix, given as

N

0

= |

N

00

N

01

N

10

N

11

|

Applying equation (10) to (6), the switching time can be

calculated as

=

l

l

l

l

2

S

sin|

pi

S

n1 -cos |

pi

S

n1

-

2

S

sin|

pi

S

(n -1)| cos |

pi

S

(n -1)|

1

1

1

1

(12)

If Vdc is normalized with S per unit, and Tz is set to S

per unit, the four coefficients in eq. (12) will alter their

values according to the sector n. If reference vector is

located in sector I, then n=1, then N

00

= 1, N

01

= -12,

N

10

= u and N

11

= 1.

The coefficients of decomposition matrix according to

sector is given in Table II

TABLE II COEFFICIENTS OF DECOMPOSITION MATRIX

Sector

n

1 2 3 4 5 6

N

00

1 1 0 -1 -1 0

International Journal of Computer and Electrical Engineering, Vol.2, No.6, December, 2010

1793-8163

1013

N

01

-1/2 1/2 1 1/2 -1/2 -1

N

10

0 -1 -1 0 1 1

N

11

1 1/2 -1/2 -1 -1/2 1/2

So from eq. (11) the switching times are calculated as

[T

n

'] = [N

00

N

01

] |

X

d

X

q

|

[T

n+1

'] =[N

10

N

11

] |

X

d

X

q

|

[T

0

'] = S - T

n

' + T

n+1

'

(13)

The calculation for eq. (13) will requires simple operators

such as shifters, adders and subtractors including X

d

, and X

q

.

Thus the proposed algorithm reduces the complexity of

conventional SVPWM algorithm.

IV. FPGA IMPLEMENTATION

Fig. 4 shows the internal architecture of simplified

SVPWM algorithm implemented using Spartan 3 FPGA

(XILINX XC3S500E)

Fig. 4 Internal Architecture of Simplified SVPWM Algorithm

The architecture mainly consists of five major blocks

1. 3-2 Transformation Module:

Values of three phase voltages i.e. V

a

, V

b

, V

c

is input to

this block. This module transforms three phase voltage

reference frame to two phase voltage reference frame using

equations (10). To implement in FPGA the resources

requires are only adders, and subtractors.

2. Sector determination module:

The input to this module is X

d

and X

q

values generated by

three to two phase transformation module. This module

checks three conditions as explained earlier and the

corresponding sectors get determined as per the rules

explained earlier.

Result of condition X

d

>0 is stored in 1 bit variable as C1.

Result of condition X

q

>0 is stored in 1 bit variable as C2

And result of condition |X

d

|>|X

q

/2| is stored as C3.

These variables are appended to form a three bit array

named as sect. The array sect = {C1, C2, C3}. The sector

can be determined from the value of sect according to

following table:

TABLE III VALUES OF ARRAYS ACCORDING TO SECTOR

Sector Array value

1 7

2 2,6

3 3

4 1

5 0,4

6 5

For example, if Xd>0, then C1=1 and Xq<0, C2=0 and

for |Xd|>|Xq/2|, C3=1. So sect= {1,0,1}=5.

So according to table III, the sector 6 will get selected.

3. Switching time calculation module:

Switching time calculation requires values of X

d

, X

q

and

sectors. These values are calculated by two blocks as

explained earlier. The values of parameters T

n

' and T

n+1

']

are determined from equation (13). The coefficients of

decomposition matrix and their values are obtained from

table II based on sector number.

4. Symmetrical PWM generation module:

This module is the heart of this algorithm which is

responsible for generation of six symmetrical PWM signals.

This module requires sector number and switching time

values calculated by previous blocks. The PWM switching

frequency can be adjusted in this module. Dead time

generation module is a part of this module.

Figure 5(a) and 5(b) shows the waveform produced for

sector I and II as a sample.

Figure 5 (a) Symmetrical PWM for sector I

Figure 5 (b) Symmetrical PWM for sector II

Each waveform has following properties

1. Each PWM channel switches twice per PWM

period except when duty cycle is 0 or 100%

International Journal of Computer and Electrical Engineering, Vol.2, No.6, December, 2010

1793-8163

1014

2. There is fixed switching order among the three

PWM channels for each sector

According to figure 5 (a) and 5 (b) the values of different

PWM outputs are changes only for the states S2, S3, S5, and

S6 out of which the pattern of S2 and S6 are always same as

well the pattern of S3 and S5 are always same, Hence 3 bit

array (S2ar and S3ar) is created each for S2 (same for S6)

and S3 (same for S5) respectively. Values are assigned to

these arrays based on sector of V

ref

according to table IV.

TABLE IV SYMMETRICAL PWM OUTPUTS ACCORDING

TO STATES

STATES

N 1 2 3 4 5 6

S2,S6

PWMA 1 0 0 0 0 1

PWMB 0 1 1 0 0 0

PWMC 0 0 0 1 1 0

S3,S5

PWMA 1 1 0 0 1 1

PWMB 1 1 1 1 0 0

PWMC 0 0 1 1 1 1

The value of switching time T

z

is kept equal to V

dc

for

normalization.

A counter is set to 0 at the beginning of each switching

period which counts up to T

z

. The time step to this counter

is adjustable. Larger time step means smaller frequency and

vice versa. Thus the PWM frequency can be adjusted by

adjusting the time step. For C < T

0

/4, PWMA, PWMB and

PWMC are off. (Refer S1 state of fig.5). Then for T

0

/4 C

< T

n

/2, the PWMA, PWMB and PWMC are assigned

values of S2ar which are sector dependent (state S2 of Fig.5).

For state S3, the values of PWMA, PWMB and PWMC are

assigned as given by S3ar.

This procedure is continued till the counter reaches Tz.

Thus PWM signals for one switching period are generated.

Now the counter is set to zero and again same procedure is

repeated for new values of V

ref

Thus symmetrical PWM

signals are continuously generated.

The table shows the comparison of resource utilization for

conventional SVPWM and simplified SVPWM algorithm

implemented using Xilinx Spartan 3 FPGA (XC3S500E)

operating at 50MHz.

TABLE V

COMPARISION OF SVPWM SCHEMES IMPLEMENTED

USING SPARTEN 3 FPGA OPERATING AT 50MHZ

Scheme Multipliers Dividers Adders

/Subtra

ctors

CLBs %

Utiliz

ation

Conve-

-ntional

8 2 24+ 1796 15%

Proposed 0 0 32+ 490 4%

5) Dead time generation module

In ideal conditions, the gating signals to the power

switches of same phase leg of the PWM inverter should be

complementary. However, the turn-off time of a power

switch is usually longer than its turn-on time. So, if the

switching is carried out simultaneously, the device turns on

quickly as compared to other device which is supposed to be

turned off. This can cause short circuit due to both switches

of the same leg being on at the same time. This can damage

the switches as well as coil of motor. So this condition must

be avoided. It is done by delaying the switching on of a

device than switching off of its complementary device. An

appropriate delay time must be inserted between these two

gating signals. The length of this delay time is usually about

1.5 to 2 times the maximum turn-off time. The following

diagram shows how the dead-time is inserted between two

PWM signals of the same leg. Dead time generation module

is the part of the symmetric PWM generation algorithm.

Figure 6 Dead time generation for PWMA

The scheme shown in figure (6) is implemented in the

algorithm. As seen from the figure, the switching on of

upper switches of VSI is delayed by dead time value which

is configurable. The switching off of lower switches of VSI

is delayed by dead time value. Thus short circuiting is

prevented.

V. EXPRIMENTAL VERIFICATION OF ALGORITHM

The scheme implemented for testing of the algorithm is as

shown in figure (1). Figure (7) shows experimental setup.

The DAQ card from National Instruments is used for

generation of three 120 degree phase shifted variable

frequency sine waves as V

a

, V

b

and V

c

interfaced with Lab

VIEW software. These voltage waveforms are given to SPI

based 12-bit ADC MCP3204. It is set to scan three channels

continuously. The ADC continuously samples the three sine

wave inputs by its minimum sampling time and digital

values are continuously accepted by FPGA. Thus FPGA

gets the values of V

a

, V

b

and V

c

i.e. after calculation V

ref

for

SVPWM generation.

The SVPWM generation algorithm is executed in FPGA.

It produces six PWM signals output. The PWM signals from

FPGA act as switching signals for IGBTs of VSI. In place

of motor, star connected resistive-inductive load is used.

The output of VSI is given to this resistive load. To filter the

load voltage, low pass RC filters are used. To observe the

outputs, Tektronix DSO with 4 input channels is used which

has waveform storage function. After testing on R-L load,

the algorithm is tested on three phase induction motor. The

result matches those of the simulated R-L load.

Motor Parameters

Rated Voltage : 230V

Three Phase rating : 1.5KW

fr

lin

No of poles

Frequency (

Power rating

Stator Resis

Rotor Resis

Stator Leaka

Rotor Leaka

Moment of

Figure 7 sh

equency. Figu

ne-to-neutral v

Figure 7

Figure

Internati

(P)

(f)

g

stance (Rs)

tance (Rr)

age reactance

age reactance

inertia

hows the SV

ure 8 and 9 sh

voltage wavef

7 Experimental re

e 8 Experimental r

ional Journal of

:

:

:

:

:

(Xls) :

(Xlr) :

:

VPWM puls

hows the line-

forms respecti

esults of output S

result of line-to-li

f Computer and

4

50Hz

3hp

4.6933 Ohm

4.4374 Ohm

4.85737Oh

7.12623Oh

0.01218

ses of 6.25

to line voltag

ively.

SVPWM pulses

ine voltage

d Electrical Eng

1793-8163

1015

m

m

hm

hm

KHz

e and

Figur

fund

frequ

outp

frequ

Fig

gineering, Vol.2

Figure 9 Ex

Figure 10 E

re 11 show

damental freq

uency in Hz a

ut frequency

uency.

gure 11 Experime

expected fu

2, No.6, Decem

xperimental result

Experimental resu

s the comp

quency in H

at the step size

is matching

ental result of Out

undamental freque

mber, 2010

t of line-to-neutra

ult of filtered load

parison betw

Hz and outpu

e of 5Hz, the g

with expect

tput fundamental

ency with step siz

al voltage

d current

ween expect

ut fundamen

graph shows t

ted fundamen

frequency versus

ze of 5Hz

ted

ntal

the

ntal

s

PW

in

al

pr

al

Sp

ra

ra

to

de

M

ex

tw

w

[1

[2

Figure 12 Ex

In context w

WM algorithm

nduction mot

lgorithm is pro

rovided to ve

lgorithm. The

partan 3 FPG

anging from

anging from 2

o digitally imp

ecoders. The

Microcontroller

xecution time.

wo-level VSI

with some mod

] Ying-Yu Tzo

Vector PWM

Transaction o

] Prawin Ange

Multilevel Sp

Engineering a

8236

Internati

xperimental result

Figure 13 Ex

VI. CON

with digital im

m for three p

tor, a simp

oposed in this

erify the feasi

e algorithm

GA and tested

0.5Hz to 150

200Hz to 50 K

plement as it u

same can be i

rs or DSP p

. The VSI mo

but the same

difications in a

REFE

ou, and Hau-Jea

M Control IC fo

on Power Electro

el Miachael, Dr.N

pace Vector PWM

and Technology,

ional Journal of

ts of dead time ge

xperimental set-up

NCLUSION

mplementation

phase inverter

lified and r

s paper. Exper

ibility and va

is implemen

for the fund

00Hz and sw

KHz. The algo

uses only adde

implemented u

processors an

odel used to te

can be used

algorithm.

ERENCES

an Hsu FPGA

or Three-Phase P

onics, Vol. 12, No

N.Devrajan, FP

M Algorithms In

Vol. 1, No.3, Au

f Computer and

eneration module

p

n of Space V

r used for 3-p

resource effi

rimental resul

alidity of prop

nted using X

damental frequ

witching frequ

orithm is so si

ers, subtractor

using convent

nd will get f

est the algorith

for multilevel

Realization of

PWM Inverters

.6, Nov. 1997

GA implementat

nternational Jour

ugust 2009 ISSN

d Electrical Eng

1793-8163

1016

Vector

phase

ficient

ts are

posed

Xilinx

uency

uency

imple

rs and

tional

faster

hm is

l VSI

Space-

IEEE

tion of

rnal of

N:1793-

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

gineering, Vol.2

Atif Iqbal, Adou

Space Vector P

Universities Pow

Z. Keliang and

modulation and

analysis, IEEE

Feb. 2002.

Zeliang Shu, Jian

Low Computati

Transaction on P

Simin Jiang, Jian

FPGA- Based S

Society 2005 IEC

C.L.Toh, N.R.N

TMS320C31 DS

(DTC) of Induc

science, engineer

A. M. Trzynad

Technique for

transaction on

1091~1097

Amit Kumar G

Multilevel Invert

Transaction on I

Ma Fengmin. Ya

Scheme for A

Conference on E

7, 2000, Shanzha

Su Chen, Gkza

Using Field Pro

IEEE Applied P

APEC 2002, Dal

Nikola Celanov

for Multilevel

Industrial Applic

Zhaoyong Zhou

Vector PWM Co

Power Electronic

Wei-Feng Zhang

Strategies Jour

Vol. 5, No.3, Sep

E.Monmasson, Y

Control of Electr

Society Newslette

D. N

Instr

Pune

Con

Nan

Pune

rese

FPG

He i

and

Dr.

of E

Engi

Elec

Nagp

form

PhD

resea

com

2, No.6, Decem

um Lamine, et.al

PWM for Three

wer engineering C

d W. Danwei,

three-phase carr

Trans. Ind. Elec

n Tang, et.al. An

ional Overhead

Power Electronics

ngang Liang, et.a

SVPWM Control

CON 2005, 31

st

A

N.Idris, et.al.

SP and FPGA for

ction Machines.

ring and technolo

dlowski, et.al.

DSP-Controlled

industry applic

Gupta, et.al. A

ters Based on Tw

Industrial electron

ang Tao. et.al. A

AC/DC Voltage

Environmental Ele

ai, China

a Jobs Symmetr

grammable Gate

Power Electronics

las

ic, et.al. A Fast

Three-Phase Co

cations, Vol. 37, N

u and Tiecai Li,

ontroller Based o

cs Conference an

g and Yue-Hui Y

rnal of Electronic

p 2007

Y. A. Chapuis,

rical Systems, a R

er 49/(4)

N. Sonawane As

rumentation and

e, India. He rece

ntrol form S. G

nded in 1997 and

e in 2000. He

arch at Pune Uni

GA (IP Core dev

is a member of I

Biomedical Soci

Mukul Sutaone

Electronics and

ineering, Pune,

ctronics form V

pur and M E in E

m College of En

D in Texture anal

arch area inc

munication.

mber, 2010

l. MATLAB/SIM

e-Phase Voltage

Conference, 2006,

Relationship be

rier-based PWM

ctron., vol. 49, n

n Efficient SVPW

for Three-Phas

s, Vol.22, No.5, S

al. Modeling an

l for PMSM Ind

nnual Conferenc

Design and

Conventional Di

Proceedings of

ogy, volume 38, F

An integral S

Voltage Sourc

cations, Vol. 3

Space Vector

wo- level Space V

nics, Vol. 53, issu

A Novel Simplifie

-Source Conver

ectromagnetic. C

rical SVPWM P

e Array Impleme

s Conference an

Space-Vector Mo

onverters IEEE

No.2 march/April

et.al. Design of

on FPGA 19

th

an

nd Exposition, 20

Yu Comparison o

cs Science and T

Contributions o

Review, IEEE in

ssistant Professo

Control, Colleg

eived B. E. in In

G. G. S. College

ME from Colleg

e is currently p

iversity. His rese

velopment) and E

Instrument Socie

ety of India (BM

e, Professor and

Telecommunica

India. He rec

. R. C. College

Electronics and T

ngineering, Pune

lysis form Unive

cludes signal

MULINK Model

Source Inverter

, New castle

etween space-vec

M: A comprehens

no. 1, pp. 1861

WM Algorithm w

se Inverters IE

Sep. 2007

nd Co simulation

dustrial Electron

e of IEEE

Implementation

irect Torque Con

f world academy

Feb 2009

pace-Vector PW

ce Inverters IE

5, issue 5, 19

PWM Scheme

Vector PWM IE

ue: 5, 2006

ed SVPWM Cont

rters Asia-Pac

CEEMI 2000 May

Pattern Genera

entation 7

th

Ann

d Exposition, 20

odulation Algorit

E Transactions

l 2001

f a Universal Sp

nnual IEEE Appl

04, APEC 04

of Three SVPWM

Technology of Chi

of FPGAs to

ndustrial Electron

or, Department o

ge of Engineerin

nstrumentation an

e of Engineerin

ge of Engineerin

pursuing doctor

earch area include

Embedded System

ety of India (ISO

MESI)

Head, Departmen

ation, College o

ceived B. E. i

e of Engineering

Telecommunicatio

. He received h

ersity of Pune; h

processing an

l of

rs.

ctor

sive

196,

with

EEE

n of

nics

of

trol

y of

WM

EEE

999,

for

EEE

trol

cific

y 3-

ator

nual

002,

thm

on

ace

lied

M

ina,

the

nics

of

g,

nd

g,

g,

ral

es

m.

OI)

nt

of

in

g,

on

his

his

nd

International Journal of Computer and Electrical Engineering, Vol.2, No.6, December, 2010

1793-8163

1017

Dr. Bhalchandra Choudhari, Professor and Head,

Department of Electrical Engineering, College of

Engineering, Pune, India. He received B. E. and M.E in

Electrical Engineering from Govt. College of

Engineering, Aurangabad. He received his PhD form

Indian Institute of Technology, Bombay (IITB) in

Machine Design; his research area includes AC-DC

machine modeling, design and analysis.

Вам также может понравиться

- Implementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollerДокумент5 страницImplementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollermitulОценок пока нет

- V/F Control of Three Phase Induction Motor Drive with Different PWM TechniquesДокумент15 страницV/F Control of Three Phase Induction Motor Drive with Different PWM TechniquesJaimin ChainaniОценок пока нет

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveДокумент7 страницDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretОценок пока нет

- Inverter and SV-PWMДокумент5 страницInverter and SV-PWMcoep05Оценок пока нет

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerДокумент12 страницDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaОценок пока нет

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsДокумент9 страницA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Оценок пока нет

- Simulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveДокумент7 страницSimulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveIOSRjournalОценок пока нет

- A Vector Controlled Induction Motor Drive With Neural Network Based Space Vector Pulse Width ModulatorДокумент8 страницA Vector Controlled Induction Motor Drive With Neural Network Based Space Vector Pulse Width ModulatorTiruchengode VinothОценок пока нет

- Simplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesДокумент6 страницSimplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesKoukou AmkoukouОценок пока нет

- Novel SVPWM Algorithm Implementation for Three-Phase Power ConverterДокумент4 страницыNovel SVPWM Algorithm Implementation for Three-Phase Power ConverterRanjit SinghОценок пока нет

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterДокумент12 страницLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadОценок пока нет

- SVPWM Schemes Comparison for Two-Level and Three Level InvertersДокумент6 страницSVPWM Schemes Comparison for Two-Level and Three Level InvertersEzra NaveenaОценок пока нет

- Psim SVMДокумент9 страницPsim SVMNarendra ReddyОценок пока нет

- InvertersДокумент7 страницInverterslohitashriyaОценок пока нет

- Three Level InverterДокумент5 страницThree Level InverterManish PrajapatiОценок пока нет

- Letters: Harmonic Analysis of Advanced Bus-Clamping PWM TechniquesДокумент6 страницLetters: Harmonic Analysis of Advanced Bus-Clamping PWM TechniquesunnvishnuОценок пока нет

- A Hybrid PWM Strategy Combining Modified Space Vector and Triangle Comparison Methods - Vladimir Blasko PDFДокумент7 страницA Hybrid PWM Strategy Combining Modified Space Vector and Triangle Comparison Methods - Vladimir Blasko PDFStefania OliveiraОценок пока нет

- PWM VetorialДокумент7 страницPWM VetorialrocasojuОценок пока нет

- Adaptive Droop Control Applied ToДокумент6 страницAdaptive Droop Control Applied ToManoj BadoniОценок пока нет

- A Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andДокумент6 страницA Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andShiviAroraОценок пока нет

- Implementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERДокумент6 страницImplementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERIDESОценок пока нет

- Space Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterДокумент5 страницSpace Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterIDESОценок пока нет

- Simplified Space Vector PWM Algorithm For A Three Level InverterДокумент8 страницSimplified Space Vector PWM Algorithm For A Three Level InverterGanesh ChallaОценок пока нет

- A Fractal Approach To Generate Space Vector PWM For Multilevel InvertersДокумент6 страницA Fractal Approach To Generate Space Vector PWM For Multilevel InvertersTekalign TesfayeОценок пока нет

- Analysis and Simulation of Bus-Clamping PWM Techniques Based On Space Vector ApproachДокумент10 страницAnalysis and Simulation of Bus-Clamping PWM Techniques Based On Space Vector ApproachIjesat JournalОценок пока нет

- Karampuri 2016Документ6 страницKarampuri 2016Kill MongerОценок пока нет

- Space Vector PWM - 3Документ6 страницSpace Vector PWM - 3guanitouОценок пока нет

- Generalized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveДокумент22 страницыGeneralized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveHari ReddyОценок пока нет

- SpaceVector PWM InverteДокумент27 страницSpaceVector PWM InverteShoaib KhizerОценок пока нет

- Ijret - Study of Sinusoidal and Space Vector Pulse Width Modulation Techniques For A Cascaded Three-Level InverterДокумент6 страницIjret - Study of Sinusoidal and Space Vector Pulse Width Modulation Techniques For A Cascaded Three-Level InverterInternational Journal of Research in Engineering and TechnologyОценок пока нет

- 30th Annual IEEE Conference on Industrial ElectronicsДокумент6 страниц30th Annual IEEE Conference on Industrial Electronicsdjoo77Оценок пока нет

- FPGA Implementation On SVPWM MLIДокумент5 страницFPGA Implementation On SVPWM MLISheetal VermaОценок пока нет

- SpaceVector PWM InverterДокумент35 страницSpaceVector PWM Invertersolomong50% (2)

- PEMD2014 0282 FinalДокумент6 страницPEMD2014 0282 FinalSherif M. DabourОценок пока нет

- Multilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersДокумент7 страницMultilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersAthiesh KumarОценок пока нет

- Three-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationДокумент14 страницThree-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationiisteОценок пока нет

- Ijrte0205288291 PDFДокумент4 страницыIjrte0205288291 PDFPasupuleti SivakumarОценок пока нет

- Novel, Switch, Z-Source Three-Phase InverterДокумент6 страницNovel, Switch, Z-Source Three-Phase InverterJanjanam PraveenОценок пока нет

- Paper 2 - PEL20120014 - 2ndДокумент5 страницPaper 2 - PEL20120014 - 2ndSherif M. DabourОценок пока нет

- FPGA Realization of Space-Vector Pulse Width Modulation for a 3-Level InverterДокумент5 страницFPGA Realization of Space-Vector Pulse Width Modulation for a 3-Level InvertersrfmlpОценок пока нет

- Basic SVPWMДокумент6 страницBasic SVPWMVAMSIKRISHNAEEEОценок пока нет

- Fuzzy PI Speed Controller for Induction Motors Using FPGAДокумент7 страницFuzzy PI Speed Controller for Induction Motors Using FPGABharati RajaОценок пока нет

- Space Vector PWM Control of Dual Inverter Fed Open-End Winding Induction MotorДокумент7 страницSpace Vector PWM Control of Dual Inverter Fed Open-End Winding Induction MotorGanesh ChallaОценок пока нет

- 06125602Документ6 страниц06125602Ahmad Sadam SyaeroziОценок пока нет

- 2018 A Fast Model Predictive Control With Fixed Switching Frequency Based On Virtual Space Vector For Three-Phase InvertersДокумент7 страниц2018 A Fast Model Predictive Control With Fixed Switching Frequency Based On Virtual Space Vector For Three-Phase Invertersdaiduongxanh14113Оценок пока нет

- SVPWM & VbyfДокумент11 страницSVPWM & VbyfPravin NagraleОценок пока нет

- Durgasukumar 2011Документ6 страницDurgasukumar 2011aditya317crazyОценок пока нет

- Fujimoto - 2007Документ6 страницFujimoto - 2007Ariana Ribeiro LameirinhasОценок пока нет

- Analysis of Space Vector PWM For Three Phase Inverter and Comparison With SPWMДокумент8 страницAnalysis of Space Vector PWM For Three Phase Inverter and Comparison With SPWMАлексей ЯмаОценок пока нет

- A Switched Capacitor Waveform GeneratorДокумент3 страницыA Switched Capacitor Waveform GeneratorSaujal VaishnavОценок пока нет

- A New Approach Based On Sinusoidal PWM Inverter With PI Controller For Vector Control of Induction MotorДокумент7 страницA New Approach Based On Sinusoidal PWM Inverter With PI Controller For Vector Control of Induction MotortheijesОценок пока нет

- Simplified SVPWM Algorithm For VectorДокумент4 страницыSimplified SVPWM Algorithm For VectorPrudhvi RajОценок пока нет

- Simulation and Comparison of Three Level Inverter-392Документ10 страницSimulation and Comparison of Three Level Inverter-392Đức Khánh Đức KhánhОценок пока нет

- Space Vector PWM - 2Документ6 страницSpace Vector PWM - 2guanitouОценок пока нет

- Predictive Direct Power Control of Three-Phase Boost RectifierДокумент6 страницPredictive Direct Power Control of Three-Phase Boost RectifierArun KumarОценок пока нет

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОт EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОценок пока нет

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetОт EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetРейтинг: 2 из 5 звезд2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetОт EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetОценок пока нет

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsОт EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsОценок пока нет

- Advanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesОт EverandAdvanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesОценок пока нет

- G12gasa Group5 PR2Документ7 страницG12gasa Group5 PR2Lizley CordovaОценок пока нет

- Roof Slab of Guard RoomДокумент3 страницыRoof Slab of Guard RoomAditya KumarОценок пока нет

- Intermot Hydraulic Motors IAM+ Series Technical CatalogueДокумент81 страницаIntermot Hydraulic Motors IAM+ Series Technical CatalogueeduardoraulОценок пока нет

- Oracle SCM TrainingДокумент9 страницOracle SCM TrainingVishnu SajaiОценок пока нет

- Assessment of Groundwater Quality Using GIS - A Case Study of The Churu District of RajasthanДокумент9 страницAssessment of Groundwater Quality Using GIS - A Case Study of The Churu District of RajasthanSivaShankarОценок пока нет

- A1.2.3 Method Statement 4a Redacted Version2Документ98 страницA1.2.3 Method Statement 4a Redacted Version2ChanelОценок пока нет

- OD Main Switch & OD OFF Indicator Light CircuitДокумент4 страницыOD Main Switch & OD OFF Indicator Light Circuitcelestino tuliaoОценок пока нет

- Prepositions-Of-place Worksheet Azucena SalasДокумент3 страницыPrepositions-Of-place Worksheet Azucena SalasAndreia SimõesОценок пока нет

- BS 5896 2010Документ33 страницыBS 5896 2010shashiresh50% (2)

- Analytic DeviceДокумент4 страницыAnalytic DeviceuiuiuiuОценок пока нет

- Chap1-Geometrical Optics - ExercisesДокумент3 страницыChap1-Geometrical Optics - ExercisesReema HlohОценок пока нет

- Attachment To Division Memorandum No. - , S, 2020Документ3 страницыAttachment To Division Memorandum No. - , S, 2020Jasmin Move-RamirezОценок пока нет

- BNF Syntax of Ruby - Less than 40 character title for Ruby BNF syntax documentДокумент2 страницыBNF Syntax of Ruby - Less than 40 character title for Ruby BNF syntax documentChristian FerrazОценок пока нет

- Newsletter Template NewДокумент4 страницыNewsletter Template Newapi-458544253Оценок пока нет

- UntitledДокумент47 страницUntitledAndy SánchezОценок пока нет

- GRC Fiori End User Guide Final - V2Документ75 страницGRC Fiori End User Guide Final - V2Subhash BharmappaОценок пока нет

- RefrigerationДокумент11 страницRefrigerationBroAmirОценок пока нет

- Galaxy Service ManualДокумент100 страницGalaxy Service ManualGovind RajОценок пока нет

- SI Units in Geotechnical EngineeringДокумент7 страницSI Units in Geotechnical EngineeringfaroeldrОценок пока нет

- Google Analytics Certification Test QuestionsДокумент36 страницGoogle Analytics Certification Test QuestionsRoberto Delgato100% (1)

- Fortumo Mobile Payments API GuideДокумент8 страницFortumo Mobile Payments API GuideVladimir UtješinovićОценок пока нет

- Abstracts Book Nanotech 2013Документ151 страницаAbstracts Book Nanotech 2013felipe de jesus juarez torresОценок пока нет

- PERFAPPRAISAL Research proposal on performance appraisal practices at National Bank of Pakistan and United Bank LimitedДокумент4 страницыPERFAPPRAISAL Research proposal on performance appraisal practices at National Bank of Pakistan and United Bank LimitedNadia KhanОценок пока нет

- Applying The Haar Wavelet Transform To Time Series InformationДокумент27 страницApplying The Haar Wavelet Transform To Time Series InformationJohn LemonОценок пока нет

- Difference Between AND: Shahirah Nadhirah Madihah Suhana AtiqahДокумент11 страницDifference Between AND: Shahirah Nadhirah Madihah Suhana AtiqahShahirah ZafirahОценок пока нет

- Battery Testing and MaintenanceДокумент23 страницыBattery Testing and MaintenanceMormor Omerta0% (1)

- Method of MomentsДокумент114 страницMethod of MomentsankladhaОценок пока нет

- PD 957 AND BP 220 HOUSING DESIGN STANDARDSДокумент5 страницPD 957 AND BP 220 HOUSING DESIGN STANDARDSGeraldine F. CalubОценок пока нет

- Computer Science: FieldsДокумент2 страницыComputer Science: FieldstdoraxОценок пока нет