Академический Документы

Профессиональный Документы

Культура Документы

74HC112

Загружено:

lhlearthИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

74HC112

Загружено:

lhlearthАвторское право:

Доступные форматы

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications The IC06 74HC/HCT/HCU/HCMOS Logic Package Information The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT112 Dual JK flip-flop with set and reset; negative-edge trigger

Product specication Supersedes data of December 1990 File under Integrated Circuits, IC06 1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

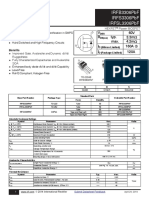

FEATURES Asynchronous set and reset Output capability: standard ICC category: flip-flops GENERAL DESCRIPTION The 74HC/HCT112 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT112 are dual negative-edge triggered JK-type flip-flops featuring individual nJ, nK, clock (nCP), set (nSD) and reset (nRD) inputs. QUICK REFERENCE DATA GND = 0 V; Tamb = 25 C; tr = tf = 6 ns

74HC/HCT112

The set and reset inputs, when LOW, set or reset the outputs as shown in the function table regardless of the levels at the other inputs. A HIGH level at the clock (nCP) input enables the nJ and nK inputs and data will be accepted. The nJ and nK inputs control the state changes of the flip-flops as shown in the function table. The nJ and nK inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. Output state changes are initiated by the HIGH-to-LOW transition of nCP. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

TYPICAL SYMBOL tPHL/ tPLH PARAMETER propagation delay nCP to nQ, nQ nSD to nQ, nQ nRD to nQ, nQ fmax CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in W): PD = CPD VCC2 fi + (CL VCC2 fo) where: fi = input frequency in MHz fo = output frequency in MHz (CL VCC2 fo) = sum of outputs CL = output load capacitance in pF VCC = supply voltage in V 2. For HC the condition is VI = GND to VCC For HCT the condition is VI = GND to VCC 1.5 V maximum clock frequency input capacitance power dissipation capacitance per ip-op notes 1 and 2 CONDITIONS HC CL = 15 pF; VCC = 5 V 17 15 18 66 3.5 27 19 15 19 70 3.5 30 ns ns ns MHz pF pF HCT UNIT

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

ORDERING INFORMATION TYPE NUMBER 74HC112D; 74HCT112D 74HC112DB; 74HCT112DB 74HC112N; 74HCT112N 74HC112PW; 74HCT112PW PACKAGE NAME SO16 SSOP16 DIP16 TSSOP16 DESCRIPTION plastic small outline package; 16 leads; body width 3.9 mm

74HC/HCT112

VERSION SOT109-1 SOT338-1 SOT38-1 SOT403-1

plastic shrink small outline package; 16 leads; body width 5.3 mm plastic dual in-line package; 16 leads (300 mil); long body plastic thin shrink small outline package; 16 leads; body width 4.4 mm

PIN DESCRIPTION PIN NO. 1, 13 2, 12 3, 11 4, 10 5, 9 6, 7 8 15, 14 16 SYMBOL 1CP, 2CP 1K, 2K 1J, 2J 1SD, 2SD 1Q, 2Q 1Q, 2Q GND 1RD, 2RD VCC NAME AND FUNCTION clock input (HIGH-to-LOW, edge triggered) data inputs; ip-ops 1 and 2 data inputs; ip-ops 1 and 2 set inputs (active LOW) true ip-op outputs complement ip-op outputs ground (0 V) reset inputs (active LOW) positive supply voltage

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

FUNCTION TABLE INPUTS OPERATING MODE nSD asynchronous set asynchronous reset undetermined toggle load 0 (reset) load 1 (set) hold no change Note L H L H H H H nRD H L L H H H H nCP X X X nJ X X X h l h l

74HC/HCT112

OUTPUTS nK X X X h h l l nQ H L H q L H q nQ L H L q H L q

Fig.4 Functional diagram.

1. If nSD and nRD simultaneously go from LOW to HIGH, the output states will be unpredictable. H = HIGH voltage level h = HIGH voltage level one set-up time prior to the HIGH-to-LOW CP transition L = LOW voltage level l = LOW voltage level one set-up time prior to the HIGH-to-LOW CP transition q = lower case letters indicate the state of the referenced output one set-up time prior to the HIGH-to-LOW CP transition X = dont care = HIGH-to-LOW CP transition

Fig.5 Logic diagram (one flip-flop).

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

DC CHARACTERISTICS FOR 74HC For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Output capability: standard ICC category: flip-flops

74HC/HCT112

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

AC CHARACTERISTICS FOR 74HC GND = 0 V; tr = tf = 6 ns; CL = 50 pF Tamb (C) SYMBOL PARAMETER 74HC +25 min. typ. tPHL/ tPLH propagation delay nCP to nQ propagation delay nCP to nQ propagation delay nRD to nQ, nQ propagation delay nSD to nQ, nQ 55 20 16 55 20 16 58 21 17 50 18 14 19 7 6 22 8 6 22 8 6 22 8 6 19 7 6 19 7 6 11 4 3 20 60 71 max. 175 35 30 175 35 30 180 36 31 155 31 26 75 15 13 100 20 17 100 20 17 125 25 21 100 20 17 100 20 17 0 0 0 4.8 24 28 40 to +85 min. max. 220 44 37 220 44 37 225 45 38 295 39 33 95 19 16 120 24 20 120 24 20 150 30 26 120 24 20 120 24 20 0 0 0 4.0 20 24 ns 40 to +125 min. max. 265 53 45 265 53 45 270 54 46 235 47 40 110 22 19 ns UNIT

74HC/HCT112

TEST CONDITIONS VCC (V) 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 Fig.7 WAVEFORMS

Fig.6

tPHL/ tPLH

ns

Fig.6

tPHL/ tPLH

ns

Fig.7

tPHL/ tPLH

ns

Fig.7

tTHL/ tTLH

output transition time 80 16 14 80 set or reset pulse width 16 LOW 14 80 removal time 16 nRD to nCP 14 clock pulse width HIGH or LOW removal time nSD to nCP set-up time nJ, nK to nCP hold time nJ, nK to nCP maximum clock pulse frequency 80 16 14 80 16 14 0 0 0 6 30 35

ns

Fig.6

tW

ns

Fig.6

tW

ns

Fig.7

trem

ns

Fig.7

trem

tsu

ns

Fig.6

th

ns

Fig.6

fmax

MHz

Fig.6

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

DC CHARACTERISTICS FOR 74HCT For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Output capability: standard ICC category: flip-flops Note to HCT types

74HC/HCT112

The value of additional quiescent supply current (ICC) for a unit load of 1 is given in the family specifications. To determine ICC per input, multiply this value by the unit load coefficient shown in the table below. INPUT 1SD, 2SD 1K, 2K 1RD, 2RD 1J, 2J 1CP, 2CP UNIT LOAD COEFFICIENT 0.5 0.6 0.65 1 1

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

AC CHARACTERISTICS FOR 74HCT GND = 0 V; tr = tf = 6 ns; CL = 50 pF Tamb (C) 74HCT SYMBOL PARAMETER min. tPHL/ tPLH tPHL/ tPLH tPHL/ tPLH tPHL/ tPLH tTHL/ tTLH tW tW trem trem tsu th fmax propagation delay nCP to nQ propagation delay nCP to nQ propagation delay nRD to nQ, nQ propagation delay nSD to nQ, nQ output transition time clock pulse width HIGH or LOW 16 +25 typ. 21 23 22 18 7 8 10 11 8 7 7 64 40 to +85 max. min. 35 40 37 32 15 20 23 25 25 20 0 24 max. 44 50 46 40 19 24 27 30 30 24 0 20 40 to +125 min. max. 53 60 56 48 22 ns ns ns ns ns ns ns ns ns ns ns MHz UNIT

74HC/HCT112

TEST CONDITIONS VCC (V) WAVEFORMS

4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5

Fig.6 Fig.6 Fig.7 Fig.7 Fig.6 Fig.6 Fig.7 Fig.7 Fig.7 Fig.6 Fig.6 Fig.6

set or reset pulse width 18 LOW removal time nRD to nCP removal time nSD to nCP set-up time nJ, nK to nCP hold time nJ, nK to nCP maximum clock pulse frequency 20 20 16 0 30

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

AC WAVEFORMS

74HC/HCT112

(1) HC : VM = 50%; VI = GND to VCC. HCT: VM = 1.3 V; VI = GND to 3 V. The shaded areas indicate when the input is permitted to change for predictable output performance.

Fig.6

Waveforms showing the clock (nCP) to output (nQ, nQ) propagation delays, the clock pulse width, the nJ, nK to nCP set-up times, the nCP to nJ, nK hold times, the output transition times and the maximum clock pulse frequency.

handbook, full pagewidth

nCP INPUT

VM(1)

trem

nSD INPUT

VM(1)

tW

trem tW

nRD INPUT

VM(1)

tPLH

tPHL

nQ OUTPUT

VM(1)

tPHL

tPLH

nQ OUTPUT

VM(1)

MBK218

(1) HC : VM = 50%; VI = GND to VCC. HCT: VM = 1.3 V; VI = GND to 3 V.

Fig.7

Waveforms showing the set (nSD) and reset (nRD) input to output (nQ, nQ) propagation delays, the set and reset pulse width and the nRD and nSD to nCP removal time.

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

PACKAGE OUTLINES SO16: plastic small outline package; 16 leads; body width 3.9 mm

74HC/HCT112

SOT109-1

A X

c y HE v M A

Z 16 9

Q A2 A1 pin 1 index Lp 1 e bp 8 w M L detail X (A 3) A

2.5 scale

5 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm inches A max. 1.75 A1 0.25 0.10 A2 1.45 1.25 A3 0.25 0.01 bp 0.49 0.36 c 0.25 0.19 D (1) 10.0 9.8 E (1) 4.0 3.8 0.16 0.15 e 1.27 HE 6.2 5.8 L 1.05 Lp 1.0 0.4 0.039 0.016 Q 0.7 0.6 0.028 0.020 v 0.25 0.01 w 0.25 0.01 y 0.1 Z (1) 0.7 0.3

0.010 0.057 0.069 0.004 0.049

0.019 0.0100 0.39 0.014 0.0075 0.38

0.244 0.050 0.041 0.228

0.028 0.004 0.012

8 0o

Note 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. OUTLINE VERSION SOT109-1 REFERENCES IEC 076E07S JEDEC MS-012AC EIAJ EUROPEAN PROJECTION

ISSUE DATE 95-01-23 97-05-22

1998 Jun 10

10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

74HC/HCT112

SSOP16: plastic shrink small outline package; 16 leads; body width 5.3 mm

SOT338-1

A X

c y HE v M A

Z 16 9

Q A2 pin 1 index Lp L 1 bp 8 w M detail X A1 (A 3) A

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 2.0 A1 0.21 0.05 A2 1.80 1.65 A3 0.25 bp 0.38 0.25 c 0.20 0.09 D (1) 6.4 6.0 E (1) 5.4 5.2 e 0.65 HE 7.9 7.6 L 1.25 Lp 1.03 0.63 Q 0.9 0.7 v 0.2 w 0.13 y 0.1 Z (1) 1.00 0.55 8 0o

o

Note 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT338-1 REFERENCES IEC JEDEC MO-150AC EIAJ EUROPEAN PROJECTION

ISSUE DATE 94-01-14 95-02-04

1998 Jun 10

11

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

74HC/HCT112

DIP16: plastic dual in-line package; 16 leads (300 mil); long body

SOT38-1

D seating plane

ME

A2

A1

c Z e b1 b 16 9 MH w M (e 1)

pin 1 index E

5 scale

10 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm inches A max. 4.7 0.19 A1 min. 0.51 0.020 A2 max. 3.7 0.15 b 1.40 1.14 0.055 0.045 b1 0.53 0.38 0.021 0.015 c 0.32 0.23 0.013 0.009 D (1) 21.8 21.4 0.86 0.84 E (1) 6.48 6.20 0.26 0.24 e 2.54 0.10 e1 7.62 0.30 L 3.9 3.4 0.15 0.13 ME 8.25 7.80 0.32 0.31 MH 9.5 8.3 0.37 0.33 w 0.254 0.01 Z (1) max. 2.2 0.087

Note 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT38-1 REFERENCES IEC 050G09 JEDEC MO-001AE EIAJ EUROPEAN PROJECTION

ISSUE DATE 92-10-02 95-01-19

1998 Jun 10

12

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

74HC/HCT112

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

SOT403-1

c y HE v M A

16

Q A2 pin 1 index A1 Lp L (A 3) A

1

e bp

8

w M detail X

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 1.10 A1 0.15 0.05 A2 0.95 0.80 A3 0.25 bp 0.30 0.19 c 0.2 0.1 D (1) 5.1 4.9 E (2) 4.5 4.3 e 0.65 HE 6.6 6.2 L 1.0 Lp 0.75 0.50 Q 0.4 0.3 v 0.2 w 0.13 y 0.1 Z (1) 0.40 0.06 8 0o

o

Notes 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT403-1 REFERENCES IEC JEDEC MO-153 EIAJ EUROPEAN PROJECTION ISSUE DATE 94-07-12 95-04-04

1998 Jun 10

13

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

SOLDERING Introduction There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used. This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our Data Handbook IC26; Integrated Circuit Packages (order code 9398 652 90011). DIP SOLDERING BY DIPPING OR BY WAVE The maximum permissible temperature of the solder is 260 C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds. The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (Tstg max). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit. REPAIRING SOLDERED JOINTS Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 C, contact may be up to 5 seconds. SO, SSOP and TSSOP REFLOW SOLDERING Reflow soldering techniques are suitable for all SO, SSOP and TSSOP packages. Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement. Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary

74HC/HCT112

between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 C. Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 C. WAVE SOLDERING Wave soldering can be used for all SO packages. Wave soldering is not recommended for SSOP and TSSOP packages, because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices. If wave soldering is used - and cannot be avoided for SSOP and TSSOP packages - the following conditions must be observed: A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used. The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end. Even with these conditions: Only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1). Do not consider wave soldering TSSOP packages with 48 leads or more, that is TSSOP48 (SOT362-1) and TSSOP56 (SOT364-1). During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured. Maximum permissible solder temperature is 260 C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 C within 6 seconds. Typical dwell time is 4 seconds at 250 C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications. REPAIRING SOLDERED JOINTS Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 C. When using a dedicated tool, all other leads can be soldered in 14

1998 Jun 10

Philips Semiconductors

Product specication

Dual JK ip-op with set and reset; negative-edge trigger

one operation within 2 to 5 seconds between 270 and 320 C. DEFINITIONS Data sheet status Objective specication Preliminary specication Product specication Limiting values

74HC/HCT112

This data sheet contains target or goal specications for product development. This data sheet contains preliminary data; supplementary data may be published later. This data sheet contains nal product specications.

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specication is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specication. LIFE SUPPORT APPLICATIONS These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

1998 Jun 10

15

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

Вам также может понравиться

- Desfibrilador Cardiac Science G3 6677 PDFДокумент57 страницDesfibrilador Cardiac Science G3 6677 PDFlhlearthОценок пока нет

- Desfibrilador Cardiac Science G3 6677 PDFДокумент57 страницDesfibrilador Cardiac Science G3 6677 PDFlhlearthОценок пока нет

- 7411 Datasheet - WWW - Booknstuff.comДокумент4 страницы7411 Datasheet - WWW - Booknstuff.comyampireОценок пока нет

- Manual Placa MãeДокумент78 страницManual Placa MãelhlearthОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Wireline Works Tech-BulletinsДокумент25 страницWireline Works Tech-BulletinsRio de Mario100% (1)

- Types of Solids 1Документ16 страницTypes of Solids 1Fern BaldonazaОценок пока нет

- Pipe Clamp For Sway Bracing TOLCOДокумент1 страницаPipe Clamp For Sway Bracing TOLCOEdwin G Garcia ChОценок пока нет

- InfoWater Student Analysis and Design WorkbookДокумент80 страницInfoWater Student Analysis and Design WorkbookefcarrionОценок пока нет

- Formula Sheet: Basic Trigonometric IdentitiesДокумент4 страницыFormula Sheet: Basic Trigonometric Identitieschetan temkarОценок пока нет

- Driver LCI 150W 500-850ma FlexC NF h28 EXC3 enДокумент7 страницDriver LCI 150W 500-850ma FlexC NF h28 EXC3 enMoustafa HelalyОценок пока нет

- Technical Data: Series Allclean AcnpДокумент1 страницаTechnical Data: Series Allclean AcnpBoško IvanovićОценок пока нет

- ST7201-Finite Element MethodДокумент14 страницST7201-Finite Element MethodVishal RanganathanОценок пока нет

- 5R55W-S Repair DiagnosisДокумент70 страниц5R55W-S Repair Diagnosisaxallindo100% (2)

- OIML R 137-1 & 2: Nternational EcommendationДокумент76 страницOIML R 137-1 & 2: Nternational EcommendationAMY WEIОценок пока нет

- MicrowaveДокумент41 страницаMicrowaveMaryem MostafaОценок пока нет

- MX3Документ154 страницыMX3Dung Nguyen0% (1)

- Irfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120AДокумент12 страницIrfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADirson Volmir WilligОценок пока нет

- Chapter 3Документ23 страницыChapter 3pganoelОценок пока нет

- Unit 07 Self-Test Chemistry Self TestДокумент2 страницыUnit 07 Self-Test Chemistry Self TestOluwatusin Ayo OluwatobiОценок пока нет

- Bates Stamped Edited 0607 w22 QP 61Документ6 страницBates Stamped Edited 0607 w22 QP 61Krishnendu SahaОценок пока нет

- Checklist For Conreting WorkДокумент13 страницChecklist For Conreting WorkMin Khant AungОценок пока нет

- Ecoflam Burners 2014 enДокумент60 страницEcoflam Burners 2014 enanonimppОценок пока нет

- Life Processes: Science Unit 1Документ19 страницLife Processes: Science Unit 1patil pratikОценок пока нет

- Implant TrainingДокумент5 страницImplant Trainingrsrinath91Оценок пока нет

- EI 6702-Logic and Distributed Control SystemДокумент2 страницыEI 6702-Logic and Distributed Control SystemMnskSaro50% (2)

- Business Analytics Data Analysis and Decision Making 6th Edition Albright Solutions ManualДокумент24 страницыBusiness Analytics Data Analysis and Decision Making 6th Edition Albright Solutions ManualAngelaLewisyqza100% (26)

- Chapter 6 - Process Capability AnalysisДокумент21 страницаChapter 6 - Process Capability AnalysisKaya Eralp AsanОценок пока нет

- Sap SCM TrainingДокумент5 страницSap SCM TrainingGLOBAL TEQОценок пока нет

- Number System Questions PDFДокумент20 страницNumber System Questions PDFMynur RahmanОценок пока нет

- DC Power Supply and Voltage RegulatorsДокумент73 страницыDC Power Supply and Voltage RegulatorsRalph Justine NevadoОценок пока нет

- PS1Документ2 страницыPS1Nitesh Kumar DubeyОценок пока нет

- Illiquidity and Stock Returns - Cross-Section and Time-Series Effects - Yakov AmihudДокумент50 страницIlliquidity and Stock Returns - Cross-Section and Time-Series Effects - Yakov AmihudKim PhượngОценок пока нет

- PPF CalculatorДокумент2 страницыPPF CalculatorshashanamouliОценок пока нет

- Rotational Dynamics-07-Problems LevelДокумент2 страницыRotational Dynamics-07-Problems LevelRaju SinghОценок пока нет