Академический Документы

Профессиональный Документы

Культура Документы

Synops Nikhil

Загружено:

Akshay BhosaleИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Synops Nikhil

Загружено:

Akshay BhosaleАвторское право:

Доступные форматы

Walchand College Of Engineering, Sangli.

(An Autonomous Institute) Department of Electronics Engineering M.Tech. Part II Dissertation Phase I SYNOPSIS

1. Name of Student 2. Name of Course 3. Date of Registration 4. Name of Guide 5. Proposed Title of Dissertation : : : : : Mr. Mane Nikhil Niwas M.Tech. in Electronics Engineering August, 2009. Mr. B. G. Patil Iris feature extraction and classification using FPGA.

6.

Synopsis of the Work

A) Problem Definition and Relevance Iris image processing having main four steps are image acquisition, image preprocessing, feature extraction and matching. Output of feature extraction block is nxm size image. To increase speed of matching stage need to reduce dimension of template image without losing information. Singular value decomposition algorithm extract nxm size image to 1xm size array hence matching can be perform n times faster. Beauty of SVD algorithm is, it extracts maximum information at first element and minimum information at last element in array hence we can ignore last elements for more optimization. Template can be matched with stored templates in read only memory in FPGA and classify using calculating hamming distance. This work deals with FPGA implementation of iris feature extraction using singular value decomposition (SVD) algorithm and iris pattern matching (i.e. classification) using hamming distance. Image data can be sent through serial or parallel port of personal computer. Images will be taken from standard database.

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA. B) Present Theories Iris biometric processing require large computation time than other biometric processing, so using single chip solutions for iris recognition system having constraint on speed and throughput. Now a days single chip solutions are provided by some manufacturer e.g. Texas instrument (TI) TMS320DM54xx, TMS320DM64x, OMAP series processors but not specific for iris image processing. Iris Recognition: Intelligent personal identification based on biometrics measurement such as facial feature, thermal emission, retina, iris, gait, voiceprint, gesture, palmprints, fingerprints, handwritten signature, hand geometry etc. Iris is the only internal human organ that is visible from outside thus well protected from external modifiers. Fingerprint may suffer from harm and aging, voice patterns may be altered due to vocal diseases. The main steps in Iris recognition system consists of: Image Acquisition: The first step of Iris Recognition is image acquisition. Normally, black and white camera should use for acquisition and must have enough resolution to capture the details of the iris patterns. The illumination angle will determine the dark and light parts of the image. It is very important that one system implements consistent illumination, on the contrary the same iris may generate two different classes under two different illumination angles. Also, the pupil is an open door to the retina, one of the most sensitive organs of our body, and extra care must be taken when shedding direct light over it. y Image Segmentation: The segmentation is process to remove non useful information, namely the pupil segment and the part outside the iris (sclera, eyelids, skin). Following are steps involve in segmentation. Detecting the Pupil Boundary Iris Edge Detection y Feature Extraction: Image is a huge redundant data. Single image contains lot of low frequency components within region of interest (ROI) hence feature extraction process extract valuable information from ROI into a small vector that represents univocally the user. Feature extraction algorithm chosen is based on two requirements, performance of the whole system and complexity of the hardware required to achieve it. y

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA. Iris Pattern Matching: After the feature extraction the Iris templates are then matched with unknown templates using matching algorithms. Performance of this block should be the most robust part of the system. Hamming distance is simpler way to find out depth of matching. Matching and non-matching is based on hamming distance. If distance is minimum (i.e. below threshold value) pattern is match, otherwise corresponding Iris pattern is not in the database. y

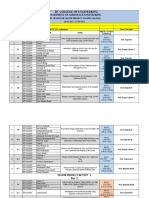

7. Introduction: This work will do with combination of hardware and software. Using FPGA speed, area, power and throughput can be optimize, also re-configurability obtained easily. Hardware system will be FPGA starter kit. The image data can be get via communication port of personal computer. Note that interfacing parallel port to FPGA kits needs extra hardware such as line buffers. Block diagram of system:-

Figure 1: block diagram of system Personal computer: Acquisition of image is either from camera or standard image database. Todays cameras are able to provide compressed image (using JPEG standards) camera itself. Image segmentation can be done using Hough transform. These two steps can be performing with the help of MTLAB software. Segmented images are stored into personal computer due to limited memory in FPGA integrated circuit.

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

Serial / parallel communication: The segmented image data can be sent through communication port, to reduce data transmission time can use parallel interface, since transmission can be n times faster than serial interface. Where n is number of parallel bits (max 8). FPGA starter kit: Calculations of Singular Value Decomposition and hamming distance can implements in FPGA kit using VHDL programming, size of S vector (template) is depends on architecture of FPGA kit.

Single value decomposition algorithm: If X is a matrix with row and column dimensions n and m respectively, then n by n orthogonal matrix U and m by m orthogonal matrix V can be found such that,

Where is a p by p diagonal matrix (p is the minimum of n and m). The diagonal elements of are the singular values of X and they are stored from largest to smallest. The above equation assumes that n >= m. Since U and V are orthogonal (and so their inverses are equal to their transpose), the above equation can also be written as:

For large matrices, it can be impractical to compute U (which is n by n). However, U can be partitioned into U = (U1, U2) Where U1 is n by p. Then X = U1SV This factorization of X called singular value decomposition. The singular values in S are square roots of Eigen values from U or V. The singular values are always real numbers. If the matrix A is a real matrix, then U and V are also real.

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

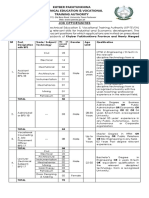

Flow chart for hardware implementation of SVD algorithm:

Start Set communication parameters. Convert serial data to parallel vector. Combining parallel vectors becomes n x m size image A (n x m). Obtain transpose in matrix A as A (m x n). Obtain W1 (n x n) = A*A and W2 (m x m) = A*A. Obtain eigenvector of W1 is U (n x n) and W2 is V (m x m). Obtain square root of eigenvalue of U or V is diagonal elements of S (p x p) matrix, arranged in descending form.

Store diagonal S (1 x p) matrix into temporary in on chip RAM

Finish

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

Flow chart for implementation of matching algorithm:

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

8. The Proposed Work: 1. Study of SVD algorithm and matching algorithm. 2. Study of FPGA implementation techniques for optimizing speed, power and performance. 3. Study of Xilinx ISE design suite Software. 4. VHDL codes and FPGA implementation using Xilinx software suite. 5. Study the performance of system on the basis of area, power, throughput, etc. 10. Facilities Available : Xilinx ISE Tool, FPGA starter kit, Library, Computer Lab, Internet etc

11. Estimated Cost

: 15,000/-(Approx.)

12. Expected Date of Completion: July, 2011.

Nikhil Niwas Mane Student

Prof. Mr. B. G. Patil Guide

H.O.D. Electronics Department Walchand College of Engg., Sangli.

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

References:

Papers: 1) Liu-Jimenez, J. Sanchez-Reillo, and R. Sanchez-Avila, "FULL HARDWARE

SOLUTION FOR PROCESSING IRIS BIOMETRICS" security Technology, 2005. CCST '05. 39th Annual 2005. 2) Christel-loc TISSE, Lionel MARTIN, Lionel TORRES and Michel ROBERT

"Person identification technique using human iris recognition" France, July 2000. 3) Li Ma, Yunhong Wang and Tieniu Tan "Iris Recognition Using Circular

Symmetric Filters Pattern Recognition, 2002. 4) Ignacio Bravo, Pedro Jimenez, Manuel Mazo, Jose Luis Lzaro and Alfredo

Gardel IMPLEMENTATION IN FPGAS OF JACOBI METHOD TO SOLVE THE EIGENVALUE AND EIGENVECTOR PROBLEM, 2006. 5) Li Ma, Tieniu Tan, Fellow, IEEE, Yunhong Wang, Member, IEEE, and Dexin

Zhang "Efficient Iris Recognition by Characterizing Key Local Variations"IEEE TRANSACTIONS ON IMAGE PROCESSING, VOL. 13, NO. 6, JUNE 2004. 6) Li Ma, Tieniu Tan, Senior Member, IEEE, Yunhong Wang, Member, IEEE, and

Dexin Zhang "Personal Identification Based on Iris Texture Analysis", IEEE TRANSACTIONS ON PATTERN ANALYSIS AND MACHINE INTELLIGENCE, VOL. 25, NO. 12, DECEMBER 2003. 7) Fernando E. Ortiz, John R. Humphrey, James P. Durbano and Dennis W. Prather

A Study on the Design of Floating-Point Functions in FPGAs 2003. 8) Javier Hormigo, Manuel Sanchez, Mario A. Gonzalez, Gerardo Bandera, Julio

Villalba, Optimized FPGA Implementation of Trigonometric Functions with Large Input Argument Proc. Of XIX Conference on Design of Circuits and Integrated Systems, 2004

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Iris feature extraction and classification using FPGA.

Websites: 1. 2. 3. 4. web.mit.edu www.xilinx.com wikipedia.org ieeexplore.ieee.org

Books: 1. Rafael Gonzalez, Richard E. Woods, Digital Image Processing, Pearson Education, India (2002). 2. Xilinx vertex series user guide. 3. Xilinx Spartan series user guide.

Department of Electronics Engineering, Walchand College of Engineering, Sangli.

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Jesus Prayer-JoinerДокумент13 страницJesus Prayer-Joinersleepknot_maggotОценок пока нет

- Leak Detection ReportДокумент29 страницLeak Detection ReportAnnMarie KathleenОценок пока нет

- Digital Image ProcessingДокумент85 страницDigital Image ProcessingAkshay BhosaleОценок пока нет

- OER DocumentationДокумент14 страницOER DocumentationAkshay BhosaleОценок пока нет

- RTOS uCOS IIДокумент66 страницRTOS uCOS IIAkshay BhosaleОценок пока нет

- FELICSДокумент56 страницFELICSAkshay BhosaleОценок пока нет

- Azimuth Steueung - EngДокумент13 страницAzimuth Steueung - EnglacothОценок пока нет

- Activity # 1 (DRRR)Документ2 страницыActivity # 1 (DRRR)Juliana Xyrelle FutalanОценок пока нет

- Review1 ScheduleДокумент3 страницыReview1 Schedulejayasuryam.ae18Оценок пока нет

- Chapter 13 Exercises With AnswerДокумент5 страницChapter 13 Exercises With AnswerTabitha HowardОценок пока нет

- KP Tevta Advertisement 16-09-2019Документ4 страницыKP Tevta Advertisement 16-09-2019Ishaq AminОценок пока нет

- 8.ZXSDR B8200 (L200) Principle and Hardware Structure Training Manual-45Документ45 страниц8.ZXSDR B8200 (L200) Principle and Hardware Structure Training Manual-45mehdi_mehdiОценок пока нет

- Quick Help For EDI SEZ IntegrationДокумент2 страницыQuick Help For EDI SEZ IntegrationsrinivasОценок пока нет

- User Manual For Speed Control of BLDC Motor Using DspicДокумент12 страницUser Manual For Speed Control of BLDC Motor Using DspicTrung TrựcОценок пока нет

- Objective & Scope of ProjectДокумент8 страницObjective & Scope of ProjectPraveen SehgalОценок пока нет

- DN Cross Cutting IssuesДокумент22 страницыDN Cross Cutting Issuesfatmama7031Оценок пока нет

- De Thi Hoc Ki 1 Mon Tieng Anh Lop 5 Co File NgheДокумент10 страницDe Thi Hoc Ki 1 Mon Tieng Anh Lop 5 Co File Nghetuyen truongОценок пока нет

- Oracle Forms & Reports 12.2.1.2.0 - Create and Configure On The OEL 7Документ50 страницOracle Forms & Reports 12.2.1.2.0 - Create and Configure On The OEL 7Mario Vilchis Esquivel100% (1)

- 18 June 2020 12:03: New Section 1 Page 1Документ4 страницы18 June 2020 12:03: New Section 1 Page 1KarthikNayakaОценок пока нет

- Analizador de Combustion Kigaz 310 Manual EngДокумент60 страницAnalizador de Combustion Kigaz 310 Manual EngJully Milagros Rodriguez LaicheОценок пока нет

- Problem Set-02Документ2 страницыProblem Set-02linn.pa.pa.khaing.2020.2021.fbОценок пока нет

- Report On GDP of Top 6 Countries.: Submitted To: Prof. Sunil MadanДокумент5 страницReport On GDP of Top 6 Countries.: Submitted To: Prof. Sunil MadanAbdullah JamalОценок пока нет

- Crown WF-3000 1.2Документ5 страницCrown WF-3000 1.2Qirat KhanОценок пока нет

- FAMOUS PP Past TenseДокумент21 страницаFAMOUS PP Past Tenseme me kyawОценок пока нет

- Android Developer PDFДокумент2 страницыAndroid Developer PDFDarshan ChakrasaliОценок пока нет

- Career Essay 1Документ2 страницыCareer Essay 1api-572592063Оценок пока нет

- Fss Presentation Slide GoДокумент13 страницFss Presentation Slide GoReinoso GreiskaОценок пока нет

- Mixed Up MonstersДокумент33 страницыMixed Up MonstersjaneОценок пока нет

- Dalasa Jibat MijenaДокумент24 страницыDalasa Jibat MijenaBelex ManОценок пока нет

- Thermally Curable Polystyrene Via Click ChemistryДокумент4 страницыThermally Curable Polystyrene Via Click ChemistryDanesh AzОценок пока нет

- Impact of Advertising On Consumers' Buying Behavior Through Persuasiveness, Brand Image, and Celebrity EndorsementДокумент10 страницImpact of Advertising On Consumers' Buying Behavior Through Persuasiveness, Brand Image, and Celebrity Endorsementvikram singhОценок пока нет

- Ricoh IM C2000 IM C2500: Full Colour Multi Function PrinterДокумент4 страницыRicoh IM C2000 IM C2500: Full Colour Multi Function PrinterKothapalli ChiranjeeviОценок пока нет

- Hole CapacityДокумент2 страницыHole CapacityAbdul Hameed OmarОценок пока нет

- Heterogeneity in Macroeconomics: Macroeconomic Theory II (ECO-504) - Spring 2018Документ5 страницHeterogeneity in Macroeconomics: Macroeconomic Theory II (ECO-504) - Spring 2018Gabriel RoblesОценок пока нет