Академический Документы

Профессиональный Документы

Культура Документы

Enunciado Enero 2010

Загружено:

marcosmartinezpeiroОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Enunciado Enero 2010

Загружено:

marcosmartinezpeiroАвторское право:

Доступные форматы

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

PROBLEMA 1. (2,5ptos) FAMLIAS LGICAS Cuatro estudiantes A, B, C y D votan en un consejo. Disear en CMOS con el mnimo nmero de transistores posible la funcin RESULTADO de la votacin (Y). Y=1 en caso de obtener mayor nmero de unos, Y=0 en caso de mayor nmero de ceros; por ltimo, en caso de empate, decide el voto de calidad de A. a) (1 pto) Exprese la funcin Y simplificada por ceros y por unos. b) (1,5ptos). Disee la funcin CMOS resultado de la implementacin por 1s.

PROBLEMA 2. (2,5ptos) CIRCUITOS COMBINACIONALES Implemente la funcin , , , =

=4

2,3,8,9,10,11,13,14,15

a) (1ptos) Utilizando exclusivamente multiplexores 2 a 1. Las variables negadas no estn disponibles. b) (0,5ptos) Utilizando una PAL del mnimo tamao posible (inputs, productos trmino, outputs). c) (1pto) Implementar con un decodificador 3 a 8 (74LS138) y con un multiplexor doble 4 a 1 (74LS153). No se puede utilizar ningn otro tipo de puerta. Las variables negadas no estn disponibles. Multiplexor 74LS153

Electrnica Digital

Pgina 1 de 6

Enero de 2010

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

Decodificador 74LS138

PROBLEMA 3. (2,5ptos) AUTMATAS FINITOS En el siguiente circuito, que es un generador de secuencia, el circuito combinacional tiene como ecuacin S(A,B,C) =3 (0,2,5).

SALIDA

Circuito combinacional

C B A

A

CLK

C

CLK

CLK Q K CLR Q

Q CLR

CLR

RELOJ BORRADO

Se pide: a) (1pto.) Anlisis del Circuito. Haced la tabla de funcionamiento (transiciones excitaciones), el diagrama de estados y deducid cual es la secuencia de salida. b) (0.25ptos) Si todos los Flip-flops tienen un tp = 5 ns (t. de propagacin), un tsetup = 5 ns un thold = 2 ns y el circuito combinacional tiene un tiempo de respuesta de 20 ns. Cul ser la mxima frecuencia de reloj que podemos aplicar al circuito?. c) (0.25ptos) Tiene esta mquina estados espreos o inancanzables?. Si es as cuales son y cules son sus estados siguientes? d) (1pto.) Suponiendo que la secuencia que genera es 01001110. Disead el diagrama de estados de una mquina de Mealy que detecte dicha secuencia con solapamiento.

Electrnica Digital

Pgina 2 de 6

Enero de 2010

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

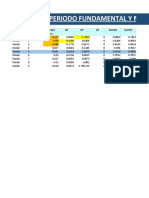

PROBLEMA 4 (2,5ptos) SUBSISTEMAS SECUENCIALES En el departamento de control de una fbrica de automviles se comprueba la resistencia de la pintura de la carrocera del automvil a determinados productos corrosivos. Para ello, las muestras bajo control se ponen en contacto con dichos productos durante 19 segundos. Para facilitar la labor de los operarios que trabajan en este departamento, la fbrica de automviles te ha encargado el diseo de un cronmetro digital que cuente 19 segundos (en modo ascendente o descendente). Una vez transcurridos los 19 segundos, el cronmetro debe reiniciarse automticamente. El cronmetro debe incluir: 1. Dos displays donde se muestren las cuentas (unidades y decenas). 2. Un pulsador/interruptor que permita el reset manual del sistema en cualquier momento. 3. Un pulsador/interruptor que permita la parada manual del sistema en cualquier momento. 4. Un pulsador/interruptor que permita conmutar manualmente entre los dos modos de funcionamiento: cuenta ascendente o descendente. Los subsistemas y circuitos integrados que se tienen disponibles son los siguientes: 1. Oscilador de referencia que proporciona una seal cuadrada de 100Hz. 2. Circuitos Integrados: 74LS49, 74HC93, 74LS162 EPROM de diferentes capacidades Puertas Bsicas (NAND, OR, NOT, AND) 3. Displays de nodo y ctodo comn 4. Resistencias, interruptores y pulsadores Se pide: a) (0.5ptos) Utilizando el CI 74HC93 y puertas bsicas (NAND, OR, NOT, AND) implementa un reloj de frecuencia 1Hz. b) (1.5ptos) Utilizando el CI 74LS162, una memoria EPROM del menor tamao posible, puertas bsicas y la seal generada en el apartado anterior, implementa el cronmetro descrito en el enunciado con salida BCD, es decir, la salida no tiene que aparecer representada en los displays. (b.1) Rellena la tabla que se adjunta con el contenido de la memoria. En la primera columna debe aparecer la direccin codificada en decimal, y en las siguientes columnas el dato codificado en binario. Dependiendo de la solucin escogida necesitars ms o menos casillas de la tabla. Para fijar ideas a continuacin se muestra cmo se indicara en la tabla que en la direccin 16 de la memoria se ha almacenado un 3 para un bus de datos de 6 bits: Dir D5 16 0 D4 D3 D2 D1 D0 0 0 0 1 1

(b.2.) Cuntas palabras de la EPROM no se aprovechan?

Electrnica Digital

Pgina 3 de 6

Enero de 2010

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

c) (0.5ptos) Utilizando el CI 74LS49 (salidas O.C.) implementa la interfaz de salida (displays). (c.1.) Indica qu tipo de display utilizaras (nodo comn o ctodo comn), justificando tu respuesta. Una respuesta sin justificar ser considerada incorrecta. (c.2) Coloca justificadamente las resistencias que sean necesarias para el correcto funcionamiento del display. Una respuesta sin justificar ser considerada incorrecta. (c.3) Puede realizarse el diseo de la interfaz de salida de modo que slo se muestren los ceros que sean significativos en los displays? En el caso de que tu respuesta sea afirmativa indica de qu modo.

Electrnica Digital

Pgina 4 de 6

Enero de 2010

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

NOMBRE: GRUPO: APELLIDOS: DNI:

TABLA DE MEMORIA (Problema 4) DIR

Electrnica Digital

Pgina 5 de 6

Enero de 2010

EXAMEN DE ELECTRNICA DIGITAL ETSIT-UPV (21 de ENERO de 2010)

Electrnica Digital

Pgina 6 de 6

Enero de 2010

Вам также может понравиться

- Animales en Inglés - Nombres, Habitat, Expresiones y PronunciaciónДокумент6 страницAnimales en Inglés - Nombres, Habitat, Expresiones y PronunciaciónIsrael Miranda ZamarcaОценок пока нет

- Reconocimiento General y de Actores TgsДокумент6 страницReconocimiento General y de Actores TgsdiyivealОценок пока нет

- Centros Formacion Profesional para El Empleo 06092018Документ1 103 страницыCentros Formacion Profesional para El Empleo 06092018redes ifct0110Оценок пока нет

- Sistemas Digitales - Ejercicios ResueltosДокумент104 страницыSistemas Digitales - Ejercicios ResueltosBrandon Payano De La Cruz100% (1)

- Cómo Acceder A Un MikrotikДокумент7 страницCómo Acceder A Un MikrotikAbraham PachecoОценок пока нет

- Tesis PublicidadДокумент122 страницыTesis Publicidadedwinpila100% (1)

- Asilo Innovacion PDFДокумент6 страницAsilo Innovacion PDFJohanna Luna LeónОценок пока нет

- Lab RegresionДокумент27 страницLab RegresionWaly PeñaОценок пока нет

- Solucionario Raz Matematico A Ordinario 2015 IIДокумент4 страницыSolucionario Raz Matematico A Ordinario 2015 IIInstituto de Investigación Académica: PraxisОценок пока нет

- Ejemplo de PFAДокумент4 страницыEjemplo de PFALuis Alejandro Alvarez ZapataОценок пока нет

- Cedom03 PDFДокумент52 страницыCedom03 PDFjcrrubОценок пока нет

- Tarea Sobre PoaДокумент3 страницыTarea Sobre PoaKathyaОценок пока нет

- Informe Procesos AutomatizadosДокумент8 страницInforme Procesos AutomatizadosFabricio Pinto SalinasОценок пока нет

- NotДокумент195 страницNotedgar507Оценок пока нет

- Comunicación ParalelaДокумент1 страницаComunicación ParalelaAndrés Camilo LópezОценок пока нет

- Telmex SpamДокумент49 страницTelmex Spamapi-26323961Оценок пока нет

- Contrato de TeletrabajoДокумент7 страницContrato de TeletrabajoRocio Sarabia PavonОценок пока нет

- Ejemplo de Guia de Estilo, Paradigma y MetaforaДокумент2 страницыEjemplo de Guia de Estilo, Paradigma y MetaforaArgel Diaz GarzaОценок пока нет

- Configuración Básica de Un RouterДокумент3 страницыConfiguración Básica de Un RouterFernando100% (1)

- Servidor de Discos en Red Con FreeNasДокумент14 страницServidor de Discos en Red Con FreeNasHermis Ramos EspinalОценок пока нет

- La - Robotica - Aplicada - A - La - Ludica Maso MasoДокумент12 страницLa - Robotica - Aplicada - A - La - Ludica Maso MasoK'rlo EscaОценок пока нет

- EPSON PowerLite® S39Документ4 страницыEPSON PowerLite® S39Support Technician Indra Colombia LtdaОценок пока нет

- Tarea Preparatoria 1 ParcialДокумент3 страницыTarea Preparatoria 1 ParcialAnonymous R7sLmJPhPОценок пока нет

- Lista de ProgramasДокумент5 страницLista de ProgramasrobyОценок пока нет

- Marlis S OperativosДокумент6 страницMarlis S OperativosSther RoPeОценок пока нет

- Aig Ingenieros Consultores y Constructores Sac - r225609sn - Aigsac@Документ1 страницаAig Ingenieros Consultores y Constructores Sac - r225609sn - Aigsac@Luis AguilarОценок пока нет

- Requisitos para ConferenciasДокумент3 страницыRequisitos para ConferenciasenriquejsantiagoОценок пока нет

- Ejercicio 2 ExcelДокумент27 страницEjercicio 2 Excelyoelito_06Оценок пока нет

- Análisis Sísmico EstáticoДокумент13 страницAnálisis Sísmico EstáticoGerardo SalvadorОценок пока нет