Академический Документы

Профессиональный Документы

Культура Документы

Eletrônica de Potencia - Unicamp

Загружено:

Rogerio RossiОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Eletrônica de Potencia - Unicamp

Загружено:

Rogerio RossiАвторское право:

Доступные форматы

UNIVERSIDADE ESTADUAL DE CAMPINAS

Faculdade de Engenharia Eltrica e de Computao

Departamento de Sistemas e Controle de Energia

Eletrnica de

Potncia

Jos Antenor Pomilio

Publicao FEEC 01/98

Fevereiro de 1998

Revisado em Janeiro de 2002

ii

Apresentao

O texto que se segue foi elaborado para a disciplina "Eletrnica de Potncia"

ministrada nos cursos de ps-graduao em Engenharia Eltrica na Faculdade de Engenharia

Eltrica e de Computao da Universidade Estadual de Campinas.

Este um material que vem sofrendo freqentes atualizaes, em funo da constante

evoluo tecnolgica na rea da Eletrnica de Potncia, alm do que, o prprio texto pode

ainda conter eventuais erros, para os quais pedimos a colaborao dos estudantes e

profissionais que eventualmente fizerem uso do mesmo, enviando ao autor uma comunicao

sobre as falhas detectadas.

Os resultados experimentais includos no texto referem-se a trabalhos executados pelo

autor, juntamente com estudantes e outros pesquisadores e foram publicados em congressos e

revistas, conforme indicado nas referncias bibliogrficas.

Textos semelhantes foram, ou esto sendo produzidos referentes s disciplinas de

"Fontes Chaveadas" e Condicionamento de Energia Eltrica e Dispositivos FACTS.

Campinas, 21 de Janeiro de 2002

Jos Antenor Pomilio

Jos Antenor Pomilio Engenheiro Eletricista, Mestre e Doutor em

Engenharia Eltrica pela Universidade Estadual de Campinas - UNICAMP

(1983, 1986 e 1991, respectivamente). professor junto Faculdade de

Engenharia Eltrica e de Computao da UNICAMP desde 1984. Participou

do Grupo de Eletrnica de Potncia do Laboratrio Nacional de Luz

Sncrotron (CNPq) entre 1988 e 1993, sendo chefe do Grupo entre 1988 e

1991. Realizou um estgio de ps-doutoramento junto ao Departamento de

Engenharia Eltrica da Universidade de Pdua, Itlia, em 1993/94. Foi

Liaison da IEEE Power Electronics Society para a Regio 9 (Amrica

Latina) em 1998/1999. Foi eleito Member at Large do Comit de

Administrao da IEEE Power Electronics Society para o trinio 2000/2002.

Foi editor da Revista Eletrnica de Potncia (99/2000). presidente da

Sociedade Brasileira de Eletrnica de Potncia (2000-2002).

iii

Contedo

1. COMPONENTES SEMICONDUTORES DE POTNCIA

1.1 BREVE REVISO DA FSICA DE SEMICONDUTORES

1.1.1 Os portadores: eltrons e lacunas

1.1.2 Semicondutores dopados

1.1.3 Recombinao

1.1.4 Correntes de deriva e de difuso

1.2 DIODOS DE POTNCIA

1.3 DIODOS SCHOTTKY

1.4 TIRISTOR

1.4.1 Princpio de funcionamento

1.4.2 Maneiras de disparar um tiristor

1.4.3 Parmetros bsicos de tiristores

1.4.4 Circuitos de excitao do gate

1.4.5 Redes Amaciadoras

1.4.6 Associao em Paralelo de Tiristores

1.4.7 Associao em srie de tiristores

1.4.8 Sobre-tenso

1.4.9 Resfriamento

1.5 GTO - GATE TURN-OFF THYRISTOR

1.5.1 Princpio de funcionamento

1.5.2 Parmetros bsicos do GTO

1.5.3 Condies do sinal de porta para chaveamento

1.5.4 Circuitos amaciadores (snubber)

1.5.5 Associaes em srie e em paralelo

1.6 TRANSISTOR BIPOLAR DE POTNCIA (TBP)

1.6.1 Princpio de funcionamento

1.6.2 Limites de tenso

1.6.3 rea de Operao Segura (AOS)

1.6.4 Regio de quase-saturao

1.6.5 Ganho de corrente

1.6.6 Caractersticas de chaveamento

1.6.7 Circuitos amaciadores (ou de ajuda comutao) - "snubber"

1.6.8 Conexo Darlington

1.6.9 Mtodos de reduo dos tempos de chaveamento

1.7 MOSFET

1.7.1 Princpio de funcionamento (canal N)

1.7.2 rea de Operao Segura

1.7.3 Caracterstica de chaveamento - carga indutiva

1.8 IGBT (INSULATED GATE BIPOLAR TRANSISTOR)

1.8.1 Princpio de funcionamento

1.8.2 Caractersticas de chaveamento

1.9 ALGUNS CRITRIOS DE SELEO ENTRE TRANSISTORES

1.10 MCT - MOS-CONTROLLED THYRISTOR

1.10.1 Princpio de funcionamento

1.10.2 Comparao entre P-MCT e N-MCT

1.11 MATERIAIS EMERGENTES

1.12 REFERNCIAS BIBLIOGRFICAS

iv

2. TCNICAS DE MODULAO DE POTNCIA

2.1 CONTROLE POR CICLOS INTEIROS

2.2 CONTROLE DE FASE

2.3 MODULAO POR ONDA QUADRADA

2.3.1 Modulao com onda quase-quadrada.

2.4 MODULAO MULTINVEL

2.5 MODULAO POR LARGURA DE PULSO - MLP

2.6 MODULAO EM FREQNCIA - MF

2.7 MODULAO POR LIMITES DE CORRENTE - MLC (HISTERESE)

2.8 MODULAO MLP COM FREQNCIA DE PORTADORA VARIVEL

2.9 ELIMINAO DE HARMNICAS

2.10 OUTRAS TCNICAS DE MODULAO

2.10.1 Controle One-cycle

2.10.2 Controle de carga

2.10.3 Modulao Delta

2.11 MODULAO VETORIAL

2.11.1 Saturao

2.12 REFERNCIAS BIBLIOGRFICAS

3. CONVERSORES CA-CC - RETIFICADORES

3.1 RETIFICADORES NO CONTROLADOS

3.1.1 Retificadores no-controlados com entrada trifsica

3.2 FATOR DE POTNCIA

3.2.1 Definio de Fator de Potncia

3.2.2 Desvantagens do baixo fator de potncia (FP) e da alta distoro da corrente

3.3 NORMAS IEC 1000-3-2: DISTRBIOS CAUSADOS POR EQUIPAMENTO

CONECTADO REDE PBLICA DE BAIXA TENSO

3.4 RETIFICADORES COM ALTO FATOR DE POTNCIA

3.4.1 Solues passivas

3.4.2 Solues ativas para retificadores com alto FP

3.5 COMUTAO

3.6 RETIFICADORES CONTROLADOS

3.6 ASSOCIAO DE RETIFICADORES

3.7 RETIFICADOR MLP

3.7.1 Equaes bsicas

3.7.2 Absoro de reativos

3.7.3 Controle da corrente CC

3.8 REFERNCIAS BIBLIOGRFICAS

4. CONVERSORES CC-CC PARA ACIONAMENTO DE MQUINAS DE

CORRENTE CONTNUA

4.1 PRINCPIOS DE ACIONAMENTO DE MQUINAS DE CORRENTE CONTNUA

4.1.1 Equaes estticas

4.1.2 Equaes dinmicas

4.1.3 Quadrantes de operao

4.2 TOPOLOGIAS DE CONVERSORES PARA ACIONAMENTO DE MCC

4.2.1 Conversor Classe A

4.2.2 Conversor Classe B

4.2.3 Conversor Classe C

4.2.4 Conversor Classe D

v

4.2.5 Conversor Classe E

4.3 REFERNCIAS BIBLIOGRFICAS

5. TOPOLOGIAS BSICAS DE FONTES CHAVEADAS

5.1 CONVERSOR ABAIXADOR DE TENSO (STEP-DOWN OU BUCK): VO<E

5.1.1 Modo de conduo contnua (MCC)

5.1.2 Modo de conduo descontnua (MCD)

5.1.3 Dimensionamento de L e de C

5.2 CONVERSOR ELEVADOR DE TENSO (STEP-UP OU BOOST): VO>E

5.2.1 Modo de conduo contnua

5.2.2 Modo de conduo descontnua

5.2.3 Dimensionamento de L e de C

5.3 CONVERSOR ABAIXADOR-ELEVADOR (BUCK-BOOST)

5.3.1 Modo de conduo contnua

5.3.2 Modo de conduo descontnua

5.3.3 Clculo de L e de C

5.4 CONVERSOR `CUK

5.4.1 Dimensionamento de C1

5.4.2 Dimensionamento de L1

5.4.3 Clculo de L2

5.4.4 Clculo de Co (capacitor de sada)

5.5 CONVERSOR SEPIC

5.6 CONVERSOR ZETA

5.7 CONVERSORES COM ISOLAO

5.7.1 Conversor `Cuk

5.7.2 Conversores SEPIC e Zeta isolados

5.7.3 Conversor fly-back (derivado do abaixador-elevador)

5.7.4 Conversor forward (derivado do abaixador de tenso)

5.7.5 Conversor push-pull

5.8 CONSIDERAO SOBRE A MXIMA TENSO DE SADA NO CONVERSOR

ELEVADOR DE TENSO

5.9 REFERNCIAS BIBLIOGRFICAS

6. CONVERSORES CC-CA COMO FONTES DE ALIMENTAO COM

FREQUNCIA FIXA

6.1 REQUISITOS DE QUALIDADE NA ALIMENTAO DE EQUIPAMENTOS

SENSVEIS

6.2 CLASSIFICAO DAS UPS

6.3 OUTRAS CARACTERSTICAS DE UPS

6.3.1 Forma de onda da sada

6.3.2 Isolao eltrica

6.3.3 Paralelismo

6.4 COMPONENTES DE UMA UPS ESTTICA

6.4.1 Retificador

6.4.2 Inversor

6.4.3 A chave esttica ou by-pass

6.5 RESULTADOS EXPERIMENTAIS

6.5.1 Linha prioritria

6.5.2 Inversor prioritrio

6.6 REFERNCIAS BIBLIOGRFICAS

vi

7. CONVERSORES CC-CA PARA ACIONAMENTO DE MQUINA DE INDUO

TRIFSICA

7.1 MODELAMENTO DA MQUINA DE INDUO TRIFSICA

7.2 MTODOS DE CONTROLE DA VELOCIDADE DE MQUINA DE INDUO

7.2.1 Controle pela resistncia

7.2.2 Controle pela tenso de alimentao do estator

7.2.3 Controle pela variao da freqncia

7.2.4 Controle da tenso e da freqncia

7.2.5 Controle da corrente

7.3 INVERSORES DE TENSO

7.4 INVERSORES DE CORRENTE

7.4.1 Inversor a tiristores

7.4.2 Inversor com IGBT (ou GTO)

7.5 REFERNCIAS BIBLIOGRFICAS

8. INVERSORES DE TENSO COM COMUTAO SUAVE

8.1 INVERSOR COM LINK CC RESSONANTE

8.2 INVERSOR COM LINK CC RESSONANTE COM LIMITAO DA SOBRE-

TENSO

8.3 INVERSOR MLP COM LINK QUASE-RESSONANTE

8.3.1 Princpio de operao

8.3.2 Dimensionamento dos componentes

8.4 INVERSOR COM POLO RESSONANTE AUXILIAR

8.4.1 Princpio de funcionamento do circuito auxiliar de comutao

8.5 INVERSOR/RETIFICADOR MLP COM COMUTAO ZVS COM CIRCUITO

AUXILIAR

8.5.1 Princpio de funcionamento

8.6 REFERNCIAS BIBLIOGRFICAS

9. INVERSORES E RETIFICADORES DE CORRENTE COM COMUTAO SUAVE

.

9.1 RETIFICADOR/INVERSOR COM LINK CC RESSONANTE EM SRIE

9.2 INVERSORES/RETIFICADORES MLP COM COMUTAO ZCS

9.2.1 Princpio de funcionamento

9.2.2 Dimensionamento dos componentes

9.3 INVERSORES/RETIFICADORES MLP COM COMUTAO ZVS

9.3.1 Dimensionamento dos componentes

9.3.2 Funcionamento do circuito como inversor

9.4 REFERNCIAS BIBLIOGRFICAS

10. CONVERSORES CA-CA: VARIADORES DE TENSO E CICLOCONVERSORES

10.1 VARIADORES DE TENSO

10.1.1 Controle Liga-Desliga

10.1.2 Controle de fase

10.2 CIRCUITOS MONOFSICOS

10.2.1 Carga Resistiva

10.2.2 Carga indutiva

vii

10.2.3 Carga RL

10.3 VARIADORES DE TENSO TRIFSICO

10.3.1 Carga resistiva

10.3.2 Carga indutiva (em Y sem neutro)

10.3.3 Carga RL

10.4 EXEMPLO DE APLICAO

10.4.1 Linha sem compensao

10.4.2 CCT atuando e sada de carga

10.4.3 CCT atuando, sada de carga e atuao do RCT

10.5 CICLOCONVERSORES COM COMUTAO NATURAL

10.6 CONVERSOR EM MATRIZ

10.7 REFERNCIAS BIBLIOGRFICAS

11. DIMENSIONAMENTO DE SISTEMAS DE DISSIPAO DE CALOR PARA

DISPOSITIVOS SEMICONDUTORES DE POTNCIA

11.1 INTRODUO

11.2 CLCULO DA POTNCIA DISSIPADA

11.2.1 Diodos

11.2.2 Tiristores

11.2.3 Transistores

11.3 COMPORTAMENTO EM REGIME PERMANENTE: POTNCIA MDIA

11.3.1 Dissipador de calor

11.4 COMPORTAMENTO EM REGIME TRANSITRIO: POTNCIA DE PICO

11.5 CLCULO DE DISSIPADORES

11.6 FONTES DE CALOR DISTRIBUDAS

11.7 REFRIGERAO FORADA

11.8 REFERNCIAS BIBLIOGRFICAS

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-1

1. COMPONENTES SEMICONDUTORES DE POTNCIA

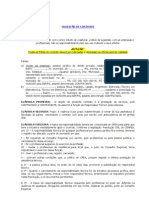

A figura 1.1 mostra uma distribuio dos componentes semicondutores, indicando

limites (1994) para valores de tenso de bloqueio, corrente de conduo e freqncia de

comutao. Obviamente estes limites evoluem com o desenvolvimento tecnolgico e servem

como uma ilustrao para a verificao, numa primeira aproximao, das faixas de potncia

em que cada componente pode ser utilizado.

Tiristores

GTO

IGBT

MCT

TBP

MOSFET

Tenso

5kV

4kV

3kV

2kV

1kV

1kA 2kA 3kA

Corrente

Frequncia

1kHz

10kHz

100kHz

1MHz

Figura 1.1 Limites de operao de componentes semicondutores de potncia.

1.1 Breve Reviso da Fsica de Semicondutores

A passagem de corrente eltrica em um meio depende da aplicao de um campo

eltrico e da existncia de portadores livres (usualmente eltrons) neste meio. Em metais,

como o cobre ou a prata, a densidade de portadores livres (eltrons) da ordem de 10

23

/cm

3

,

enquanto nos materiais isolantes, como o quartzo ou o xido de alumnio, o valor da ordem

de 10

3

/cm

3

. Os chamados semicondutores, como o silcio, tem densidades intermedirias, na

faixa de 10

8

a 10

19

/cm

3

. Nos condutores e nos isolantes, tais densidades so propriedades dos

materiais, enquanto nos semicondutores estas podem ser variadas, seja pela adio de

impurezas de outros materiais, seja pela aplicao de campos eltricos em algumas

estruturas de semicondutores.

1.1.1 Os portadores: eltrons e lacunas

tomos de materias com 4 eltrons em sua camada mais externa (C, Ge, Si, etc.), ou

ainda molculas com a mesma propriedade, permitem o estabelecimento de ligaes muito

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-2

estveis, uma vez que, pelo compartilhamento dos eltrons externos pelos tomos vizinhos

(ligao covalente), tem-se um arranjo com 8 eltrons na camada de valncia, como ilustra a

figura 1.2.

eltrons

compartilhados

ncleos

atmicos

Figura 1.2 Estrutura cristalina de material semicondutor

Em qualquer temperatura acima do zero absoluto (-273

o

C), algumas destas ligaes

so rompidas (ionizao trmica), produzindo eltrons livres. O tomo que perde tal eltron se

torna positivo. Eventualmente um outro eltron tambm escapa de outra ligao e, atrado pela

carga positiva do tomo, preenche a ligao covalente. Desta maneira tem-se uma

movimentao relativa da carga positiva, chamada de lacuna, que, na verdade, devida ao

deslocamento dos eltrons que saem de suas ligaes covalentes e vo ocupar outras, como

mostra a figura 1.3.

eltron

ligao

rompida

tomo

ionizado

movimento

da lacuna

Figura 1.3 Movimento de eltrons e lacunas em semicondutor

A ionizao trmica gera o mesmo nmero de eltrons e lacunas. Em um material

puro, a densidade de portadores aproximadamente dada por:

kT

qE

i

g

e C n

(1.1)

onde C uma constante de proporcionalidade, q a carga do eltron (valor absoluto), E

g

a

banda de energia do semicondutor (1,1 eV para o Si), k a constante de Boltzmann, T a

temperatura em Kelvin. Para o Si, temperatura ambiente (300K), n

i

10

10

/cm

3

.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-3

1.1.2 Semicondutores dopados

Quando se faz a adio de tomos de materiais que possuam 3 (como o alumnio ou o

boro) ou 5 eltrons (como o fsforo) em sua camada de valncia estrutura dos

semicondutores, os tomos vizinhos a tal impureza tero suas ligaes covalentes incompletas

ou com excesso de eltrons, como mostra a figura 1.4.

Si

Si Si

Si

Si

Si Si Si

Bo

ligao

incompleta

Si

Si Si

Si

Si

Si Si Si

P

eltron

em excesso

Figura 1.4 Semicondutores dopados

Neste caso no tem-se mais o equilbrio entre eltrons e lacunas, passando a existir um

nmero maior de eltrons livres nos materiais dopados com elementos da quinta coluna da

tabela peridica, ou de lacunas, caso a dopagem seja com elementos da terceira coluna.

Respectivamente, produzem-se os chamados materiais semicondutores tipo N e tipo P.

Observe-se, no entanto, que o material permanece eletricamente neutro, uma vez que a

quantidade total de eltrons e prtons a mesma.

Quando a lacuna introduzida pelo boro captura um eltron livre, tem-se a

movimentao da lacuna. Neste caso diz-se que as lacunas so os portadores majoritrios,

sendo os eltrons os portadores minoritrios.

J no material tipo N, a movimentao do eltron excedente deixa o tomo ionizado, o

que o faz capturar outro eltron livre. Neste caso os portadores majoritrios so os eltrons,

enquanto os minoritrios so as lacunas.

As dopagens das impurezas (10

19

/cm

3

ou menos), tipicamente so feitas em nveis

muito menores que a densidade de tomos do material semicondutor (10

23

/cm

3

), de modo que

as propriedades de ionizao trmica no so afetadas.

Mesmo em um material dopado, o produto das densidades de lacunas e de eltrons (p

o

e n

o

, respectivamente) igual ao valor n

i

2

dado pela equao (1.1), embora aqui p

o

n

o

.

Alm da ionizao trmica, tem-se uma quantidade adicional de cargas livres,

relativas s prprias impurezas. Pelos valores indicados anteriormente, pode-se verificar que a

concentrao de tomos de impurezas muitas ordens de grandeza superior densidade de

portadores gerados por efeito trmico, de modo que, num material tipo P, p

o

N

a

, onde N

a

a densidade de impurezas aceitadoras de eltrons. J no material tipo N, n

o

N

d

, onde N

d

a densidade de impurezas doadoras de eltrons.

Em qualquer dos materiais, a densidade dos portadores minoritrios proporcional ao

quadrado da densidade intrnseca, n

i

, e fortemente dependente da temperatura.

o

2

i

o

p

n

n ,

a o

N p (1.2)

o

2

i

o

n

n

p ,

d o

N n (1.3)

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-4

1.1.3 Recombinao

Uma vez que a quantidade n

i

determinada apenas por propriedades do material e pela

temperatura, necessrio que exista algum mecanismo que faa a recombinao do excesso

de portadores medida que novos portadores so criados pela ionizao trmica.

Tal mecanismo inclui tanto a recombinao propriamente dita de um eltron com uma

lacuna em um tomo de Si, quanto a captura dos eltrons pela impureza ionizada., ou,

adicionalmente, por imperfeies na estrutura cristalina. Tais imperfeies fazem com que os

tomos adjacentes no necessitem realizar 4 ligaes covalentes.

Pode-se definir o tempo de vida de um portador como o tempo mdio necessrio

para que o eltron ou a lacuna sejam neutralizados pela consecusso de uma ligao

covalente. Em muitos casos pode-se considerar o tempo de vida de um portador como uma

constante do material. No entanto, especialmente nos semicondutores de potncia, esta no

uma boa simplificao.

Quando ocorre um significativo aumento na temperatura do semicondutor, tem-se um

aumento no tempo de recombinao do excesso de portadores, o que leva a um aumento nos

tempos de comutao dos dispositivos de tipo portadores minoritrios, como o transistor

bipolar e os tiristores.

J em situaes de alta dopagem (10

17

/cm

3

ou superior), a taxa de recombinao

aumenta,o que leva a um crescimento da queda de tenso sobre o dispositivo quando este est

em conduo.

Uma vez que este tempo de vida dos portadores afeta significantemente o

comportamento dos dispositivos de potncia, a obteno de mtodos que possam control-lo

importante. Um dos mtodos que possibilita o ajuste deste tempo a dopagem com ouro,

uma vez que este elemento funciona como um centro de recombinao, uma vez que realiza

tal operao com grande facilidade. Outro mtodo o da irradiao de eltrons de alta energia,

bombardeando a estrutura cristalina de modo a deform-la e, assim, criar centros de

recombinao. Este ltimo mtodo tem sido preferido devido sua maior controlabilidade (a

energia dos eltrons facilmente controlvel, permitindo estabelecer a que profundidade do

cristal se quer realizar as deformaes) e por ser aplicado no final do processo de construo

do componente.

1.1.4 Correntes de deriva e de difuso

Quando um campo eltrico for aplicado a um material semicondutor, as lacunas se

movimentaro no sentido do campo decrescente, enquanto os eltrons seguiro em sentido

oposto. Esta corrente depende de um parmetro denominado mobilidade, que depende do

material e do tipo de portador. A mobilidade dos eltrons aproximadamente 3 vezes maior

do que a das lacunas para o Si em temperatura ambiente. A mobilidade diminui

aproximadamente com o quadrado do aumento da temperatura.

Outro fator de movimentao de portadores por difuso, quando existem regies

adjacentes em que h diferentes concentraes de portadores. O movimento aleatrio dos

portadores tende a equalizar sua disperso pelo meio, de modo que tende a haver uma

migrao de portadores das regies mais concentradas para as mais dispersas.

1.2 Diodos de Potncia

Um diodo semicondutor uma estrutura P-N que, dentro de seus limites de tenso e de

corrente, permite a passagem de corrente em um nico sentido. Detalhes de funcionamento,

em geral desprezados para diodos de sinal, podem ser significativos para componentes de

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-5

maior potncia, caracterizados por uma maior rea (para permitir maiores correntes) e maior

comprimento (a fim de suportar tenses mais elevadas). A figura 1.5 mostra,

simplificadamente, a estrutura interna de um diodo.

Aplicando-se uma tenso entre as regies P e N, a diferena de potencial aparecer na

regio de transio, uma vez que a resistncia desta parte do semicondutor muito maior que

a do restante do componente (devido concentrao de portadores).

Quando se polariza reversamente um diodo, ou seja, se aplica uma tenso negativa no

anodo (regio P) e positiva no catodo (regio N), mais portadores positivos (lacunas) migram

para o lado N, e vice-versa, de modo que a largura da regio de transio aumenta, elevando a

barreira de potencial.

P N

+ + + + + + + +

+ + + + + + +

+ + + + + + +

+ + + + + + +

+ + + + + + +

+

+ _ _ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _ _

+

_ _

_ _

_ _

_ _

_ _

+ +

+ +

+ +

+ +

+ +

1 u

Potencial

0

+

_

Difuso

Juno metalrgica

Anodo Catodo

Figura 1.5 Estrutura bsica de um diodo semicondutor.

Por difuso ou efeito trmico, uma certa quantidade de portadores minoritrios penetra

na regio de transio. So, ento, acelerados pelo campo eltrico, indo at a outra regio

neutra do dispositivo. Esta corrente reversa independe da tenso reversa aplicada, variando,

basicamente, com a temperatura.

Se o campo eltrico na regio de transio for muito intenso, os portadores em trnsito

obtero grande velocidade e, ao se chocarem com tomos da estrutura, produziro novos

portadores, os quais, tambm acelerados, produziro um efeito de avalanche. Dado o aumento

na corrente, sem reduo significativa na tenso na juno, produz-se um pico de potncia que

destri o componente.

Uma polarizao direta leva ao estreitamento da regio de transio e reduo da

barreira de potencial. Quando a tenso aplicada superar o valor natural da barreira, cerca de

0,7V para diodos de Si, os portadores negativos do lado N sero atrados pelo potencial

positivo do anodo e vice-versa, levando o componente conduo.

Na verdade, a estrutura interna de um diodo de potncia um pouco diferente desta

apresentada. Existe uma regio N intermediria, com baixa dopagem. O papel desta regio

permitir ao componente suportar tenses mais elevadas, pois tornar menor o campo eltrico

na regio de transio (que ser mais larga, para manter o equilbrio de carga).

Esta regio de pequena densidade de dopante dar ao diodo uma significativa

caracterstica resistiva quando em conduo, a qual se torna mais significativa quanto maior

for a tenso suportvel pelo componente. As camadas que fazem os contatos externos so

altamente dopadas, a fim de fazer com que se obtenha um contato com caracterstica hmica e

no semi-condutor.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-6

O contorno arredondado entre as regies de anodo e catodo tem como funo criar

campos eltricos mais suaves (evitando o efeito de pontas).

No estado bloqueado, pode-se analisar a regio de transio como um capacitor, cuja

carga aquela presente na prpria regio de transio.

Na conduo no existe tal carga, no entanto, devido alta dopagem da camada P+,

por difuso, existe uma penetrao de lacunas na regio N-. Alm disso, medida que cresce

a corrente, mais lacunas so injetadas na regio N-, fazendo com que eltrons venham da

regio N+ para manter a neutralidade de carga. Desta forma, cria-se uma carga espacial no

catodo, a qual ter que ser removida (ou se recombinar) para permitir a passagem para o

estado bloqueado do diodo.

O comportamento dinmico de um diodo de potncia , na verdade, muito diferente do

de uma chave ideal, como se pode observar na figura 1.6. Suponha-se que se aplica uma

tenso v

i

ao diodo, alimentando uma carga resistiva (cargas diferentes podero alterar alguns

aspectos da forma de onda).

Durante t1, remove-se a carga acumulada na regio de transio. Como ainda no

houve significativa injeo de portadores, a resistncia da regio N- elevada, produzindo um

pico de tenso. Indutncias parasitas do componente e das conexes tambm colaboram com a

sobre-tenso. Durante t2 tem-se a chegada dos portadores e a reduo da tenso para cerca de

1V. Estes tempos so, tipicamente, da ordem de centenas de ns.

No desligamento, a carga espacial presente na regio N- deve ser removida antes que

se possa reiniciar a formao da barreira de potencial na juno. Enquanto houver portadores

transitando, o diodo se mantm em conduo. A reduo em V

on

se deve diminuio da

queda hmica. Quando a corrente atinge seu pico negativo que foi retirado o excesso de

portadores, iniciando-se, ento, o bloqueio do diodo. A taxa de variao da corrente, associada

s indutncias do circuito, provoca uma sobre-tenso negativa.

Anodo

Catodo

N+

N

_

P+ 10e19 cm-3

10e14 cm-3

10e19cm-3

10 u

Depende

250 u

substrato

da tenso

i

D

v

D

v

i

+Vr

-Vr

Qrr

t1

t2

t3

t4 t5

-Vr

i=Vr/R

Von

trr

dir/dt

Vfp

Vrp

dif/dt

vi

v

D

i

D

R

Figura 1.6 - Estrutura tpica de diodo de potncia e formas de onda tpicas de comutao de

diodo de potncia.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-7

A figura 1.7 mostra resultados experimentais de um diodo de potncia lento

(retificador) em um circuito como o da figura 1.6, no qual a indutncia desprezvel, como se

nota na figura (a), pela inverso quase imediata da polaridade da corrente. A corrente reversa

limitada pela resistncia presente no circuito. J na entrada em conduo, a tenso aplicada

ao circuito aparece instantaneamente sobre o prprio diodo, o que contribui para limitar o

crescimento da corrente. Quando esta tenso cai, a corrente vai assumindo seu valor de

regime.

(a) (b)

Figura 1.7 - Resultados experimentais das comutaes de diodo: (a) desligamento;

(b) entrada em conduo.

Diodos rpidos possuem t

rr

da ordem de, no mximo, poucos micro-segundos,

enquanto nos diodos normais de dezenas ou centenas de micro-segundos.

O retorno da corrente a zero, aps o bloqueio, devido sua elevada derivada e ao fato

de, neste momento, o diodo j estar desligado, uma fonte importante de sobretenses

produzidas por indutncias parasitas associadas aos componentes por onde circula tal

corrente. A fim de minimizar este fenmeno foram desenvolvidos os diodos soft-recovery,

nos quais esta variao de corrente suavizada, reduzindo os picos de tenso gerados.

Em aplicaes nas quais o diodo comuta sob tenso nula, como o caso dos

retificadores com filtro capacitivo, praticamente no se observa o fenmeno da recombinao

reversa.

1.3 Diodos Schottky

Quando feita uma juno entre um terminal metlico e um material semicondutor, o

contato tem, tipicamente, um comportamento hmico, ou seja, a resistncia do contato

governa o fluxo da corrente. Quando este contato feito entre um metal e uma regio

semicondutora com densidade de dopante relativamente baixa, o efeito dominante deixa de ser

o resistivo, passando a haver tambm um efeito retificador.

Um diodo Schottky formado colocando-se um filme metlico em contato direto com

um semicondutor, como indicado na figura 1.8. O metal usualmente depositado sobre um

material tipo N, por causa da maior mobilidade dos portadores neste tipo de material. A parte

metlica ser o anodo e o semicondutor, o catodo.

Numa deposio de Al (3 eltrons na ltima camada), os eltrons do semicondutor tipo

N migraro para o metal, criando uma regio de transio na juno.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-8

Note-se que apenas eltrons (portadores majoritrios em ambos materiais) esto em

trnsito. O seu chaveamento muito mais rpido do que o dos diodos bipolares, uma vez que

no existe carga espacial armazenada no material tipo N, sendo necessrio apenas refazer a

barreira de potencial (tipicamente de 0,3V). A regio N+ tem uma dopagem relativamente

alta, a fim de reduzir as perdas de conduo, com isso, a mxima tenso suportvel por estes

diodos de cerca de 100V.

A aplicao deste tipo de diodos ocorre principalmente em fontes de baixa tenso, nas

quais as quedas sobre os retificadores so significativas.

Na figura 1.4.(b) tem-se uma forma de onda tpica no desligamento do componente.

Note que, diferentemente dos diodos convencionais, assim que a corrente se inverte a tenso

comea a crescer, indicando a no existncia dos portadores minoritrios no dispositivo.

Substrato tipo P

Tipo N

N+

Al

SiO2

Al

contato

hmico

contato

retificador

(a) (b)

Figura 1.8 - (a) Estrutura de diodo Schottky; (b) Forma de onda tpica no desligamento

1.4 Tiristor

O nome tiristor engloba uma famlia de dispositivos semicondutores que operam em

regime chaveado, tendo em comum uma estrutura de 4 camadas semicondutoras numa

sequncia p-n-p-n, apresentando um funcionamento biestvel.

O tiristor de uso mais difundido o SCR (Retificador Controlado de Silcio),

usualmente chamado simplesmente de tiristor. Outros componentes, no entanto, possuem

basicamente uma mesma estrutura: LASCR (SCR ativado por luz), tambm chamado de LTT

(Light Triggered Thyristor), TRIAC (tiristor triodo bidirecional), DIAC (tiristor diodo

bidirecional), GTO (tiristor comutvel pela porta), MCT (Tiristor controlado por MOS).

1.4.1 Princpio de funcionamento

O tiristor formado por quatro camadas semicondutoras, alternadamente p-n-p-n,

possuindo 3 terminais: anodo e catodo, pelos quais flui a corrente, e a porta (ou gate) que, a

uma injeo de corrente, faz com que se estabelea a corrente andica. A figura 1.9 ilustra

uma estrutura simplificada do dispositivo.

Se entre anodo e catodo tivermos uma tenso positiva, as junes J1 e J3 estaro

diretamente polarizadas, enquanto a juno J2 estar reversamente polarizada. No haver

conduo de corrente at que a tenso Vak se eleve a um valor que provoque a ruptura da

barreira de potencial em J2.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-9

Se houver uma tenso Vgk positiva, circular uma corrente atravs de J3, com

portadores negativos indo do catodo para a porta. Por construo, a camada P ligada porta

suficientemente estreita para que parte destes eltrons que cruzam J3 possuam energia cintica

suficiente para vencer a barreira de potencial existente em J2, sendo ento atrados pelo

anodo.

A

Anodo

A K

G

Gate G

K Catodo

Vcc Rc (carga)

Rg

Vg

Rg

Vg

CH

Rc

Vcc

P N- P N+

J1 J2 J3

Figura 1.9 - Funcionamento bsico do tiristor e seu smbolo.

Desta forma, a juno reversamente polarizada tem sua diferena de potencial

diminuda e estabelece-se uma corrente entre anodo e catodo, que poder persistir mesmo na

ausncia da corrente de porta.

Quando a tenso Vak for negativa, J1 e J3 estaro reversamente polarizadas, enquanto

J2 estar diretamente polarizada. Uma vez que a juno J3 intermediria a regies de alta

dopagem, ela no capaz de bloquear tenses elevadas, de modo que cabe juno J1 manter

o estado de bloqueio do componente.

comum fazer-se uma analogia entre o funcionamento do tiristor e o de uma

associao de dois transistores, conforme mostrado na figura 1.10.

Quando uma corrente Ig positiva aplicada, Ic2 e Ik crescero. Como Ic2 = Ib1, T1

conduzir e teremos Ib2=Ic1 + Ig, que aumentar Ic2 e assim o dispositivo evoluir at a

saturao, mesmo que Ig seja retirada. Tal efeito cumulativo ocorre se os ganhos dos

transistores forem maior que 1. O componente se manter em conduo desde que, aps o

processo dinmico de entrada em conduo, a corrente de anodo tenha atingido um valor

superior ao limite I

L

, chamado de corrente de "latching".

Para que o tiristor deixe de conduzir necessrio que a corrente por ele caia abaixo do

valor mnimo de manuteno (I

H

), permitindo que se restabelea a barreira de potencial em J2.

Para a comutao do dispositivo no basta, pois, a aplicao de uma tenso negativa entre

anodo e catodo. Tal tenso reversa apressa o processo de desligamento por deslocar nos

sentidos adequados os portadores na estrutura cristalina, mas no garante, sozinha, o

desligamento.

Devido a caractersticas construtivas do dispositivo, a aplicao de uma polarizao

reversa do terminal de gate no permite a comutao do SCR. Este ser um comportamento

dos GTOs, como se ver adiante.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-10

P

N

P

N

P

N

A

K

G

A

K

G

Ia

Ik

T2

T1

Ib1

Ic2

Ig Ib2

Ic1

Figura 1.10 - Analogia entre tiristor e transistores bipolares

1.4.2 Maneiras de disparar um tiristor

Podemos considerar cinco maneiras distintas de fazer com que um tiristor entre em

conduo:

a) Tenso

Quando polarizado diretamente, no estado desligado, a tenso de polarizao

aplicada sobre a juno J2. O aumento da tenso Vak leva a uma expanso da regio de

transio tanto para o interior da camada do gate quanto para a camada N adjacente. Mesmo

na ausncia de corrente de gate, por efeito trmico, sempre existiro cargas livre que penetram

na regio de transio (no caso, eltrons), as quais so aceleradas pelo campo eltrico presente

em J2. Para valores elevados de tenso (e, consequentemente, de campo eltrico), possvel

iniciar um processo de avalanche, no qual as cargas aceleradas, ao chocarem-se com tomos

vizinhos, provoquem a expulso de novos portadores, os quais reproduzem o processo. Tal

fenmeno, do ponto de vista do comportamento do fluxo de cargas pela juno J2, tem efeito

similar ao de uma injeo de corrente pelo gate, de modo que, se ao se iniciar a passagem de

corrente for atingido o limiar de I

L

, o dispositivo se manter em conduo. A figura. 1.11

mostra a caracterstica esttica de um SCR.

b) Ao da corrente positiva de porta

Sendo o disparo atravs da corrente de porta a maneira mais usual de ser ligado o

tiristor, importante o conhecimento dos limites mximos e mnimos para a tenso Vgk e a

corrente Ig, como mostrados na figura 1.12.

O valor Vgm indica a mnima tenso de gate que garante a conduo de todos os

componentes de um dado tipo, na mnima temperatura especificada.

O valor Vgo a mxima tenso de gate que garante que nenhum componente de um

dado tipo entrar em conduo, na mxima temperatura de operao.

A corrente Igm a mnima corrente necessria para garantir a entrada em conduo de

qualquer dispositivo de um certo tipo, na mnima temperatura.

Para garantir a operao correta do componente, a reta de carga do circuito de

acionamento deve garantir a passagem alm dos limites Vgm e Igm, sem exceder os demais

limites (tenso, corrente e potncia mximas).

c) Taxa de crescimento da tenso direta

Quando reversamente polarizadas, a rea de transio de uma juno comporta-se de

maneira similar a um capacitor, devido ao campo criado pela carga espacial. Considerando

que praticamente toda a tenso est aplicada sobre a juno J2 (quando o SCR estiver

desligado e polarizado diretamente), a corrente que atravessa tal juno dada por:

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-11

( )

I

d C V

dt

C

dV

dt

V

dC

dt

j

j ak

j

ak

ak

j

=

= + (1.4)

Onde C

j

a capacitncia da juno.

Vak

Ia

Von

I

I

L

H

Vbo

Vbr

Ig2 > Ig1 > Ig=0

Figura 1.11 - Caracterstica esttica do tiristor.

Mxima tenso de gate

Mxima potncia

Instantnea de gate

Ig

Vgk

6V

0,5A 0

0

Igm

Vgm

Vgo

Limite de

baixa corrente

Limite de

alta corrente

Reta de carga

do circuito de acionamento

Figura 1.12 - Condies para disparo de tiristor atravs de controle pela porta.

Quando V

ak

cresce, a capacitncia diminui, uma vez que a regio de transio aumenta

de largura. Entretanto, se a taxa de variao da tenso for suficientemente elevada, a corrente

que atravessar a juno pode ser suficiente para levar o tiristor conduo.

Uma vez que a capacitncia cresce com o aumento da rea do semicondutor, os

componentes para correntes mais elevadas tendem a ter um limite de dv/dt menor. Observe-se

que a limitao diz respeito apenas ao crescimento da tenso direta (V

ak

> 0). A taxa de

crescimento da tenso reversa no importante, uma vez que as correntes que circulam pelas

junes J1 e J3, em tal situao, no tem a capacidade de levar o tiristor a um estado de

conduo.

Como se ver adiante, utilizam-se circuitos RC em paralelo com os tiristores com o

objetivo de limitar a velocidade de crescimento da tenso direta sobre eles.

d) Temperatura

A altas temperaturas, a corrente de fuga numa juno p-n reversamente polarizada

dobra aproximadamente com o aumento de 8

o

C. Assim, a elevao da temperatura pode levar

a uma corrente atravs de J2 suficiente para levar o tiristor conduo.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-12

e) Energia radiante

Energia radiante dentro da banda espectral do silcio, incidindo e penetrando no cristal,

produz considervel quantidade de pares eltron-lacuna, aumentando a corrente de fuga

reversa, possibilitando a conduo do tiristor. Este tipo de acionamento o utilizado nos

LASCR, cuja aplicao principal em sistemas que operam em elevado potencial, onde a

isolao necessria s obtida por meio de acoplamentos ticos.

1.4.3 Parmetros bsicos de tiristores

Apresentaremos a seguir alguns parmetros tpicos de tiristores e que caracterizam

condies limites para sua operao. Alguns j foram apresentados e comentados

anteriormente e sero, pois, apenas citados aqui.

Tenso direta de ruptura (V

BO

)

Mxima tenso reversa (V

BR

)

Mxima corrente de anodo (I

amax

): pode ser dada como valor RMS, mdio, de pico e/ou

instantneo.

Mxima temperatura de operao (T

jmax

): temperatura acima da qual, devido a um possvel

processo de avalanche, pode haver destruio do cristal.

Resistncia trmica (R

th

): a diferena de temperatura entre 2 pontos especificados ou

regies, dividido pela potncia dissipada sob condies de equilbrio trmico. uma

medida das condies de fluxo de calor do cristal para o meio externo.

Caracterstica I2t: o resultado da integral do quadrado da corrente de anodo num

determinado intervalo de tempo, sendo uma medida da mxima potncia dissipvel pelo

dispositivo. dado bsico para o projeto dos circuitos de proteo.

Mxima taxa de crescimento da tenso direta Vak (dv/dt).

Mxima taxa de crescimento da corrente de anodo (di/dt): fisicamente, o incio do

processo de conduo de corrente pelo tiristor ocorre no centro da pastilha de silcio, ao

redor da regio onde foi construda a porta, espalhando-se radialmente at ocupar toda a

superfcie do catodo, medida que cresce a corrente. Mas se a corrente crescer muito

rapidamente, antes que haja a expanso necessria na superfcie condutora, haver um

excesso de dissipao de potncia na rea de conduo, danificando a estrutura

semicondutora. Este limite ampliado para tiristores de tecnologia mais avanada

fazendo-se a interface entre gate e catodo com uma maior rea de contato, por exemplo,

'interdigitando" o gate. A figura 1.13 ilustra este fenmeno.

Corrente de manuteno de conduo (I

H

): a mnima corrente de anodo necessria para

manter o tiristor em conduo.

Corrente de disparo (I

L

): mnima corrente de anodo requerida para manter o SCR ligado

imediatamente aps ocorrer a passagem do estado desligado para o ligado e ser removida a

corrente de porta.

Tempo de disparo (t

on

): o tempo necessrio para o tiristor sair do estado desligado e

atingir a plena conduo.

Tempo de desligamento (t

off

): o tempo necessrio para a transio entre o estado de

conduo e o de bloqueio. devido a fenmenos de recombinao de portadores no

material semicondutor.

Corrente de recombinao reversa (I

rqm

): valor de pico da corrente reversa que ocorre

durante o intervalo de recombinao dos portadores na juno.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-13

P

N-

P

N

N

A

K

G

Contato metlico

Catodo

G

P

N

N

P G

Gate interdigitado

Gate circular

Figura 1.13 - Expanso da rea de conduo do tiristor a partir das vizinhanas da regio de

gate.

A figura 1.14 ilustra algumas destas caractersticas.

di/dt

dv/dt

Tenso direta de bloqueio

Corrente de fuga direta

Von

ton

toff

Corrente de fuga reversa

Tenso reversa de bloqueio

Irqm

Figura 1.14 Tenses e correntes caractersticas de tiristor.

1.4.4 Circuitos de excitao do gate

a) Conduo

Conforme foi visto, a entrada em conduo de um tiristor controlada pela injeo de

uma corrente no terminal da porta, devendo este impulso estar dentro da rea delimitada pela

figura 1.12. Por exemplo, para um dispositivo que deve conduzir 100 A, um acionador que

fornea uma tenso Vgk de 6 V com impedncia de sada 12 ohms adequado. A durao do

sinal de disparo deve ser tal que permita corrente atingir I

L

quando, ento, pode ser retirada.

Observamos ser bastante simples o circuito de disparo de um SCR e, dado o alto

ganho do dispositivo, as exigncias quando ao acionamento so mnimas.

b) Comutao

Se, por um lado, fcil a entrada em conduo de um tiristor, o mesmo no se pode

dizer de sua comutao. Lembramos que a condio de desligamento que a corrente de

anodo fique abaixo do valor I

H

. Se isto ocorrer juntamente com a aplicao de uma tenso

reversa, o bloqueio se dar mais rapidamente.

No existe uma maneira de se desligar o tiristor atravs de seu terminal de controle,

sendo necessrio algum arranjo no nvel do circuito de anodo para reduzir a corrente principal.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-14

b.1) Comutao Natural

utilizada em sistemas de CA nos quais, em funo do carter ondulatrio da tenso

de entrada, em algum instante a corrente tender a se inverter e ter, assim, seu valor

diminudo abaixo de I

H

, desligando o tiristor. Isto ocorrer desde que, num intervalo inferior a

t

off

, no cresa a tenso direta V

ak

, o que poderia lev-lo novamente conduo.

A figura 1.15 mostra um circuito de um controlador de tenso CA, alimentando uma

carga RL, bem como as respectivas formas de onda. Observe que quando a corrente se anula a

tenso sobre a carga se torna zero, indicando que nenhum dos SCRs est em conduo.

vi(t)

i(t)

v

L

L

R

S1

S2

5ms 10ms 15ms 20ms 25ms 30ms 35ms 40ms

200V

-200V

40A

-40A

200V

-200V

vi(t)

i(t)

vL(t)

Figura 1.15 - Controlador de tenso CA com carga RL e formas de onda tpicas.

b.2) Comutao por ressonncia da carga

Em algumas aplicaes especficas, possvel que a carga, pela sua dinmica prpria,

faa com que a corrente tenda a se inverter, fazendo o tiristor desligar. Isto ocorre, por

exemplo, quando existem capacitncias na carga as quais, ressoando com as indutncias do

circuito produzem um aumento na tenso ao mesmo tempo em que reduzem a corrente. Caso

a corrente se torne menor do que a corrente de manuteno e o tiristor permanea

reversamente polarizado pelo tempo suficiente, haver o seu desligamento. A tenso de

entrada pode ser tanto CA quanto CC. A figura 1.16 ilustra tal comportamento. Observe que

enquanto o tiristor conduz a tenso de sada, vo(t), igual tenso de entrada. Quando a

corrente se anula e S1 desliga, o que se observa a tenso imposta pela carga ressonante.

b.3) Comutao forada

utilizada em circuitos com alimentao CC e nos quais no ocorre reverso no

sentido da corrente de anodo.

A idia bsica deste tipo de comutao oferecer corrente de carga um caminho

alternativo ao tiristor, enquanto se aplica uma tenso reversa sobre ele, desligando-o.

Antes do surgimento dos GTOs, este foi um assunto muito discutido, buscando-se

topologias eficientes. Com o advento dos dispositivos com comutao pelo gate, os SCRs

tiveram sua aplicao concentrada nas aplicaes nas quais ocorrem comutao natural ou

pela carga.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-15

Carga

Ressonante

L

io(t)

vo(t)

Vcc

S1

0

i

o

v

o

Vcc

Figura 1.17 Circuito e formas de onda de comutao por ressonncia da carga.

A figura 1.18 mostra um circuito para comutao forada de SCR e as formas de onda

tpicas. A figura 1.19 mostra detalhes de operao do circuito auxiliar de comutao.

Em um tempo anterior a to, a corrente da carga (suposta quase constante, devido

elevada constante de tempo do circuito RL) passa pelo diodo de circulao. A tenso sobre o

capacitor negativa, com valor igual ao da tenso de entrada.

Em t1 o tiristor principal, Sp, disparado, conectando a fonte carga, levando o diodo

Df ao desligamento. Ao mesmo tempo surge uma malha formada por Sp, Cr, D1 e Lr, a qual

permite a ocorrncia de uma ressonncia entre Cr e Lr, levando inverso na polaridade da

tenso do capacitor. Em t1 a tenso atinge seu mximo e o diodo D1 desliga (pois a corrente

se anula). O capacitor est preparado para realizar a comutao de Sp.

Quanto o tiristor auxiliar, Sa, disparado, em t2, a corrente da carga passa a ser

fornecida atravs do caminho formado por Lr, Sa e Cr, levando a corrente por Sp a zero, ao

mesmo tempo em que se aplica uma tenso reversa sobre ele, de modo a deslig-lo.

Vcc

Lr

Cr

+

Vc

i

c

Lo

Ro

+

Vo

i

T

Sp

Sa

D1

D2

Df

200V

-200V

-60A

60A

0

v

C

v

o

i

T

i

C

Figura 1.18 Topologia com comutao forada de SCR e formas de onda tpicas.

Continua a haver corrente por Cr, a qual, em t3, se torna igula corrente da carga,

fazendo com que a variao de sua tenso assuma uma forma linear. Esta tenso cresce (no

sentido negativo) at levar o diodo de circulao conduo, em t4. Como ainda existe

corrente pelo indutor Lr, ocorre uma pequena oscilao na malha Lr, Sa, Cr e D2 e, quando a

corrente por Sa se anula, o capacitor se descarrega at a tenso Vcc na malha formada por Cr,

D1, Lr, fonte e Df.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-16

200V

-60A

60A

-200V

0

i

T

i

c

v

o

v

c

to

t1

t2 t3 t4 t5

Figura 1.19 - Detalhes das formas de onda durante comutao.

1.4.5 Redes Amaciadoras

O objetivo destas redes evitar problemas advindos de excessivos valores para dv/dt e

di/dt, conforme descrito anteriormente.

a) O problema di/dt

Uma primeira medida capaz de limitar possveis danos causados pelo crescimento

excessivamente rpido da corrente de anodo construir um circuito acionador de gate

adequado, que tenha alta derivada de corrente de disparo para que seja tambm rpida a

expanso da rea condutora.

Um reator saturvel em srie com o tiristor tambm limitar o crescimento da corrente

de anodo durante a entrada em conduo do dispositivo.

Alm deste fato tem-se outra vantagem adicional que a reduo da potncia

dissipada no chaveamento pois, quando a corrente de anodo crescer, a tenso V

ak

ser

reduzida pela queda sobre a indutncia.

O atraso no crescimento da corrente de anodo pode levar necessidade de um pulso

mais longo de disparo, ou ainda a uma seqncia de pulsos, para que seja assegurada a

conduo do tiristor.

b) O problema do dv/dt

A limitao do crescimento da tenso direta V

ak

, usualmente feita pelo uso de

circuitos RC, RCD, RLCD em paralelo com o dispositivo, como mostrado na figura 1.20.

No caso mais simples (a), quando o tiristor comutado, a tenso V

ak

segue a dinmica

dada por RC que, alm disso desvia a corrente de anodo facilitando a comutao. Quando o

SCR ligado o capacitor descarrega-se, ocasionando um pico de corrente no tiristor, limitado

pelo valor de R.

No caso (b) este pico pode ser reduzido pelo uso de diferentes resistores para os

processos de carga e descarga de C. No 3

o

caso, o pico limitado por L, o que no traz

eventuais problemas de alto di/dt. A corrente de descarga de C auxilia a entrada em conduo

do tiristor para obter um I

a

>I

L

, uma vez que se soma corrente de anodo proveniente da carga.

A energia acumulada no capacitor praticamente toda dissipada sobre o resistor de

descarga.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-17

R

C

C

R1

R2

D

D

L

R

C

(a) (b) (c)

Figura 1.20 - Circuitos amaciadores para dv/dt.

1.4.6 Associao em Paralelo de Tiristores

Desde o incio da utilizao do tiristor, em 1958, tm crescido constantemente os

limites de tenso e corrente suportveis, atingindo hoje faixas de 5000 V e 4000 A. H, no

entanto, diversas aplicaes nas quais necessria a associao de mais de um destes

componentes, seja pela elevada tenso de trabalho, seja pela corrente exigida pela carga.

Quando a corrente de carga, ou a margem de sobre-corrente necessria, no pode ser

suportada por um nico tiristor, essencial a ligao em paralelo. A principal preocupao

neste caso a equalizao da corrente entre os dispositivos, tanto em regime, como durante o

chaveamento. Diversos fatores influem na distribuio homognea da corrente, desde aspectos

relacionados tecnologia construtiva do dispositivo, at o arranjo mecnico da montagem

final.

Existem duas tecnologias bsicas de construo de tiristores, diferindo basicamente no

que se refere regio do catodo e sua juno com a regio da porta. A tecnologia de difuso

cria uma regio de fronteira entre catodo e gate pouco definida, formando uma juno no-

uniforme, que leva a uma caracterstica de disparo (especialmente quanto ao tempo de atraso e

sensibilidade ao disparo) no homognea. A tecnologia epitaxial permite fronteiras bastante

definidas, implicando numa maior uniformidade nas caractersticas do tiristor. Conclui-se

assim que, quando se faz uma associao (srie ou paralela) destes dispositivos, prefervel

empregar componentes de construo epitaxial.

Em ligaes paralelas de elementos de baixa resistncia, um fator crtico para a

distribuio de corrente so variaes no fluxo concatenado pelas malhas do circuito,

dependendo, pois, das indutncias das ligaes. Outro fator importante relaciona-se com a

caracterstica do coeficiente negativo de temperatura do dispositivo, ou seja, um eventual

desequilbrio de corrente provoca uma elevao de temperatura no SCR que, por sua vez,

melhora as condies de condutividade do componente, aumentando ainda mais o

desequilbrio, podendo lev-lo destruio.

Uma primeira precauo para reduzir estes desbalanceamentos realizar uma

montagem de tal maneira que todos os tiristores estejam a uma mesma temperatura, o que

pode ser feito, por exemplo, pela montagem em um nico dissipador.

No que se refere indutncia das ligaes, a prpria disposio dos componentes em

relao ao barramento afeta significativamente esta distribuio de corrente. Arranjos

cilndricos tendem a apresentar um menor desequilbrio.

1.4.6.1 Estado estacionrio

Alm das consideraes j feitas quanto montagem mecnica, algumas outras

providncias podem ser tomadas para melhorar o equilbrio de corrente nos tiristores:

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-18

a) Impedncia srie

A idia adicionar impedncias em srie com cada componente a fim de limitar o

eventual desequilbrio. Se a corrente crescer num ramo, haver aumento da tenso, o que far

com que a corrente se distribua entre os demais ramos. O uso de resistores implica no

aumento das perdas, uma vez que dado o nvel elevado da corrente, a dissipao pode atingir

centenas de watts, criando problemas de dissipao e eficincia. Outra alternativa o uso de

indutores lineares.

b) Reatores acoplados

Conforme ilustrado na figura 1.21, se a corrente por SCR1 tende a se tornar maior que

por SCR2, uma fora contra-eletro-motriz aparecer sobre a indutncia, proporcionalmente ao

desbalanceamento, tendendo a reduzir a corrente por SCR1. Ao mesmo tempo uma tenso

induzida do outro lado do enrolamento, aumentando a corrente por SCR2. As mais

importantes caractersticas do reator so alto valor da saturao e baixo fluxo residual, para

permitir uma grande excurso do fluxo a cada ciclo.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

(a)

(b)

(c)

Figura 1.21 - Equalizao de corrente com reatores acoplados

1.4.6.2 Disparo

H duas caractersticas do tiristor bastante importantes para boa diviso de corrente

entre os componentes no momento em que se deve dar o incio da conduo: o tempo de

atraso (td) e a mnima tenso de disparo (Von

min

).

O tempo de atraso pode ser interpretado como o intervalo entre a aplicao do sinal de

gate e a real conduo do tiristor.

A mnima tenso de disparo o valor mnimo da tenso direta entre anodo e catodo

com a qual o tiristor pode ser ligado por um sinal adequado de porta. Recorde-se, da

caracterstica esttica do tiristor, que quanto menor a tenso V

ak

, maior deve ser a corrente de

gate para levar o dispositivo conduo.

Diferenas em td podem fazer com que um componente entre em conduo antes do

outro. Com carga indutiva este fato no to crtico pela inerente limitao de di/dt da carga,

o que no ocorre com cargas capacitivas e resistivas. Alm disso, como Von

min

maior que a

queda de tenso direta sobre o tiristor em conduo, possvel que outro dispositivo no

consiga entrar em conduo.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-19

Esta situao crtica quando se acoplam diretamente os tiristores, sendo minimizada

atravs dos dispositivos de equalizao j descritos e ainda por sinais de porta de durao

maior que o tempo de atraso.

1.4.6.3 Desligamento

Especialmente com carga indutiva, deve-se prever algum tipo de arranjo que consiga

manter o equilbrio de corrente mesmo que haja diferentes caractersticas entre os tiristores

(especialmente relacionadas com os tempos de desligamento). A capacitncia do circuito

amaciador limita o desbalanceamento, uma vez que absorve a corrente do tiristor que comea

a desligar.

1.4.6.4 Circuito de disparo

A corrente de gate deve ser alvo de atenes. O uso de um nico circuito de comando

para acionar todos os tiristores minimiza os problemas de tempos de atraso. Alm disso, deve-

se procurar usar nveis iguais de corrente e tenso de gate, uma vez que influem

significativamente no desempenho do disparo. Para minimizar os efeitos das diferenas nas

junes gate-catodo de cada componente pode-se fazer uso de um resistor ou indutor em srie

com o gate, para procurar equalizar os sinais. importante que se tenha atingido a corrente de

disparo (I

L

) antes da retirada do pulso de gate, o que pode levar necessidade de circuitos

mais elaborados para fornecer a energia necessria. Uma seqncia de pulsos tambm pode

ser empregada.

1.4.7 Associao em srie de tiristores

Quando o circuito opera com tenso superior quela suportvel por um nico tiristor,

preciso associar estes componentes em srie, com precaues para garantir a distribuio

equilibrada de tenso entre eles. Devido a diferenas nas correntes de bloqueio, capacitncias

de juno, tempos de atraso, quedas de tenso direta e recombinao reversa, redes de

equalizao externa so necessrias, bem como cuidados quanto ao circuito de disparo.

A figura 1.22 indica uma possvel distribuio de tenso numa associao de 3

tiristores, nas vrias situaes de operao.

Durante os estados de bloqueio direto e reverso (I e VI), diferenas nas caractersticas

de bloqueio resultam em desigual distribuio de tenso em regime. Ou seja, o tiristor com

menor condutncia quando bloqueado ter de suportar a maior tenso. interessante, ento,

usar dispositivos com caractersticas o mais prximas possvel.

Os estados de conduo (III e IV) no apresentam problema de distribuio de tenso.

Estados II e V representam um desbalanceamento indesejado durante os transientes de disparo

e comutao. No estado II o tempo de atraso do SCR1 consideravelmente mais longo que o

dos outros e, assim, ter que, momentaneamente, suportar toda a tenso. O estado V resulta

dos diferentes tempos de recombinao dos componentes. O primeiro a se recombinar

suportar toda a tenso.

1.4.7.1 Estado estacionrio

O mtodo usual de equalizar tenses nas situaes I e VI colocar uma rede resistiva

com cada resistor conectado entre anodo e catodo de cada tiristor. Estes resistores representam

consumo de potncia, sendo desejvel usar os de maior valor possvel. O projeto do valor da

resistncia deve considerar a diferena nos valores das correntes de bloqueio direta e reversa.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-20

T1

T2

T3

1200V

5mA 10mA 50A 10A 10mA 10mA

1000V

50V

150V

1200V

6V

5V

1.0V

1.1V

0.9V

0.9V

1.0V

0.8V

0.7V

0.7V

1200V

100V

900V

200V

+ + + +

+ +

Bloqueio

direto

Conduo

parcial

Conduo

direta

Conduo

reversa

Recuperao

reversa

parcial

Bloqueio

reverso

I II III IV V VI

Figura 1.22 - Tenses em associao de tiristores sem rede de equalizao.

1.4.7.2 Disparo

Um mtodo que pode ser usado para minimizar o desequilbrio do estado II fornecer

uma corrente de porta com potncia suficiente e de rpido crescimento, para minimizar as

diferenas relativas ao tempo de atraso. A largura do pulso deve ser tal que garanta a

continuidade da conduo de todos os tiristores.

1.4.7.3 Desligamento

Para equalizar a tenso no estado V, um capacitor ligado entre anodo e catodo de

cada tiristor. Se a impedncia do capacitor suficientemente baixa e/ou se utiliza a constante

de tempo necessria, o crescimento da tenso no dispositivo mais rpido ser limitado at que

todos se recombinem. Esta implementao tambm alivia a situao no disparo, uma vez que

realiza uma injeo de corrente no tiristor, facilitando a entrada em conduo de todos os

dispositivos.

Mas se o capacitor providencia excelente equalizao de tenso, o pico de corrente

injetado no componente no disparo pode ser excessivo, devendo ser limitado por meio de um

resistor em srie com o capacitor. interessante um alto valor de R e baixo valor de C para,

com o mesmo RC, obter pouca dissipao de energia. Mas se o resistor for de valor muito

elevado ser imposta uma tenso de rpido crescimento sobre o tiristor, podendo ocasionar

disparo por dv/dt. Usa-se ento um diodo em paralelo com o resistor, garantindo um caminho

de carga para o capacitor, enquanto a descarga se faz por R. O diodo deve ter uma

caracterstica suave de recombinao para evitar efeitos indesejveis associados s indutncias

parasitas das ligaes. Recomenda-se o uso de capacitores de baixa indutncia parasita. A

figura 1.23 ilustra tais circuitos de equalizao.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-21

R C R C R C

D D D

Rs Rs Rs

Equalizao esttica

Equalizao

Dinmica

Figura 1.23 - Circuito de equalizao de tenso em associao srie de tiristores.

1.4.7.4 Circuito de disparo

Em muitas aplicaes, devido necessidade de isolamento eltrico entre o circuito de

comando e o de potncia, o sinal de disparo deve ser isolado por meio de algum dispositivo

como, por exemplo, transformadores de pulso ou acopladores ticos, como mostra a figura

1.24.

a) Transformador de pulso

Neste caso, tem-se transformadores capazes de responder apenas em alta frequncia,

mas que possibilitam a transferncia de pulsos de curta durao (at centenas de

microsegundos), aps o que o transformador satura. Caso seja necessrio um pulso mais largo,

ele poder ser obtido por meio de um trem de pulsos, colocando-se um filtro passa-baixas no

lado de sada. Com tais dispositivos deve-se prever algum tipo de limitao de tenso no

secundrio (onde est conectado o gate), a fim de evitar sobretenses.

Quando se usar transformador de pulso preciso garantir que ele suporte pelo menos a

tenso de pico da alimentao. Como as condies de disparo podem diferir cosideravelmente

entre os tiristores, comum inserir uma impedncia em srie com o gate para evitar que um

tiristor com menor impedncia de gate drene o sinal de disparo, impedindo que os demais

dispositivos entrem em conduo. Esta impedncia em srie pode ser um resistor ou um

capacitor, que tornaria mais rpido o crescimento do pulso de corrente.

b) Acoplamento luminoso

O acoplamento tico apresenta como principal vantagem a imunidade a interferncias

eletromagnticas, alm da alta isolao de potencial. Dois tipos bsicos de acopladores so

usados: os opto-acopladores e as fibras ticas. No primeiro caso tem-se um dispositivo onde o

emissor e o receptor esto integrados, apresentando uma isolao tpica de 2500 V. J para as

fibras ticas, o isolamento pode ser de centenas de kV.

A potncia necessria para o disparo provida por duas fontes: uma para alimentar o

emissor (em geral a prpria fonte do circuito de controle) e outra para o lado do receptor.

Eventualmente, a prpria carga armazenada no capacitor do circuito amaciador (ou rede de

equalizao), atravs de um transformador de corrente, pode fornecer a energia para o lado do

receptor, a partir da corrente que circula pelo tiristor, assegurando potncia durante todo o

perodo de conduo.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-22

+Vcc

Pulsos

+V

Req

. .

Req

+

Pulsos

Figura 1.24 Circuitos de acionamento de pulso.

1.4.8 Sobre-tenso

As funes gerais da proteo contra sobre-tenso so: assegurar, to rpido quanto

possvel, que qualquer falha em algum componente afete apenas aquele tiristor diretamente

associado ao componente; aumentar a confiabilidade do sistema; evitar reaes na rede

(como excitao de ressonncias). Estas sobre-tenses podem ser causadas tanto por aes

externas como por distribuio no homognea das tenses entre os dispositivos.

Em aplicaes onde as perdas provocadas pelos resistores de equalizao devem ser

evitadas, a distribuio de tenso pode ser realizada pelo uso de retificadores de avalanche

controlada, que tambm atuam no caso de sobre-tenses. Uma possvel restrio ao uso de

supressores de sobre-tenso (geralmente de xido metlico, os varistores), que a falha em

um certo componente (um curto em um tiristor) pode levar a uma sobrecarga nos demais

supressores, provocando uma destruio em cascata de todos.

A fim de evitar disparos indesejados dos tiristores em virtude do aumento repentino da

tenso, superando o limite de dv/dt ou o valor da mxima tenso direta de bloqueio, deve-se

manter uma polarizao negativa no terminal da porta, aumentado o nvel de tenso

suportvel.

1.4.9 Resfriamento

As caractersticas do tiristor so fornecidas a uma certa temperatura da juno. O calor

produzido na pastilha deve ser dissipado, devendo transferir-se da pastilha para o

encapsulamento, deste para o dissipador e da para o meio de refrigerao (ar ou lquido).

Este conjunto possui uma capacidade de armazenamento de calor, ou seja, uma

constante de tempo trmica, que permite sobrecargas de corrente por perodos curtos.

Tipicamente esta constante da ordem de 3 minutos para refrigerao a ar.

A temperatura de operao da juno deve ser muito menor que o mximo

especificado. Ao aumento da temperatura corresponde uma diminuio na capacidade de

suportar tenses no estado de bloqueio. Tipicamente esta temperatura no deve exceder

120

o

C.

O sistema de refrigerao deve possuir redundncia, ou seja, uma falha no sistema

deve por em operao um outro, garantindo a troca de calor necessria. Existem vrias

maneiras de implementar as trocas: circulao externa de ar filtrado, circulao interna de ar

(com trocador de calor), refrigerao com lquido, etc. A escolha do tipo de resfriamento

influenciada pelas condies ambientais e preferncias do usurio.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-23

1.5 GTO - Gate Turn-Off Thyristor

O GTO, embora tenha sido criado no incio da dcada de 60, por problemas de fraco

desempenho foi pouco utilizado. Com o avano da tecnologia de construo de dispositivos

semicondutores, novas solues foram encontradas para aprimorar tais componentes, que hoje

ocupam significativa faixa de aplicao, especialmente naquelas de elevada potncia, uma vez

que esto disponveis dispositivos para 5000V, 4000A.

1.5.1 Princpio de funcionamento

O GTO possui uma estrutura de 4 camadas, tpica dos componentes da famlia dos

tiristores. Sua caracterstica principal sua capacidade de entrar em conduo e bloquear

atravs de comandos adequados no terminal de gate.

O mecanismo de disparo semelhante ao do SCR: supondo-o diretamente polarizado,

quando a corrente de gate injetada, circula corrente entre gate e catodo. Grande parte de tais

portadores, como a camada de gate suficientemente fina, desloca-se at a camada N

adjacente, atravessando a barreira de potencial e sendo atrados pelo potencial do anodo,

dando incio corrente andica. Se esta corrente se mantiver acima da corrente de

manuteno, o dispositivo no necessita do sinal de gate para manter-se conduzindo.

A figura 1.25 mostra o smbolo do GTO e uma representao simplificada dos

processos de entrada e sada de conduo do componente.

A aplicao de uma polarizao reversa na juno gate-catodo pode levar ao

desligamento do GTO. Portadores livres (lacunas) presentes nas camadas centrais do

dispositivo so atrados pelo gate, fazendo com que seja possvel o restabelecimento da

barreira de potencial na juno J2.

A K

G

P+ N- P N+

Rg

Vg

Vcc

Rg

P+ N- P N+

Rg

Vg

Vcc

Rg

J2

J1

J3

Regio de

Transio

Entrada em conduo

Desligamento

Figura 1.25 - Smbolo, processos de chaveamento e estrutura interna de GTO.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-24

Aparentemente seria possvel tal comportamento tambm no SCR. As diferenas, no

entanto, esto no nvel da construo do componente. O funcionamento como GTO depende,

por exemplo, de fatores como:

facilidade de extrao de portadores pelo terminal de gate - isto possibilitado pelo uso de

dopantes com alta mobilidade

desaparecimento rpido de portadores nas camadas centrais - uso de dopante com baixo

tempo de recombinao. Isto implica que um GTO tem uma maior queda de tenso quando

em conduo, comparado a um SCR de mesmas dimenses.

suportar tenso reversa na juno porta-catodo, sem entrar em avalanche - menor dopagem

na camada de catodo

absoro de portadores de toda superfcie condutora - regio de gate e catodo muito

interdigitada, com grande rea de contato.

Diferentemente do SCR, um GTO pode no ter capacidade de bloquear tenses

reversas.

Existem 2 possibilidades de construir a regio de anodo: uma delas utilizando apenas

uma camada p+, como nos SCR. Neste caso o GTO apresentar uma caracterstica lenta de

comutao, devido maior dificuldade de extrao dos portadores, mas suportar tenses

reversas na juno J2.

A outra alternativa, mostrada na figura 1.26, introduzir regies n+ que penetrem na

regio p+ do anodo, fazendo contato entre a regio intermediria n- e o terminal de anodo.

Isto, virtualmente, curto-circuita a juno J1 quando o GTO polarizado reversamente. No

entanto, torna-o muito mais rpido no desligamento (com polarizao direta). Como a juno

J3 formada por regies muito dopadas, ela no consegue suportar tenses reversas elevadas.

Caso um GTO deste tipo deva ser utilizado em circuitos nos quais fique sujeito a tenso

reversa, ele deve ser associado em srie com um diodo, o qual bloquear a tenso.

anodo

metalizao do gate

metalizao do catodo placa de

contato do

catodo

p+ p+ p+

n+ n+

n-

p

n+ n+ n+

J1

J2

J3

Figura 1.26 - Estrutura interna de GTO rpido (sem bloqueio reverso)

1.5.2 Parmetros bsicos do GTO

Os smbolos utilizados pelos diversos fabricantes diferem, embora as grandezas

representadas sejam, quase sempre, as mesmas.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-25

V

drxm

- Tenso de pico, repetitiva, de estado desligado: sob condies dadas, a mxima

tenso instantnea permissvel, em estado desligado, que no ultrapasse o dv/dt mximo,

aplicvel repetidamente ao GTO.

I

t

- Corrente (RMS) de conduo: mxima corrente (valor RMS) que pode circular

continuamente pelo GTO.

I

tcm

- Corrente de conduo repetitiva controlvel: mxima corrente repetitiva, cujo valor

instantneo ainda permite o desligamento do GTO, sob determinadas condies.

I2t: escala para expressar a capacidade de sobrecorrente no-repetitiva, com respeito a um

pulso de curta durao. utilizado no dimensionamento dos fusveis de proteo.

di/dt: taxa de crescimento mxima da corrente de anodo.

V

grm

- Tenso reversa de pico de gate repetitiva: mxima tenso instantnea permissvel

aplicvel juno gate-catodo.

dv/dt: mxima taxa de crescimento da tenso direta de anodo para catodo.

I

H

- corrente de manuteno: Corrente de anodo que mantm o GTO em conduo mesmo

na ausncia de corrente de porta.

I

L

- corrente de disparo: corrente de anodo necessria para que o GTO entre em conduo

com o desligamento da corrente de gate.

t

gt

- tempo de disparo: tempo entre a aplicao da corrente de gate e a queda da tenso V

ak

.

t

gq

- tempo de desligamento: tempo entre a aplicao de uma corrente negativa de gate e a

queda da corrente de anodo (t

gq

=t

s

+t

f

)

t

s

- tempo de armazenamento

1.5.3 Condies do sinal de porta para chaveamento

Desde que, geralmente, o GTO est submetido a condies de alto di/dt, necessrio

que o sinal de porta tambm tenha rpido crescimento, tendo um valor de pico relativamente

elevado. Deve ser mantido neste nvel por um tempo suficiente (t

w1

) para que a tenso V

ak

caia

a seu valor de conduo direta. conveniente que se mantenha a corrente de gate durante todo

o perodo de conduo, especialmente se a corrente de anodo for pequena, de modo a garantir

o estado "ligado". A figura 1.27 ilustra as formas de corrente recomendadas para a entrada em

conduo e tambm para o desligamento.

Durante o intervalo "ligado" existe uma grande quantidade de portadores nas camadas

centrais do semicondutor. A comutao do GTO ocorrer pela retirada destes portadores e,

ainda, pela impossibilidade da vinda de outros das camadas ligadas ao anodo e ao catodo, de

modo que a barreira de potencial da juno J2 possa se restabelecer.

O grande pico reverso de corrente apressa a retirada dos portadores. A taxa de

crescimento desta corrente relaciona-se com o tempo de armazenamento, ou seja, o tempo

decorrido entre a aplicao do pulso negativo e o incio da queda (90%) da corrente de anodo.

Quanto maior for a derivada, menor o tempo.

Quando a corrente drenada comea a cair, a tenso reversa na juno gate-catodo

cresce rapidamente, ocorrendo um processo de avalanche. A tenso negativa de gate deve ser

mantida prxima ao valor da tenso de avalanche. A potncia dissipada neste processo

controlada (pela prpria construo do dispositivo). Nesta situao a tenso V

ak

cresce e o

GTO desliga.

Para evitar o disparo do GTO por efeito dv/dt, uma tenso reversa de porta pode ser

mantida durante o intervalo de bloqueio do dispositivo.

O ganho de corrente tpico, no desligamento, baixo (de 5 a 10), o que significa que,

especialmente para os GTOs de alta corrente, o circuito de acionamento, por si s, envolve a

manobra de elevadas correntes.

Eletrnica de Potncia - Cap. 1 J. A. Pomilio

DSCE FEEC UNICAMP 2001

1-26

Ig

Vgk

Ifgm

Ifg

t

w1

t

r

t

gq

t

s

Irg

dIrg

dt

Vrg (tenso negativa

Vr

avalanche

do circuito de comando)

Figura 1.27 - Formas de onda tpicas do circuito de comando de porta de GTO.

1.5.4 Circuitos amaciadores (snubber)

1.5.4.1 Desligamento

Durante o desligamento, com o progressivo restabelecimento da barreira de potencial

na juno reversamente polarizada, a corrente de anodo vai se concentrando em reas cada vez

menores, concentrando tambm os pontos de dissipao de potncia. Uma limitao da taxa

de crescimento da tenso, alm de impedir o gatilhamento por efeito dv/dt, implicar numa

reduo da potncia dissipada nesta transio.

O circuito mais simples utilizado para esta funo uma rede RCD, como mostrado na

figura 1.28.

Supondo uma corrente de carga constante, ao ser desligado o GTO, o capacitor se

carrega com a passagem da corrente da carga, com sua tenso vaiando de forma praticamente

linear. Assim, o dv/dt determinado pela capacitncia. Quando o GTO entrar em conduo,

este capacitor se descarrega atravs do resistor. A descarga deve ocorrer dentro do mnimo